# **OKI Semiconductor**

Oki, Network Solutions for a Global Society

PEDL87V21071-01

Issue Date: Nov. 15, 2005

## ML87V21071

## **Preliminary**

Video Signal Noise Reduction IC with a Built-in Frame Memory

#### GENERAL DESCRIPTION

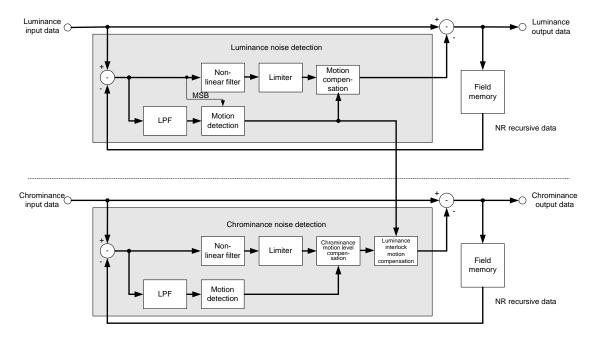

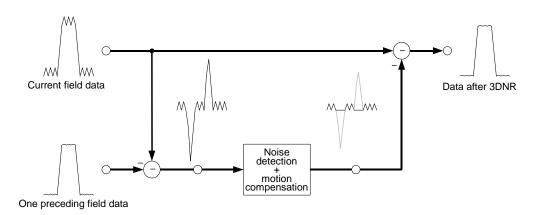

The ML87V21071, which comprises a frame memory and signal processing and memory control logic circuits, has achieved motion-adaptive 3D noise reduction.

To perform noise reduction with afterimage suppression, the ML87V21071 also enables noise reduction using the edge-adaptive 2D noise reduction filter.

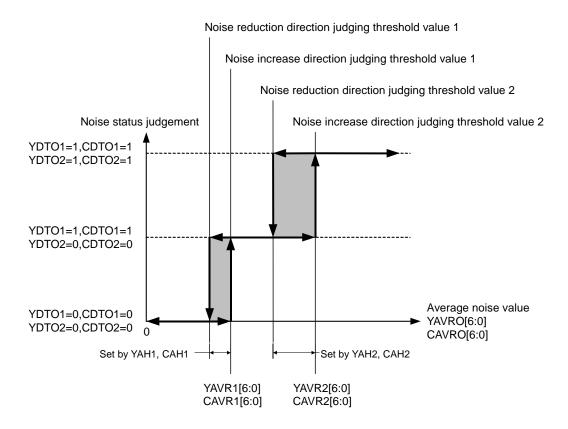

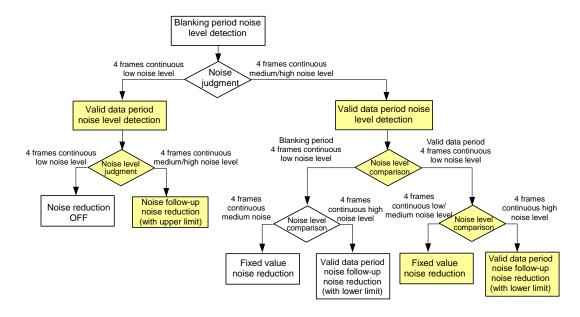

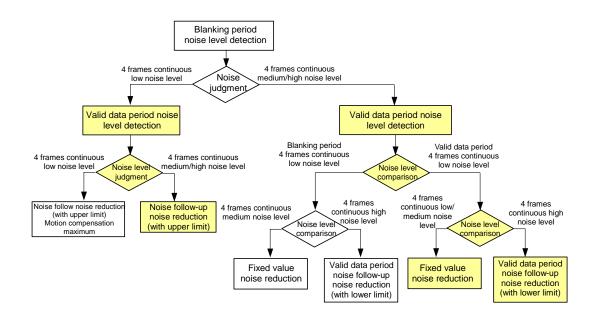

Each noise reduction function allows setting an automatic mode. In automatic mode, noise of a vertical blanking period and a valid data period is detected to reduce noise according to the noise status from which the noise reduction setting value is detected.

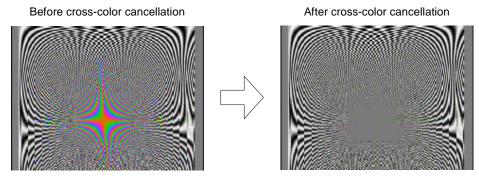

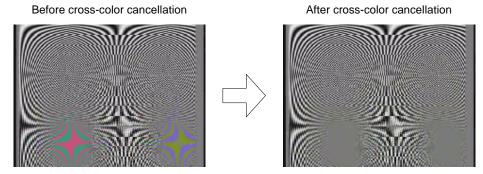

The ML87V21071 also has a cross-color cancellation function that uses the motion-adaptive 3D comb filter method that removes cross colors occurring at two-dimensional YC separation in the NTSC/PAL system.

Since the same format as the input can be selected for output, noise reduction can easily be achieved by inserting the IC into the conventional system.

#### **FEATURES**

• Built-in memory:

Frame memory  $(78 \times 608 \times 16\text{-bit}) \times 1$  unit

Maximum input and output operating frequencies (16-bit/8-bit, ITU-R BT.656): 14.75/29.5 MHz

\* For 525p/625p, only 16-bit input mode is supported (Max.: 29.5 MHz).

• Power supply voltage:

$3.3 \text{ V} \pm 0.3 \text{ V}$

• Input/ouput pin:

LVCMOS (3.3 V)

• Input/ouput data format:

YCbCr (8 bit (Y) + 8 bit (CbCr))(4:2:2): 16-bit mode YCbCr (8 bit (YCbCr))(4:2:2): 8-bit mode

ITU-R656 (8 bit (YCbCr)): ITU-R BT.656 mode

\* In 16-bit input mode, neither 8-bit mode nor ITU-R BT.656 mode can be selected for output.

• Serial bus:

I<sup>2</sup>C-bus interface: (400 kHz, 100 kHz)

Memory controller:

Compatible with 625/50Hz 2:1(625i), 525/60Hz 2:1(525i), 625/50Hz 1:1(625p), and 525/60Hz 1:1(525p)

• Motion-adaptive 3D noise reduction:

Frame-field-line-correlation noise detection and noise subtraction method

Supports automatic noise reduction setting

• Edge-adaptive 2D noise reduction:

Edge-adaptive space filter used

Chrominance signal cross color cancelling:

Motion-adaptive 3D comb filter used

Compatible with 525i (NTSC decode signal)/625i (PAL decode signal)

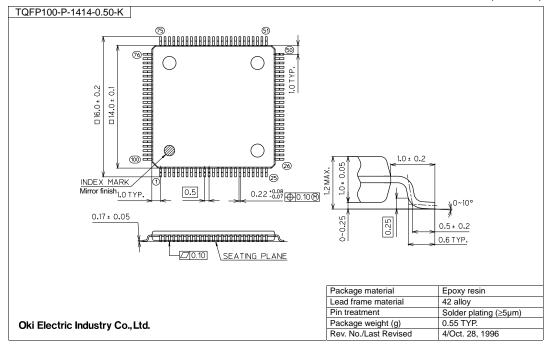

• Package:

100-pin TQFP (TQFP100-P-1414-0.50-K) (ML87V21071TB)

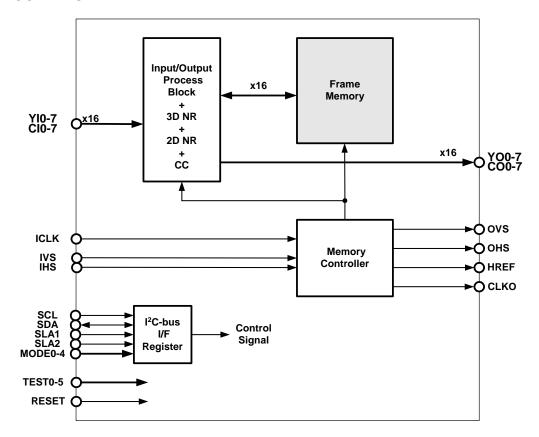

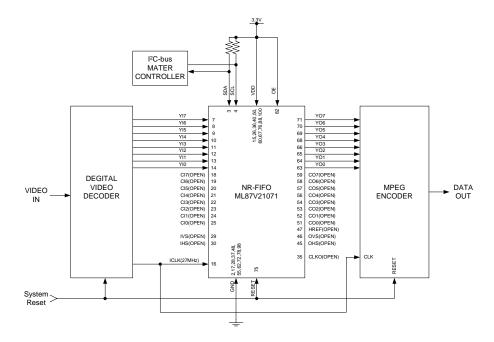

## **BLOCK DIAGRAM**

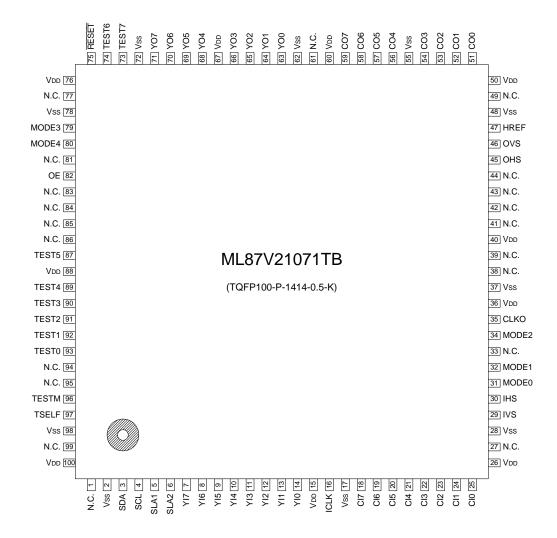

## PIN CONFIGURATION (TOP VIEW)

## PIN DESCRIPTIONS

| No. | Symbol          | I/O      | Pad Remarks                    | Pin Description                                                 | Termination of unused pin    |

|-----|-----------------|----------|--------------------------------|-----------------------------------------------------------------|------------------------------|

| 1   | N.C.            | _        |                                | Unused pin                                                      | Not used                     |

| 2   | V <sub>SS</sub> | _        |                                | Ground                                                          | Х                            |

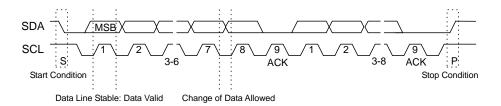

| 3   | SDA             | I/O      | Schmitt(IN)/<br>OpenDrain(OUT) | I <sup>2</sup> C-bus data pin                                   | Х                            |

| 4   | SCL             | ı        | Schmitt                        | I <sup>2</sup> C-bus clock pin                                  | X                            |

| 5   | SLA1            | I        | Schmitt<br>pull-down 50k       | Slave address setting pin bit 1                                 | Not used or connected to GND |

| 6   | SLA2            | I        | Schmitt<br>pull-down 50k       | Slave address setting pin bit 2                                 | Not used or connected to GND |

| 7   | YI7             | I        |                                | Luminance signal input pin bit 7 (MSB)                          | Х                            |

| 8   | YI6             | I        |                                | Luminance signal input pin bit 6                                | Х                            |

| 9   | YI5             | I        |                                | Luminance signal input pin bit 5                                | Х                            |

| 10  | YI4             | I        |                                | Luminance signal input pin bit 4                                | Х                            |

| 11  | YI3             | I        |                                | Luminance signal input pin bit 3                                | Х                            |

| 12  | YI2             | I        |                                | Luminance signal input pin bit 2                                | Х                            |

| 13  | YI1             | I        |                                | Luminance signal input pin bit 1                                | Х                            |

| 14  | YI0             | Ι        |                                | Luminance signal input pin bit 0 (LSB)                          | X                            |

| 15  | $V_{DD}$        | _        |                                | 3.3 V power supply                                              | Х                            |

| 16  | ICLK            | I        |                                | System clock Input pin                                          | X                            |

| 17  | $V_{SS}$        | _        |                                | Ground                                                          | X                            |

| 18  | CI7             | I        | pull-down 50k                  | Chrominance signal input pin bit 7 (MSB)                        | Not used or connected to GND |

| 19  | CI6             | I        | pull-down 50k                  | Chrominance signal input pin bit 6                              | Not used or connected to GND |

| 20  | CI5             | I        | pull-down 50k                  | Chrominance signal input pin bit 5                              | Not used or connected to GND |

| 21  | CI4             | I        | pull-down 50k                  | Chrominance signal input pin bit 4                              | Not used or connected to GND |

| 22  | CI3             | I        | pull-down 50k                  | Chrominance signal input pin bit 3                              | Not used or connected to GND |

| 23  | CI2             | I        | pull-down 50k                  | Chrominance signal input pin bit 2                              | Not used or connected to GND |

| 24  | CI1             | I        | pull-down 50k                  | Chrominance signal input pin bit 1                              | Not used or connected to GND |

| 25  | CI0             | I        | pull-down 50k                  | Chrominance signal input pin bit 0 (LSB)                        | Not used or connected to GND |

| 26  | $V_{DD}$        | _        |                                | 3.3 V power supply                                              | X                            |

| 27  | N.C.            | _        |                                | Unused pin                                                      | Not used                     |

| 28  | $V_{SS}$        | _        |                                | Ground                                                          | X                            |

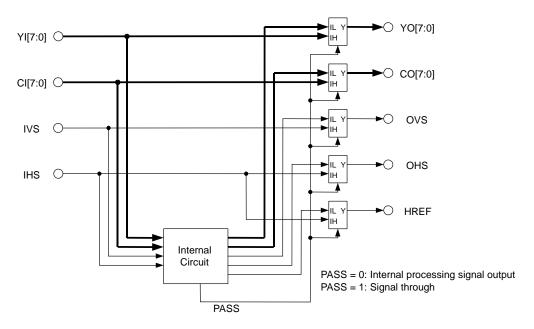

| 29  | IVS             | I        | Schmitt<br>pull-down 50k       | Input system vertical Sync. signal input pin                    | Not used or connected to GND |

| 30  | IHS             | I        | Schmitt<br>pull-down 50k       | Input system horizontal Sync. signal input pin                  | Not used or connected to GND |

| 31  | MODE0           | I        | Schmitt<br>pull-down 50k       | Mode setting pin bit 0 (Equivalent to internal register VMD[0]) | Not used or connected to GND |

| 32  | MODE1           | I        | Schmitt<br>pull-down 50k       | Mode setting pin bit 1 (Equivalent to internal register HMD[0]) | Not used or connected to GND |

| 33  | N.C.            | <u> </u> |                                | Unused pin                                                      | Not used                     |

|     |                 | •        | •                              | •                                                               | •                            |

| MODE2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | No. | Symbol          | I/O        | Pad Remarks | Pin Description                                                   | Termination of unused pin    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------|------------|-------------|-------------------------------------------------------------------|------------------------------|

| State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 34  | MODE2           | ı          |             | Mode setting pin bit 2 (Equivalent to internal register DISEL[0]) | Not used or connected to GND |

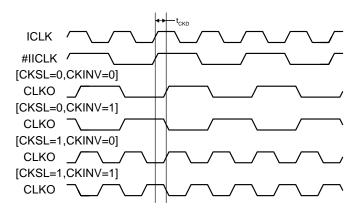

| 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 35  | CLKO            | 0          |             | Clock output (I <sup>2</sup> C-bus control possible)              | Not used                     |

| 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 36  |                 |            |             | ,                                                                 | X                            |

| 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 37  |                 |            |             | Ground                                                            | X                            |

| 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 38  |                 | _          |             | Unused pin                                                        | Not used                     |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 39  | N.C.            | _          |             | Unused pin                                                        | Not used                     |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 40  | $V_{DD}$        | _          |             | 3.3 V power supply                                                | X                            |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 41  |                 | <b> </b> — |             | Unused pin                                                        | Not used                     |

| 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 42  | N.C.            | <b>—</b>   |             | Unused pin                                                        | Not used                     |

| Horizontal Sync. signal output pin   Not used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 43  | N.C.            | <b>—</b>   |             | Unused pin                                                        | Not used                     |

| 46         OVS         O         Vertical Sync. signal output pin         Not used           47         HREF         O         Data output horizontal reference signal output pin         Not used           48         Vss         —         Ground         X           49         N.C.         —         Unused pin         Not used           50         Vpo         —         3.3 V power supply         X           51         CO0         O         Chrominance signal output pin bit 0 (LSB)         Not used           52         CO1         O         Chrominance signal output pin bit 1         Not used           53         CO2         O         Chrominance signal output pin bit 2         Not used           54         CO3         O         Chrominance signal output pin bit 3         Not used           55         Vss         —         Ground         X           56         CO4         O         Chrominance signal output pin bit 4         Not used           57         CO5         O         Chrominance signal output pin bit 6         Not used           58         CO6         O         Chrominance signal output pin bit 7 (MSB)         Not used           59         CO7         O         Chro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 44  | N.C.            | <b> </b> — |             | Unused pin                                                        | Not used                     |

| 47         HREF         O         Data output horizontal reference signal output pin pin         Not used           48         Vss         —         Ground         X           49         N.C.         —         Unused pin         Not used           50         Vpb         —         3.3 V power supply         X           51         COO         O         Chrominance signal output pin bit 0 (LSB)         Not used           52         CO1         O         Chrominance signal output pin bit 1         Not used           53         CO2         O         Chrominance signal output pin bit 2         Not used           54         CO3         O         Chrominance signal output pin bit 3         Not used           55         Vss         —         Ground         X           56         CO4         O         Chrominance signal output pin bit 5         Not used           57         CO5         O         Chrominance signal output pin bit 6         Not used           58         CO6         O         Chrominance signal output pin bit 7 (MSB)         Not used           60         Vpo         —         3.3 V power supply         X           K         Vss         —         Ground <t< td=""><td>45</td><td>OHS</td><td>0</td><td></td><td>Horizontal Sync. signal output pin</td><td>Not used</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 45  | OHS             | 0          |             | Horizontal Sync. signal output pin                                | Not used                     |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 46  | OVS             | 0          |             | Vertical Sync. signal output pin                                  | Not used                     |

| 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 47  | HREF            | 0          |             |                                                                   | Not used                     |

| 50         V <sub>DD</sub> —         3.3 V power supply         X           51         CO0         O         Chrominance signal output pin bit 0 (LSB)         Not used           52         CO1         O         Chrominance signal output pin bit 1         Not used           53         CO2         O         Chrominance signal output pin bit 2         Not used           54         CO3         O         Chrominance signal output pin bit 3         Not used           55         V <sub>SS</sub> —         Ground         X           56         CO4         O         Chrominance signal output pin bit 4         Not used           57         CO5         O         Chrominance signal output pin bit 5         Not used           58         CO6         O         Chrominance signal output pin bit 6         Not used           59         CO7         O         Chrominance signal output pin bit 7 (MSB)         Not used           60         V <sub>DD</sub> —         3.3 V power supply         X           61         N.C.         —         Unused pin         Not used           62         V <sub>SS</sub> —         Ground         X           63         YO0         O         Luminance signal output pin bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48  | V <sub>SS</sub> | _          |             | Ground                                                            | X                            |

| 51         CO0         O         Chrominance signal output pin bit 0 (LSB)         Not used           52         CO1         O         Chrominance signal output pin bit 1         Not used           53         CO2         O         Chrominance signal output pin bit 2         Not used           54         CO3         O         Chrominance signal output pin bit 3         Not used           55         Vss         —         Ground         X           56         CO4         O         Chrominance signal output pin bit 4         Not used           57         CO5         O         Chrominance signal output pin bit 5         Not used           58         CO6         O         Chrominance signal output pin bit 6         Not used           59         CO7         O         Chrominance signal output pin bit 7 (MSB)         Not used           60         Vp0         —         3.3 V power supply         X           61         N.C.         —         Unused pin         Not used           62         Vss         —         Ground         X           63         YO0         O         Luminance signal output pin bit 0 (LSB)         X           64         YO1         O         Luminance signal out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 49  | N.C.            | _          |             | Unused pin                                                        | Not used                     |

| 52         CO1         O         Chrominance signal output pin bit 1         Not used           53         CO2         O         Chrominance signal output pin bit 2         Not used           54         CO3         O         Chrominance signal output pin bit 3         Not used           55         Vss         —         Ground         X           56         CO4         O         Chrominance signal output pin bit 4         Not used           57         CO5         O         Chrominance signal output pin bit 5         Not used           58         CO6         O         Chrominance signal output pin bit 6         Not used           59         CO7         O         Chrominance signal output pin bit 7 (MSB)         Not used           60         VpD         —         3.3 V power supply         X           61         N.C.         —         Unused pin         Not used           62         Vss         —         Ground         X           63         YO0         O         Luminance signal output pin bit 0 (LSB)         X           64         YO1         O         Luminance signal output pin bit 2         X           65         YO2         O         Luminance signal output pin bit 3 </td <td>50</td> <td><math>V_{DD}</math></td> <td>_</td> <td></td> <td>3.3 V power supply</td> <td>Х</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 50  | $V_{DD}$        | _          |             | 3.3 V power supply                                                | Х                            |

| 53         CO2         O         Chrominance signal output pin bit 2         Not used           54         CO3         O         Chrominance signal output pin bit 3         Not used           55         Vss         —         Ground         X           56         CO4         O         Chrominance signal output pin bit 4         Not used           57         CO5         O         Chrominance signal output pin bit 5         Not used           58         CO6         O         Chrominance signal output pin bit 6         Not used           59         CO7         O         Chrominance signal output pin bit 7 (MSB)         Not used           60         Vpb         —         3.3 V power supply         X           61         N.C.         —         Unused pin         Not used           62         Vss         —         Ground         X           63         YO0         O         Luminance signal output pin bit 0 (LSB)         X           64         YO1         O         Luminance signal output pin bit 1         X           65         YO2         O         Luminance signal output pin bit 3         X           67         Vpb         —         3.3 V power supply         X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 51  | CO0             | 0          |             | Chrominance signal output pin bit 0 (LSB)                         | Not used                     |

| 54         CO3         O         Chrominance signal output pin bit 3         Not used           55         Vss         —         Ground         X           56         CO4         O         Chrominance signal output pin bit 4         Not used           57         CO5         O         Chrominance signal output pin bit 5         Not used           58         CO6         O         Chrominance signal output pin bit 6         Not used           59         CO7         O         Chrominance signal output pin bit 7 (MSB)         Not used           60         VpD         —         3.3 V power supply         X           61         N.C.         —         Unused pin         Not used           62         Vss         —         Ground         X           63         YO0         O         Luminance signal output pin bit 0 (LSB)         X           64         YO1         O         Luminance signal output pin bit 1         X           65         YO2         O         Luminance signal output pin bit 3         X           67         VpD         —         3.3 V power supply         X           68         YO4         O         Luminance signal output pin bit 4         X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 52  | CO1             | 0          |             | Chrominance signal output pin bit 1                               | Not used                     |

| 55         V <sub>SS</sub> —         Ground         X           56         CO4         O         Chrominance signal output pin bit 4         Not used           57         CO5         O         Chrominance signal output pin bit 5         Not used           58         CO6         O         Chrominance signal output pin bit 6         Not used           59         CO7         O         Chrominance signal output pin bit 7 (MSB)         Not used           60         V <sub>DD</sub> —         3.3 V power supply         X           61         N.C.         —         Unused pin         Not used           62         V <sub>SS</sub> —         Ground         X           63         YO0         O         Luminance signal output pin bit 0 (LSB)         X           64         YO1         O         Luminance signal output pin bit 1         X           65         YO2         O         Luminance signal output pin bit 2         X           66         YO3         O         Luminance signal output pin bit 3         X           67         V <sub>DD</sub> —         3.3 V power supply         X           68         YO4         O         Luminance signal output pin bit 4         X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 53  | CO2             | 0          |             | Chrominance signal output pin bit 2                               | Not used                     |

| 56         CO4         O         Chrominance signal output pin bit 4         Not used           57         CO5         O         Chrominance signal output pin bit 5         Not used           58         CO6         O         Chrominance signal output pin bit 6         Not used           59         CO7         O         Chrominance signal output pin bit 7 (MSB)         Not used           60         V <sub>DD</sub> —         3.3 V power supply         X           61         N.C.         —         Unused pin         Not used           62         V <sub>SS</sub> —         Ground         X           63         YO0         O         Luminance signal output pin bit 0 (LSB)         X           64         YO1         O         Luminance signal output pin bit 1         X           65         YO2         O         Luminance signal output pin bit 2         X           66         YO3         O         Luminance signal output pin bit 3         X           67         V <sub>DD</sub> —         3.3 V power supply         X           68         YO4         O         Luminance signal output pin bit 4         X           69         YO5         O         Luminance signal output pin bit 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 54  | CO3             | 0          |             | Chrominance signal output pin bit 3                               | Not used                     |

| 57         CO5         O         Chrominance signal output pin bit 5         Not used           58         CO6         O         Chrominance signal output pin bit 6         Not used           59         CO7         O         Chrominance signal output pin bit 7 (MSB)         Not used           60         VpD         —         3.3 V power supply         X           61         N.C.         —         Unused pin         Not used           62         Vss         —         Ground         X           63         YO0         O         Luminance signal output pin bit 0 (LSB)         X           64         YO1         O         Luminance signal output pin bit 1         X           65         YO2         O         Luminance signal output pin bit 2         X           66         YO3         O         Luminance signal output pin bit 3         X           67         VpD         —         3.3 V power supply         X           68         YO4         O         Luminance signal output pin bit 4         X           69         YO5         O         Luminance signal output pin bit 5         X           70         YO6         O         Luminance signal output pin bit 6         X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 55  | Vss             |            |             | Ground                                                            | X                            |

| 58         CO6         O         Chrominance signal output pin bit 6         Not used           59         CO7         O         Chrominance signal output pin bit 7 (MSB)         Not used           60         V <sub>DD</sub> —         3.3 V power supply         X           61         N.C.         —         Unused pin         Not used           62         V <sub>SS</sub> —         Ground         X           63         YO0         O         Luminance signal output pin bit 0 (LSB)         X           64         YO1         O         Luminance signal output pin bit 1         X           65         YO2         O         Luminance signal output pin bit 2         X           66         YO3         O         Luminance signal output pin bit 3         X           67         V <sub>DD</sub> —         3.3 V power supply         X           68         YO4         O         Luminance signal output pin bit 4         X           69         YO5         O         Luminance signal output pin bit 5         X           70         YO6         O         Luminance signal output pin bit 7 (MSB)         X           72         V <sub>SS</sub> —         Ground         X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 56  | CO4             | 0          |             | Chrominance signal output pin bit 4                               | Not used                     |

| 59         CO7         O         Chrominance signal output pin bit 7 (MSB)         Not used           60         V <sub>DD</sub> —         3.3 V power supply         X           61         N.C.         —         Unused pin         Not used           62         V <sub>SS</sub> —         Ground         X           63         YO0         O         Luminance signal output pin bit 0 (LSB)         X           64         YO1         O         Luminance signal output pin bit 1         X           65         YO2         O         Luminance signal output pin bit 2         X           66         YO3         O         Luminance signal output pin bit 3         X           67         V <sub>DD</sub> —         3.3 V power supply         X           68         YO4         O         Luminance signal output pin bit 4         X           69         YO5         O         Luminance signal output pin bit 5         X           70         YO6         O         Luminance signal output pin bit 7 (MSB)         X           71         YO7         O         Luminance signal output pin bit 7 (MSB)         X           72         Vss         —         Ground         Test input pin bit 6 (1: Test mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 57  | CO5             | 0          |             | Chrominance signal output pin bit 5                               | Not used                     |

| 60         V <sub>DD</sub> —         3.3 V power supply         X           61         N.C.         —         Unused pin         Not used           62         V <sub>SS</sub> —         Ground         X           63         YOO         O         Luminance signal output pin bit 0 (LSB)         X           64         YO1         O         Luminance signal output pin bit 1         X           65         YO2         O         Luminance signal output pin bit 2         X           66         YO3         O         Luminance signal output pin bit 3         X           67         V <sub>DD</sub> —         3.3 V power supply         X           68         YO4         O         Luminance signal output pin bit 4         X           69         YO5         O         Luminance signal output pin bit 5         X           70         YO6         O         Luminance signal output pin bit 6         X           71         YO7         O         Luminance signal output pin bit 7 (MSB)         X           72         Vss         —         Ground         X           73         TEST7         I         Schmitt pull-down 50k         Test input pin bit 6 (1: Test mode)         Not used or c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 58  | CO6             | 0          |             | Chrominance signal output pin bit 6                               | Not used                     |

| 61         N.C.         —         Unused pin         Not used           62         V <sub>SS</sub> —         Ground         X           63         YOO         O         Luminance signal output pin bit 0 (LSB)         X           64         YO1         O         Luminance signal output pin bit 1         X           65         YO2         O         Luminance signal output pin bit 2         X           66         YO3         O         Luminance signal output pin bit 3         X           67         V <sub>DD</sub> —         3.3 V power supply         X           68         YO4         O         Luminance signal output pin bit 4         X           69         YO5         O         Luminance signal output pin bit 5         X           70         YO6         O         Luminance signal output pin bit 6         X           71         YO7         O         Luminance signal output pin bit 7 (MSB)         X           72         V <sub>SS</sub> —         Ground         X           73         TEST7         I         Schmitt pull-down 50k         Test input pin bit 7 (1: Test mode)         Not used or connected to G           75         RESET         I         Schmitt pull-down 50k<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 59  | CO7             | 0          |             | Chrominance signal output pin bit 7 (MSB)                         | Not used                     |

| 62         V <sub>SS</sub> —         Ground         X           63         YOO         O         Luminance signal output pin bit 0 (LSB)         X           64         YO1         O         Luminance signal output pin bit 1         X           65         YO2         O         Luminance signal output pin bit 2         X           66         YO3         O         Luminance signal output pin bit 3         X           67         V <sub>DD</sub> —         3.3 V power supply         X           68         YO4         O         Luminance signal output pin bit 4         X           69         YO5         O         Luminance signal output pin bit 5         X           70         YO6         O         Luminance signal output pin bit 6         X           71         YO7         O         Luminance signal output pin bit 7 (MSB)         X           72         V <sub>SS</sub> —         Ground         X           73         TEST7         I         Schmitt pull-down 50k         Test input pin bit 7 (1: Test mode)         Not used or connected to G           74         TEST6         I         Schmitt pull-down 50k         Test input pin bit 6 (1: Test mode)         Not used or connected to G           7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 60  | $V_{DD}$        | _          |             | 3.3 V power supply                                                | Х                            |

| Schmitt   Schmitt   Schmitt   Schmitt   FESTE     Schmitt   Schmitt   Schmitt   Dull-down 50k   System reset   1. Operation   System reset   Schmitt   Sch | 61  | N.C.            | _          |             | Unused pin                                                        | Not used                     |

| 64         YO1         O         Luminance signal output pin bit 1         X           65         YO2         O         Luminance signal output pin bit 2         X           66         YO3         O         Luminance signal output pin bit 3         X           67         V <sub>DD</sub> —         3.3 V power supply         X           68         YO4         O         Luminance signal output pin bit 4         X           69         YO5         O         Luminance signal output pin bit 5         X           70         YO6         O         Luminance signal output pin bit 6         X           71         YO7         O         Luminance signal output pin bit 7 (MSB)         X           72         Vss         —         Ground         X           73         TEST7         I         Schmitt pull-down 50k         Test input pin bit 7 (1: Test mode)         Not used or connected to G           74         TEST6         I         Schmitt pull-down 50k         Test input pin bit 6 (1: Test mode)         Not used or connected to G           75         RESET         I         Schmitt Schmitt O: System reset/input pin O: System reset/input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 62  | V <sub>SS</sub> | _          |             | Ground                                                            | Х                            |

| 65         YO2         O         Luminance signal output pin bit 2         X           66         YO3         O         Luminance signal output pin bit 3         X           67         V <sub>DD</sub> —         3.3 V power supply         X           68         YO4         O         Luminance signal output pin bit 4         X           69         YO5         O         Luminance signal output pin bit 5         X           70         YO6         O         Luminance signal output pin bit 6         X           71         YO7         O         Luminance signal output pin bit 7 (MSB)         X           72         V <sub>SS</sub> —         Ground         X           73         TEST7         I         Schmitt pull-down 50k         Test input pin bit 7 (1: Test mode)         Not used or connected to G           74         TEST6         I         Schmitt pull-down 50k         Test input pin bit 6 (1: Test mode)         Not used or connected to G           75         RESET         I         Schmitt O: System reset/input pin O: System reset (input pin D)         X           1: Operation         X         X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 63  | YO0             | 0          |             | Luminance signal output pin bit 0 (LSB)                           | Х                            |

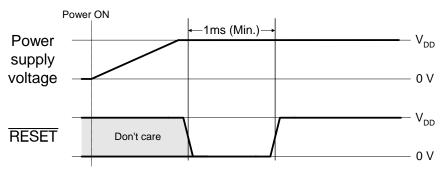

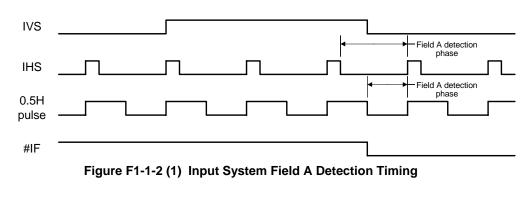

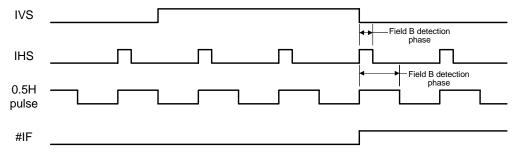

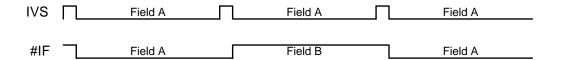

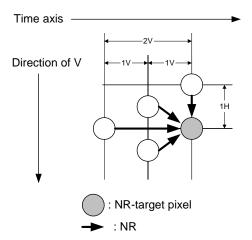

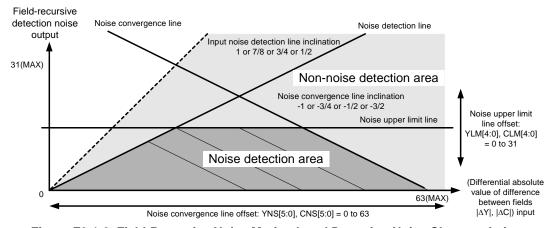

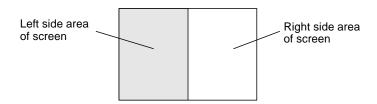

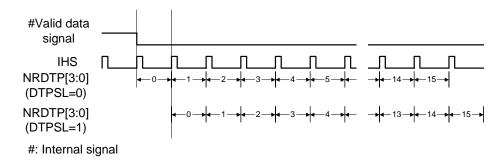

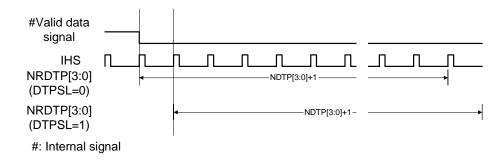

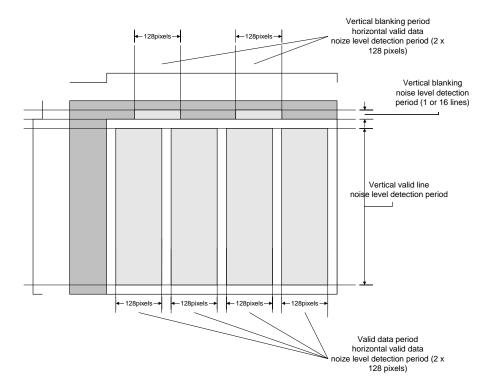

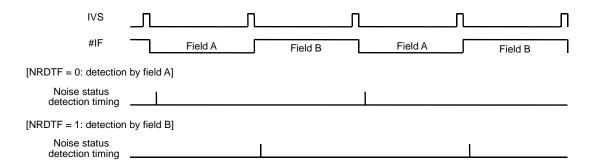

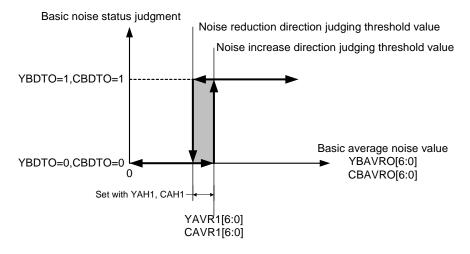

| 66         YO3         O         Luminance signal output pin bit 3         X           67         V <sub>DD</sub> —         3.3 V power supply         X           68         YO4         O         Luminance signal output pin bit 4         X           69         YO5         O         Luminance signal output pin bit 5         X           70         YO6         O         Luminance signal output pin bit 6         X           71         YO7         O         Luminance signal output pin bit 7 (MSB)         X           72         V <sub>SS</sub> —         Ground         X           73         TEST7         I         Schmitt pull-down 50k         Test input pin bit 7 (1: Test mode)         Not used or connected to G           74         TEST6         I         Schmitt pull-down 50k         Test input pin bit 6 (1: Test mode)         Not used or connected to G           75         RESET         I         Schmitt O: System reset/input pin O: System reset (1: Test mode)         X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 64  | YO1             | 0          |             | Luminance signal output pin bit 1                                 | Х                            |