# **OKI** Semiconductor

This version: Jan. 1998 Previous version: Nov. 1996

# MSM7708-02

Serial Register Interface ADPCM CODEC for Telephone Recording

### GENERAL DESCRIPTION

The MSM7708-02 is a CMOS IC developed for applying to PHS (Personal Handyphone System). This device provides a CODEC function which performs transcoding between the voice band analog signal and 32 kbps ADPCM data. It also provides a serial register interface function for telephone call recording.

Provided with such functions as DTMF tone and several kinds of tone generation, transmit/receive data mute and gain control, side-tone pass, and voice/silence detection, the MSM7708-02 is best suited for PHS handsets.

### **FEATURES**

- Single 3 V power supply operation (V<sub>DD</sub>: 2.7 V to 3.6 V)

- Low power consumption When system is operating: 6 mA typ.

When powered down: 0.02 mA typ.

# (ADPCM CODEC)

- ADPCM: ITU-T Recommendations G.721 (32 kbps)

- Transmit/receive full duplex capability

- PCM interface code format: μ-law or A-law selectable

- Serial ADPCM and PCM transmission rate: 64 kbps to 2,048 kbps

- Transmit/receive mute function; transmit/receive programmable gain setting

- Side tone generator (8-step level adjustment)

- Built-in DTMF tone, ringing tone, and various tone generators

- Built-in VOX function

### (Serial Register Interface)

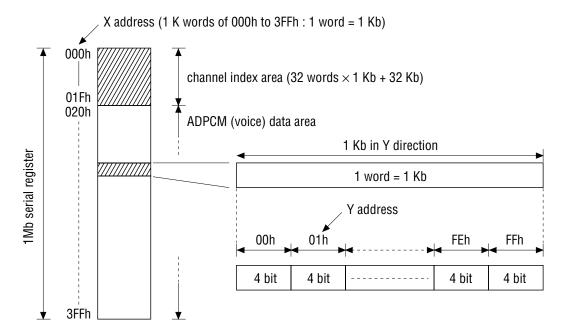

- Interface for a serial register: 1 Mb (MSM63V89C), 4 Mb (MSM6684), 8 Mb (MSM6685)

- Interface for a serial voice ROM: 1 Mb (MSM6595A), 2 Mb (MSM6596A), 3 Mb (MSM6597A)

- Maximum recording time: 32 s (1 Mb), 128 s (4 Mb), 256 s (8 Mb)

- Maximum recording channels: 32 ch

- Playback data transmit/receive selectable

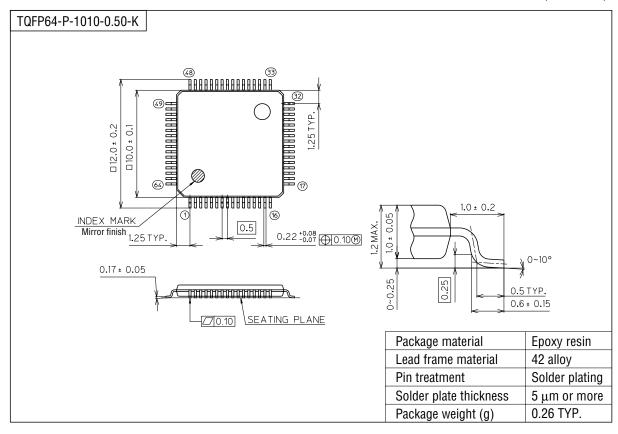

- Package:

64-pin plastic TQFP (TQFP64-P-1010-0.50-K) (Product name: MSM7708-02TS-K)

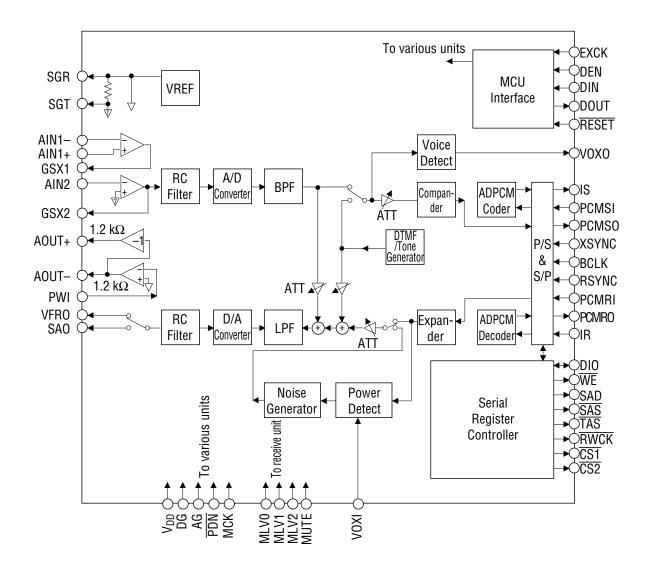

# **BLOCK DIAGRAM**

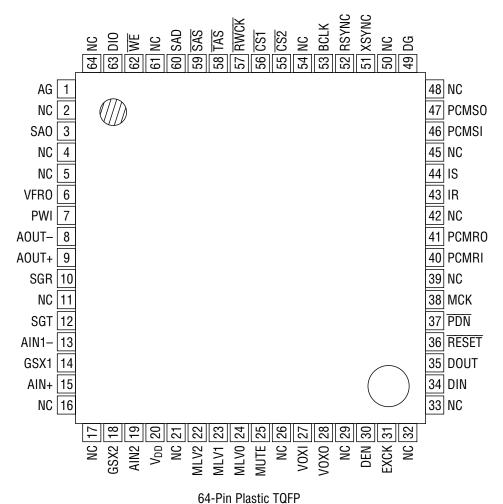

# **PIN CONFIGURATION (TOP VIEW)**

NC: No connect pin

# **PIN DESCRIPTIONS**

| Pin | Symbol          | Туре | Description                                        |

|-----|-----------------|------|----------------------------------------------------|

| 1   | AG              | I    | Analog ground                                      |

| 2   | NC              | _    | No connection                                      |

| 3   | SAO             | 0    | Receive side sounder amplifier output              |

| 4   | NC              | _    | No connection                                      |

| 5   | NC              | _    | No connection                                      |

| 6   | VFR0            | 0    | Receive side voice output                          |

| 7   | PWI             | I    | Receive side voice amplifier input                 |

| 8   | AOUT-           | 0    | Receive side voice amplifier output (–)            |

| 9   | AOUT+           | 0    | Receive side voice amplifier output (+)            |

| 10  | SGR             | 0    | Receive side analog signal ground                  |

| 11  | NC              | _    | No connection                                      |

| 12  | SGT             | 0    | Transmit side analog signal ground                 |

| 13  | AIN1-           | I    | Transmit side amplifier 1 inverting input          |

| 14  | GSX1            | 0    | Transmit side amplifier 1 output                   |

| 15  | AIN1+           | I    | Transmit side amplifier 1 non-inverting input      |

| 16  | NC              | _    | No connection                                      |

| 17  | NC              | _    | No connection                                      |

| 18  | GSX2            | 0    | Transmit side amplifier 2 output                   |

| 19  | AIN2            | I    | Transmit side amplifier 2 inverting input          |

| 20  | V <sub>DD</sub> | I    | Power supply                                       |

| 21  | NC              | _    | No connection                                      |

| 22  | MLV2            | I    | Receive side voice path mute level set             |

| 23  | MLV1            | I    | Receive side voice path mute level set             |

| 24  | MLV0            | I    | Receive side voice path mute level set             |

| 25  | MUTE            | I    | Receive side voice path mute enable signal input   |

| 26  | NC              |      | No connection                                      |

| 27  | VOXI            | l    | Receive side voice/silence detect function input   |

| 28  | VOXO            | 0    | Transmit side voice/silence detect function output |

| 29  | NC              | _    | No connection                                      |

| 30  | DEN             | I    | Enable signal input for control register           |

| 31  | EXCK            | I    | Clock signal input for control register            |

| 32  | NC              | _    | No connection                                      |

| 33  | NC              |      | No connection                                      |

| 34  | DIN             | I    | Address and data input for control                 |

| 35  | DOUT            | 0    | Data output for control register                   |

| 36  | RESET           | I    | RESET control input for control register           |

| 37  | PDN             | I    | Power down control input                           |

| 38  | MCK             | 1    | Master clock input                                 |

| 39  | NC              | _    | No connection                                      |

| 40  | PCMRI           | l    | Receive side PCM signal input                      |

# **PIN DESCRIPTIONS (Continued)**

| Pin | Symbol | Туре | Description                                        |

|-----|--------|------|----------------------------------------------------|

| 41  | PCMRO  | 0    | Receive side PCM signal output                     |

| 42  | NC     | _    | No connection                                      |

| 43  | IR     | ı    | Receive side ADPCM signal input                    |

| 44  | IS     | 0    | Transmit side ADPCM signal output                  |

| 45  | NC     | _    | No connection                                      |

| 46  | PCMSI  | I    | Transmit side PCM signal input                     |

| 47  | PCMSO  | 0    | Transmit side PCM signal output                    |

| 48  | NC     | _    | No connection                                      |

| 49  | DG     | I    | Digital ground                                     |

| 50  | NC     | _    | No connection                                      |

| 51  | XSYNC  | I    | Transmit side PCM and ADPCM data sync signal input |

| 52  | RSYNC  | I    | Receive side PCM and ADPCM data sync signal input  |

| 53  | BCLK   | I    | PCM and ADPCM data shift clock input               |

| 54  | NC     | _    | No connection                                      |

| 55  | CS2    | 0    | Voice ROM chip select output                       |

| 56  | CS1    | 0    | Serial register chip select output                 |

| 57  | RWCK   | 0    | Serial register data clock output                  |

| 58  | TAS    | 0    | Serial register transfer address-strobe output     |

| 59  | SAS    | 0    | Serial register address-strobe output              |

| 60  | SAD    | 0    | Serial register address data output                |

| 61  | NC     | _    | No connection                                      |

| 62  | WE     | 0    | Serial register write enable output                |

| 63  | DIO    | 1/0  | Serial register data input/output                  |

| 64  | NC     |      | No connection                                      |

# PIN AND FUNCTIONAL DESCRIPTIONS

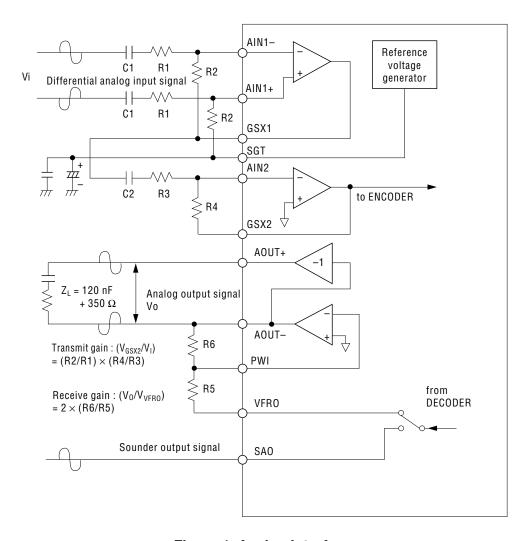

# AIN1+, AIN1-, AIN2, GSX1, GSX2

The transmit analog input and the output for transmit gain adjustment.

The pin AIN1– (AIN2) connects to inverting input of the internal transmit amplifier, and the pin AIN1+ connects to non-inverting input of the internal transmit amplifier. The pin GSX1 (GSX2) connects to output of the internal transmit amplifier. Gain adjustment should be referred to Fig. 1.

# VFRO, AOUT+, AOUT-, PWI

Used for the receive analog output and the output for receive gain adjustment.

VFRO is an output of the receive filter. AOUT+ and AOUT- are differential analog signal outputs which can directly drive  $Z_L$  = 350  $\Omega$ +120 nF or the 1.2 k $\Omega$  load. Gain adjustment should be referred to Fig. 1.

These outputs are in high impedance state during power down.

# **SAO**

Differential analog output for a sounder.

Variable tones including "Audio sound", "DTMF tone", "S tone", "F tone", and "R tone", and telephone call signals can be output to either VFRO pin or SAO pin by CR0 - B1 of the control register. These output pins are in the high impedance state during power down.

Figure 1 Analog Interface

### SGT, SGR

Outputs of the analog signal ground voltage.

SGT outputs the analog signal ground voltage of the transmit system, and SGR outputs the same for the receive system. The output voltage value is approximately 1.4 V. Connect bypass  $10\,\mu\text{F}$  and  $0.1\,\mu\text{F}$  (ceramic type) capacitors between these pins and the AG pin. To reduce the response time of the receiver power on, it is recommended to apply  $1\,\mu\text{F}$  and  $0.1\,\mu\text{F}$  bypass capacitors. During power down, the output changes to  $0\,\text{V}$ .

# $V_{DD}$

Power supply.

# DG, AG

Ground.

DG is the digital system ground. AG is the analog system ground. Since DG and AG are separated in the device, connect them as close as possible on the circuit board.

# **PDN**

Power down control input.

When set to a digital "0", the system changes to the power down state and control register is not reset. Since the power down mode is controlled by CRC0 - B5 of the control register ORed with the signal from the  $\overline{PDN}$  pin, set CRC0 - B5 to digital "0" when using this pin.

### RESET

Reset control input of the CODEC control register.

When set to digital "0," each bit of the control register is reset and the internal circuit changes to the power down state. During normal operation, set this pin to digital "1".

### **MCK**

Master clock input.

The clock frequency is 19.2 MHz. MCK can be asynchronous with XSYNC, RSYNC, and BCLK.

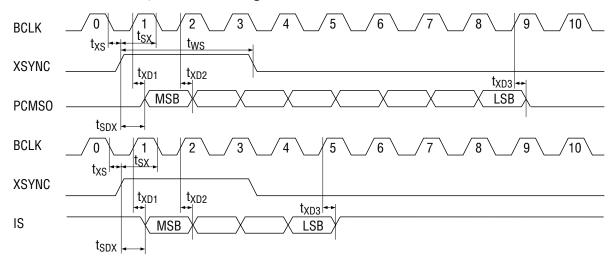

# **PCMSO**

Transmit PCM data output.

This PCM output signal is output from MSB synchronously with the rising edge of BCLK and XSYNC.

### **PCMSI**

Transmit PCM data input.

This signal is converted to the ADPCM data. The PCM signal is shifted in on the falling edge of BCLK. Normally, this pin is connected to PCMSO.

### **PCMRO**

Receive PCM data output.

This PCM signal is the output signal after ADPCM decoder processing. This signal is serially output from MSB synchronously with the rising edge of BCLK and RSYNC.

### **PCMRI**

Receive PCM data input.

This PCM input signal is shifted in on the rising edge of BCLK and is input from MSB. Normally, this pin is connected to PCMRO.

### IS

Transmit ADPCM signal output.

This signal is the output signal after ADPCM encoding, and is serially output from MSB synchronously with the rising edge of BCLK and XSYNC. This pin is an open drain output which remains in a high impedence state during power down. It requires pull-up resistor.

### IR

Receive ADPCM signal input.

This input signal is shifted in serially on the rising edge of BCLK synchronously with RSYNC and is input from MSB.

### **BCLK**

Shift clock input for the PCM data (PCMSO, PCMSI, PCMRO, PCMRI) and the ADPCM data(IS, IR). The frequency is in the 64 kHz to 2048 kHz range.

# **XSYNC**

8 kHz synchronous signal input for transmit PCM and ADPCM data.

This signal should be synchronized with BCLK. XSYNC is used for indicating the MSB of the transmit serial PCM and ADPCM data stream.

### **RSYNC**

8 kHz synchronous signal input for receive PCM and ADPCM data.

This signal should be synchronized with BCLK signal. RSYNC is used for indicating the MSB of the receive serial PCM and ADPCM data stream.

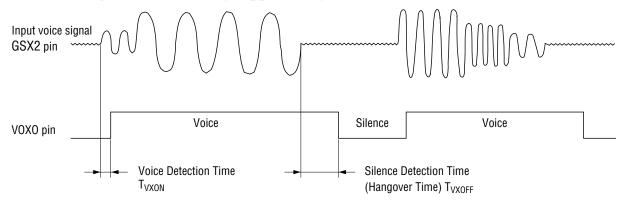

### VOXO

Transmit side voice/silence detect signal output.

This output is valid when CR6 - B7 is set to "1". VOXO shows the presence or absence of the transmit voice signal by detecting the signal. "1" and "0" set to this pin correspond to the presence and the absence, respectively. This result also appears at the register data CR7 - B7. The signal detect threshold is set by the control register CR6 - B6, B5. When control register CR0 - B6 is set to "1" and VOXI input is "1" during the voice detection (VOXO = "1"), receive signal is automatically suppressed by 6 dB.

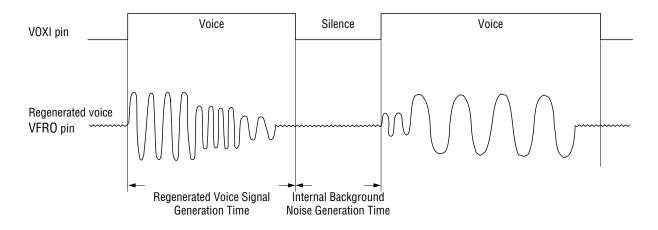

### VOXI

Receive side voice/silence detect signal input.

This output is valid when CR6 - B7 is set to "1". A "1" level at VOXI indicates the presence of voice signal, in which case the decoder block processes normal receive signal and the voice signal appears at analog output pins. A "0" level indicates the absence of voice signal, in which case the background noise generated in this device is transferred to the analog output pins. The background noise amplitude is set by the control register CR6 - B1, B0. Since this signal is ORed with the register CR6 - B3, set the control register CR6 - B3 to "0" when using this pin. When control register CR0 - B6 is set to "1" and VOXI input is "1" during the voice detection (VOXO = "1") receive signal is automatically suppressed by 6 dB.

(a) Transmission Side Voice/Silence Detect Function Timing Diagram

(b) Receive Side Voice/Silence Detect Function Timing Diagram

Note: The VOXO and VOXI pin functions are enabled when CR6 - B7 is set to "1".

Figure 2 Voice/Silence Detect Function

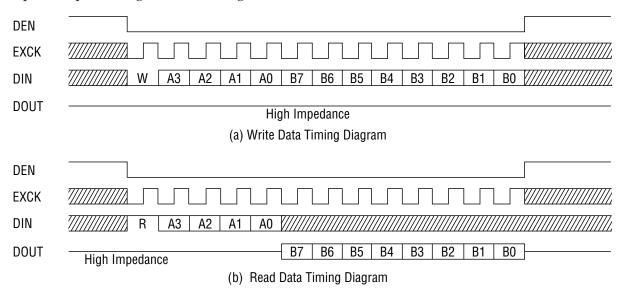

### DEN, EXCK, DIN, DOUT

Serial control ports for MCU interface.

Reading and writing data is performed by an external CPU through these pins. 14-byte control registers (CR0 - 13) are provided in this device.

DEN is the "Enable" control signal input, EXCK is the data shift clock input, DIN is the address and data input, and DOUT is the data output.

Input/output timing is shown in Fig. 3.

Figure 3 MCU Interface Input/Output Timing

# **MUTE**

This pin is used to enable the receive side voice path mute level. To set the mute level, set this pin to "1".

# MLV0, MLV1, MLV2

This pin is used to set the receive side voice path mute level.

For the control method, refer to the control register description (CR1). Since these signals are ORed with CR1 - B2, B1, and B0 internally, set these register data to "0" when using this pin.

The register map is shown in Table 1.

Table 1 Control Register (CR0 to CR13) Map

| Register Address |   |           |            | ;  |                     | Data Description   |                    |                |               |                       |                  |                  |     |  |

|------------------|---|-----------|------------|----|---------------------|--------------------|--------------------|----------------|---------------|-----------------------|------------------|------------------|-----|--|

| Name             |   | <b>A2</b> | <b>A</b> 1 | Α0 | В7                  | В6                 | B5                 | B4             | В3            | B2                    | B1               | В0               | R/W |  |

| CR0              | 0 | 0         | 0          | 0  | A/μ<br>SEL          | Spprs<br>ON        | PDN<br>ALL         | PDN<br>TX      | PDN<br>RX     | SA,VF<br>OUT          | SAO/<br>VFRO     | AOUT<br>PON      | R/W |  |

| CR1              | 0 | 0         | 0          | 1  | TX<br>MUTE          | RX<br>ON/OFF       | ADPCM<br>RESET     | TX<br>ON/OFF   | RX<br>MUTE    | RX<br>MLV2            | RX<br>MLV1       | RX<br>MLV0       | R/W |  |

| CR2              | 0 | 0         | 1          | 0  | TX<br>GAIN3         | TX<br>GAIN2        | TX<br>GAIN1        | TX<br>GAIN0    | RX<br>GAIN3   | RX<br>GAIN2           | RX<br>GAIN1      | RX<br>GAIN0      | R/W |  |

| CR3              | 0 | 0         | 1          | 1  | Side Tone<br>GAIN2  | Side Tone<br>GAIN1 | Side Tone<br>GAINO | TONE<br>ON/OFF | TONE<br>GAIN3 | TONE<br>GAIN2         | TONE<br>GAIN1    | TONE<br>GAINO    | R/W |  |

| CR4              | 0 | 1         | 0          | 0  | DTMF/<br>OTHERS SEL | TONE<br>SEND       | TONE5              | TONE4          | TONE3         | TONE2                 | TONE1            | TONEO            | R/W |  |

| CR5              | 0 | 1         | 0          | 1  | SEND/<br>REC        | ROW/<br>SR         | 4M8M/<br>1M        | _              | _             | _                     | CMD1             | CMD0             | R/W |  |

| CR6              | 0 | 1         | 1          | 0  | VOX<br>ON/OFF       | ON<br>LVL1         | ON<br>LVL0         | OFF<br>TIME    | VOX<br>IN     | RX NOISE<br>LEVEL SEL | RX NOISE<br>LVL1 | RX NOISE<br>LVL0 | R/W |  |

| CR7              | 0 | 1         | 1          | 1  | VOX<br>OUT          | SILENCE<br>LVL1    | SILENCE<br>LVL0    | _              |               | _                     | BUSY             | RPM              | R   |  |

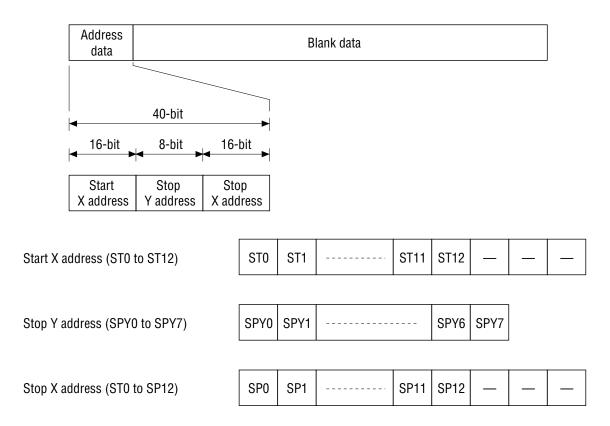

| CR8              | 1 | 0         | 0          | 0  | ST0                 | ST1                | ST2                | ST3            | ST4           | ST5                   | ST6              | ST7              | R/W |  |

| CR9              | 1 | 0         | 0          | 1  | ST8                 | ST9                | ST10               | ST11           | ST12          | _                     | _                | _                | R/W |  |

| CR10             | 1 | 0         | 1          | 0  | SPY0                | SPY1               | SPY2               | SPY3           | SPY4          | SPY5                  | SPY6             | SPY7             | R/W |  |

| CR11             | 1 | 0         | 1          | 1  | SP0                 | SP1                | SP2                | SP3            | SP4           | SP5                   | SP6              | SP7              | R/W |  |

| CR12             | 1 | 1         | 0          | 0  | SP8                 | SP9                | SP10               | SP11           | SP12          | _                     | _                | _                | R/W |  |

| CR13             | 1 | 1         | 0          | 1  | СНО                 | CH1                | CH2                | CH3            | CH4           |                       | ADRD             | ADWT             | R/W |  |

Note: Details are explained in the Control Register Description.

R/W: Both read and write are supported R: Read-only register

### (Register Controllers)

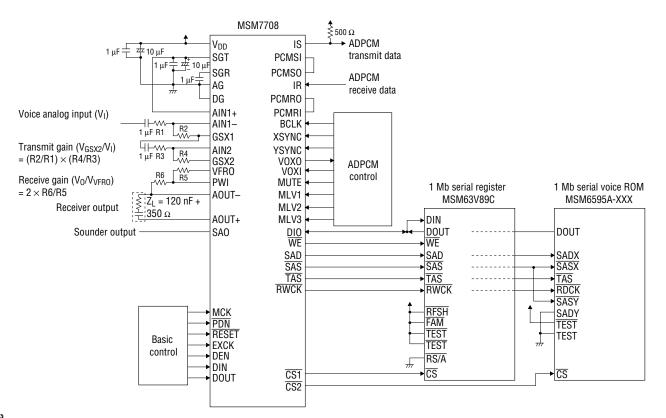

### DIO

This I/O pin is used to output the write data and fetch the read data.

Connect this pin to the DIN and DOUT pins of the serial register and to the DOUT pin of the serial voice ROM.

### WE

This output pin is used to select the read or write mode.

Connect this pin to the  $\overline{WE}$  pin of the serial register.

### SAD

This pin is used to output the read/write start address data.

Connect this pin to the SAD pin of the serial register and to the SADX pin of the serial voice ROM.

# SAS

This clock output pin is used to write the serial address.

Connect this pin to the  $\overline{SAS}$  pin of the serial register and to the  $\overline{SASX}$  and  $\overline{SASY}$  pins of the serial voice ROM.

# **TAS**

This output pin is used to set the serial address input from the SAD pin into the address counter inside the serial register/serial voice ROM.

Connect this pin to the  $\overline{TAS}$  pin of the serial register/serial voice ROM.

### **RWCK**

This clock output pin is used to write or read data to or from the serial register.

Connect this pin to the  $\overline{RWCK}$  pin of the serial register and to the  $\overline{RDCK}$  pin of the serial voice ROM.

# CS1, CS2

CS1 and CS2 are chip select pins.

Connect  $\overline{CS1}$  to the  $\overline{CS}$  pin of the serial register, and  $\overline{CS2}$  to the  $\overline{CS}$  pin of the serial voice ROM.

# **ABSOLUTE MAXIMUM RATINGS**

| Parameter             | Symbol           | Condition    | Rating                        | Unit |

|-----------------------|------------------|--------------|-------------------------------|------|

| Power Supply Voltage  | V <sub>DD</sub>  | <del>-</del> | -0.3 to +5                    | V    |

| Analog Input Voltage  | V <sub>AIN</sub> | _            | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Digital Input Voltage | V <sub>DIN</sub> | _            | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Operating Temperature | T <sub>op</sub>  | <del>_</del> | -25 to +70                    | °C   |

| Storage Temperature   | T <sub>STG</sub> | _            | -55 to +150                   | °C   |

# RECOMMENDED OPERATING CONDITIONS

| Parameter                        | Symbol            | Condition                 | (- DL | Min.                 | Тур. | Max.                 | Unit |

|----------------------------------|-------------------|---------------------------|-------|----------------------|------|----------------------|------|

| Power Supply Voltage             | $V_{DD}$          | Voltage must be fixed     |       | 2.7                  | _    | 3.6                  | ٧    |

| High Level Input Voltage         | V <sub>IH</sub>   | To all digital input pin  | S     | $0.45 \times V_{DD}$ | _    | Vdd                  | V    |

| Low Level Input Voltage          | V <sub>IL</sub>   | To all digital input pin  | S     | 0                    | _    | $0.16 \times V_{DD}$ | V    |

| Digital Input Rise Time          | t <sub>lr</sub>   | To all digital input pin  | S     |                      | _    | 50                   | ns   |

| Digital Input Fall Time          | t <sub>lf</sub>   | To all digital input pins |       |                      | _    | 50                   | ns   |

| Digital Output Load              | $R_{DL}$          | IS (Pull-up resistor)     |       | 500                  | _    |                      | Ω    |

| Digital Output Load              | $C_{DL}$          | To all digital output p   | _     | _                    | 100  | pF                   |      |

| Bypass Capacitor for SG          | C <sub>SGT</sub>  | Between SGT and AG        |       | 10 + 0.1             | _    | _                    | μF   |

| bypass capacitor for SG          | C <sub>SGR</sub>  | Between SGR and AG        | 1     | _                    | _    | μF                   |      |

| Master Clock Frequency           | F <sub>MCK</sub>  | MCK                       |       | -0.01%               | 19.2 | 0.01%                | MHz  |

| Master Clock Duty Ratio          | D <sub>MCK</sub>  | MCK                       |       | 40                   | 50   | 60                   | %    |

| Bit Clock Frequency              | F <sub>BCK</sub>  | BCLK                      |       | 64                   | _    | 2048                 | kHz  |

| Synchronous Signal Frequency     | F <sub>SYNC</sub> | XSYNC, RSYNC              |       | _                    | 8.0  | _                    | kHz  |

| Clock Duty Ratio                 | D <sub>CK</sub>   | BCLK, EXCK                |       | 40                   | 50   | 60                   | %    |

| Transmit Sync Pulse Setting Time | $t_{XS,}t_{SX}$   | BCLK↔XSYNC                |       | 100                  | _    | _                    | ns   |

| Receive Sync Pulse Setting Time  | $t_{RS,}t_{SR}$   | BCLK↔RSYNC                |       | 100                  | _    | _                    | ns   |

| Synchronous Signal Width         | t <sub>WS</sub>   | XSYNC, RSYNC Fig.4        |       | 1 BCLK               | _    | 100                  | μS   |

| PCM, ADPCM Setup Time            | t <sub>DS</sub>   | _                         |       | 100                  | _    | _                    | ns   |

| PCM, ADPCM Hold Time             | t <sub>DH</sub>   | _                         |       | 100                  | _    |                      | ns   |

# **ELECTRICAL CHARACTERISTICS**

# **DC Characteristics**

| Parameter                 | Symbol           | Condition                                                                      | Min.                | Тур. | Max.     | Unit |

|---------------------------|------------------|--------------------------------------------------------------------------------|---------------------|------|----------|------|

|                           | I <sub>DD1</sub> | When operating<br>(When no signal, and V <sub>DD</sub> = 3.0 V)                | _                   | 6.0  | 11.0     | mA   |

| Power Supply Current      | I <sub>DD2</sub> | When powered down (When V <sub>DD</sub> = 3.0 V)                               | _                   | 0.02 | 0.1      | mA   |

| Input Leakage Current     | I <sub>IH</sub>  | $V_I = V_{DD}$                                                                 | _                   | _    | 2.0      | μΑ   |

|                           | Ι <sub>Ι</sub> _ | V <sub>I</sub> = 0 V                                                           |                     | _    | 0.5      | μΑ   |

| High Level Output Voltage | V <sub>OH1</sub> | I <sub>OH</sub> = 0.4 mA                                                       | $0.5 \times V_{DD}$ | _    | $V_{DD}$ | V    |

|                           | V <sub>OH2</sub> | I <sub>OH</sub> = 1 μA                                                         | $0.8 \times V_{DD}$ |      | $V_{DD}$ | V    |

| Low Level Output Voltage  | V <sub>OL</sub>  | $I_{OL} = -1.2 \text{ mA}$<br>(IS pin is pulled up with 500 $\Omega$ resistor) | 0                   | 0.2  | 0.4      | V    |

| Output Leakage Current    | I <sub>0</sub>   | IS pin                                                                         | _                   |      | 10       | μА   |

| Input Capacitance         | C <sub>IN</sub>  | _                                                                              | _                   | 5    | _        | pF   |

# **Analog Interface Characteristics**

$(V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}, Ta = -25^{\circ}\text{C to } +70^{\circ}\text{C})$

| Parameter                 | Symbol           | Condition                                           | Min.        | Тур. | Max. | Unit            |

|---------------------------|------------------|-----------------------------------------------------|-------------|------|------|-----------------|

| Input Resistance          | R <sub>IN</sub>  | AIN+, AIN-, AIN2, PWI                               | 10          |      | _    | MΩ              |

| Output Desistence Load    | R <sub>L1</sub>  | GSX1, GSX2, VFR0, SA0                               | 20          | _    | _    | kΩ              |

| Output Resistance Load    | R <sub>L2</sub>  | AOUT+, AOUT-                                        | 1.2         | _    | _    | kΩ              |

| Output Capacitance Load   | C <sub>L1</sub>  | GSX1, GSX2, VFR0, SA0                               | _           | _    | 100  | pF              |

|                           | $C_{L2}$         | AOUT+, AOUT-                                        | _           | _    | 100  | pF              |

|                           | V <sub>01</sub>  | GSX1, GSX2, VFR0, SA0( $R_L = 20 \text{ k}\Omega$ ) | _           |      | 1.3  | V <sub>PP</sub> |

| Output Voltage Level (*1) | V <sub>02</sub>  | AOUT+, AOUT– $(R_L = 1.2 \text{ k}\Omega)$          | _           | _    | 1.3  | V <sub>PP</sub> |

|                           | V <sub>OF1</sub> | VFRO, SAO                                           | -100        | _    | +100 | mV              |

| Offset Voltage            | V <sub>OF2</sub> | GSX1, GSX2, AOUT+, AOUT-                            | -20         | _    | +20  | mV              |

| SGT, SGR Output Voltage   | $V_{SG}$         | SGT, SGR                                            | <del></del> | 1.4  | _    | V               |

| SGT Output Impedance      | R <sub>SGT</sub> | SGT                                                 |             | 40   | 80   | kΩ              |

| SGR Output Impedance      | R <sub>SGR</sub> | SGR                                                 |             | 8    | 12   | kΩ              |

<sup>\*1</sup>  $-7.7 \text{ dBm } (600 \Omega) = 0 \text{ dBm0}, +3.14 \text{ dBm0} = 1.30 \text{ V}_{PP}.$

# **Digital Interface Characteristics**

| Parameter                 | Symbol                              | Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Reference | Min. | Тур. | Max.      | Unit |

|---------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|------|-----------|------|

|                           | t <sub>SDX</sub> , t <sub>SDR</sub> | 1 LSTTL + 100 pF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           | 0    |      | 200 (100) | ns   |

| Digital Output Delay Time | $t_{XD1,}t_{RD1}$                   | mean C load = 10 pF, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Eig 4     | 0    |      | 200 (100) | ns   |

| PCM, ADPCM Interface      | $t_{XD2,}t_{RD2}$                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Fig. 4    | 0    |      | 200 (100) | ns   |

|                           | $t_{XD3}, t_{RD3}$                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           | 0    |      | 200 (100) | ns   |

|                           | t <sub>1</sub>                      | - гр гр. |           | 50   |      | _         | ns   |

|                           | t <sub>2</sub>                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           | 50   | _    | _         | ns   |

|                           | t <sub>3</sub>                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Fig. 5    | 50   |      | _         | ns   |

|                           | t <sub>4</sub>                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           | 50   |      | _         | ns   |

|                           | $t_5$                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           | 100  |      | _         | ns   |

| Serial Port Digital I/O   | t <sub>6</sub>                      | Cloud FO nE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           | 50   | _    | _         | ns   |

| Timing Characteristics    | t <sub>7</sub>                      | C load = 50 pF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           | 50   |      | _         | ns   |

|                           | t <sub>8</sub>                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           | 0    |      | 100       | ns   |

|                           | t <sub>9</sub>                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           | 50   |      | _         | ns   |

|                           | t <sub>10</sub>                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           | 50   |      | _         | ns   |

|                           | t <sub>11</sub>                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           | 0    |      | 50        | ns   |

|                           | t <sub>12</sub>                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           | 200  |      | _         | ns   |

| EXCK Clock Frequency      | F <sub>EXCK</sub>                   | EXCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _         | _    |      | 10        | MHz  |

# **Serial Register Interface Characteristics**

| Parameter                   | Symbol           | Condition                    | Reference | Min. | Тур. | Max. | Unit |

|-----------------------------|------------------|------------------------------|-----------|------|------|------|------|

| Control Degister Deta Input | t <sub>CRW</sub> | Write                        |           | _    | _    | 200  | ns   |

| Control Register Data Input | t <sub>CRR</sub> | Reset                        |           | _    | _    | 200  | ns   |

| D D:4                       | t <sub>BSR</sub> | Setup time                   | Fig. 6    | _    | _    | 10   | μs   |

| Busy Bit                    | t <sub>BSH</sub> | Valid time                   | ] rig. 0  | _    | _    | 450  | μs   |

|                             | t <sub>RPR</sub> | Setup time                   |           | _    | _    | 15   | μs   |

| RPM Bit                     | t <sub>RPF</sub> | Hold time after stop command |           | _    | _    | 140  | μs   |

# **AC Characteristics**

| Parameter             | Cumhal              | Cond           | lition      | N.A.  | T         | Mary  | 11   |

|-----------------------|---------------------|----------------|-------------|-------|-----------|-------|------|

| Parameter             | Symbol              | Frequency (Hz) | Level dBm0  | Min.  | Тур.      | Max.  | Unit |

|                       | L <sub>OSS</sub> T1 | 0 to 60        |             | 25    | _         | _     | dB   |

|                       | L <sub>OSS</sub> T2 | 300 to 3000    |             | -0.15 | _         | +0.20 | dB   |

| Transmit Frequency    | L <sub>OSS</sub> T3 | 1020           | 0           |       | Reference |       | dB   |

| Response              | L <sub>OSS</sub> T4 | 3300           |             | -0.15 | _         | +0.80 | dB   |

|                       | L <sub>OSS</sub> T5 | 3400           |             | 0     | _         | 0.80  | dB   |

|                       | L <sub>OSS</sub> T6 | 3968.75        |             | 13    | _         | _     | dB   |

|                       | L <sub>OSS</sub> R1 | 0 to 3000      |             | -0.15 | _         | +0.20 | dB   |

| Receive Frequency     | L <sub>OSS</sub> R2 | 1020           |             |       | Reference |       | dB   |

|                       | L <sub>OSS</sub> R3 | 3300           | 0           | -0.15 | _         | +0.80 | dB   |

| Response              | L <sub>OSS</sub> R4 | 3400           |             | 0     | _         | 0.80  | dB   |

|                       | L <sub>OSS</sub> R5 | 3968.75        |             | 13    | _         | _     | dB   |

|                       | SD T1               |                | 3           | 35    | _         | _     | dB   |

| T ".O"                | SD T2               | 1020           | 0           | 35    | _         | _     | dB   |

| Transmit Signal to    | SD T3               |                | -30         | 35    | _         | _     | dB   |

| Distortion Ratio (*1) | SD T4               |                | -40         | 28    | _         | _     | dB   |

|                       | SD T5               |                | <b>-45</b>  | 23    | _         | _     | dB   |

|                       | SD R1               |                | 3           | 35    | _         | _     | dB   |

| Danahar Olamakta      | SD R2               | ,              | 0           | 35    | _         | _     | dB   |

| Receive Signal to     | SD R3               | 1020           | -30         | 35    | _         | _     | dB   |

| Distortion Ratio (*1) | SD R4               | ,              | -40         | 28    | _         | _     | dB   |

|                       | SD R5               |                | <b>–45</b>  | 23    | _         | _     | dB   |

|                       | GT T1               |                | 3           | -0.2  | _         | +0.2  | dB   |

| Turn and the Order    | GT T2               |                | -10         |       | Reference |       | dB   |

| Transmit Gain         | GT T3               | 1020           | -40         | -0.2  | _         | +0.2  | dB   |

| Tracking              | GT T4               | ,              | -50         | -0.5  | _         | +0.5  | dB   |

|                       | GT T5               |                | <b>-</b> 55 | -1.2  | _         | +1.2  | dB   |

|                       | GT R1               |                | 3           | -0.2  | _         | +0.2  | dB   |

| Danatina O. i         | GT R2               |                | -10         |       | Reference |       | dB   |

| Receive Gain          | GT R3               | 1020           | -40         | -0.2  | _         | +0.2  | dB   |

| Tracking              | GT R4               |                | -50         | -0.5  | _         | +0.5  | dB   |

|                       | GT R5               |                | <b>–</b> 55 | -1.2  | _         | +1.2  | dB   |

<sup>\*1</sup> P-message filter used

# AC Characteristics (Continued)

$(V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}, \text{ Ta} = -25^{\circ}\text{C to } +70^{\circ}\text{C})$

| Parameter                  | Cumbal            | C                | Min.         | Turn  | Max.     | Unit  |         |        |

|----------------------------|-------------------|------------------|--------------|-------|----------|-------|---------|--------|

| Parameter                  | Symbol            | Frequency (Hz)   | Level dBm0   | Other | IVIII 1. | Тур.  | IVIAX.  | Onit   |

| Idle Channel Noise<br>(*1) | N                 |                  | AIN CC       |       |          |       | -68     |        |

|                            | N <sub>IDLT</sub> | _                | AIN = SG     | _     |          |       | (-75.7) | dBm0p  |

|                            | N <sub>IDLR</sub> |                  | (*2)         | _     | -        | _     | -72     | (dBmp) |

|                            |                   |                  |              |       |          |       | (-79.7) |        |

| Abaqluta Laval (*2)        | A <sub>VT</sub>   | 1020             | 0            | GSX2  | 0.285    | 0.320 | 0.359   | Vrms   |

| Absolute Level (*3)        | A <sub>VR</sub>   | 1020             |              | VFR0  | 0.285    | 0.320 | 0.359   | Vrms   |

| Power Supply Noise         | P <sub>SRRT</sub> | Noise frequency: | Noise level: |       | 30       | _     |         | dB     |

| Rejection Ratio            | P <sub>SRRR</sub> | 0 to 50 kHz      | 50 mVpp      |       | 30       | _     | _       | dB     |

<sup>\*1</sup> P-message filter used

ADPCM unit characteristics are fully compliant with ITU-T Recommendation G.721.

# **AC Characteristics (DTMF and Other Tones)**

$(V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}, \text{ Ta} = -25^{\circ}\text{C to } +70^{\circ}\text{C})$

| Parameter                      | Symbol            | C                                                                   | Condition                                     | Min. | Тур. | Max. | Unit |

|--------------------------------|-------------------|---------------------------------------------------------------------|-----------------------------------------------|------|------|------|------|

| Fraguanay Daviation            | D <sub>FT1</sub>  | DTMF tones, Oth                                                     | -1.5                                          |      | +1.5 | %    |      |

| Frequency Deviation            | D <sub>FT2</sub>  | Tone scale                                                          | -1.0                                          | _    | +1.0 | %    |      |

| Tone Reference                 | $V_{TL}$          | Transmit side tone                                                  | DTMF (low group)                              | -18  | -16  | -14  | dBm0 |

|                                | $V_{TH}$          | (Gain setting 0 dB)                                                 | DTMF (high group), other                      | -16  | -14  | -12  | dBm0 |

| Output Level                   | $V_{RL}$          | Receive side tone                                                   | DTMF (low group)                              | -10  | -8   | -6   | dBm0 |

| (*1)                           | $V_{RH}$          | (Gain setting –6 dB)                                                | (Gain setting –6 dB) DTMF (high group), other |      | -6   | -4   | dBm0 |

| DTMF Tone Level Relative Value | R <sub>DTMF</sub> | V <sub>TH</sub> /V <sub>TL</sub> , V <sub>RH</sub> /V <sub>RI</sub> | L                                             | 1    | 2    | 3    | dB   |

<sup>\*1.</sup> Not including programmable gain set values

# **AC Characteristics (Gain Settings)**

$(V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}, Ta = -25^{\circ}\text{C to } +70^{\circ}\text{C})$

|                       |                | ( 55                      |      | ,    |      |      |

|-----------------------|----------------|---------------------------|------|------|------|------|

| Parameter             | Symbol         | Condition                 | Min. | Тур. | Max. | Unit |

| Transmit/Receive Gain | D <sub>G</sub> | For all gain set values   | _1   | 0    | .1   | dB   |

| Setting Accuracy      | DG             | i oi ali yalii set values |      | U    | T1   | ub   |

# **AC Characteristics (Voice/Silence Detect Function)**

| Parameter                                  | Symbol            |                 | Condition                            | Min.    | Тур.    | Max.    | Unit |

|--------------------------------------------|-------------------|-----------------|--------------------------------------|---------|---------|---------|------|

| Transmit Voice/Silence                     | T <sub>VXON</sub> | Silence→voice   | VOXO pin: See Fig. 2                 | _       | 5       | _       | ms   |

| Detection Time                             | T <sub>VXOF</sub> | Voice→silence   | Voice/silence<br>differential: 10 dB | 140/300 | 160/320 | 180/340 | ms   |

| Transmit Voice<br>Detection Level Accuracy | D <sub>VX</sub>   | For detection I | evel set values by                   | -2.5    | 0       | 2.5     | dB   |

<sup>\*2</sup> PCMRI input: "11010101" (A-law), "111111111" (μ-law)

<sup>\*3</sup>  $0.320 \text{ Vrms} = 0 \text{ dBm0} = -7.7 \text{ dBm } (600 \Omega)$

# **TIMING DIAGRAM**

# **Transmit Side PCM, ADPCM Timing**

# Receive Side PCM, ADPCM Timing

Figure 4 PCM, ADPCM Interface

# **Serial Port Timing for Microcontroller Interface**

Figure 5 Serial Control Port Interface

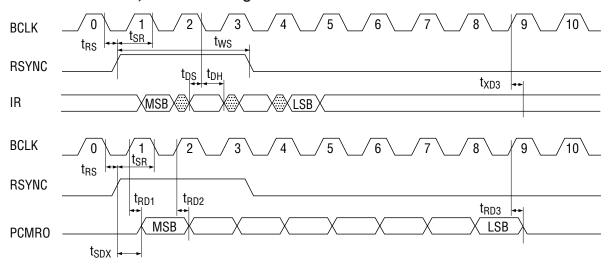

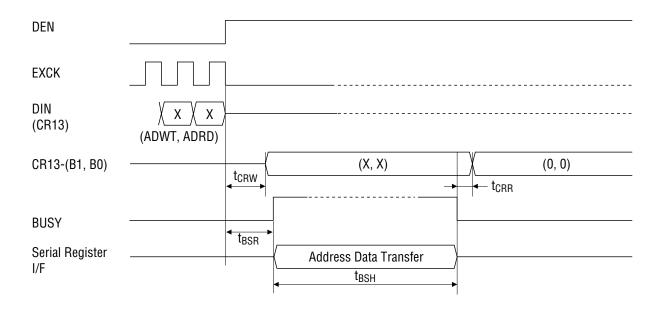

# **Address Write/Read Mode Timing**

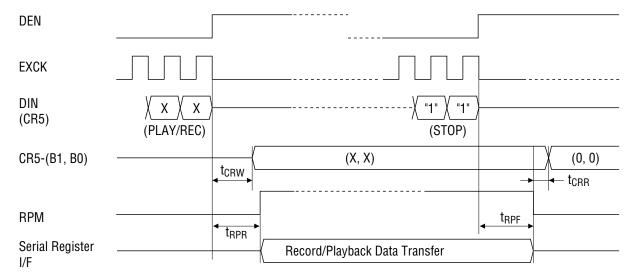

# **Record/Playback Mode Timing**

Figure 6 Serial Register Interface

# **FUNCTIONAL DESCRIPTION**

# **Control Register Description**

# (1) CR0 (Basic Operation Mode Settings)

|               | В7  | В6 | B5  | B4  | В3  | B2     | B1   | В0   |

|---------------|-----|----|-----|-----|-----|--------|------|------|

| CR0           | A/μ |    | PDN | PDN | PDN | SA, VF | SAO/ | AOUT |

| UNU           | SEL |    | ALL | TX  | RX  | OUT    | VFR0 | PON  |

| Initial value | 0   | 0  | 0   | 0   | 0   | 0      | 0    | 0    |

B7: ......PCM interface companding law selection 0: μ-law1: A-law

B6: ...... Automatic suppression function control 0: suppression off

1: suppression on

When transmit voice is detected, receive level is suppressed automatically by 6 dB.

B5: ...............Power down (entire unit) 0: Power ON 1: Power down ORed with the inverted external power down signal. When using this data, set  $\overline{PDN}$  to "1".

B3: ......Power down (receive side only) 0: Power ON 1: Power down B2: ......The sounder output amp (SAO) and receiver system output amp

(VFRO) operation control0: The output pin selected by CR0 - B1 operates.

1: The sounder system output (SAO) and receiver system output (VFRO) both operate.

B1: ......Selection of sounder system output (SAO) or receiver system output

0: VFRO 1: SAO

SGR potential is output to the non selected pin.

B0: ..... AOUT+, AOUT- power on control

0: AOUT+, – power down

1: AOUT+, – power on

# (2) CR1 (ADPCM Operation Mode Settings)

|               | В7   | В6     | B5    | B4     | В3   | B2   | B1   | В0   |

|---------------|------|--------|-------|--------|------|------|------|------|

| 004           | TX   | RX     | ADPCM | TX     | RX   | RX   | RX   | RX   |

| CR1           | MUTE | ON/OFF | RESET | ON/OFF | MUTE | MLV2 | MLV1 | MLV0 |

| Initial value | 0    | 0      | 0     | 0      | 0    | 0    | 0    | 0    |

B7: ..... Transmit side ADPCM data MUTE

1: MUTE

B6: ..... Receive side PCM signal ON/OFF

0: ON

1: OFF

B5: ......Transmit/Receive side ADPCM RESET (in accordance with the G.721)

1: RESET

B4: .....Transmit side PCM signal ON/OFF

0: ON

1: OFF

PCM idle pattern is transmitted when set OFF B3: ...... Receive side ADPCM data MUTE 1: N

1: MUTE

Mute operation set by B2, 1, 0 is available, provided this bit is valid when MUTE pin is "0".

B2, 1, 0: ..... Receive side voice path mute level settings

(MLV2, MLV1, MLV0) =

(0, 0, 0): through

(0, 0, 1): -6 dB

(0, 1, 0): -12 dB

(0, 1, 1): -18 dB

(1, 0, 0): -24 dB

(1, 0, 1): -30 dB

(1, 1, 0): -36 dB

(1, 1, 1): MUTE

Note: The above settings are not applied to various tone, side tone, and background noise.

# (3) CR2 (PCM CODEC Operation Mode Settings and Transmit/Receive Gain Adjustment)

|               | B7    | В6      | B5    | B4    | В3    | B2    | B1    | В0    |

|---------------|-------|---------|-------|-------|-------|-------|-------|-------|

| ODO           | TX    | X TX TX |       | TX    | RX    | RX    | RX    | RX    |

| CR2           | GAIN3 | GAIN2   | GAIN1 | GAIN0 | GAIN3 | GAIN2 | GAIN1 | GAIN0 |

| Initial value | 0     | 0       | 0     | 0     | 0     | 0     | 0     | 0     |

B7, B6, B5, B4: .... Transmit side signal gain adjustment (refer to Table 2) B3, B2, B1, B0: .... Receive side signal gain adjustment (refer to Table 2)

Table 2 Transmit/Receive Gain Settings

| B7 | В6 | B5 | B4 | Transmit Side Gain | В3 | B2 | B1 | В0 | Receive Side Gain |

|----|----|----|----|--------------------|----|----|----|----|-------------------|

| 1  | 0  | 0  | 0  | −16 dB             | 1  | 0  | 0  | 0  | −16 dB            |

| 1  | 1  | 0  | 1  | –14 dB             | 1  | 1  | 0  | 1  | −14 dB            |

| 1  | 0  | 1  | 0  | −12 dB             | 1  | 0  | 1  | 0  | −12 dB            |

| 1  | 0  | 1  | 1  | −10 dB             | 1  | 0  | 1  | 1  | −10 dB            |

| 1  | 1  | 0  | 0  | −8 dB              | 1  | 1  | 0  | 0  | −8 dB             |

| 1  | 1  | 0  | 1  | −6 dB              | 1  | 1  | 0  | 1  | −6 dB             |

| 1  | 1  | 1  | 0  | −4 dB              | 1  | 1  | 1  | 0  | −4 dB             |

| 1  | 1  | 1  | 1  | −2 dB              | 1  | 1  | 1  | 1  | −2 dB             |

| 0  | 0  | 0  | 0  | 0 dB               | 0  | 0  | 0  | 0  | 0 dB              |

| 0  | 0  | 0  | 1  | +2 dB              | 0  | 0  | 0  | 1  | +2 dB             |

| 0  | 0  | 1  | 0  | +4 dB              | 0  | 0  | 1  | 0  | +4 dB             |

| 0  | 0  | 1  | 1  | +6 dB              | 0  | 0  | 1  | 1  | +6 dB             |

| 0  | 1  | 0  | 0  | +8 dB              | 0  | 1  | 0  | 0  | +8 dB             |

| 0  | 1  | 0  | 1  | +10 dB             | 0  | 1  | 0  | 1  | +10 dB            |

| 0  | 1  | 1  | 0  | +12 dB             | 0  | 1  | 1  | 0  | +12 dB            |

| 0  | 1  | 1  | 1  | +14 dB             | 0  | 1  | 1  | 1  | +14 dB            |

The above gain settings table shows the transmit/receive voice signal gain settings and the transmit side gain settings for DTMF tones and other tones. Tone signal transmission is enabled by CR4 - B6 (discussed later), and the gain setting is set to the levels shown below.

DTMF tones (low group): .....-16 dBm0

DTMF tones (high group) and other tones: ... –14 dBm0

For example, if the transmit gain set value is set to +8 dB (B7, B6, B5, B4) = (0, 1, 0, 0), then the following tones appear at the PCMSO pin.

DTMF tones (low group): ......-8 dBm0

DTMF tones (high group) and other tones: ... -6 dBm0

However, the gain of the receive side tone and the gain of the side tones (path from transmit side to receive side) are set by the CR3 register.

# (4) CR3 (Side Tone and Tone Generator Gain Adjustment)

|               | B7        | В6        | B5        | B4     | В3    | B2    | B1    | В0    |

|---------------|-----------|-----------|-----------|--------|-------|-------|-------|-------|

| CDO           | Side Tone | Side Tone | Side Tone | TONE   | TONE  | TONE  | TONE  | TONE  |

| CR3           | GAIN2     | GAIN1     | GAIN0     | ON/OFF | GAIN3 | GAIN2 | GAIN1 | GAIN0 |

| Initial value | 0         | 0         | 0         | 0      | 0     | 0     | 0     | 0     |

B7, B6, B5: ...... Side tone gain adjustment (refer to Table 3)

B4: ...... Tone generator ON/OFF 0: OFF 1: ON

B3, B2, B1, B0: . Tone generator Receive side gain adjustment (refer to Table 4)

**Table 3 Side Tone Gain Settings**

| B7 | В6 | <b>B</b> 5 | Side Tone Gain |  |  |  |  |

|----|----|------------|----------------|--|--|--|--|

| 0  | 0  | 0          | 0 OFF          |  |  |  |  |

| 0  | 0  | 1          | 1 –15 dB       |  |  |  |  |

| 0  | 1  | 0          | 0 –13 dB       |  |  |  |  |

| 0  | 1  | 1          | -11 dB         |  |  |  |  |

| 1  | 0  | 0          | - 9 dB         |  |  |  |  |

| 1  | 0  | 1          | - 7 dB         |  |  |  |  |

| 1  | 1  | 0          | - 5 dB         |  |  |  |  |

| 1  | 1  | 1          | - 3 dB         |  |  |  |  |

**Table 4 Receive Side Tone Generator Gain Settings**

| В3 | B2 | B1 | В0 | Tone Generator Gain | В3 | B2 | B1 | В0 | Tone Generator Gain |

|----|----|----|----|---------------------|----|----|----|----|---------------------|

| 0  | 0  | 0  | 0  | −36 dB              | 1  | 0  | 0  | 0  | –20 dB              |

| 0  | 0  | 0  | 1  | −34 dB              | 1  | 0  | 0  | 1  | –18 dB              |

| 0  | 0  | 1  | 0  | −32 dB              | 1  | 0  | 1  | 0  | –16 dB              |

| 0  | 0  | 1  | 1  | -30 dB              | 1  | 0  | 1  | 1  | −14 dB              |

| 0  | 1  | 0  | 0  | −28 dB              | 1  | 1  | 0  | 0  | −12 dB              |

| 0  | 1  | 0  | 1  | −26 dB              | 1  | 1  | 0  | 1  | −10 dB              |

| 0  | 1  | 1  | 0  | −24 dB              | 1  | 1  | 1  | 0  | – 8 dB              |

| 0  | 1  | 1  | 1  | −22 dB              | 1  | 1  | 1  | 1  | - 6 dB              |

The receive side tone generator gain settings shown in Table 4 are set with the following levels as a reference.

DTMF tones (low group): ..... –2 dBm0

DTMF tones (high group) and other tones: ... 0 dBm0

For example, if the tone generator gain set value is set to –6 dB (B3, B2, B1, B0)=(1, 1, 1, 1), then tones at the following levels appear at the SAO or VFRO pin.

DTMF tones (low group): .....-8 dBm0

DTMF tones (high group) and other tones: ... –6 dBm0

# (5) CR4 (Tone Generator Operation Mode and Frequency Settings)

|               | B7         | В6   | B5    | B4    | В3    | B2    | B1    | В0    |

|---------------|------------|------|-------|-------|-------|-------|-------|-------|

| CR4           | DTMF/      | TONE | TONE5 | TONE4 | TONE3 | TONE2 | TONE1 | TONEO |

|               | OTHERS SEL | SEND |       |       |       |       |       |       |

| Initial value | 0          | 0    | 0     | 0     | 0     | 0     | 0     | 0     |

B7: ..... Selection of DTMF signal and other tones

(S tone, F tone, R tone, etc.) 0: Other tones 1: DTMF tones

B6: ..... Transmission side tone transmit

0: Voice signal transmit 1: Tone transmit

B5, B4, B3, B2, B1, B0: .. Tone frequency setting (refer to Table 5)

# Table 5 DTMF Signal and Other Tone Settings

# (a) When B7 = 1 (DTMF Tones)

| <b>B</b> 5 | B4 | ВЗ | B2 | B1 | В0 | Description      | B5 | B4 | В3 | B2 | B1 | В0 | Description      |

|------------|----|----|----|----|----|------------------|----|----|----|----|----|----|------------------|

| *          | *  | 0  | 0  | 0  | 0  | 697 Hz + 1209 Hz | *  | *  | 1  | 0  | 0  | 0  | 852 Hz + 1209 Hz |

| *          | *  | 0  | 0  | 0  | 1  | 697 Hz + 1336 Hz | *  | *  | 1  | 0  | 0  | 1  | 852 Hz + 1336 Hz |

| *          | *  | 0  | 0  | 1  | 0  | 697 Hz + 1477 Hz | *  | *  | 1  | 0  | 1  | 0  | 852 Hz + 1477 Hz |

| *          | *  | 0  | 0  | 1  | 1  | 697 Hz + 1633 Hz | *  | *  | 1  | 0  | 1  | 1  | 852 Hz + 1633 Hz |

| *          | *  | 0  | 1  | 0  | 0  | 770 Hz + 1209 Hz | *  | *  | 1  | 1  | 0  | 0  | 941 Hz + 1209 Hz |

| *          | *  | 0  | 1  | 0  | 1  | 770 Hz + 1336 Hz | *  | *  | 1  | 1  | 0  | 1  | 941 Hz + 1336 Hz |

| *          | *  | 0  | 1  | 1  | 0  | 770 Hz + 1477 Hz | *  | *  | 1  | 1  | 1  | 0  | 941 Hz + 1477 Hz |

| *          | *  | 0  | 1  | 1  | 1  | 770 Hz + 1633 Hz | *  | *  | 1  | 1  | 1  | 1  | 941 Hz + 1633 Hz |

# (b) When B7 = 0 (Other than DTMF Tones)

| B5 | B4 | В3 | B2 | B1 | В0 |            | Description    | B5 | B4 | ВЗ | B2 | B1 | ВО | Description  |

|----|----|----|----|----|----|------------|----------------|----|----|----|----|----|----|--------------|

| 0  | 0  | 0  | 0  | 0  | 0  |            | 784.0 Hz (G)   | 1  | 0  | 0  | 0  | 0  | 0  | 1100 Hz      |

| 0  | 0  | 0  | 0  | 0  | 1  |            | 830.6 Hz (G+)  | 1  | 0  | 0  | 0  | 0  | 1  | 1200 Hz      |

| 0  | 0  | 0  | 0  | 1  | 0  |            | 880.0 Hz (A)   | 1  | 0  | 0  | 0  | 1  | 0  | 1300 Hz      |

| 0  | 0  | 0  | 0  | 1  | 1  |            | 932.3 Hz (A+)  | 1  | 0  | 0  | 0  | 1  | 1  | 1400 Hz      |

| 0  | 0  | 0  | 1  | 0  | 0  |            | 987.8 Hz (B)   | 1  | 0  | 0  | 1  | 0  | 0  | 1500 Hz      |

| 0  | 0  | 0  | 1  | 0  | 1  |            | 1046.5 Hz (C)  | 1  | 0  | 0  | 1  | 0  | 1  | 1600 Hz      |

| 0  | 0  | 0  | 1  | 1  | 0  |            | 1108.7 Hz (C+) | 1  | 0  | 0  | 1  | 1  | 0  | 1700 Hz      |

| 0  | 0  | 0  | 1  | 1  | 1  |            | 1174.7 Hz (D)  | 1  | 0  | 0  | 1  | 1  | 1  | 1800 Hz      |

| 0  | 0  | 1  | 0  | 0  | 0  |            | 1244.5 Hz (D+) | 1  | 0  | 1  | 0  | 0  | 0  | 1900 Hz      |

| 0  | 0  | 1  | 0  | 0  | 1  |            | 1318.5 Hz (E)  | 1  | 0  | 1  | 0  | 0  | 1  | 2000 Hz      |

| 0  | 0  | 1  | 0  | 1  | 0  |            | 1396.9 Hz (F)  | 1  | 0  | 1  | 0  | 1  | 0  | 2100 Hz      |

| 0  | 0  | 1  | 0  | 1  | 1  | ale        | 1480.0 Hz (F+) | 1  | 0  | 1  | 0  | 1  | 1  | 2200 Hz      |

| 0  | 0  | 1  | 1  | 0  | 0  | Tone Scale | 1568.0 Hz (G)  | 1  | 0  | 1  | 1  | 0  | 0  | 2300 Hz      |

| 0  | 0  | 1  | 1  | 0  | 1  | Ton        | 1661.2 Hz (G+) | 1  | 0  | 1  | 1  | 0  | 1  | 2400 Hz      |

| 0  | 0  | 1  | 1  | 1  | 0  |            | 1760.0 Hz (A)  | 1  | 0  | 1  | 1  | 1  | 0  | 2500 Hz      |

| 0  | 0  | 1  | 1  | 1  | 1  |            | 1864.7 Hz (A+) | 1  | 0  | 1  | 1  | 1  | 1  | 2600 Hz      |

| 0  | 1  | 0  | 0  | 0  | 0  |            | 1975.5 Hz (B)  | 1  | 1  | 0  | 0  | 0  | 0  | 2700 Hz      |

| 0  | 1  | 0  | 0  | 0  | 1  |            | 2093.0 Hz (C)  | 1  | 1  | 0  | 0  | 0  | 1  | 2800 Hz      |

| 0  | 1  | 0  | 0  | 1  | 0  |            | 2217.5 Hz (C+) | 1  | 1  | 0  | 0  | 1  | 0  | 2900 Hz      |

| 0  | 1  | 0  | 0  | 1  | 1  |            | 2349.3 Hz (D)  | 1  | 1  | 0  | 0  | 1  | 1  | 3000 Hz      |

| 0  | 1  | 0  | 1  | 0  | 0  |            | 2489.0 Hz (D+) | 1  | 1  | 0  | 1  | 0  | 0  | 2760 Hz      |

| 0  | 1  | 0  | 1  | 0  | 1  |            | 2637.0 Hz (E)  | 1  | 1  | 0  | 1  | 0  | 1  | <del>_</del> |

| 0  | 1  | 0  | 1  | 1  | 0  |            | 2793.8 Hz (F)  | 1  | 1  | 0  | 1  | 1  | 0  | <del>_</del> |

| 0  | 1  | 0  | 1  | 1  | 1  |            | 2960.0 Hz (F+) | 1  | 1  | 0  | 1  | 1  | 1  | <del>-</del> |

| 0  | 1  | 1  | 0  | 0  | 0  |            | 3136.0 Hz (G)  | 1  | 1  | 1  | 0  | 0  | 0  | <del>_</del> |

| 0  | 1  | 1  | 0  | 0  | 1  |            | 400 Hz         | 1  | 1  | 1  | 0  | 0  | 1  | _            |

| 0  | 1  | 1  | 0  | 1  | 0  |            | 500 Hz         | 1  | 1  | 1  | 0  | 1  | 0  | <del>_</del> |

| 0  | 1  | 1  | 0  | 1  | 1  |            | 600 Hz         | 1  | 1  | 1  | 0  | 1  | 1  | <u> </u>     |

| 0  | 1  | 1  | 1  | 0  | 1  |            | 700 Hz         |    | 1  | 1  | 1  | 0  | 0  | _            |

| 0  | 1  | 1  | 1  | 0  | 1  |            | 800 Hz         |    | 1  | 1  | 1  | 0  | 1  | _            |

| 0  | 1  | 1  | 1  | 1  | 0  |            | 900 Hz         | 1  | 1  | 1  | 1  | 1  | 0  | _            |

| 0  | 1  | 1  | 1  | 1  | 1  |            | 1000 Hz        | 1  | 1  | 1  | 1  | 1  | 1  | <del>_</del> |

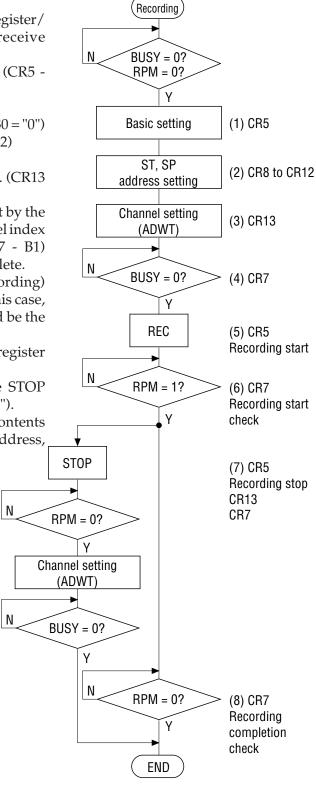

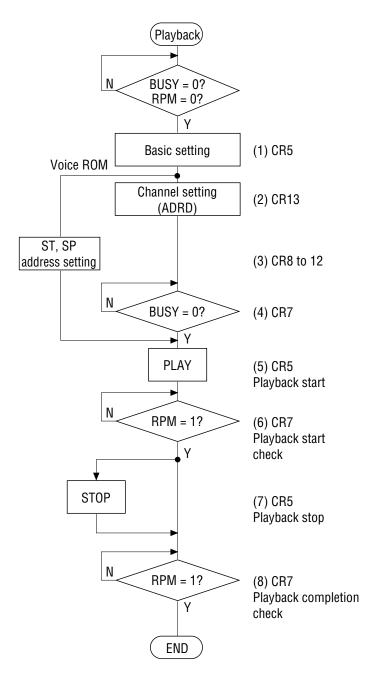

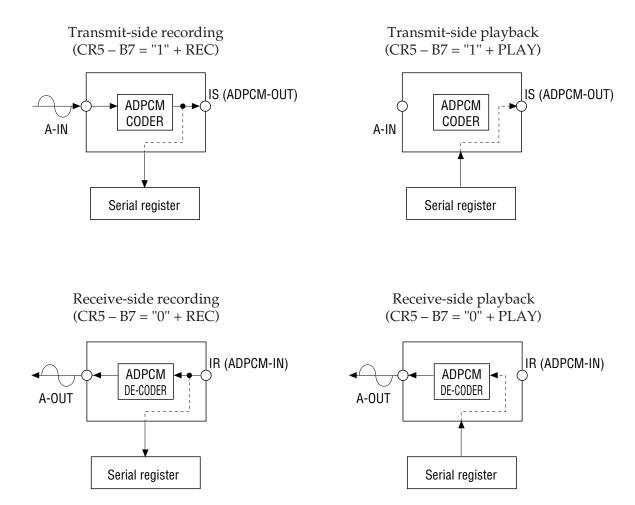

### (6) CR5 (Serial Register Interface Control)

|               | B7    | В6   | B5    | B4 | В3 | B2 | B1      | В0   |

|---------------|-------|------|-------|----|----|----|---------|------|

| CR5           | SEND/ | ROM/ | 4M8M/ |    | _  |    | CMD1    | CMD0 |

| UND           | REC   | SR   | 1M    | _  |    | _  | CIVID I |      |

| Initial value | 0     | 0    | 0     | 0  | 0  | 0  | 0       | 0    |

B7: ......Connection between register and ADPCM

0: with ADPCM receive side 1: ADPCM Transmit side

B6: ......Voice ROM/Serial register selection

0: Serial Register 1: Voice ROM

B5: ......Connecting serial register capacity

0: 1 Mb (MSM63V89C)

1: 4 Mb (MSM6684), 8 Mb (MSM6685)

B4 - B2: ..... Reserved for test. Should be set "0"

B1, B0: ......Serial register I/F Instruction command

(CMD1, CMD0) =(0,0): NOP

> (0,1): PLAY (Playback) (1,0): REC (Recording)

(1, 1): STOP (Stop)

Instruction commands of Play and REC should not be set when busy (CR5 - B1) and RPM (CR5 - B0) are "1".

### (7) CR6 (VOICE/SILENCE Detect Function Control)

|               | B7     | В6   | B5   | B4   | В3  | B2        | B1       | В0       |

|---------------|--------|------|------|------|-----|-----------|----------|----------|

| CR6           | VOX    | ON   | ON   | OFF  | VOX | RX NOISE  | RX NOISE | RX NOISE |

|               | ON/OFF | LVL1 | LVL0 | TIME | IN  | LEVEL SEL | LVL1     | LVL0     |

| Initial value | 0      | 0    | 0    | 0    | 0   | 0         | 0        | 0        |

B7: ......Voice/Silence detect function ON/OFF 0: OFF 1: ON

B6, B5: ...... Transmit side voice/silence detector level settings

(0,0): -20 dBm0(0,1): -25 dBm0

(1,0): -30 dBm0(1,1): -35 dBm0

B4: ..... Hangover time (refer to Fig. 1) settings 0: 160 ms 1: 320 ms

B3: .....Receive side Voice/Silence detect input signal

0: Internal background noise transmit 1: Voice receive signal transmit When using this data, set the VOXI pin to "0".

B2: .....Receive side background noise level setting

1: External (by B1, B0) setting 0: Internal automatic setting

Internal automatic setting  $\rightarrow$  Set to the voice signal level when B3 (VOXI)

changes from "1" to "0".

B1, B0: ..... External setting background noise level

(0,0): No noise (0,1): -55 dBm0

(1,0): -45 dBm0 (1,1): -35 dBm0

<sup>\* (</sup>CMD1, CMD0) are reset (0, 0) after command execution.

# (8) CR7 (Detect Register: Read-only)

|               | B7  | В6           | B5           | B4 | В3 | B2 | B1   | В0  |

|---------------|-----|--------------|--------------|----|----|----|------|-----|

| 0.07          | VOX | Silent Level | Silent Level |    |    | _  | Busy | RPM |

| CR7           | OUT | 1            | 0            | _  |    |    |      |     |

| Initial value | 0   | 0            | 0            | 0  | 0  | 0  | 0    | 0   |

B7: .....Transmit side voice/silence detection

0: Silence

1: Voice

B6, B5: ...... Transmit side silence level (indicator)

(0,0):Below -60 dBm0

(0,1): -50 to -60 dBm0

(1,0): -40 to -50 dBm0

(1,1): Above –40 dBm0

Note: These outputs are enabled when the voice/silence detect function is turned on by CR6 - B7.

B4, B3, B2: . Not used

B1: ..... Serial Register I/F monitoring

Monitors address read and write operation of serial register interface.