# **OKI** Semiconductor

# MSM7719-01

# Echo Canceler with ADPCM Transcoder

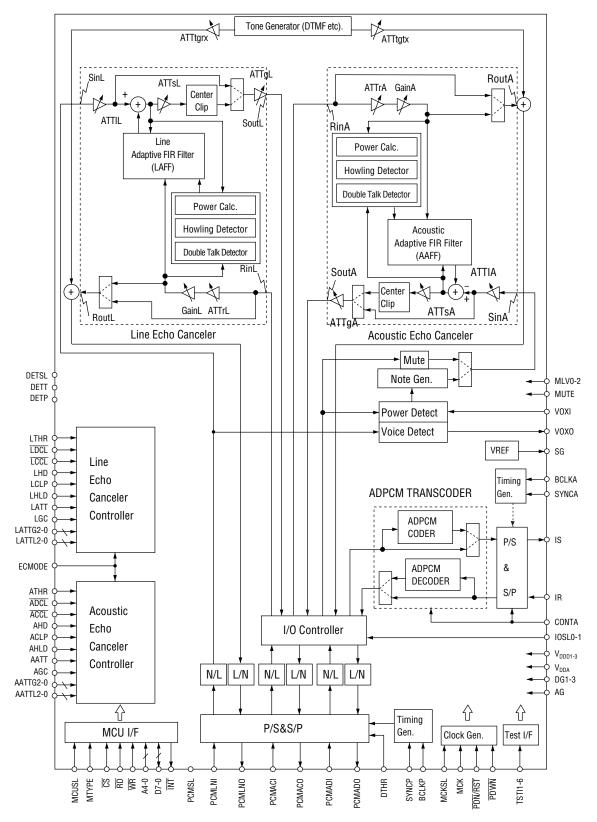

# **GENERAL DESCRIPTION**

The MSM7719, developed for PHS (Personal Handyphone System) applications, is an LSI device and contains a line echo canceler, an acoustic echo canceler (for handsfree conversation), and a single channel full-duplex ADPCM transcoder.

This device includes DTMF tone and several types of tone generation, transmit/receive data mute and gain control, and VOX function and is best suited for PHS applications.

# **FEATURES**

| <ul> <li>ADPCM :</li> <li>PCM interface coding format :</li> <li>Built-in 2-channel (line and acoustic) (</li> </ul> | V <sub>DD</sub> : 4.5 V to 5.5 V<br>ITU-T Recommendations G.726<br>μ-law<br>echo canceler |

|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Line echo canceler<br>Acoustic echo canceler (for hands:                                                             | free conversation)                                                                        |

| Echo attenuation : 30 dB (typ.)                                                                                      |                                                                                           |

| Cancelable echo delay time :                                                                                         |                                                                                           |

|                                                                                                                      | eler +27 ms (max.) for acoustic echo canceler                                             |

| Line echo canceler mode only :                                                                                       | 54 ms (max.)                                                                              |

| • Serial PCM/ADPCM transmission da                                                                                   | ata rate : 64 kbps to 2048 kbps                                                           |

| <ul> <li>Low supply current</li> </ul>                                                                               |                                                                                           |

|                                                                                                                      | Typically 50 mA ( $V_{DD} = 5.0 \text{ V}$ )                                              |

| Power-down mode :                                                                                                    | Typically $0.2 \text{ mA} (V_{DD} = 5.0 \text{ V})$                                       |

| <ul> <li>Master clock frequency :</li> </ul>                                                                         | 9.6 to 10.0 MHz/19.2 to 20.0 MHz                                                          |

| • Transmit/receive mute, transmit/rec                                                                                | eive programmable gain control                                                            |

| • Built-in DTMF tone generator and var                                                                               | rious tones generator                                                                     |

| • Control through parallel microcontro                                                                               | ller interface                                                                            |

| Pin control available for line and a                                                                                 | acoustic echo cancelers                                                                   |

| <ul> <li>Built-in VOX control</li> </ul>                                                                             |                                                                                           |

| Transmit side : V                                                                                                    | /oice/silence detect                                                                      |

| Receive side : E                                                                                                     | Background noise generation at the absence of voice signal                                |

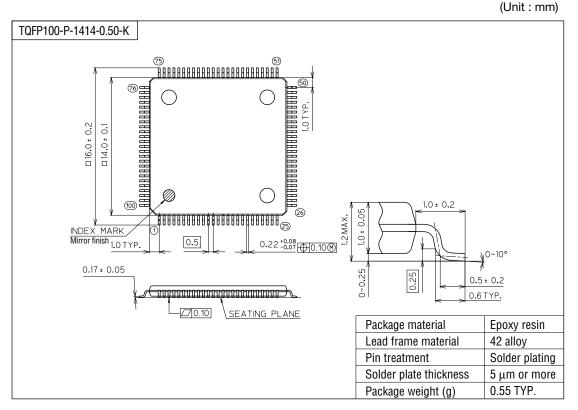

| Package:                                                                                                             |                                                                                           |

| 100-pin plastic TQFP (TQFP100-P-141                                                                                  | 4-0.50-K) (Product name : MSM7719-01TS-K)                                                 |

# **BLOCK DIAGRAM**

2/40

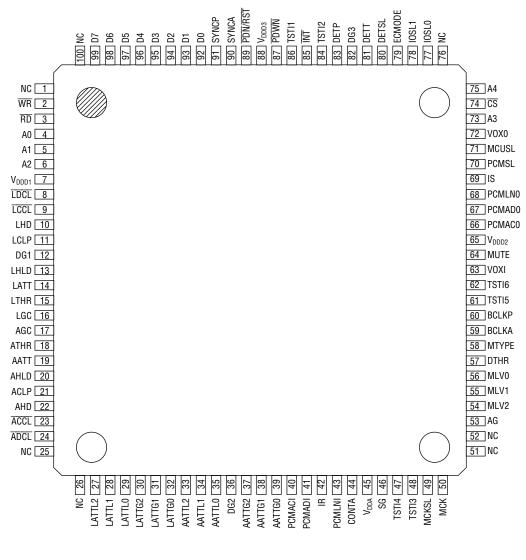

# **PIN CONFIGURATION (TOP VIEW)**

NC: No-connect pin

**100-Pin Plastic TQFP**

# PIN FUNCTIONAL DESCRIPTION

#### SG

Outputs of the analog signal ground voltage.

The output voltage is approximately 2.4 V. Connect bypass capacitors of 10  $\mu$ F and 0.1  $\mu$ F (ceramic type) between these pins and the AG pin. During power-down, the output changes to 0 V.

# AG

Analog ground.

#### DG1, 2, 3

Digital ground.

# V<sub>DDA</sub>

+5 V power supply for analog circuits.

#### V<sub>DDD1, 2, 3</sub>

+5 V power supply for digital circuits.

# PDN/RST

Power-down reset control input.

A logic "0" makes the LSI device enter a power-down state. At the same time, all control register data are reset to the initial state. Set this pin to a logic "1" during normal operating mode. Since this pin is ORed with CR0-B5 (bit 5 (B5) of control register CR0), set CR0-B5 to logic "0" when using this pin. When this pin control is not used (i.e., when controlling by the control register), set this pin to logic "1".

#### **PDWN**

Power-down control input.

The device changes to the power-down state, and each bit of control register and internal variables of control register are not reset when set to a logic "0". During normal operation, set this pin to logic "1". Since this pin is ORed with CR0-B6 (bit 6 (B6) of control register CR0), set CR0-B6 to logic "0" when using this pin. When this pin control is not used (i.e., when controlling by the control register), set this pin to logic "1".

#### MCK

Master clock input.

The frequency must be 9.6 to 10.0 MHz/19.2 to 20.0 MHz. The master clock signal is allowed to be asynchronous with SYNCP, SYNCA, BCLKP, and BCLKA.

#### MCKSL

Master clock selection input.

Set MCKSL to logic "0" when the master clock frequency is 9.6 to 10.0 MHz, and to logic "1" when it is 19.2 to 20.0 MHz.

#### PCMACO

PCM data output of the echo canceler.

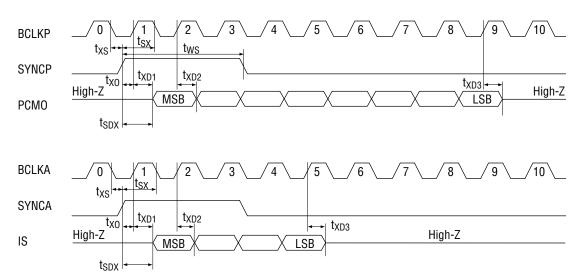

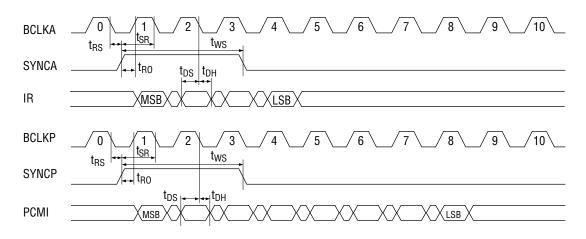

PCM is output from MSB in a sequential order, synchronizing with the rising edge of BCLKP and SYNCP.

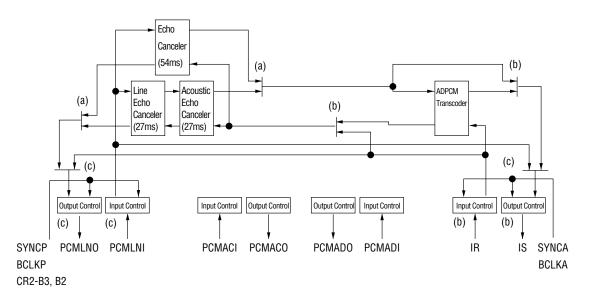

This pin is in a high impedance state except during 8-bit PCM output. When DTHR is set to logic "1", this pin becomes a 4-bit output and the input data to the input pin set by IOSL0-1 is output as it is. In this case, this pin is in a high impedance state except during 4-bit output. Note that the echo canceler signal output mode for this pin changes depending on the setting of IOSL0-1. (This pin is also in a high impedance state during power-down or initial mode.) Refer to Figs. 1-5.

#### PCMACI

PCM data input of the echo canceler.

PCM is shifted in at the falling edge of BCLKP and input from MSB.

The start of the PCM data (MSB) is identified at the rising edge of SYNCP. When DTHR is set to logic "1", this pin becomes a 4-bit input and the input data is output to the output pin set by IOSL0-1 as it is. This pin is provided with a 500-k $\Omega$  pull-up resistor. Note that the echo canceler signal input mode for this pin changes depending on the setting of IOSL0-1.

Refer to Figs. 1-5.

#### PCMADO

PCM data output.

PCM is serially output from MSB in synchronization with the rising edge of BCLKP and SYNCP. This pin is in a high impedance state except during 8-bit PCM output. When DTHR is set to logic "1", this pin becomes a 4-bit output and the input data to the input pin set by IOSL0-1 is output as it is. In this case, this pin is in a high impedance state except during 4-bit output.

Note that the signal ouput mode for this pin changes and the I/O control signal for this pin switches between BCLKA/SYNCA and BCLKP/SYNCP depending on the setting of IOSL0-1. (This pin is also in a high impedance state during power-down or initial mode.) Refer to Figs. 1-5.

#### PCMADI

#### PCM data input.

PCM is shifted in at the falling edge of the BCLKP signal and input from MSB. The start of the PCM data (MSB) is identified at the rising edge of SYNCP. When DTHR is set to logic "1", this pin becomes a 4-bit input and the input data is output to the output pin set by IOSL0-1 as it is. This pin is provided with a 500-k $\Omega$  pull-up resistor. Note that the signal input mode for this pin changes and the I/O control signal for this pin switches between BCLKA/SYNCA and BCLKP/SYNCP depending on the setting of IOSL0-1.

Refer to Figs. 1-5.

#### IOSL0-1

These pins specify PCM signal I/O mode for the PCMACO, PCMACI, PCMADO, and PCMADI pins. Since The IOSL0 and IOSL1 pins are ORed with the control register bits CR3-B6 and B5, set these bits to logic "0" before using these pins. When this pin control is not used (i.e., in the case of control with the control register), set these pins to logic "0". Refer to Figs. 1-5.

#### IS

Transmit ADPCM data output.

This data is serially output from MSB in synchronization with the rising edge of BCLKA and SYNCA. This pin is in a high impedance state except during 4-bit ADPCM output. When CONTA is set to logic "1", this pin becomes an 8-bit output and the data that passed through the ADPCM transcoder is output. In this case, this pin is in a high impedance state except during 8-bit output. (This pin is also in a high imedance state during power-down or initial mode.) Refer to Figs. 1-5.

# IR

Receive ADPCM data input.

ADPCM is shifted in on the rising edge of BCLKA in synchronization with SYNCA and input data orderly from MSB. When CONTA is set to logic "1", this pin becomes an 8-bit input and the data is passed through the ADPCM transcoder and processed. This pin is provided with a 500-k $\Omega$  pull-up resistor.

#### PCMLNO

PCM receive data output of the line echo canceler.

PCM is output from MSB in a sequential order, synchronizing with the rising edge of BCLKP and SYNCP.

This pin is in a high impedance state except during 8-bit PCM output. When DTHR is set to logic "1", this pin becomes a 4-bit output and the input data to the input pin set by IOSL0-1 is output as it is. In this case, this pin is in a high impedance state except during 4-bit output.

(This pin is also in a high impedance state during power-down or initial mode.) Refer to Figs. 1-5.

#### PCMLNI

PCM transmit data input of the line echo canceler.

PCM is shifted in at the falling edge of the BCLKP signal and input from MSB. The start of the PCM data (MSB) is identified at the rising edge of SYNCP. When DTHR is set to logic "1", this pin becomes a 4-bit input and the input data is output to the output pin set by IOSL0-1 as it is. This pin is provided with a 500-k $\Omega$  pull-up resistor.

Refer to Figs. 1-5.

#### BCLKA

Shift clock input for the ADPCM data (IS, IR). The frequency is from 64 kHz to 2048 kHz.

#### **SYNCA**

8 kHz synchronous signal input for ADPCM data. Synchronize this data with BCLKA signal. SYNCA is used for indicating the MSB of the serial ADPCM data stream.

#### BCLKP

Shift clock input for the PCM data (PCMLNO/PCMLNI, PCMACO/PCMACI, PCMADO/ PCMADI). The frequency is set in the range of 64 kHz to 2048 kHz.

#### SYNCP

8 kHz synchronous signal input for PCM data. This signal must be synchronized with the BCLKP signal.

#### **MCUSL, MTYPE**

If the microcontroller interface is not to be used, set the MCUSL input pin to logic "1". This setting skips the intitial mode as the operating mode. For the MTYPE pin, which is the microcontroller interface selection pin, logic "0" sets the read/write independent control mode and logic "1" sets read/write shared control mode.

When this pin control is not used (i.e., when controlling by the control register), set these pins to logic "0".

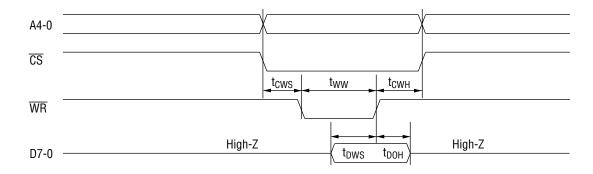

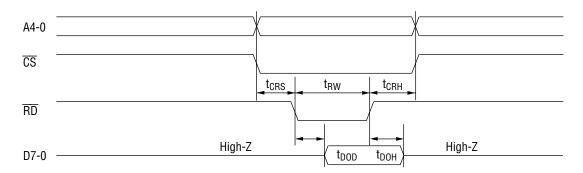

#### CS, RD, WR

A 19-byte control register is provided in this LSI device. Data is read and written by using these pins from the external microcontroller. See the microcontroller write and read timing diagrams in the Electrical Characteristics.

When this pin control is not used (i.e., when controlling by the control register), set these pins to logic "1".

#### A4-A0, D7-D0

A4-A0 are address input pins of the control register, and D7-D0 are data I/O pins. When this pin control is not used (i.e., when controlling by the control register), set these pins to logic "0".

#### INT

Reserved.

#### PCMSL

Reserved.

#### CONTA

ADPCM transcoder setting pin. When this pin is set to logic "1", the transcoder-through mode is set. In this mode, the IS and IR pins become 8-bit PCM serial input and output pins. Since this pin is ORed with the control register bit CR1-B7, set CR1-B7 to logic "0" to use this pin.

When this pin control is not used (i.e., when controlling by the control register), set this pin to logic "0".

Refer to Figs. 1-5.

#### DTHR

Through mode setting pin. When this pin is set to logic "1", the entire circuit is put in the through mode. In this mode, the PCM input and output pins become 4-bit serial input and output pins and all functions of the echo canceler, ADPCM transcoder, and MUTEVOX are disabled. Use this pin when making 32-kbps data communication.

Since this pin is ORed with the control register bit CR1-B5, set CR1-B5 to logic "0" to use this pin. When this pin control is not used (i.e., when controlling by the control register), set this pin to logic "0".

Note that 64-kbps data communication is not supported in this device. Refer to Figs. 1-5.

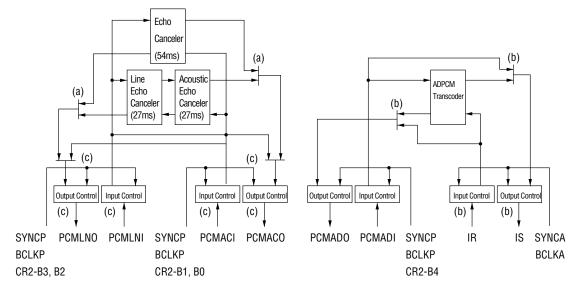

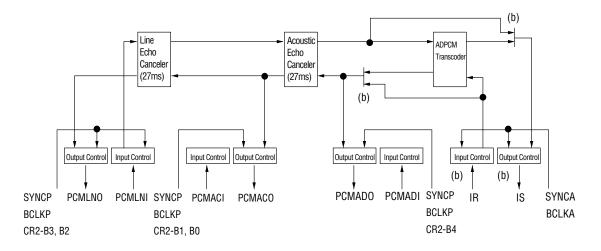

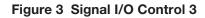

IOSL1="0", IOSL0="0" Control (a): ECMODE, CR0-B0 Control (b): CONTA, CR1-B7 Control (c): DTHR, CR1-B5

Figure 2 Signal I/O Control 2

IOSL1="0", IOSL0="1" Control (a): ECMODE, CR0-B0 Control (b): CONTA, CR1-B7 Control (c): DTHR, CR1-B5

IOSL1="1", IOSL0="0" Control (a): ECMODE, CR0-B0 Control (b): CONTA, CR1-B7 Control (c): DTHR, CR1-B5

IOSL1="1", IOSL0="1" Control (a): ECMODE, CR0-B0 Control (b): CONTA, CR1-B7 Control (c): DTHR, CR1-B5

| SYNCP/SYNCA<br>BCLKP/BCLKA<br>PCM multiplexing<br>PCMADI/O data<br>(DTHR="0") | $ \begin{array}{c} & & & & & \\ \hline \\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | U<br>N |

|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| PCMADI/O data<br>(DTHR="1")                                                   | $\begin{array}{c} \langle \underline{1} \\ \langle \underline{2} \\ \langle \underline{3} \\ \langle \underline{4} \\ \rangle \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

| PCMLNI/O data<br>PCMACI/O data<br>(DTHR="0")                                  | $ \begin{array}{c} \langle 1 \ \\ 2 \ \\ 3 \ \\ 4 \ \\ 5 \ \\ 6 \ \\ 7 \ \\ 8 \ \\ 1 \ \\ 2 \ \\ 3 \ \\ 4 \ \\ 5 \ \\ 6 \ \\ 7 \ \\ 8 \ \\ 1 \ \\ 2 \ \\ 3 \ \\ 4 \ \\ 5 \ \\ 6 \ \\ 7 \ \\ 8 \ \\ 1 \ \\ 2 \ \\ 3 \ \\ 4 \ \\ 5 \ \\ 6 \ \\ 7 \ \\ 8 \ \\ 1 \ \\ 2 \ \\ 3 \ \\ 4 \ \\ 5 \ \\ 6 \ \\ 7 \ \\ 8 \ \\ 1 \ \\ 2 \ \\ 3 \ \\ 4 \ \\ 5 \ \\ 6 \ \\ 7 \ \\ 8 \ \\ 1 \ \\ 2 \ \\ 3 \ \\ 4 \ \\ 5 \ \\ 6 \ \\ 7 \ \\ 8 \ \\ 1 \ \\ 2 \ \\ 3 \ \\ 4 \ \\ 5 \ \\ 6 \ \\ 7 \ \\ 8 \ \\ 1 \ \\ 2 \ \\ 3 \ \\ 4 \ \\ 5 \ \\ 6 \ \\ 7 \ \\ 8 \ \\ 1 \ \\ 2 \ \\ 3 \ \\ 4 \ \\ 5 \ \\ 6 \ \\ 7 \ \\ 8 \ \\ 1 \ \\ 2 \ \\ 3 \ \\ 4 \ \\ 5 \ \\ 6 \ \\ 7 \ \\ 8 \ \\ 1 \ \\ 2 \ \\ 3 \ \\ 4 \ \\ 5 \ \\ 6 \ \\ 7 \ \\ 8 \ \\ 1 \ \\ 2 \ \\ 3 \ \\ 4 \ \\ 5 \ \\ 6 \ \\ 7 \ \\ 8 \ \\ 1 \ \\ 2 \ \\ 3 \ \\ 4 \ \\ 5 \ \\ 6 \ \\ 7 \ \\ 8 \ \\ 1 \ \\ 2 \ \\ 3 \ \\ 4 \ \\ 5 \ \\ 6 \ \\ 7 \ \\ 8 \ \\ 1 \ \\ 2 \ \\ 3 \ \\ 4 \ \\ 5 \ \\ 6 \ \\ 7 \ \\ 8 \ \\ 1 \ \\ 2 \ \\ 3 \ \\ 1 \ \\ 2 \ \\ 3 \ \\ 1 \ \\ 2 \ \\ 3 \ \\ 1 \ \\ 2 \ \\ 3 \ \\ 1 \ \\ 2 \ \\ 3 \ \\ 3 \ \\ 1 \ \\ 2 \ \\ 3 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \\ 1 \ \ \ 1 \ \\ 1 \ \ \ 1 \ \ \ 1 \ \ \ \$ |        |

| PCMLNI/O data<br>PCMACI/O data<br>(DTHR="1")                                  | $\begin{array}{c} \langle 1 \ 2 \ 3 \ 4 \rangle & & \\ MSB \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |

| IR/IS data<br>(CONTA="1")                                                     | $\frac{\langle 1 \langle 2 \rangle \langle 3 \rangle \langle 4 \rangle \langle 5 \rangle \langle 6 \rangle \langle 7 \rangle \langle 8 \rangle}{MSB}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |

| IR/IS data<br>(CONTA="0")                                                     | $\langle \underline{1} \langle \underline{2} \rangle \langle \underline{3} \rangle \langle \underline{4} \rangle$<br>MSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |

Note: The PCM signals (PCMADI and PCMADO) of the ADPCM transcoder can be assigned to time slot 1 or 2.

The PCM signals (PCMLNI, PCMLNO, PCMACI, and PCMACO) of the echo canceler can be assigned to one of the time slots 1 to 4.

The ADPCM signals (IR and IS) of the ADPCM transcoder are always assigned to time slot 1.

#### Figure 5 PCM Multiplexing/ADPCM Timing

#### ECMODE

This pin specifies the operating mode of the echo canceler. When set to logic "0", this device operates as a line echo canceler (with cancelable echo delay time of 27 ms max.) + an acoustic echo canceler (with cancelabel echo delay time of 27 ms max.); when set to logic "1", it operates as a line echo canceler (with cancelable echo delay time of 54 ms max.).

When this pin control is not used (i.e., when controlling by the control register), set these pins to logic "0".

#### LTHR, ATHR

(L: Line A: Acoustic)

These pins control the through mode of the echo canceler. In this mode, SinL/A data and RinL/A data is output directly to SoutL/A and RoutL/A respectively, while retaining their echo canceler coefficients.

0: Normal mode (Echo cancellation) 1: Through mode

When this pin control is not used (i.e., when controlling by the control register), set these pins to logic "1".

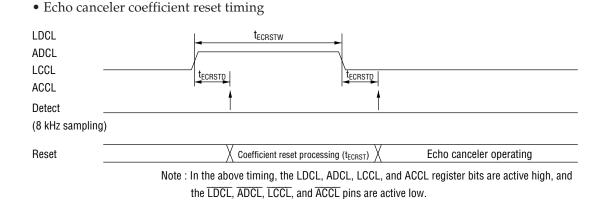

# LDCL, ADCL

These pins control clearing the coefficient 1 of the adaptive FIR filter used by the echo canceler. If the echo path changes, reset both the coefficient 1 (by setting  $\overline{\text{LDCL}}/\overline{\text{ADCL}}$  to "0") and the coefficient 2 (by setting  $\overline{\text{LCCL}}/\overline{\text{ACCL}}$  to "0") of the adaptive FIR filter whenever possible.

0: Resets the coefficient 1: Normal operation

When this pin control is not used (i.e., when controlling by the control register), set these pins to logic "1".

#### LCCL, ACCL

These pins control clearing the coefficient 2 of the adaptive FIR filter used by the echo canceler. If the echo path changes, reset both the coefficient 1 (by setting  $\overline{LDCL}/\overline{ADCL}$  to "0") and the coefficient 2 (by setting  $\overline{LCCL}/\overline{ACCL}$  to "0") of the adaptive FIR filter whenever possible.

0: Resets the coefficient 1: Normal operation

When this pin control is not used (i.e., when controlling by the control register), set these pins to logic "1".

#### LHD, AHD

Howling detection ON/OFF control pins.

0: OFF, 1: ON

When this pin control is not used (i.e., when controlling by the control register), set these pins to logic "0".

# LCLP, ACLP

These pins turn ON or OFF the Center Clipping funciton that forcibly sets the SoutL output of the line echo canceler to minimum positive value when it is -57 dBm0 or less.

0: Center Clipping OFF

1: Center Clipping ON

When this pin control is not used (i.e., when controlling by the control register), set these pins to logic "0".

#### LHLD, AHLD

These pins control updating the coefficient of the adaptive FIR filter (AFF) for the echo canceler. 0: Normal mode (updates the coefficient)

1: Coefficient Fixed mode

When this pin control is not used (i.e., when controlling by the control register), set these pins to logic "0".

# LATT, AATT

These pins turn ON or OFF the ATT function that prevents howling from occurring by means of attenuators ATTsL/A and ATTrL/A provided for the RinL/A input and the SoutL/A output of the echo canceler.

When a signal is input to RinL/A only, the attenuator ATTsL/A of the SoutL/A output is activated. When a signal is input to SinL/A only or to both SinL/A and RinL/A, the attenuator ATTrL/A of the RinL/A input is activated. The ATT values are both about 6 dB.

0: ATT function ON

1: ATT function OFF

When this pin control is not used (i.e., when controlling by the control register), set these pins to logic "0".

# LGC, AGC

These pins turn ON or OFF the gain control function that controls the RinL/A input level and prevents howling from occurring by the gain controller (GainL/A) provided for the RinL/A input of the echo canceler. The RinL/A input level is adjusted in the attenuation range of 0 to -8.5 dB. This adjusting starts at the RinL/A input level of -24 dBm0.

0: gain control OFF

1: gain control ON

When this pin control is not used (i.e., when controlling by the control register), set these pins to logic "0".

#### MUTE

Receive side voice path mute level enable pin. To set a mute level, set this pin to logic "1". When this pin control is not used (i.e., when controlling by the control register), set this pin to logic "0".

#### MLV0-2

Receive side voice path mute level setting pins. For the control method, refer to the control register (CR1) description. Since this signal is ORed with CR1-B2, B1, and B0 internally, set the bits of the register to logic "0" before using these pins.

#### DETSL

Reserved pin. Set this pin to logic "0".

#### DETT

Reserved pin. Set this pin to logic "0".

#### DETP

Reserved pin. Set this pin to logic "0".

#### LATTG2-0, AATTG2-0

Pad setting pins for the echo canceler's SoutL/A output gain.

| Level | ATTG2 | ATTG1 | ATTG0 |

|-------|-------|-------|-------|

| 0 dB  | 0     | 0     | 0     |

| 2 dB  | 0     | 0     | 1     |

| 4 dB  | 0     | 1     | 0     |

| 6 dB  | 0     | 1     | 1     |

| 8 dB  | 1     | 0     | 0     |

| 10 dB | 1     | 0     | 1     |

| 12 dB | 1     | 1     | 0     |

| 14 dB | 1     | 1     | 1     |

When this pin control is not used (i.e., when controlling by the control register), set these pins to logic "0".

#### LATTL2-0, AATTL2-0

Pad setting pins for the echo canceler's SinL/A input loss.

| Level  | ATTL2 | ATTL1 | ATTL0 |

|--------|-------|-------|-------|

| -0 dB  | 0     | 0     | 0     |

| -2 dB  | 0     | 0     | 1     |

| -4 dB  | 0     | 1     | 0     |

| 6 dB   | 0     | 1     | 1     |

| -8 dB  | 1     | 0     | 0     |

| –10 dB | 1     | 0     | 1     |

| –12 dB | 1     | 1     | 0     |

| -14 dB | 1     | 1     | 1     |

When this pin control is not used (i.e., when controlling by the control register), set these pins to logic "0".

#### TSTI1-6

Test input pins. Tie to logic "0".

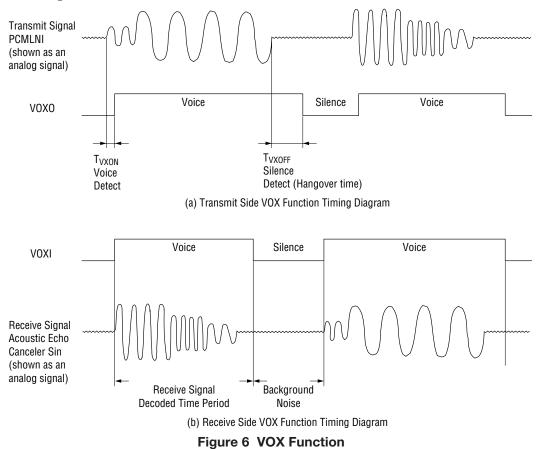

#### νοχο

Signal outut for transmit side VOX function.

This pin is effective when CR6-B7 is set to logic "1" (VOX ON).

The VOX function recognizes the presence or absence of the transmit voice signal by detecting the level of the transmit signal to the line echo canceler. "1" and "0" levels set to this pin correspond to the presence and the absence of voice, respectively. This result appears also at the register bit CR7-B7. The signal energy detect threshold is set by the control register bits CR6-B6, B5.

The timing diagram of the VOX function is shown in Figure 3.

The transmit signal to the line echo canceler refers to the signal input to the PCMLNI pin. Refer to Figure 6.

#### VOXI

Signal input for receive side (acoustic echo canceler Sin side) VOX function.

The "1" level at VOXI indicates the presence of a voice signal, the decoder block processes normal receive signal, and the voice signal on the PCMACI pin goes through. The "0" level indicates the absence of a voice signal and the background noise generated in this device is output.

The background noise amplitude is set by the control register CR6.

Because this signal is ORed with the register bit CR6-B3, set CR6-B3 to logic "0" when using this pin.

When this pin control is not used (i.e., when controlling by the control register), set this pin to logic "0".

Refer to Figure 6.

# **ABSOLUTE MAXIMUM RATINGS**

| Parameter              | Symbol           | Condition | Rating                        | Unit |

|------------------------|------------------|-----------|-------------------------------|------|

| Power Supply Voltage   | V <sub>DD</sub>  | —         | -0.3 to +7.0                  | V    |

| Digital Input Voltage  | V <sub>DIN</sub> | _         | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Digital Output Voltage | Vout             | _         | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Storage Temperature    | T <sub>STG</sub> |           | -55 to +150                   | °C   |

# **RECOMMENDED OPERATING CONDITIONS**

|                                  |                   | (V <sub>D</sub>             | <sub>D</sub> = 4.5 V t | o 5.5 V, Ta | = -25°C to           | +70°C) |

|----------------------------------|-------------------|-----------------------------|------------------------|-------------|----------------------|--------|

| Parameter                        | Symbol            | Condition                   | Min.                   | Тур.        | Max.                 | Unit   |

| Power Supply Voltage             | V <sub>DD</sub>   | —                           | +4.5                   | _           | +5.5                 | V      |

| Operating Temperature            | Та                | —                           | -25                    | +25         | +70                  | °C     |

| Input High Voltage               | VIH               | All digital inputs          | 2.4                    | _           | V <sub>DD</sub> +0.3 | V      |

| Input Low Voltage                | VIL               | All digital inputs          | 0                      | _           | 0.8                  | V      |

| Digital Input Rise Time          | t <sub>lr</sub>   | All digital inputs          |                        |             | 5                    | ns     |

| Digital Input Fall Time          | t <sub>lf</sub>   | Measurement point=0.8V&2.4V |                        | _           | 5                    | ns     |

| Maatar Clack Fraguenov           | 4                 | MCK (When MCKSL="1")        | 100 nnm                | 19.2-20.0   | +100 ppm             | MHz    |

| Master Clock Frequency           | f <sub>MCK</sub>  | MCK (When MCKSL="0")        | –100 ppm               | 9.6-10.0    | +100 ppiii           |        |

| Master Clock Duty Ratio          | D <sub>C</sub>    | МСК                         | 40                     | 50          | 60                   | %      |

| Bit Clock Frequency              | f <sub>BCK</sub>  | BCLKP, BCLKA                | 64                     | _           | 2048                 | kHz    |

| Synchronous Pulse Frequency (*1) | f <sub>SYNC</sub> | SYNCP, SYNCA                | _                      | 8.0         | —                    | kHz    |

| Clock Duty Cycle (*2)            | D <sub>CK</sub>   | BCLKP, BCLKA                | 40                     | 50          | 60                   | %      |

|                                  | +                 | BCLKP to SYNCP,             | 100                    |             |                      | ns     |

|                                  | t <sub>XS</sub>   | BCLKA to SYNCA              |                        | _           |                      | 115    |

| Transmit Sync Pulse Setting Time | tau               | SYNCP to BCLKP,             | 100                    |             |                      | no     |

| Transmit Sync Fuise Setting Time | t <sub>SX</sub>   | SYNCA to BCLKA              | 100                    |             |                      | ns     |

|                                  | tuo               | SYNCP to BCLKP,             |                        |             | 100                  | ns     |

|                                  | t <sub>X0</sub>   | SYNCA to BCLKA              |                        |             | 100                  | 115    |

|                                  | t <sub>RS</sub>   | BCLKP to SYNCP,             | 100                    |             |                      | ns     |

|                                  | <sup>4</sup> RS   | BCLKA to SYNCA              | 100                    |             |                      | 115    |

| Receive Sync Pulse Setting Time  | t <sub>SR</sub>   | SYNCP to BCLKP,             | 100                    |             |                      | ns     |

| neceive Sync ruise Setting rime  | <sup>1</sup> SR   | SYNCA to BCLKA              | 100                    |             |                      | 115    |

|                                  | tao               | SYNCP to BCLKP,             |                        |             | 100                  | ns     |

|                                  | t <sub>R0</sub>   | SYNCA to BCLKA              |                        |             | 100                  | 115    |

| Receive Sync Pulse Setting Time  | t <sub>WS</sub>   | SYNCP, SYNCA                | 1 BCLK                 | —           | 100                  | μs     |

| PCM, ADPCM Set-up Time           | t <sub>DS</sub>   |                             | 100                    | —           | —                    | ns     |

| PCM, ADPCM Hold Time             | t <sub>DH</sub>   | <u> </u>                    | 100                    | <u> </u>    | —                    | ns     |

\*1 If SYNCP and SYNCA are generated from different clocks, be sure to keep the relative timing of the rising edges of SYNCP and SYNCA (that is, which rising edge is earlier) after releasing the reset.

\*2 The recommended condition (values) for the clock duty cycle need not be observed if the clock duty cycle fulfills the digital interface timing.

# **ELECTRICAL CHARACTERISTICS**

#### **DC** Characteristics

| $(V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, \text{ Ta} = -25 \text{ to}$ |                  |                                                                           |      |      |                 | :0 +70°C) |

|------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------|------|------|-----------------|-----------|

| Parameter                                                              | Symbol           | Condition                                                                 | Min. | Тур. | Max.            | Unit      |

| Power Supply Current 1                                                 | I <sub>DD1</sub> | Operating mode, no signal<br>(V <sub>DD</sub> =5 V)                       | —    | 50   | 80              | mA        |

| Power Supply Current 2                                                 | I <sub>DD2</sub> | Power down mode<br>(V <sub>DD</sub> =5 V, only the master clock is input) | —    | 0.2  | 1               | mA        |

| Input Leakage current                                                  | IIL              | V <sub>I</sub> = V <sub>DD</sub>                                          | -10  |      | +10             | μA        |

| High Level Digital<br>Output Voltage                                   | V <sub>OH</sub>  | I <sub>0H</sub> = -0.4 nA                                                 | 4.2  | _    | V <sub>DD</sub> | V         |

| Low Level Digital<br>Output Voltage                                    | V <sub>OL</sub>  | I <sub>0L</sub> =3.2 mA                                                   | 0    | 0.2  | 0.4             | V         |

| Digital Output<br>Leakage Current                                      | I <sub>LO</sub>  | V <sub>I</sub> =V <sub>DD</sub> /0 V                                      | _    | _    | 10              | μΑ        |

| Input Capacitance                                                      | C <sub>IN</sub>  | —                                                                         | _    | 5    | —               | pF        |

#### **Analog Interface Characteristics**

$(V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, \text{ Ta} = -25 \text{ to } +70^{\circ}\text{C})$

| Parameter           | Symbol          | Condition | Min. | Тур. | Max. | Unit |

|---------------------|-----------------|-----------|------|------|------|------|

| SG Output Voltage   | V <sub>SG</sub> | SG        | 2.35 | 2.4  | 2.45 | V    |

| SG Output Impedance | R <sub>SG</sub> | SG        |      | 40   | 80   | kΩ   |

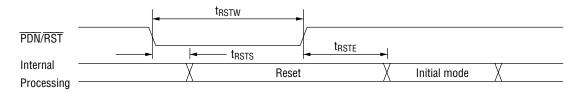

#### **Reset Timing**

$(V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, \text{ Ta} = -25 \text{ to } +70^{\circ}\text{C})$

|                        |                   |           | ( 00 - | ,    |      | /    |

|------------------------|-------------------|-----------|--------|------|------|------|

| Parameter              | Symbol            | Condition | Min.   | Тур. | Max. | Unit |

| Reset Signal Width     | t <sub>RSTW</sub> |           | 1      | —    | _    | μs   |

| Reset Start Time       | t <sub>RSTS</sub> | —         | _      | —    | 1    | μs   |

| Reset Termination Time | t <sub>RSTE</sub> |           | _      | _    | 200  | ms   |

Note: Values in the table are common to the  $\overline{PDN}/\overline{RST}$  pin and the control register bit CR0-B5.

#### • Reset timing

#### Echo Canceler Coefficient Reset Timing

|                                    |                     | (V <sub>DD</sub> = 4.5 to 5.5 V, Ta = −25 to +70 |      |      |      | +70°C) |

|------------------------------------|---------------------|--------------------------------------------------|------|------|------|--------|

| Parameter                          | Symbol              | Condition                                        | Min. | Тур. | Max. | Unit   |

| Echo Canceler Reset Signal Width   | t <sub>ECRSTW</sub> | —                                                | 125  |      | _    | μs     |

| Echo Canceler Reset Detection Time | t <sub>ECRSTD</sub> | —                                                | 0    |      | 125  | μs     |

| Echo Canceler Reset Operating Time | t <sub>ECRST</sub>  | _                                                | _    | _    | 125  | μs     |

Note: Values in the table are common to the PDN/RST pin and the control register bit CR0-B5.

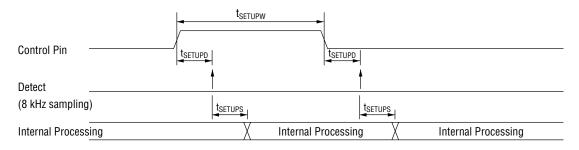

#### **Control Pin Timing**

|                               |                     |           | $(V_{DD} = 4.5)$ | to 5.5 V, I | a = -25 to | +/0°C) |

|-------------------------------|---------------------|-----------|------------------|-------------|------------|--------|

| Parameter                     | Symbol              | Condition | Min.             | Тур.        | Max.       | Unit   |

| Control Signal Width          | t <sub>SETUPW</sub> | —         | 125              | _           |            | μs     |

| Control Signal Detection Time | t <sub>SETUPD</sub> | —         | 0                | _           | 125        | μs     |

| Operation Start Time          | t <sub>SETUPS</sub> | —         | 0                | —           | 125        | μs     |

Note: The control pins / register bits are as follows: DETSL, DETT, DETP, (A/L)THR, (A/L)DCL, (A/L)CCL, (A/L)HLD, (A/L)ATT, (A/L)GC, (A/L)ATTG2-0, (A/L)ATTL2-0, PCMSL, DTHR, IOSL0-1, CINTA, MUTE, MLV0-2

#### • Control pin timing

# **Digital Interface Characteristics**

|                           |                                     |           | $(V_{DD} = 4.5)$ | to 5.5 V, | Ta = -25 1 | :o +70°C) |

|---------------------------|-------------------------------------|-----------|------------------|-----------|------------|-----------|

| Parameter                 | Symbol                              | Condition | Min.             | Тур.      | Max.       | Unit      |

| Digital Output Delay Time | t <sub>SDX</sub> , t <sub>SDR</sub> |           | 0                |           | 100        | ns        |

| PCM, ADPCM Interface      | t <sub>XD1</sub> , t <sub>RD1</sub> |           | 0                |           | 100        | ns        |

|                           | t <sub>XD2</sub> , t <sub>RD2</sub> | —         | 0                |           | 100        | ns        |

|                           | t <sub>XD3</sub> , t <sub>RD3</sub> |           | 0                | _         | 100        | ns        |

• PCM/ADPCM output timing

• PCM/ADPCM input timing

#### **AC Characteristics (Gain Settings)**

(V<sub>DD</sub> = 4.5 to 5.5 V, Ta = -25 to +70°C)

| Parameter             | Symbol | Condition               | Min. | Тур. | Max. | Unit |

|-----------------------|--------|-------------------------|------|------|------|------|

| Transmit/Receive Gain | Π.     | For all gain activation | 4    | 0    | .4   | ٩D   |

| Setting Accuracy      | $D_G$  | For all gain set values |      | U    | +1   | dB   |

#### **AC Characteristics (VOX Function)**

|                                   |                    |                   | (V <sub>DD</sub>                    | = 4.5 to \$ | 5.5 V, Ta | =25 to  | +70°C) |

|-----------------------------------|--------------------|-------------------|-------------------------------------|-------------|-----------|---------|--------|

| Parameter                         | Symbol             | -                 |                                     | Min.        | Тур.      | Max.    | Unit   |

| Transmit VOX Detection Time       | t <sub>VXON</sub>  | Silence→voice     | VOXO pin:see Fig.6<br>Voice/silence | _           | 5         | _       | ms     |

| (Voice Signal ON/OFF Detect Time) | t <sub>VXOFF</sub> | Voice→silence     | differential:10 dB                  | 140/300     | 160/320   | 180/340 | ms     |

| Transmit VOX Detection Level      |                    | For detection lev | -2.5                                | 0           | +2.5      | ٩D      |        |

| Accuracy (Voice Detection Level)  | D <sub>VX</sub>    | CR6-B6,B5         |                                     | 0           |           | dB      |        |

#### AC Characteristics (DTMF and Other Tones)

$(V_{DD} = 2.7 \text{ to } 3.6 \text{ V}, \text{ Ta} = -25 \text{ to } +70^{\circ}\text{C})$

| Parameter                    | Symbol            | C                                                                  | Condition                 | Min. | Тур. | Max. | Unit |

|------------------------------|-------------------|--------------------------------------------------------------------|---------------------------|------|------|------|------|

| Fraguency Deviation          | Df <sub>T1</sub>  | D                                                                  | -1.5                      | _    | +1.5 | %    |      |

| Frequency Deviation          | Df <sub>T2</sub>  | Other                                                              | -1.5                      |      | +1.5 | %    |      |

|                              | V <sub>TL</sub>   | Transmit side tone                                                 | DTMF (Low group)          | -10  | -8   | -6   | dBm0 |

| Tone Reference               | V <sub>TH</sub>   | (Gain set value:0dB)                                               | DTMF (High group), Others | -8   | -6   | -4   | dBm0 |

| Output Level (*1)            | V <sub>RL</sub>   | Receive side tone                                                  | DTMF (Low group)          | -10  | -8   | -6   | dBm0 |

|                              | V <sub>RH</sub>   | (Gain set value:0dB)                                               | DTMF (High group), Others | -8   | -6   | -4   | dBm0 |

| Relative Value of DTMF Tones | R <sub>DTMF</sub> | V <sub>TH</sub> /V <sub>TL,</sub> V <sub>RH</sub> /V <sub>RL</sub> |                           | 1    | 2    | 3    | dB   |

\*1 Not including programmable gain set values

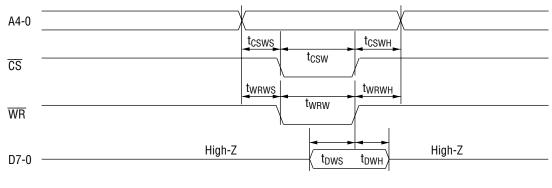

|                                                               |                  |           | (V <sub>DD</sub> = 4.5 to 5.5 V, Ta = -25 to +70 |      |      |      |  |  |  |

|---------------------------------------------------------------|------------------|-----------|--------------------------------------------------|------|------|------|--|--|--|

| Parameter                                                     | Symbol           | Condition | Min.                                             | Тур. | Max. | Unit |  |  |  |

| Address and Chip Select Setup Time                            | +                |           | 30                                               |      |      |      |  |  |  |

| (with respect to the falling edge of $\overline{\text{WR}}$ ) | t <sub>CWS</sub> |           | 30                                               |      |      |      |  |  |  |

| Address and Chip Select Setup Time                            | +.               |           | 15                                               |      |      |      |  |  |  |

| (with respect to the rising edge of $\overline{\text{WR}}$ )  | t <sub>CWH</sub> |           | 10                                               |      |      |      |  |  |  |

| WR Pulse Width                                                | t <sub>WW</sub>  |           | 45                                               | _    |      | _    |  |  |  |

| Data Input Setup Time                                         | t <sub>DWS</sub> |           | 30                                               | _    |      | _    |  |  |  |

| Data Input Hold Time                                          |                  | 15        | —                                                |      |      |      |  |  |  |

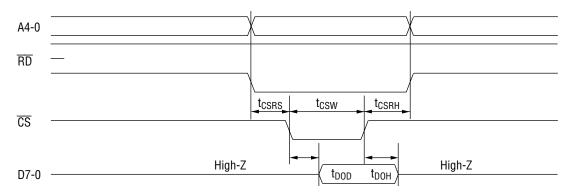

| Address and Chip Select Setup Time                            |                  | MTYPE=0   | 20                                               |      |      | ns   |  |  |  |

| (with respect to the falling edge of $\overline{\text{RD}}$ ) | t <sub>CRS</sub> |           | 30                                               |      |      |      |  |  |  |

| Address and Chip Select Setup Time                            |                  |           | 40                                               |      |      |      |  |  |  |

| (with respect to the rising edge of $\overline{\text{RD}}$ )  | tCRH             |           | 15                                               | _    |      |      |  |  |  |

| RD Pulse Width                                                | t <sub>RW</sub>  |           | 45                                               | _    |      | _    |  |  |  |

| Data Output Setup Time                                        | t <sub>DOD</sub> |           |                                                  | _    | 40   |      |  |  |  |

| Data Output Hold Time                                         | t <sub>DOH</sub> |           | 0                                                | _    |      |      |  |  |  |

# Microcontroller Interface (WR and RD Pins Controlled Independently)

# • Microcontroller write timing ( $\overline{WR}$ and $\overline{RD}$ controlled independently)

# • Microcontroller read timing ( $\overline{WR}$ and $\overline{RD}$ controlled independently)

|                                                               |                   |           | (V <sub>DD</sub> = 4.5 | to 5.5 V, T | a = –25 to | +70°C) |

|---------------------------------------------------------------|-------------------|-----------|------------------------|-------------|------------|--------|

| Parameter                                                     | Symbol            | Condition | Min.                   | Тур.        | Max.       | Unit   |

| Address Setup Time                                            | t                 |           | 30                     |             |            |        |

| (with respect to the falling edge of $\overline{\text{WR}}$ ) | t <sub>wrws</sub> |           | 30                     | _           |            |        |

| Address Setup Time                                            | +                 |           | 45                     |             |            |        |

| (with respect to the rising edge of $\overline{\text{WR}}$ )  | t <sub>WRWH</sub> |           | 15                     | _           |            |        |

| WR Pulse Width                                                | twrw              |           | 45                     | —           |            |        |

| Address Setup Time                                            |                   |           | 00                     |             |            |        |

| (with respect to the falling edge of $\overline{\text{CS}}$ ) | t <sub>CSWS</sub> |           | 30                     | _           | _          |        |

| Address Setup Time                                            | +                 | сѕwн 15   |                        |             |            |        |

| (with respect to the rising edge of $\overline{\text{CS}}$ )  | tcswn             | MTYPE=1   | 10                     | _           |            | ne     |

| CS Pulse width                                                | t <sub>CSW</sub>  |           | 45                     | —           | —          | ns     |

| Data Input Setup Time                                         | t <sub>DWS</sub>  |           | 30                     | _           |            |        |

| Data Input Hold Time                                          | t <sub>DWH</sub>  |           | 15                     | —           |            |        |

| Address Setup Time                                            | t                 |           | 30                     |             |            |        |

| (with respect to the falling edge of $\overline{\text{CS}}$ ) | t <sub>CSRS</sub> |           | 30                     | _           |            |        |

| Address Setup Time                                            | +                 |           | 15                     |             |            |        |

| (with respect to the rising edge of $\overline{\text{CS}}$ )  | t <sub>CSRH</sub> |           | 15                     |             |            |        |

| Data Output Delay Time                                        | t <sub>DOD</sub>  |           |                        | _           | 40         |        |

| Data Output Hold Time                                         | t <sub>DOH</sub>  |           | 0                      | _           | _          |        |

# Microcontroller Interface (Shared Control of WR and RD Pins)

• Microcontroller write timing (shared control of  $\overline{\text{WR}}$  and  $\overline{\text{RD}})$

• Microcontroller read timing (shared control of  $\overline{\text{WR}}$  and  $\overline{\text{RD}})$

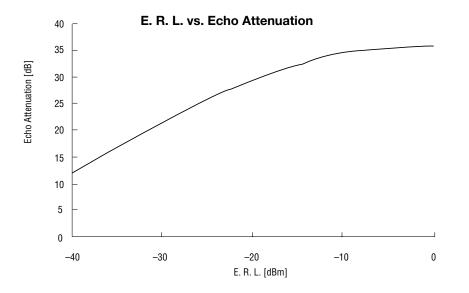

#### Echo return loss (E. R. L.) vs. echo attenuation

Conditions:

- Input level of white noise of -10 dBm, 3.4 kHz band at Rin

- Echo delay time: 2 ms

- ATT, GC, NLP: Off

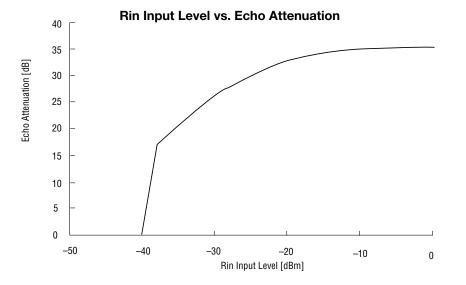

#### Rin input vs. echo attenuation

Conditions:

- Input level of 3.4 kHz-band white noise at Rin

- Echo delay time: 2 ms

- E. R. L.=–6 dBm

- ATT, GC, NLP: Off

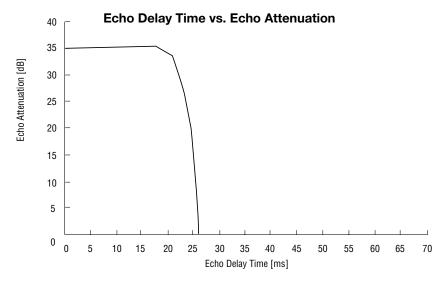

#### Echo delay time vs. echo attenuation

Conditions:

- Input level of white noise of -10 dBm, 3.4 kHz band at Rin

- E. R. L.= –6 dBm

- ATT, GC, NLP: Off ECMODE=27 ms

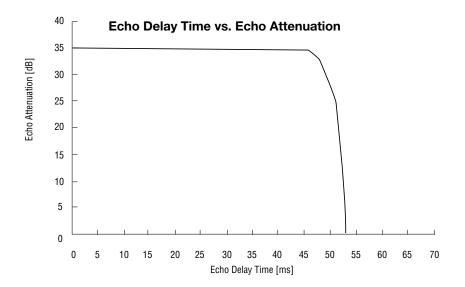

Conditions:

- Input level of white noise of -10 dBm, 3.4 kHz band at Rin

- E. R. L.= -6 dBm

- ATT, GC, NLP: Off

- ECMODE=54 ms

# **FUNCTIONAL DESCRIPTION**

# **Control Registers**

| Reg  |            | Ac         | ldre | ss |            |                    |                    |                    | Cont             | ents             |                        |                   |                   | R/W |

|------|------------|------------|------|----|------------|--------------------|--------------------|--------------------|------------------|------------------|------------------------|-------------------|-------------------|-----|

| Name | <b>A</b> 4 | <b>A</b> 3 | A2   | A1 | <b>A</b> 0 | B7                 | B6                 | B5                 | B4               | B3               | B2                     | B1                | B0                | R/W |

| CR0  | 0          | 0          | 0    | 0  | 0          |                    | PDWN               | PDN/<br>RST        |                  | OPE<br>MODE3     | OPE<br>MODE2           | OPE<br>MODE1      | OPE<br>MODE0      | R/W |

| CR1  | 0          | 0          | 0    | 0  | 1          | CONTA              | ADPCM<br>RESET     | DTHR               | TX<br>MUTE       | RX<br>MUTE       | RX<br>MLV2             | RX<br>MLV1        | RX<br>MLV0        | R/W |

| CR2  | 0          | 0          | 0    | 1  | 0          |                    |                    |                    | PCM AD<br>SEL    | PCM LN<br>SEL1   | PCM LN<br>SEL0         | PCM AC<br>SEL1    | PCM AC<br>SEL0    | R/W |

| CR3  | 0          | 0          | 0    | 1  | 1          | PCMSL              | IOSL1              | IOSL0              |                  | DETSL            | DETAUTO                | DETT              | DETP              | R/W |

| CR4  | 0          | 0          | 1    | 0  | 0          | TX TONE<br>GAIN3   | TX TONE<br>GAIN2   | TX TONE<br>GAIN1   | TX TONE<br>GAINO | RX TONE<br>GAIN3 | RX TONE<br>GAIN2       | RX TONE<br>GAIN1  | RX TONE<br>GAINO  | R/W |

| CR5  | 0          | 0          | 1    | 0  | 1          | DTMF/OTHERS<br>SEL | TX TONE<br>SEND    | RX TONE<br>SEND    | TONE4            | TONE3            | TONE2                  | TONE1             | TONE0             | R/W |

| CR6  | 0          | 0          | 1    | 1  | 0          | VOX<br>ON/OFF      | ON<br>LVL1         | ON<br>LVL0         | OFF<br>TIME      | VOX<br>IN        | RX. NOISE<br>Level sel | RX. NOISE<br>LVL1 | RX. NOISE<br>LVL0 | R/W |

| CR7  | 0          | 0          | 1    | 1  | 1          | VOX<br>OUT         | Silence Level<br>1 | Silence Level<br>O | INT              | DET<br>CPT       | DET<br>DTMF            | DETL              | DETA              | R   |

| CR8  | 0          | 1          | 0    | 0  | 0          | LTHR               | LDCL               | LCCL               | LHD              | LCLP<br>(NLP)*   | LHLD<br>(ADP)*         | LATT<br>(ATT)*    | LGC<br>(GC)*      | R/W |

| CR9  | 0          | 1          | 0    | 0  | 1          | ATHR               | ADCL               | ACCL               | AHD              | ACLP<br>(NLP)*   | AHLD<br>(APD)*         | AATT<br>(ATT)*    | AGC<br>(GC)*      | R/W |

| CR10 | 0          | 1          | 0    | 1  | 0          |                    |                    |                    | DMWR             | D TONE3          | D TONE2                | D TONE1           | D TONE0           | R/W |

| CR11 | 0          | 1          | 0    | 1  | 1          | LATTL2             | LATTL1             | LATTLO             | LATTG2           | LATTG1           | LATTGO                 |                   |                   | R/W |

| CR12 | 0          | 1          | 1    | 0  | 0          | AATTL2             | AATTL1             | AATTLO             | AATTG2           | AATTG1           | AATTG0                 |                   |                   | R/W |

| CR13 | 0          | 1          | 1    | 0  | 1          | A15                | A14                | A13                | A12              | A11              | A10                    | A9                | A8                | R/W |

| CR14 | 0          | 1          | 1    | 1  | 0          | A7                 | A6                 | A5                 | A4               | A3               | A2                     | A1                | A0                | R/W |

| CR15 | 0          | 1          | 1    | 1  | 1          | D15                | D14                | D13                | D12              | D11              | D10                    | D9                | D8                | R/W |

| CR16 | 1          | 0          | 0    | 0  | 0          | D7                 | D6                 | D5                 | D4               | D3               | D2                     | D1                | D0                | R/W |

| CR17 | 1          | 0          | 0    | 0  | 1          | —                  | _                  | _                  | —                | —                | —                      | _                 | —                 | R/W |

| CR18 | 1          | 0          | 0    | 1  | 0          | _                  | _                  | _                  | _                | _                | _                      | _                 |                   | R/W |

\*

# Table 1 Control Register Map

$R/W: Read/Write\ enable \quad R: Read\ only\ register$

: These are the symbols of control pins used in the MSM7602 (echo canceler LSI device).

|                 | B7    | B6   | B5      | B4 | B3    | B2    | B1    | B0    |

|-----------------|-------|------|---------|----|-------|-------|-------|-------|

| 000             | CRO — | PDWN |         |    | OPE   | OPE   | OPE   | OPE   |

| GRU             |       |      | PDN/RST | _  | MODE3 | MODE2 | MODE1 | MODE0 |

| Initial value * | 0     | 0    | 0       | 0  | 0     | 0     | 0     | 0     |

#### (1)CR0 (Basic operating mode settings)

\*: Indicates the value to be set when a resetting is made through the PDN/RST pin. (Also when reset by bit 5 (B5, PDN/RST), the other bits of CR0 are reset to initial values.)

#### B7... Not used

- B6... Power-down (entire system)

ORed with the inverted external power-down signals

Set the PDWN pin to "1" when this register is used. The control registers and their internal variables are retained.

- B5... Power-down reset (entire system)0: Power-on 1: Power-down reset ORed with the inverted external power-down reset signals Set the <u>PDN/RST</u> pin to "1" when this register is used. The control registers and their internal variables are reset.

#### B4... Not used

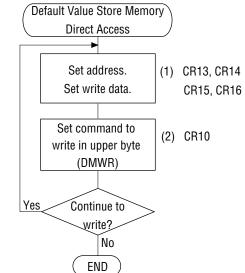

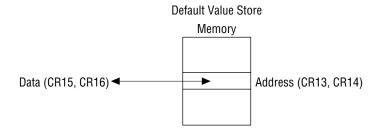

- B3, 2, 1, 0 ... Selection of an operating mode

- (0, 0, 0, 0) : Initial mode

This mode enables a change (see Fig. 5) in memory that contains internal default values such as tone generation frequencies.

In this mode, the PCM output pin acts to output idle patterns and the PCM input pin acts to input idle patterns; the echo canceler and the ADPCM transcoder do not operate. When power-down reset occurs or when power-down is released, the device enters the initial mode about 200 ms after that. When the MCUSL pin is set to "1", this mode is skipped. This mode is released by setting any of the following modes:

(0, 1, 0, 0) : Handsfree conversation mode

The tone detector, the ADPCM encoder/decoder, the tone generator, the line echo canceler, and the acoustic echo canceler become operative and can be controlled by the contents of the control registers.

(0, 1, 0, 1) : Line echo canceler expansion mode

The tone detector, the ADPCM encoder/decoder, the tone generator, and the line echo canceler (54 ms) become operative and can be controlled according to the contents of the control registers.

(Others): Not used

This register is internally processed by a logical OR of the MCUSL pin and B2, and between the ECMODE pin and B0.

|               | B7    | B6    | B5   | B4   | B3   | B2   | B1   | B0   |

|---------------|-------|-------|------|------|------|------|------|------|

| CR1           | CONTA | ADPCM | DTHR | ТΧ   | RX   | RX   | RX   | RX   |

|               |       | RESET |      | MUTE | MUTE | MLV2 | MLV1 | MLV0 |

| Initial value | 0     | 0     | 0    | 0    | 0    | 0    | 0    | 0    |

| (2) CR1 (Setting | of ADPCM o | perating mode a | and PCM I/ | O signals) |

|------------------|------------|-----------------|------------|------------|

|                  |            |                 |            |            |

B7... Control of through mode for the ADPCM CODEC0: Normal mode 1: Through modeThis bit is valid when the CONTA pin is set to "0".

B6... Transmitter/receiver ADPCM resetting (conforming to G.721) 1: Reset

B5... Control of through mode for transmit/receive signal (4-bit) through the entire circuit 0: Normal mode 1: Through mode

When set to "1", the device enters the through mode for 4-bit transmit/receive signal through the entire circuit, and the PCM input and output pins are configured to be 4-bit serial input and output. All the functions of the echo canceler, ADPCM transcoder, MUTE, and VOX become invalid. Use this bit when making 32-kbps data communication. Note that 64-kbps data communication is not supported in this device.

B4... Muting of transmitter ADPCM data 1: Mute

B3... Muting of receiver ADPCM data 1: Muting specified by bits B2, B1, and B0 is enabled. This bit is valid when the MUTE pin is set to "0".

B2, B1, B0... Setting of a receiver voice path mute level

| (MLV2, MLV1, MLV0) = | (0, 0, 0): | Through |

|----------------------|------------|---------|

|                      | (0, 0, 1): | – 6 dB  |

|                      | (0, 1, 0): | –12 dB  |

|                      | (0, 1, 1): | –18 dB  |

|                      | (1, 0, 0): | –24 dB  |

|                      | (1, 0, 1): | –30 dB  |

|                      | (1, 1, 0): | –36 dB  |

|                      | (1, 1, 1): | MUTE    |

|               | B7 | B6 | B5 | B4     | B3     | B2     | B1     | B0     |

|---------------|----|----|----|--------|--------|--------|--------|--------|

| CR2           |    |    |    | PCM AD | PCM LN | PCM LN | PCM AC | PCM AC |

|               |    | _  |    | SEL    | SEL1   | SEL0   | SEL1   | SEL0   |

| Initial value | 0  | 0  | 0  | 0      | 0      | 0      | 0      | 0      |

#### (3) CR2 (Setting of PCM I/O multiplex control)

B7, 6, 5... Not used

B4... PCMI/O multiplex timing control (PCMADI and PCMADO pins) of the ADPCM transcoder. 0: Time Slot 1 1: Time Slot 2

B3, 2... PCMI/O multiplex timing control (PCMLNI, PCMLNO pins) of the line echo canceler (See Table 2.)

B1, 0... PCM I/O multiplex timing control (PCMACI and PCMACO pins) of the acoustic echo canceler (See Table 2.)

| B3<br>(B1 | B2<br>B0) | Corresponding time slot |

|-----------|-----------|-------------------------|

| 0         | 0         | 1                       |

| 0         | 1         | 2                       |

| 1         | 0         | 3                       |

| 1         | 1         | 4                       |

#### Table 2 PCM Multiplex Timing Control Table

Note : The outputs are all in high impedance state for all time slots from the time a resetting is made to the initial mode.

#### **OKI** Semiconductor

# (4) CR3 (Setting of PCM signal I/O)

|               | B7    | B6    | B5    | B4 | B3    | B2      | B1   | B0   |

|---------------|-------|-------|-------|----|-------|---------|------|------|

| CR3           | PCMSL | IOSL1 | IOSL0 |    | DETSL | DETAUTO | DETT | DETP |

| Initial value | 0     | 0     | 0     | 0  | 0     | 0       | 0    | 0    |

B7... Reserved

B6, 5... PCM signal I/O control (see Figs. 1 to 4)

$B4\dots Not\ used$

B3, 2, 1, 0... Reserved

|               | B7      | <b>B</b> 6 | B5      | B4      | B3      | B2      | B1      | B0           |

|---------------|---------|------------|---------|---------|---------|---------|---------|--------------|

| 0.0.4         | TX TONE | TX TONE    | TX TONE | TX TONE | RX TONE | RX TONE | RX TONE | RX TONE      |

| CR4           | GAIN3   | GAIN2      | GAIN1   | GAINO   | GAIN3   | GAIN2   | GAIN1   | <b>GAINO</b> |

| Initial value | 0       | 0          | 0       | 0       | 0       | 0       | 0       | 0            |

#### (5)CR4 (Adjustment of tone generator gain)

B7, 6, 5, 4 ... Transmit side gain adjustment for the tone generator [ATTtgtx] (See Table 3.) B3, 2, 1, 0 ... Receive side gain adjustment for the tone generator [ATTtgrx] (See Table 4.)

| B7 | <b>B</b> 6 | B5 | <b>B</b> 4 | Tone generator gain | B7 | <b>B</b> 6 | B5 | B4 | Tone generator gain |

|----|------------|----|------------|---------------------|----|------------|----|----|---------------------|

| 0  | 0          | 0  | 0          | –36 dB              | 1  | 0          | 0  | 0  | –20 dB              |

| 0  | 0          | 0  | 1          | -34 dB              | 1  | 0          | 0  | 1  | –18 dB              |

| 0  | 0          | 1  | 0          | –32 dB              | 1  | 0          | 1  | 0  | -16 dB              |

| 0  | 0          | 1  | 1          | –30 dB              | 1  | 0          | 1  | 1  | -14 dB              |

| 0  | 1          | 0  | 0          | –28 dB              | 1  | 1          | 0  | 0  | -12 dB              |

| 0  | 1          | 0  | 1          | –26 dB              | 1  | 1          | 0  | 1  | -10 dB              |

| 0  | 1          | 1  | 0          | -24 dB              | 1  | 1          | 1  | 0  | 8 dB                |

| 0  | 1          | 1  | 1          | –22 dB              | 1  | 1          | 1  | 1  | 6 dB                |

#### Table 3 Setting of Transmit Side Gain of Tone Generator

| B3 | B2 | B1 | B0 | Tone generator gain | B3 | B2 | B1 | <b>B</b> 0 | Tone generator gain |

|----|----|----|----|---------------------|----|----|----|------------|---------------------|

| 0  | 0  | 0  | 0  | –36 dB              | 1  | 0  | 0  | 0          | –20 dB              |

| 0  | 0  | 0  | 1  | -34 dB              | 1  | 0  | 0  | 1          | -18 dB              |

| 0  | 0  | 1  | 0  | –32 dB              | 1  | 0  | 1  | 0          | -16 dB              |

| 0  | 0  | 1  | 1  | –30 dB              | 1  | 0  | 1  | 1          | -14 dB              |

| 0  | 1  | 0  | 0  | –28 dB              | 1  | 1  | 0  | 0          | -12 dB              |

| 0  | 1  | 0  | 1  | –26 dB              | 1  | 1  | 0  | 1          | -10 dB              |

| 0  | 1  | 1  | 0  | –24 dB              | 1  | 1  | 1  | 0          | -8 dB               |

| 0  | 1  | 1  | 1  | –22 dB              | 1  | 1  | 1  | 1          | 6 dB                |

Settings of Table 4 are made in relation to the following tone levels:

DTMF tone (Low frequency group) : -2 dBm0

DTMF tone (High frequency group) and other tone : 0 dBm0

For example, when bits B3, B2, B1, and B0 are set to "1, 1, 1, 1" (–6 dB), the PCMLNO pin outputs a tone of the following levels:

| DTMF tone (Low frequency group)                 | : –8 dBm0 |

|-------------------------------------------------|-----------|

| DTMF tone (High frequency group) and other tone | : -6 dBm0 |

The default value change command enables the gain adjustment by -1 dB step. Writing "390Ah" into the address 16Dh adds a gain of -1 dB to the values in the above table. The default value is "4000h".

|               | B7          | <b>B</b> 6 | B5      | B4    | B3    | B2    | B1    | B0    |

|---------------|-------------|------------|---------|-------|-------|-------|-------|-------|

| ODE           | DTMF/OTHERS | TX TONE    | RX TONE |       | TONE2 | TONE2 | TONE1 | TONEO |

| CR5           | SEL         | SEND       | SEND    | TONE4 | TONE3 |       |       |       |

| Initial value | 0           | 0          | 0       | 0     | 0     | 0     | 0     | 0     |

(6) CR5 (Setting of tone generator operating mode and tone frequency)

B7... Selection of DTMF signal and S stone

0: Others 1: DTMF signal

B6... Transmission of transmit side tone 0: Not transmit 1: Transmit

B5... Transmission of receive side tone 0: Not transmit 1: Transmit

B4, 3, 2, 1, 0... Setting of a tone frequency (See Table 5.)

#### Table 5 Setting of Tone Generator Frequencies

| (a) When $B7 = "1"$ | (DTMF tone) |

|---------------------|-------------|

|---------------------|-------------|

| <b>B</b> 4 | <b>B</b> 3 | B2 | B1 | <b>B</b> 0 | Description          | <b>B</b> 4 | <b>B</b> 3 | B2 | <b>B1</b> | <b>B</b> 0 | Description          |

|------------|------------|----|----|------------|----------------------|------------|------------|----|-----------|------------|----------------------|

| *          | 0          | 0  | 0  | 0          | 697 Hz + 1209 Hz (1) | *          | 1          | 0  | 0         | 0          | 852 Hz + 1209 Hz (7) |

| *          | 0          | 0  | 0  | 1          | 697 Hz + 1336 Hz (2) | *          | 1          | 0  | 0         | 1          | 852 Hz + 1336 Hz (8) |

| *          | 0          | 0  | 1  | 0          | 697 Hz + 1477 Hz (3) | *          | 1          | 0  | 1         | 0          | 852 Hz + 1477 Hz (9) |

| *          | 0          | 0  | 1  | 1          | 697 Hz + 1633 Hz (A) | *          | 1          | 0  | 1         | 1          | 852 Hz + 1633 Hz (C) |

| *          | 0          | 1  | 0  | 0          | 770 Hz + 1209 Hz (4) | *          | 1          | 1  | 0         | 0          | 941 Hz + 1209 Hz (*) |

| *          | 0          | 1  | 0  | 1          | 770 Hz + 1336 Hz (5) | *          | 1          | 1  | 0         | 1          | 941 Hz + 1336 Hz (0) |

| *          | 0          | 1  | 1  | 0          | 770 Hz + 1477 Hz (6) | *          | 1          | 1  | 1         | 0          | 941 Hz + 1477 Hz (#) |

| *          | 0          | 1  | 1  | 1          | 770 Hz + 1633 Hz (B) | *          | 1          | 1  | 1         | 1          | 941 Hz + 1633 Hz (D) |

(b) When B7 = "0" (Others)

The table below lists default frequencies. Eight tones from "10000" to "10111" are single tones. For procedures to change frequencies, see the next page.

| <b>B</b> 4 | <b>B</b> 3 | B2 | B1 | <b>B</b> 0 | Description | <b>B</b> 4 | <b>B</b> 3 | <b>B</b> 2 | B1 | <b>B</b> 0 | Description         |

|------------|------------|----|----|------------|-------------|------------|------------|------------|----|------------|---------------------|