# **OKI Semiconductor**

**FEDL7580-04** Issue Date: Aug. 12, 2004

# **MSM7580**

#### ITU-T G.721 ADPCM TRANSCODER

#### **GENERAL DESCRIPTION**

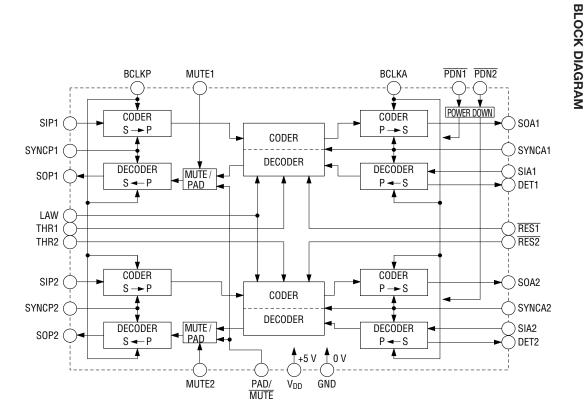

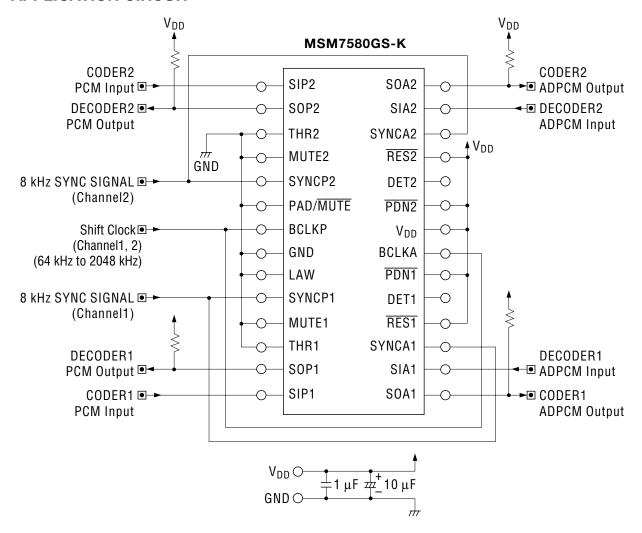

The MSM7580 is an ADPCM transcoder which is used by the new digital cordless system. It converts 64 kbps voice PCM serial data to 32 kbps ITU-T G.721 ADPCM serial data, and vice versa.

This device consists of two systems with full-duplex voice data channels and a data-through mode.

The MSM7580 provides cost effective solutions for digital cordless office telephone systems which are incorporated into PABXs and for the public base stations which are connected to the central office through digital PSTNs.

#### **FEATURES**

- Conforms to ITU-T G.721

- Built-in Full-duplex Transcoder with Two Data channels

- PCM companding Law: A-law/μ-law selectable

- Synchronized Operation between coder and decoder, and between two channels.

- Serial PCM Data Transmission Speed: 64 kbps to 2048 kbps

- Serial ADPCM Data Transmission Speed: 32 kbps to 2048 kbps

- Hardware Reset ITU-T G.721 Optional Reset for each channel

- Power Down Control for each channel

- Decoder (ADPCM → PCM ) MUTE Mode and PAD Mode for each channel

- ADPCM Data-through Mode

- Capable of time slot conversion

- Special ADPCM Input Data Code ("0000") Detector for each channel

- Master Clock Signal: Not necessary

- Power supply voltage/Consumption current :

- $+5 \text{ V} \pm 10\%$ , 2.5 mA/channel

- Package :

28-pin plastic SOP (SOP28-P-430-1.27-K) (MSM7580GS-K)

**OKI** Semiconductor

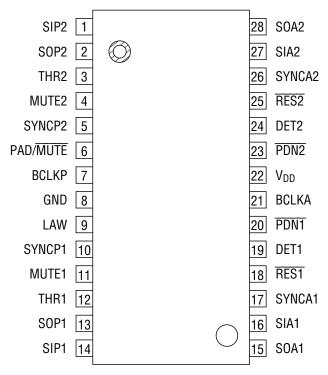

# **PIN CONFIGURATION (TOP VIEW)**

28-Pin Plastic SOP

#### PIN AND FUNCTIONAL DESCRIPTIONS

#### **GND**

Ground, 0 V.

#### SIP1, SOP1

PCM serial data input (SIP1) and output (SOP1) for Channel 1.

SOP1 is an open-drain output, which goes into a high impedance state after a continuous 8-bit serial data output.

### SIP2, SOP2

PCM serial data input (SIP2) and output (SOP2) for Channel 2.

SOP2 is an open-drain output, which goes into a high impedance state after a continuous 8-bit serial data output.

#### PAD/ MUTE

Control input for the selection of PAD or MUTE mode.

When digital "1" is input, the PAD mode is selected and when digital "0" is input, the MUTE mode is selected.

#### THR1, THR2

Control pins for the data through modes.

THR1 and THR2 are for Channel 1 and Channel 2, respectively. The data-through mode is selected when digital "1" is applied to THR1 and THR2. In this mode, 8-bit serial input data applied to SIA1 and SIA2 (ADPCM data input) is passed to the PCM serial data output pins, SOP1 and SOP2, without any data modification. SOP1 and SOP2 go to the high impedance state after the output of 8-bit data has been applied to SIA1 and SIA2.

Conversely 8-bit serial input data applied to SIP1 and SIP2 (PCM data input) is passed to ADPCM serial data output pins, SOA1 and SOA2, without any data modification.

SOA1 and SOA2 go to the high impedance state after the output of 8-bit data has been applied to SIP1 and SIP2.

Since ADPCM and PCM data interfaces have the mutually independent signal input pins for synchronizing signals the time slots for data input and output can be exchanged between them. Some timing at which data may be deleted or duplicated as described in "Notes on Usage" should not be used.

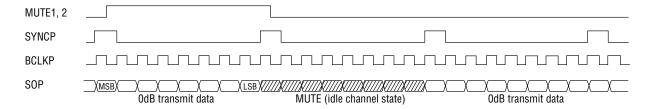

#### **MUTE1, MUTE2**

Setting a digital "1" at these pins sets the PCM output to the idle pattern state regardless of the ADPCM input data, when the MUTE mode is selected by the PAD $/\overline{\text{MUTE}}$  pin.

When the PAD mode is selected, the PCM output has a 12 dB loss.

Normally, these pins are set to a digital "0".

When the data through mode is selected, the function of these pins is invalid.

#### SYNCP1, SYNCP2

Synchronous signal input.

SYNCP1 and SYNCP2 control the PCM data input/output timing for Channel 1 (SIP1, SOP1) and Channel 2 (SIP2, SOP2), respectively.

Since other synchronous signal input pins SYNCA1 and SYNCA2 for ADPCM interfaces are also provided, the PCM and ADPCM data can be input or output with different timing.

PCM and ADPCM data interfaces can be used at a mutually independent timing except same timing.

Note: When PCM and ADPCM data interfaces are used at a mutually independent timing, the timing described in "Notes on Usage" should not be used.

#### **BCLKP**

Bit clock input.

This signal defines the PCM data transmission speed at the PCM data input/output pins. BCLKP is used for Channels 1 and 2. Since BCLKA defines the data rate of the ADPCM data interface, the PCM and ADPCM data can be input or output at different speeds.

#### **LAW**

PCM data companding law (A-law/ $\mu$ -law) selection. Digital "1" and "0" correspond to A-law and  $\mu$ -law, respectively.

#### PDN1, PDN2

Power down mode selection.

$\overline{PDN1}$  and  $\overline{PDN2}$  can be independently set to power down mode. When a digital "0" is applied, these pins are in the power-down mode.

#### SIA1, SOA1

ADPCM serial data input (SIA1) and output (SOA1) pins for Channel 1.

SOA1 is an open-drain pin and enters to the high impedance state after outputting a continuous 4-bit serial data stream. When the data-through mode is selected, SOA1 enters to the high impedance state after outputting an 8-bit serial data stream.

#### SIA2, SOA2

ADPCM serial data input (SIA2) and output (SOA2) pins for Channel 2. These pins function the same as SIA1 and SOA1.

#### SYNCA1, SYNCA2

Synchronous signal input pins.

SYNCA1 and SYNCA 2 control the ADPCM data input/output timing for Channel 1 (SIA1, SOA1) and Channel 2 (SIA2, SOA2), respectivery.

The ADPCM data can be input or output with timing other than the PCM data interface.

Therefore PCM and ADPCM interfaces can be used at a mutually independent timing except some timing.

Since master clocks are generated by the internal PLL using SYNCA, a synchronous signal should be input to there pins.

Note: When PCM and ADPCM data interfaces are used at a mutually independent timing, the timing described in "Notes on Usage" should not be used.

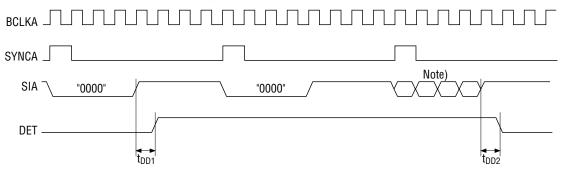

### DET1, DET2

Special ADPCM input data pattern detect pins.

When a 4-bit continuous "0" pattern at the ADPCM input pins Channel 1 (STA1) and Channel 2 (SIA2) is detected, DET1 and DET2 go from a digital "0" to a digital "1" state.

A digital "1" is output at the rising edge of the clock.

The fourth data bit (LSB) is clocked into the register by the bit clock (BCLKA) and the held there until the rising edge in the next time frame.

When detecting the special data pattern in the next time frame, the digital "1" on the pins DET (1,2) is remains. When the THR1 pin or THR2 pin is at digital "1" level, the functions of these pins are invalid.

### RES1, RES2

Algorithm reset signal input pins for Channel 1 ( $\overline{RES1}$ ) and Channel 2 ( $\overline{RES2}$ ). When a digital "0" is applied, the entire transcoder goes to its initial state. This reset is defined by ITU-T G.721 and is an optional reset.

#### **BCLKA**

Bit clock input pin used to define the data transmission speed at the ADPCM interface. This pin can be used for Channels 1 and 2, which allows the ADPCM data interface speed to be defined differently than the PCM data interface speed.

### $V_{DD}$

Power supply.

The device must operate at  $+5 \text{ V} \pm 10\%$ .

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter             | Symbol           | Condition | Rating                        | Unit |

|-----------------------|------------------|-----------|-------------------------------|------|

| Power Supply Voltage  | $V_{DD}$         | _         | 0 to 7                        | V    |

| Digital Input Voltage | V <sub>DIN</sub> | _         | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Storage Temperature   | T <sub>STG</sub> | _         | -55 to +150                   | °C   |

### RECOMMENDED OPERATING CONDITIONS

| Parameter                    | Symbol             | Condition                                    | Min.   | Тур. | Max.     | Unit |

|------------------------------|--------------------|----------------------------------------------|--------|------|----------|------|

| Power Supply Voltage         | $V_{DD}$           | _                                            | 4.5    | _    | 5.5      | V    |

| Operating Temperature        | Ta                 | _                                            | -30    | +25  | +80      | °C   |

| Digital Input High Voltage   | V <sub>IH</sub>    | All Digital Ingust Diga                      | 2.2    |      | $V_{DD}$ | V    |

| Digital Input Low Voltage    | V <sub>IL</sub>    | All Digital Input Pins                       | 0      | _    | 0.6      | V    |

| Dit Clock Fraguency          | F <sub>BCLKA</sub> | BCLKA                                        | 32     | _    | 2048     | kHz  |

| Bit Clock Frequency          | F <sub>BCLKP</sub> | BCLKP                                        | 64     |      | 2048     | kHz  |

| Synchronous Signal Frequency | Fsync              | SYNCP1, SYNCP2,<br>SYNCA1, SYNCA2            | _      | 8.0  | _        | kHz  |

| Clock Duty Ratio             | Dc                 | BCLKA, BCLKP                                 | 30     | 50   | 70       | %    |

| Digital Input Rise Time      | t <sub>lr</sub>    | ,                                            | _      |      | 50       | ns   |

| Digital Input Fall Time      | t <sub>lf</sub>    | All Digital Input Pins                       | _      |      | 50       | ns   |

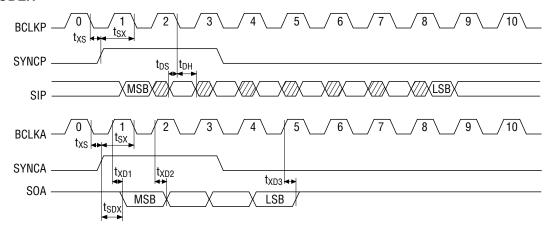

| Synchronous Signal Timing    | txs                | BCLKA, BCLKP to SYNCP                        | 100    | _    | _        | ns   |

| CODER                        | t <sub>SX</sub>    | SYNCP to BCLKA, BCLKP                        | 100    | _    | _        | ns   |

| Synchronous Signal Timing    | t <sub>SX</sub>    | BCLKA, BCLKP to SYNCA                        | 100    |      | _        | ns   |

| DECODER                      | tsR                | SYNCA to BCLKA, BCLKP                        | 100    |      | _        | ns   |

| Synchronous<br>Signal Width  | t <sub>WS</sub>    | SYNCP1, SYNCP2,<br>SYNCA1, SYNCA2            | 1 BCLK | _    | 100      | μS   |

| Data Set-up Time             | t <sub>DS</sub>    | _                                            | 100    |      | _        | ns   |

| Data Hold Time               | t <sub>DH</sub>    | _                                            | 100    | _    | _        | ns   |

| Digital Output Load          | R <sub>DL</sub>    | SOP1, SOP2, SOA1, SOA2<br>(Pull-up Resistor) | 500    |      | _        | Ω    |

| Digital Output Load          | C <sub>DL</sub>    | SOP1, SOP2, SOA1, SOA2,<br>DET1, DET2        | _      | _    | 100      | pF   |

### **ELECTRICAL CHARACTERISTICS**

### **DC Characteristics**

$(V_{DD} = 4.5 \text{ V to } 5.5 \text{ V}, Ta = -30^{\circ}\text{C to } +80^{\circ}\text{C})$

| Parameter                      | Symbol           | Condition                              | Min. | Тур | Max.     | Unit |

|--------------------------------|------------------|----------------------------------------|------|-----|----------|------|

| Power Supply Current           | I <sub>DD1</sub> | Power On Mode: 2 Channels              |      | 5   | 10       | mA   |

|                                | I <sub>DD2</sub> | Power Down Mode: 2 Channels            |      | 0.1 | 0.2      | mA   |

| Input High Voltage             | V <sub>IH</sub>  | _                                      | 2.2  | _   | $V_{DD}$ | V    |

| Input Low Voltage              | V <sub>IL</sub>  | _                                      | 0.0  | _   | 0.6      | V    |

| Input Leakage                  | Іін              | $V_I = V_{DD}$                         | _    | _   | 2.0      | μΑ   |

| Current                        | I <sub>IL</sub>  | $V_I = 0 V$                            | _    | _   | 0.5      | μΑ   |

| Digital<br>Output High Voltage | V <sub>OH</sub>  | DET1, DET2 : I <sub>OH</sub> = -0.4 mA | 2.8  | _   | $V_{DD}$ | V    |

| Digital                        | V <sub>0L1</sub> | 1 LSTTL, Pull-up : 500 Ω               | 0.0  | 0.2 | 0.4      | V    |

| Output Low Voltage             | V <sub>0L2</sub> | DET1, DET2 : I <sub>OL</sub> = 1.6 mA  | 0.0  | 0.2 | 0.4      | V    |

| Output Leakage Current         | I <sub>OL</sub>  | SOP1, SOP2, SOA1, SOA2                 | _    | _   | 10       | μΑ   |

| Input Capacitance              | C <sub>IN</sub>  | _                                      |      | 5   | _        | pF   |

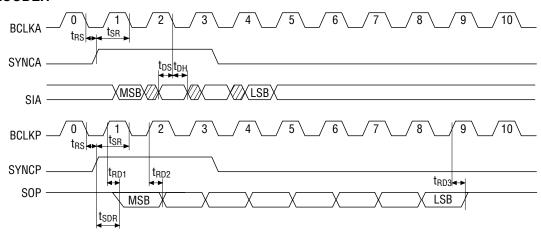

### **AC Characteristics**

$(V_{DD} = 4.5 \text{ V to } 5.5 \text{ V,Ta} = -30^{\circ}\text{C to } +80^{\circ}\text{C})$

| , 22                      |                                     |                                    |      |      |      |      |

|---------------------------|-------------------------------------|------------------------------------|------|------|------|------|

| Parameter                 | Symbol                              | Condition                          | Min. | Тур. | Max. | Unit |

| Digital Output Delay Time | t <sub>SDX</sub>                    | 1 LSTTL + 100 pF<br>Pull-up: 500 Ω | 0    | _    | 200  | ns   |

|                           | t <sub>SDR</sub>                    |                                    | 0    | _    | 200  | ns   |

|                           | t <sub>XD1</sub> , t <sub>RD1</sub> |                                    | 0    | _    | 200  | ns   |

|                           | txd2, trd2                          |                                    | 0    | _    | 200  | ns   |

|                           | t <sub>XD3</sub> , t <sub>RD3</sub> |                                    | 0    | _    | 200  | ns   |

|                           | t <sub>DD1</sub>                    |                                    | 0    |      | 200  | ns   |

|                           | t <sub>DD2</sub>                    |                                    | 0    | _    | 200  | ns   |

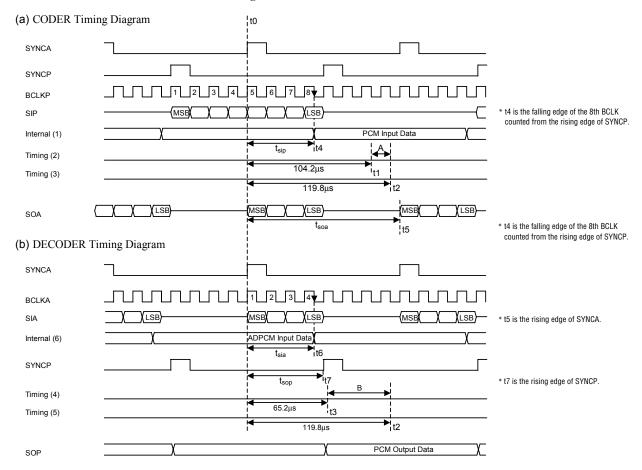

### **TIMING DIAGRAM**

### **CODER**

#### **DECODER**

### **DET ("0000" detection) Output Timing**

Note: 4-bit data pattern except "0000"

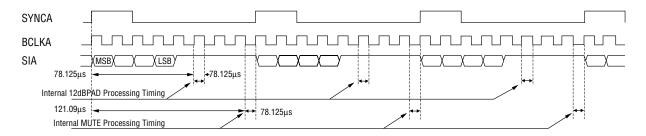

### **PAD/MUTE Processing Timing**

### PAD Mode; MUTE1 and MUTE 2 Timings PAD/MUTE="H"

### MUTE Mode; MUTE1 and MUTE 2 Timings PAD/MUTE="L"

As mentioned above, PAD and MUTE processings are carried out according to the rising edge of SYNCA.

Even if BCLK is not 128 kHz, these processings are performed in the absolute time counted from the rising edge of SYNCA.

Therefore, MUTE1 and MUTE 2 pins must be controlled so as to cover there processings.

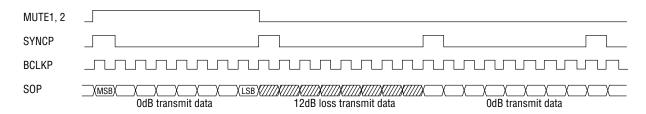

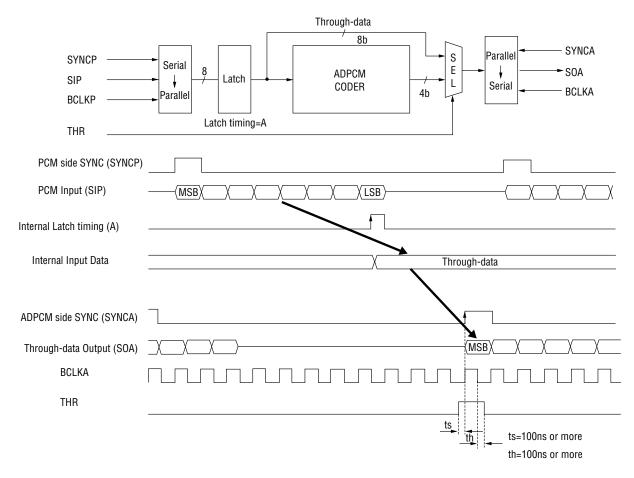

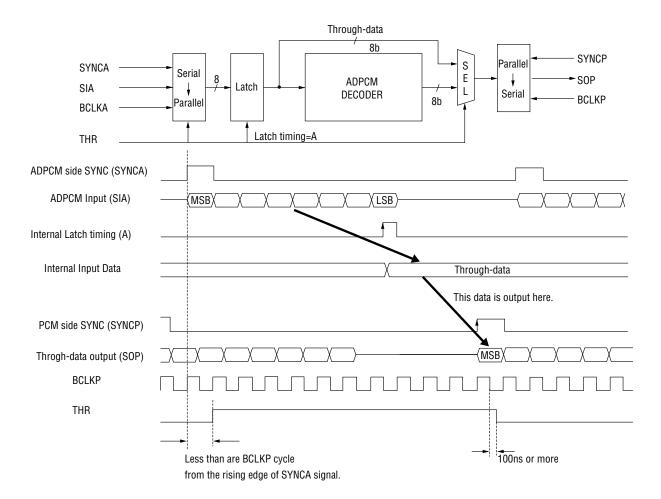

### **THR Processing Timing**

Timing Block Diagrams, when CODER and DECODER output data, are shown in the following figures.

The parallel to serial conversion of the output unit employs a load format and the load point is at the rising edge of a synchronous signal.

Therefore, input THR signal with respect to SYNCA for CODER with timing of satisfying ts and th conditions shown in the figure.

For DECODER, THR signal should be input even when through-data is input.

The input timing should satisfy the conditions shown in the following figures.

#### **CODER**

Note: That data-ship may occur when the rising edge (data load point) of SYNCA and input of the internal latch timing overlap each other.

### **DECODER**

### **APPLICATION CIRCUIT**

### **NOTES ON USAGE**

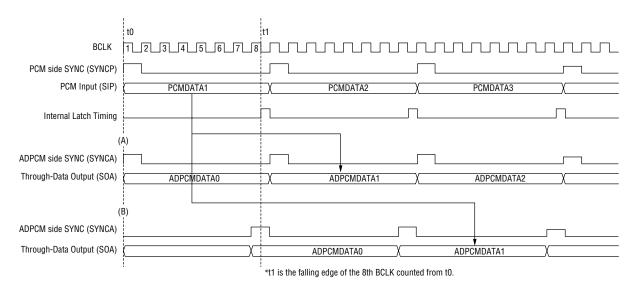

### (1) Through Mode (CODER Side)

- (A) When SYNCA rises after t1, PCMDATA1 is output to ADPCMDATA1.

- (B) When SYNCA rises before t1, PCMDATA1 is output to ADPCMDATA1.

If SYNCA rises near the t1 and jitter occurs, data slip may occur. Therefore SYNCA should not rise in the range of ±500ns from t1. Data slip means that data is deleted or the same data is output twice.

### (2) Through Mode (DECODER Side)

- (A) When SYNCA rises after t1, ADPCMDATA1 is output to PCMDATA1.

- (B) When SYNCA rises before t1, ADPCMDATA1 is output to PCMDATA1.

If SYNCP rises near the t1 and jitter occurs, data slip may occur. Therefore SYNCA should not rise in the range of ±500ns from t1. Data slip means that data is deleted or the same data is output twice.

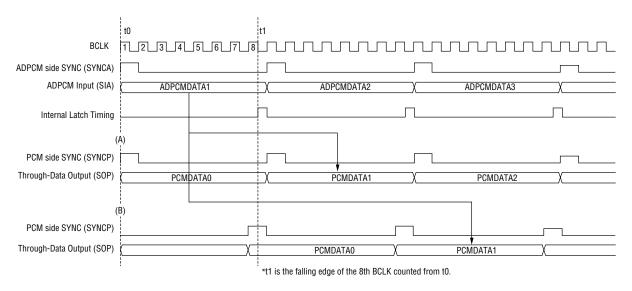

### (3) PCM→ADPCM, ADPCM→PCM during Transcode

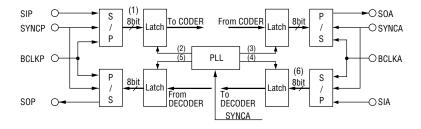

#### (c) Internal Circuit Configuration

In this device, internal operating signals are generated according to the ADPCM side SYNC (SYNCA) signal.

The timings are shouwn in the figures (a) and (b);

The arithmetic operation of CODER is performed at "A" in the figure (a).

The arithmetic operation of DECODER is performed at "B" in the figure (b).

Therefore, when the conversion delay time Tsip of the CODER is less than t1, ADPCM is output at the timing of Tsoa.

When Tsip is more than t1, ADPCM is output at the timing of Tsoa + 125µs.

For DECODER, when Tsia<t3 and Tsop<t2, the conversion delay time is Tsop-Tsia.

As mentioned above, a data ship may occur at Tsip=t1 in CODER, and at Tsia=t3 and Tsop=t2 in DECODER.

Therefore, the timings of SYNC signals of both PCM and ADPCM sides should not be set up in the range about ±500nsec of Tsip=t1, Tsia=t3 and Tsop=t2.

For normal operation, SYNC clocks for ADPCM and PCM sides should be continuous at 8 kHz and synchronized with each other even if their phases are different.

#### PACKAGE DIMENSIONS

SOP28-P-430-1.27-K

Package material Epoxy resin

Lead frame material 42 alloy

Pin treatment Solder plating (≥5µm)

Package weight (g) 0.75 TYP.

Oki Electric Industry Co.,Ltd.

0.4 ± 0.1 0.25M

0.15 ± 0.05

888

1.27

Notes for Mounting the Surface Mount Type Package

11.8 ± 0.3 8.8 ± 0.1

Mirror finish 1.0 TYP.

The surface mount type packages are very susceptible to heat in reflow mounting and humidity absorbed in storage. Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

## **REVISION HISTORY**

| Document      |               | Page                |                    |                                                                               |  |

|---------------|---------------|---------------------|--------------------|-------------------------------------------------------------------------------|--|

| No.           | Date          | Previous<br>Edition | Current<br>Edition | Description                                                                   |  |

| E2U0031-39-61 | Jun. 1999     | _                   | _                  | Final edition 3                                                               |  |

| FEDL7580-04   | Aug. 12, 2004 | _                   | _                  | Final edition 4                                                               |  |

|               |               | 15                  | 15                 | Modified Sections (a), CODER Timing Diagram, and (b), DECODER Timing Diagram. |  |

### **NOTICE**

The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not, unless specifically authorized by Oki, authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans.Such applications include, but are not limited to, traffic and automotive equipment, safety devices,

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

aerospace equipment, nuclear power control, medical equipment, and life-support systems.

8. No part of the contents contained herein may be reprinted or reproduced without our prior permission.

Copyright 2004 Oki Electric Industry Co., Ltd.