# 0.8µm Mixed 3-V/5-V MSM38S0000 Sea of Gates and MSM98S000 Customer Structured Arrays

February 1995

#### **TRADEMARKS**

AIX, DOS, PC, and Windows are trademarks, and IBM is a registered trademark of IBM Corporation Apollo, Domain, and DomainOS are trademarks of Apollo Computer, a subsidiary of Hewlett-Packard AutoLogic, IDEA, QuickFault, QuickGrade, QuickPath, QuickSim, and Mentor Graphics are trademarks of Mentor Graphics Corporation

Composer, Concept, HDL, Leapfrog, PLI, Veritime, and VHDL are trademarks, and Cadence, DRACULA, TestScan, Verifault, and Verilog are registered trademarks of Cadence Design Systems, Inc.

Design Compiler, HDL/VHDL Compiler, Test Compiler, and VSS are trademarks of Synopsys, Inc.

HP and HP-UX are trademarks of Hewlett-Packard Company

Alchemy and IKOS are trademarks of IKOS Systems, Inc.

Powerview, Viewlogic, ViewRetargeter, ViewSim, ViewSynthesis, and Workview are trademarks of Viewlogic Systems, Inc.

Solaris, Sun, Sun-3, Sun-4, and SunOS are trademarks of Sun Microsystems, Inc.

$UNIX\ is\ a\ registered\ trademark\ of\ UNIX\ System\ Laboratories,\ Inc.$

All other products or services mentioned in this document are identified by the trademarks, service marks, or product names as designated by the companies who market those products. Inquiries concerning such trademarks should be made directly to those companies.

OKI Semiconductor reserves the right to make changes in specifications at anytime and without notice. This information furnished by OKI Semiconductor in this publication is believed to be accurate and reliable. However, no responsibility is assumed by OKI Semiconductor for its use; nor for any infringements of patents or other rights of third parties resulting from its use. No license is granted under any patents or patent rights of OKI.

# MSM38S0000/MSM98S000

# 0.8µm Mixed 3-V/5-V Sea of Gates and Customer Structured Arrays

#### DESCRIPTION

OKI's 0.8 $\mu$ m ASIC products, specially designed for mixed 3-V/5-V applications, are now available in both Sea Of Gates (SOG) and Customer Structured Array (CSA) architectures. Both the SOG-based MSM38S Series and the CSA-based MSM98S Series use a three-layer-metal process on 0.8 $\mu$ m drawn (0.6 $\mu$ m L-effective) CMOS technology. The semiconductor process is adapted from OKI's production-proven 16-Mbit DRAM manufacturing process.

Ideal for low-power portable applications, the MSM38S/98S are constructed with separate power busses for internal core logic and configurable I/O functions. Altogether, the architecture provides maximum flexibility, meeting the needs of all 3-V, 5-V, and mixed 3-V/5-V signal requirements.

The MSM38S SOG Series is available in seven sizes with up to 420 I/O pads and over 135,000 usable gates. SOG array sizes are designed to fit the most popular quad flat pack (QFP) packages, such as 100-, 136-, 160-, and 208-pin QFPs. MSM38S SOG-based designs are therefore ideal for pad-limited circuits that require rapid prototyping turnaround times.

The MSM98S CSA Series is an all-mask-level superset of the SOG series, available in 29 sizes. The CSA offerings combine the SOG architecture's logic flexibility with the higher integration yielded by optimized diffusion for faster and more compact memory blocks. The MSM98S is ideal for core-limited applications or circuits with large and/or multiple memory functions. Customer modification to the structure of any of the 29 predefined masterslices, rather than creation of a new masterslice every time, improves the prototyping turnaround time over cell-based manufacturing techniques.

Both product families are supported by OKI's proprietary MEMGEN tool which quickly and easily generates SOG memories (for the MSM38S) as well as optimized memories for the MSM98S Series. The families also feature floorplanning to control pre-layout timing, clock-skew management software that guarantees worst-case clock skew of 1 ns or less, and scan-path design techniques that support ATVG for fault coverage approaching 100%.

#### **FFATURES**

- 0.8µm drawn three-layer metal CMOS

- Mixed 3-V/5-V operation for low power and high speed

- SOG and CSA architecture availability

- Clock tree cells with ≤ 1.0-ns clock skew, worst-case (fan-out = 2000 at 70 MHz)

- Usable density from 6.5k to 135k gates

- I/Os may be VSS, 3 V, 5 V, VDD, CMOS, TTL, and 3state. with 2-mA to 48-mA drive

- I/O level shifter cells, allowing any buffer (input, output, or bidirectional) to interface with 3 V or 5 V

- Slew-rate-controlled outputs for low radiated noise

- User-configurable single and multi-port memories

- Specialized 3-V and 5-V macrocells, including phaselocked loop, and PCI cells

- Floorplanning for front-end simulation and back-end layout controls

- JTAG boundary scan and scan-path ATVG

# MSM38S/98S FAMILY LISTING

| CSA Part #<br>MSM | SOG Part #<br>MSM | I/O Pads | Rows <sup>[1]</sup> | Columns | Raw Gates | Usable Gates [2] |

|-------------------|-------------------|----------|---------------------|---------|-----------|------------------|

| 98S020x020        | _                 | 80       | 44                  | 148     | 6,512     | 4,689            |

| 98S023x023        | _                 | 92       | 51                  | 176     | 8,976     | 6,463            |

| _                 | 38S0110           | 100      | 56                  | 194     | 10,752    | 7,741            |

| 98S026x026        | _                 | 104      | 59                  | 200     | 11,800    | 8,496            |

| 98S029x029        | _                 | 116      | 66                  | 228     | 15,048    | 10,835           |

| 98S032x032        | _                 | 128      | 74                  | 252     | 18,648    | 13,427           |

| _                 | 38S0210           | 136      | 79                  | 270     | 21,172    | 15,244           |

| 98S035x035        | _                 | 140      | 81                  | 276     | 22,356    | 16,096           |

| 98S038x038        | _                 | 152      | 89                  | 304     | 27,056    | 19,480           |

| _                 | 38S0300           | 160      | 94                  | 322     | 30,080    | 21,658           |

| 98S041x041        | _                 | 164      | 96                  | 328     | 31,488    | 22,671           |

| 98S044x044        | _                 | 176      | 104                 | 356     | 37,024    | 25,917           |

| 98S047x047        | _                 | 188      | 111                 | 380     | 42,180    | 29,526           |

| 98S050x050        | _                 | 200      | 119                 | 408     | 48,552    | 33,986           |

| 98S053x053        | _                 | 212      | 126                 | 432     | 54,432    | 38,102           |

| _                 | 38S0570           | 216      | 129                 | 442     | 56,760    | 39,732           |

| 98S056x056        | _                 | 224      | 134                 | 456     | 61,104    | 42,162           |

| 98S059x059        | _                 | 236      | 141                 | 484     | 68,244    | 47,088           |

| 98S062x062        | _                 | 248      | 149                 | 508     | 75,692    | 51,471           |

| 98S065x065        | _                 | 260      | 156                 | 536     | 83,616    | 56,859           |

| 98S068x068        | _                 | 272      | 164                 | 560     | 91,840    | 62,451           |

| _                 | 38S0980           | 280      | 169                 | 580     | 97,344    | 66,194           |

| 98S071x071        | _                 | 284      | 171                 | 588     | 100,548   | 67,367           |

| 98S074x074        | _                 | 296      | 179                 | 612     | 109,548   | 72,302           |

| 98S077x077        | _                 | 308      | 186                 | 636     | 118,296   | 75,709           |

| 98S080x080        | _                 | 320      | 194                 | 664     | 128,816   | 82,442           |

| 98S083x083        | _                 | 332      | 201                 | 688     | 138,288   | 88,504           |

| 98S086x086        | 38S1500           | 344      | 209                 | 716     | 149,644   | 95,772           |

| 98S089x089        | _                 | 356      | 216                 | 740     | 159,840   | 99,101           |

| 98S092x092        | _                 | 368      | 224                 | 768     | 172,032   | 103,219          |

| 98S095x095        | _                 | 380      | 231                 | 792     | 182,952   | 109,771          |

| 98S098x098        | _                 | 392      | 239                 | 816     | 195,024   | 117,014          |

| 98S101x101        | _                 | 404      | 246                 | 844     | 207,624   | 124,574          |

| 98S104x104        | _                 | 416      | 254                 | 868     | 220,472   | 132,283          |

| _                 | 38\$2250          | 420      | 256                 | 880     | 224,256   | 134,554          |

<sup>[1]</sup> Row and column numbers are used to evaluate the number and size of mega macrocells that may be included into each array. For example, a 7,600-gate mega macrocell with a size and aspect ratio of 36 rows by 245 columns can be used on the MSM98S032x032 or any larger array base, but not on the MSM98S029x029.

2

<sup>[2]</sup> Usable gate count is design dependent and varies based upon the number of fan-outs per net, internal busses, floor plan, RAM/ROM blocks, etc.

#### ARRAY ARCHITECTURE

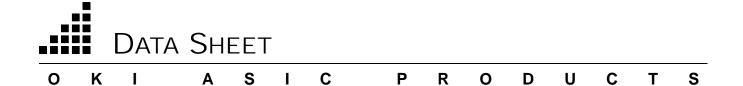

The primary components of a 0.8µm MSM38S/98S circuit include:

- I/O base cells

- Configurable I/O pads for V<sub>DD</sub>, V<sub>SS</sub>, or I/O (I/O in both 3V and 5V)

- V<sub>DD</sub> and V<sub>SS</sub> pads dedicated to wafer probing

- · Separate power bus for output buffers

- · Separate power bus for internal core logic and input buffers

- Core base cells containing N-channel and P-channel pairs, arranged in column of gates

- · Isolated gate structure for reduced input capacitance and increased routing flexibility

Each array has 16 dedicated corner pads for power and ground use during wafer probing, with four pads per corner. The arrays also have separate power rings for the internal core functions ( $V_{DDC}$  and  $V_{SSC}$ ) and output drive transistors ( $V_{DDO}$  for 3 V and  $V_{SSO}$ ).

Figure 1. MSM38S/98S Array Architecture

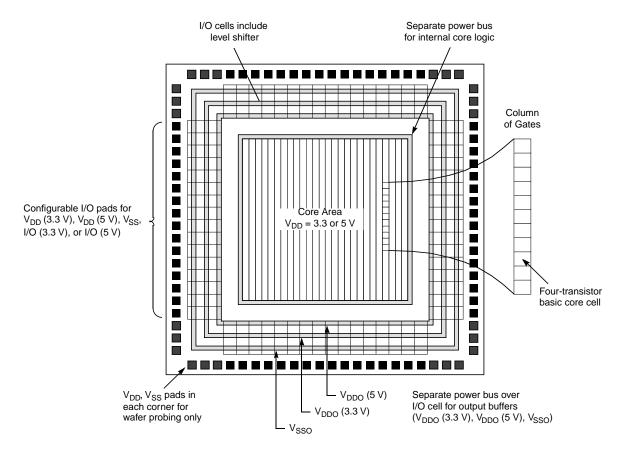

MSM98S000 CSA Layout Methodology

The procedure to design, place, and route a CSA follows.

- 1. Select suitable base array frame from the available predefined sizes. To select an array size:

- Identify the macrocell functions required and the minimum array size to hold the macrocell functions.

- Add together all the area occupied by the required random logic and macrocells and select the optimum array.

- 2. Make a floor plan for the design's megacells.

- OKI Design Center engineers verify the master slice and review simulation.

- OKI Design Center engineers floorplan the array using OKI's proprietary floorplanner and customer performance specifications.

- Using OKI CAD software, Design Center engineers remove the SOG transistors and replace them with diffused memory macrocells to the customer's specifications.

Figure 2shows an array base after placement of the optimized memory macrocells.

Figure 2. Optimized Memory Macrocell Floor Plan

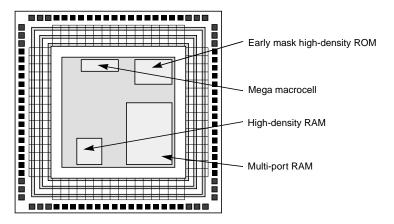

- 3. Place and route logic into the array transistors.

- OKI Design Center engineers use layout software and customer performance specifications to connect the random logic and optimized memory macrocells.

Figure 3 marks the area in which placement and routing is performed with light shading.

Figure 3. Random Logic Place and Route

## **ELECTRICAL CHARACTERISTICS**

## **Absolute Maximum Ratings**

| Parameter                        | Symbol           | Conditions [1]               | Value                        | Unit |

|----------------------------------|------------------|------------------------------|------------------------------|------|

| Power supply voltage             | $V_{DD}$         | T <sub>j</sub> = 25° C       | -0.5 to +6.5                 | V    |

| Input voltage                    | V <sub>I</sub>   | $\vec{V}_{SS} = 0 \text{ V}$ | -0.5 to V <sub>DD</sub> +0.5 | V    |

| Output voltage                   | V <sub>O</sub>   |                              | -0.5 to V <sub>DD</sub> +0.5 | V    |

| Output current per I/O base cell | I <sub>0</sub>   |                              | -24 to + 24                  | mA   |

| Current per power PAD            | I <sub>PAD</sub> |                              | -90 to +90                   | mA   |

| Storage temperature              | T <sub>stg</sub> | -                            | -65 to +150                  | ° C  |

<sup>[1]</sup> Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the other sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# Recommended Operating Conditions ( $V_{SS} = 0 V$ )

| Parameter                                         | Symbol                            | Min | Тур | Max | Unit |

|---------------------------------------------------|-----------------------------------|-----|-----|-----|------|

| Power supply voltage                              | $V_{DD}$                          | 2.7 | 3.3 | 3.6 | V    |

|                                                   |                                   | 4.5 | 5.0 | 5.5 | V    |

| Operating temperature                             | Ta                                | -40 | +25 | +85 | °C   |

| Input rise/fall time (normal type)[1][2]          | tr <sub>A</sub> , tf <sub>A</sub> | -   | 2   | 500 | ns   |

|                                                   | tr <sub>B</sub> , tf <sub>B</sub> | -   | 2   | 500 | ns   |

| Input rise/fall time (Schmitt Trigger type)[3][4] | tr <sub>C</sub> , tf <sub>C</sub> | _   | -   | 60  | μs   |

|                                                   | tr <sub>D</sub> , tf <sub>D</sub> | -   | -   | 200 | μs   |

<sup>[1]</sup>  $tr_A$ ,  $tf_A - TTL$  interface, normal input buffer.

# Operating Range (V<sub>SS</sub> = 0 V)

| Parameter                 | Symbol           | Rated Value  | Unit |

|---------------------------|------------------|--------------|------|

| Supply voltage            | $V_{DD}$         | 2.7 to 5.5   | V    |

| Ambient temperature       | Ta               | -40 to +85   | ° C  |

| Oscillation frequency [1] | f <sub>OSC</sub> | 30 k to 50 M | Hz   |

<sup>[1] 50-</sup>MHz oscillator frequency for  $V_{DD}$  is 4.5 ~ 5.5 V.

$<sup>\</sup>label{eq:thmost} \mbox{[2]} \quad \mbox{tr}_{\mbox{\footnotesize{B}}}, \mbox{tf}_{\mbox{\footnotesize{B}}} - \mbox{\footnotesize{CMOS}} \mbox{ interface, normal input buffer.}$

<sup>[3]</sup>  $tr_C$ ,  $tf_C$  – TTL interface, Schmitt Trigger input buffer.

<sup>[4]</sup>  $tr_D$ ,  $tf_D$  – CMOS interface, Schmitt Trigger input buffer.

# **DC Characteristics**

$(V_{DD} = 4.5 \sim 5.5 \text{ V}, V_{SS} = 0 \text{ V}, T_j = -40^{\circ} \text{ C} \sim +85^{\circ} \text{ C})$

|                                                   |                  |                                                         |                      | Rated Value        |                      |      |

|---------------------------------------------------|------------------|---------------------------------------------------------|----------------------|--------------------|----------------------|------|

| Parameter                                         | Symbol           | Conditions                                              | Min                  | Typ <sup>[1]</sup> | Max                  | Unit |

| High-level input voltage                          | V <sub>IH</sub>  | TTL input                                               | 2.2                  | -                  | V <sub>DD</sub> +0.5 | V    |

|                                                   |                  | CMOS input                                              | 0.7xV <sub>DD</sub>  | -                  |                      | V    |

| Low-level input voltage                           | V <sub>IL</sub>  | TTL input                                               | -0.5                 | -                  | 0.8                  | V    |

|                                                   |                  | CMOS input                                              | -0.5                 | -                  | 0.3xV <sub>DD</sub>  | V    |

| TTL-level Schmitt Trigger input threshold voltage | $V_{t+}$         | -                                                       | -                    | 1.7                | 2.2                  | V    |

|                                                   | V <sub>t-</sub>  | -                                                       | 0.8                  | 1.3                | -                    | V    |

|                                                   | ΔVT              | V <sub>t+</sub> - V <sub>t-</sub>                       | 0.2                  | 0.4                | -                    | V    |

| CMOS-level Schmitt Trigger input threshold        | V <sub>t+</sub>  | -                                                       | -                    | 3.1                | 0.76xV <sub>DD</sub> | V    |

| voltage                                           | V <sub>t-</sub>  | -                                                       | 0.24xV <sub>DD</sub> | 1.8                | -                    | V    |

|                                                   | ΔVΤ              | V <sub>t+</sub> - V <sub>t-</sub>                       | 0.6                  | 1.3                | -                    | V    |

| High-level output voltage                         | V <sub>OH</sub>  | I <sub>OH</sub> = 2, 4, 8, 12, 16, 24 mA                | 3.7                  | -                  | -                    | V    |

| Low-level output voltage                          | V <sub>OL</sub>  | I <sub>OL</sub> = 2, 4, 8, 12, 16, 24 mA                | -                    | -                  | 0.4                  | V    |

|                                                   |                  | I <sub>OL</sub> = 48 mA                                 | -                    | -                  | 0.5                  | V    |

| High-level input current                          | I <sub>IH</sub>  | $V_{IH} = V_{DD}$                                       | -                    | 0.01               | 10                   | μΑ   |

|                                                   |                  | $V_{IH} = V_{DD}(50 \text{ k}\Omega \text{ pull down})$ | 20                   | 100                | 250                  | μΑ   |

| Low-level input current                           | I <sub>IL</sub>  | $V_{IL} = V_{SS}$                                       | -10                  | -0.01              | -                    | μA   |

|                                                   |                  | $V_{IL} = V_{SS}$ (50 k $\Omega$ pull up)               | -250                 | -100               | -20                  | μA   |

|                                                   |                  | $V_{IL} = V_{SS} (3 \text{ k}\Omega \text{ pull up})$   | -5                   | -1.6               | -0.5                 | mA   |

| 3-state output leakage current                    | IOZ <sub>H</sub> | $V_{OH} = V_{DD}$                                       | -                    | 0.01               | 10                   | μA   |

|                                                   | IOZ <sub>L</sub> | $V_{OL} = V_{SS}$                                       | -10                  | -0.01              | -                    | μA   |

|                                                   |                  | $V_{OL} = V_{SS}$ (50 k $\Omega$ pull up)               | -250                 | -100               | -20                  | μA   |

|                                                   |                  | $V_{OL} = V_{SS}$ (3 k $\Omega$ pull up)                | -5                   | -1.6               | -0.5                 | mA   |

| Stand-by current <sup>[2]</sup>                   | I <sub>DDS</sub> | Output open $V_{IH} = V_{DD}$ , $V_{IL} = V_{SS}$       | _                    | 0.1                | 100                  | μΑ   |

<sup>[1]</sup> Typical condition is  $V_{DD}$  = 5.0 V and  $T_j$  = 25° C for a typical process. [2] RAM/ROM should be in power-down mode.

# **DC Characteristics**

$(V_{DD} = 2.7 \sim 3.6 \text{ V}, V_{SS} = 0 \text{ V}, T_j = -40^{\circ} \text{ C} \sim +85^{\circ} \text{ C})$

|                                            |                  |                                                   |                      | Rated Value        |                      |      |

|--------------------------------------------|------------------|---------------------------------------------------|----------------------|--------------------|----------------------|------|

| Parameter                                  | Symbol           | Conditions                                        | Min                  | Typ <sup>[1]</sup> | Max                  | Unit |

| High-level input voltage                   | V <sub>IH</sub>  | CMOS input                                        | 0.7xV <sub>DD</sub>  | -                  | V <sub>DD</sub> +0.5 | V    |

| Low-level input voltage                    | V <sub>IL</sub>  | CMOS input                                        | -0.5                 | -                  | 0.3xV <sub>DD</sub>  | V    |

| CMOS-level Schmitt Trigger input threshold | V <sub>t+</sub>  | -                                                 | -                    | 2                  | 0.76xV <sub>DD</sub> | V    |

| voltage                                    | V <sub>t-</sub>  | -                                                 | 0.24xV <sub>DD</sub> | 1                  | -                    | V    |

|                                            | ΔVT              | $V_{t+}$ - $V_{t-}$                               | 0.1xV <sub>DD</sub>  | 1                  | -                    | V    |

| High-level output voltage                  | V <sub>OH</sub>  | I <sub>OH</sub> = 1, 2, 4, 6, 8, 12 mA            | 2.2                  | -                  | -                    | V    |

| Low-level output voltage                   | V <sub>OL</sub>  | I <sub>OL</sub> = 1, 2, 4, 6, 8, 12, 24 mA        | -                    | -                  | 0.4                  | V    |

| High-level input current                   | I <sub>IH</sub>  | V <sub>IH</sub> = V <sub>DD</sub>                 | -                    | 0.01               | 1                    | μA   |

|                                            |                  | $V_{IH} = V_{DD}$ (100 k $\Omega$ pull down)      | 5                    | 35                 | 120                  | μA   |

| Low-level input current                    | I <sub>IL</sub>  | $V_{IL} = V_{SS}$                                 | -1                   | -0.01              | -                    | μΑ   |

|                                            |                  | $V_{IL} = V_{SS}$ (100 k $\Omega$ pull up)        | -120                 | -35                | -5                   | μA   |

|                                            |                  | $V_{IL} = V_{SS}$ (6 k $\Omega$ pull up)          | -2                   | 55                 | 120                  | mA   |

| 3-state output leakage current             | IOZ <sub>H</sub> | $V_{OH} = V_{DD}$                                 | -                    | 0.01               | 1                    | μA   |

|                                            | IOZ <sub>L</sub> | $V_{OL} = V_{SS}$                                 | -1                   | -0.01              | -                    | μA   |

|                                            |                  | $V_{OL} = V_{SS}$ (100 k $\Omega$ pull up)        | -120                 | -35                | -5                   | μΑ   |

|                                            |                  | $V_{OL} = V_{SS}$ (6 k $\Omega$ pull up)          | -2                   | 55                 | 12                   | mA   |

| Stand-by current <sup>[2]</sup>            | I <sub>DDS</sub> | Output open $V_{IH} = V_{DD}$ , $V_{IL} = V_{SS}$ | -                    | 0.1                | 10                   | μA   |

$<sup>\</sup>label{eq:total_power_state} \begin{tabular}{ll} [1] & Typical condition is $V_{DD}=3.3$ V and $T_j=25^\circ$ C for a typical process. \\ [2] & RAM/ROM should be in power-down mode. \\ \end{tabular}$

# AC Characteristics (Core $V_{DD} = 5 \text{ V}$ , $V_{SS} = 0 \text{ V}$ , $T_i = 25^{\circ} \text{ C}$ )

| Param                       | eter                                      | Driving Type                        | Conditions                                                                   | Rated Value [1][2]                | Unit |

|-----------------------------|-------------------------------------------|-------------------------------------|------------------------------------------------------------------------------|-----------------------------------|------|

| Internal gate delay times   | Inverter<br>2-input NAND<br>2-input NOR   | 1x<br>1x<br>1x                      | Input tr/tf = V <sub>DD</sub> /1.0 ns<br>Output loading:<br>FO = 1, L = 0 mm | 0.20<br>0.25<br>0.28              | ns   |

|                             | Inverter                                  | 1x<br>2x<br>4x                      |                                                                              | 0.47<br>0.35<br>0.22              | ns   |

|                             | 2-input NAND                              | 1x<br>2x<br>4x                      | Input tr/tf = V <sub>DD</sub> /1.0 ns<br>Output loading:                     | 0.57<br>0.36<br>0.25              | ns   |

|                             | 2-input NOR                               | 1x<br>2x<br>4x                      | FO = 2, L = 2 mm<br>L = Metal length                                         | 0.69<br>0.53<br>0.51              | ns   |

| Flip-flop (FD1A)            | Delay time:<br>Set-up time:<br>Hold time: | CLK↑ to Q<br>D to CLK↑<br>CLK↑ to D |                                                                              | 1.63<br>1.5<br>0.1 <sup>[3]</sup> | ns   |

| Toggle frequency of flip-fl | ор                                        |                                     | FO = 1, L = 0 mm                                                             | 500                               | MHz  |

<sup>[1]</sup> For the purpose of this table, Rated Value is calculated as an average of the LH and HL delay times of each macro type.

# **AC Characteristics**

(Core  $V_{DD}$  = 3.3 V,  $V_{SS}$  = 0 V,  $T_j$  = 25° C)

| Param                       | eter                                      | Driving Type                        | Conditions                                                                   | Rated Value [1][2]                  | Unit |

|-----------------------------|-------------------------------------------|-------------------------------------|------------------------------------------------------------------------------|-------------------------------------|------|

| Internal gate delay times   | Inverter<br>2-input NAND<br>2-input NOR   | 1x<br>1x<br>1x                      | Input tr/tf = V <sub>DD</sub> /1.0 ns<br>Output loading:<br>FO = 1, L = 0 mm | 0.31<br>0.38<br>0.43                | ns   |

|                             | Inverter                                  | 1x<br>2x<br>4x                      | 0.72<br>0.54<br>0.34                                                         |                                     | ns   |

|                             | 2-input NAND                              | 1x<br>2x<br>4x                      | Input tr/tf = V <sub>DD</sub> /1.0 ns<br>Output loading:                     | 0.87<br>0.55<br>0.38                | ns   |

|                             | 2-input NOR                               | 1x<br>2x<br>4x                      | FO = 2, L = 2 mm<br>L = Metal length                                         | 1.06<br>0.81<br>0.78                | ns   |

| Flip-flop (FD1A)            | Delay time:<br>Set-up time:<br>Hold time: | CLK↑ to Q<br>D to CLK↑<br>CLK↑ to D |                                                                              | 2.66<br>2.29<br>0.15 <sup>[3]</sup> | ns   |

| Toggle frequency of flip-fl | lop                                       |                                     | FO = 1, L = 0 mm                                                             | 327                                 | MHz  |

<sup>[1]</sup> For the purpose of this table, Rated Value is calculated as an average of the LH and HL delay times of each macro type

<sup>[2]</sup> Characteristics are quoted for a typical process.

<sup>[3]</sup>  $th_L$  (C,D)  $\geq$  0.1 ns. For I/O information, please refer to the AC Characteristics listed in the I/O table.

<sup>[2]</sup> Characteristics are quoted for a typical process.

<sup>[3]</sup>  $th_1$  (C,D)  $\geq$  0.15 ns. For I/O information, please refer to the AC Characteristics listed in the I/O table.

# AC Characteristics (I/O $V_{DD}$ = 3.3 V or 5 V, $V_{SS}$ = 0 V, $T_j$ = 25° C)

|                                                                  |                          |                                |                                                                                                          | Rat                          | ted Values For                           | V <sub>DD Conditon</sub> [               | 1][2]                        |      |

|------------------------------------------------------------------|--------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------|------------------------------------------|------------------------------------------|------------------------------|------|

| Parameter                                                        | Ту                       | pe                             | Conditions                                                                                               | LL<br>3-V Ext<br>3-V Core    | HL<br>3-V Ext <sup>[3]</sup><br>5-V Core | LH<br>5-V Ext <sup>[3]</sup><br>3-V Core | HH<br>5-V Ext<br>5-V Core    | Unit |

| Input buffer delay times                                         | CMOS input               |                                | Input<br>tr, tf = 0.2 ns/3.3 V<br>FO = 2,<br>L = 2 mm <sup>[4]</sup>                                     | 1                            | -                                        | -                                        | 0.82                         | ns   |

|                                                                  |                          |                                | Input<br>tr, tf = 0.3 ns/5 V<br>(LH, HH)<br>tr, tf = 0.2 ns/3.3 V<br>(LL, HL)<br>FO = 2,<br>L = 2 mm [4] | 0.95                         | 1.78                                     | 0.96                                     | 0.71                         | ns   |

| Output buffer delay times (t <sub>in</sub> = 0.3 ns/5 V          | Push-pull for HH<br>& LH | 4 mA<br>8 mA<br>16 mA<br>24 mA | $C_L = 20 \text{ pF}$ $C_L = 50 \text{ pF}$ $C_L = 100 \text{ pF}$ $C_L = 150 \text{ pF}$                | -<br>-<br>-                  | -<br>-<br>-<br>-                         | 2.90<br>3.86<br>3.87<br>3.69             | 1.39<br>1.86<br>2.03<br>2.51 | ns   |

| for LH & HL or t <sub>in</sub><br>= 0.2 ns/3.3 V for<br>LL & HL) | Push-pull for LL &<br>HL | 2 mA<br>4 mA<br>8 mA<br>12 mA  | $C_L = 20 \text{ pF}$ $C_L = 50 \text{ pF}$ $C_L = 100 \text{ pF}$ $C_L = 150 \text{ pF}$                | 2.30<br>3.11<br>3.34<br>3.76 | 1.53<br>1.99<br>2.18<br>2.58             | -<br>-<br>-                              | -<br>-<br>-                  | ns   |

| Output buffer transition time                                    | Push-pull                |                                | C <sub>1</sub> = 150 pF for 24 mA                                                                        | -<br>-                       | -<br>-                                   | 3.38 (r)<br>3.59 (f)                     | 2.66 (r)<br>3.04 (f)         | ns   |

| (20-80%)                                                         | Push-pull with s         | slew rate control              | buffer <sup>[5]</sup>                                                                                    | -                            | -<br>-                                   | 9.20 (r)<br>7.86 (f)                     | 3.60 (r)<br>3.62 (f)         | ns   |

<sup>[1]</sup> Rated values are calculated as an average of the L-H and the H-L delay times for each macro type.

<sup>[2]</sup> Characteristics are quoted for a typical process.

<sup>[3]</sup> Parameters include level shifter cell where appropriate.

<sup>[4]</sup> For L = 2 mm, metal capacitance value of 0.304 pF has been chosen.

<sup>[5]</sup> Output rising and falling times are specified.

#### MACRO LIBRARY

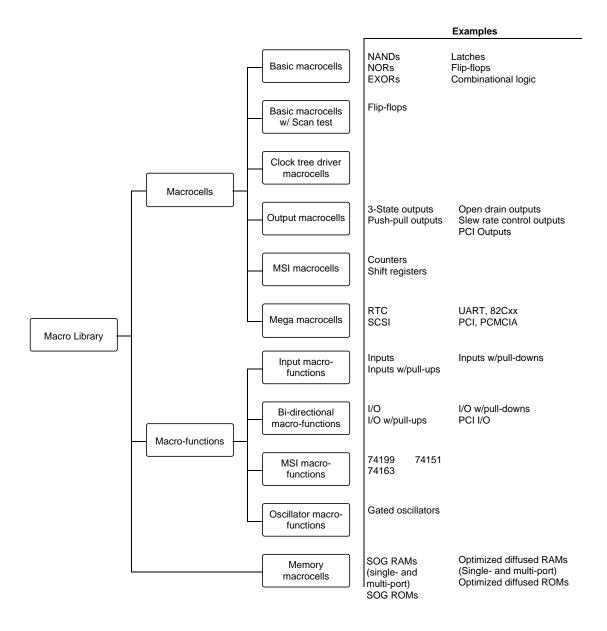

Figure 4. OKI Macro Library

## MACROCELLS FOR DRIVING CLOCK TREES

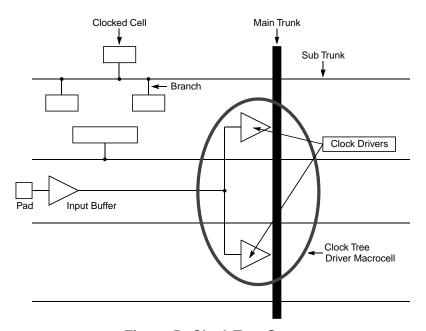

OKI offers clock-tree drivers that guarantee a skew time of less than 1.0 ns. The advanced layout software uses dynamic driver placement and sub-trunk allocation to optimize the clock-tree implementation for a particular circuit. Features of the clock-tree driver-macrocells include:

- Clock skew  $\leq 1.0$  ns

- Automatic fan-out balancing

- Dynamic sub-trunk allocation

- Single clock tree driver logic symbol

- Single-level clock drivers

- · Automatic branch length minimization

- · Dynamic driver placement

- Up to four clock trunks

The clock-skew management scheme is described in detail in the 0.8µm Technolog€lock Skew Management Application Note

Figure 5. Clock Tree Structure

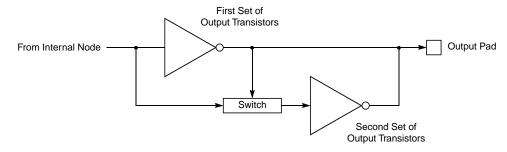

#### OUTPUT DRIVER MACROCELLS FOR SLEW RATE CONTROL

The slew-rate-control output driver macrocells reduce both simultaneous-switching noise and output-ringing noise. The output transistors are split into two sets; first, one set of output transistors drive the output pads, then, after the output passes the threshold, the second set of output transistors drive the I/O pads.

Figure 6below shows output drivers configured for slew-rate control. All outputs with a drive of 8 mA or more are available with slew-rate control.

Figure 6. Slew Rate Control Output Buffer

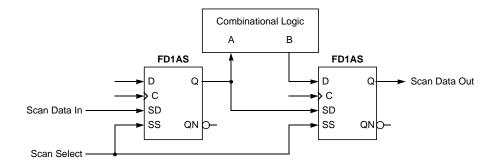

## AUTOMATIC TEST VECTOR GENERATION

OKI's 0.8µm ASIC technologies support Automatic Test Vector Generation (ATVG) using full scan-path design techniques, including the following:

- Increases fault coverage ≥ 95%

- Uses Synopsys Test Compiler

- Automatically inserts scan structures

- Connects scan chains

- · Traces and reports scan chains

- Checks for rule violations

- Generates complete fault reports

- Allows multiple scan chains

- Supports vector compaction

Figure 7. Full Scan Path Configuration

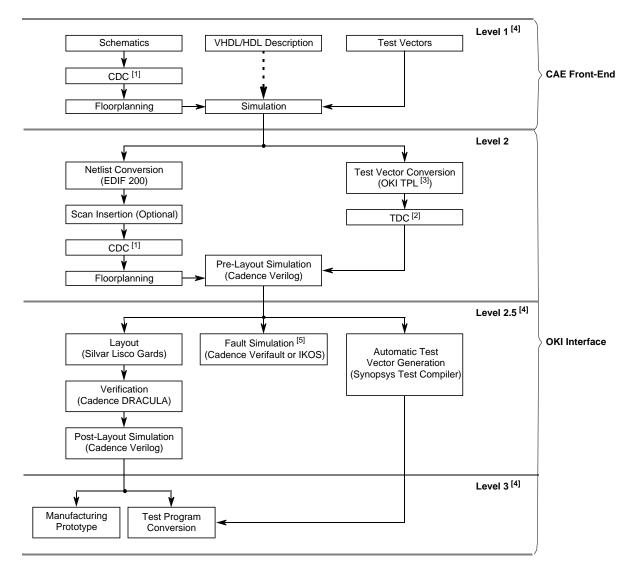

# **DESIGN PROCESS**

- OKI Circuit Data Check program (CDC) verifies logic design rules

OKI Test Data Check program (TDC) verifies test vector rules

OKI Test Pattern Language (TPL)

Alternate Customer-OKI design interfaces available in addition to standard level 2

- [5] Standard design process includes fault simulation

Figure 8. OKI Design Process

## OKI ADVANCED DESIGN CENTER CAD TOOLS

- Floorplanning for front-end simulation and back-end layout controls

- · Clock tree structures improve first-time silicon success by eliminating clock skew problems

- Power calculation which predicts circuit power under simulation conditions to accurately model package requirements

# **Design Kits**

| Vendor          | Platform                                                                                        | Operating System [1]                            | Vendor Software [1]                                                                         | Description                                                                                             |

|-----------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Cadence         | Sun <sup>[2]</sup>                                                                              | SunOS<br>Solaris <sup>[3]</sup>                 | Composer<br>Verilog<br>Veritime<br>Verifault<br>Synergy<br>Concept<br>Leapfrog              | Design capture Simulation Timing analysis Fault grading Design synthesis Design capture VHDL simulation |

|                 | HP9000, 7xx                                                                                     | HP-UX                                           | Composer<br>Verilog<br>Veritime<br>Verifault<br>Synergy                                     | Design capture<br>Simulation<br>Timing analysis<br>Fault simulation<br>Design synthesis                 |

|                 | IBM RS6000                                                                                      | AIX                                             | Composer<br>Verilog<br>Synergy                                                              | Design capture<br>Simulation<br>Design synthesis                                                        |

| IKOS            | Sun <sup>[2]</sup>                                                                              | SunOS<br>Solaris <sup>[3]</sup>                 | Alchemy                                                                                     | Simulation<br>Fault grading                                                                             |

| Mentor Graphics | HP9000, 7xx                                                                                     | HP-UX                                           | IDEA<br>QuickVHDL<br>QuickSim II                                                            | Design capture<br>VHDL simulation<br>Logic simulation                                                   |

|                 | Sun <sup>[2]</sup>                                                                              | SunOS<br>Solaris <sup>[3]</sup>                 | QuickPath<br>QuickFault<br>QuickGrade<br>AutoLogic<br>DFT Advisor                           | Timing analysis<br>Fault grading<br>Fault grading<br>Design synthesis<br>Test synthesis                 |

| Synopsys        | (Interface to Mentor<br>Graphics, VIEWLogic)<br>Sun <sup>[2]</sup><br>HP9000, 7xx<br>IBM RS6000 | SunOS<br>Solaris <sup>[3]</sup><br>HP-UX<br>AIX | Design Compiler<br>HDL/VHDL Compiler<br>Test Compiler<br>VSS                                | Compilation<br>Design synthesis<br>Test synthesis<br>VHDL simulation                                    |

| VIEWLogic       | Sun <sup>[2]</sup>                                                                              | SunOS<br>Solaris <sup>[3]</sup>                 | Workview Plus<br>Powerview                                                                  | Design capture<br>Simulation                                                                            |

|                 | PC                                                                                              | DOS<br>Windows<br>Windows NT <sup>[3]</sup>     | Vantage Optium ViewTime/Motive <sup>[3]</sup> ViewRetargeter ViewSynthesis ViewSim with VSO | VHDL simulation<br>Timing analysis<br>Design migration<br>Design synthesis<br>Simulation                |

<sup>[1]</sup> Contact OKI Application Engineering for current software versions.

<sup>[2]</sup> Sun<sup>®</sup> or Sun-compatible.

<sup>[3]</sup> In development.

# PACKAGE OPTIONS

# MSM38S0000 42-Alloy QFP Package Menu

| Master          |                            | QFP (42-Alloy) |         |         |         |         |         |         |         |  |

|-----------------|----------------------------|----------------|---------|---------|---------|---------|---------|---------|---------|--|

| Slice<br>MSM38S | I/O<br>Pads <sup>[1]</sup> | 44             | 60      | 80      | 100     | 128     | 136     | 144     | 160     |  |

| 0110            | 100                        | •              | •       | •       | •       |         |         |         |         |  |

| 0210            | 136                        |                |         |         | •       | •       | •       |         |         |  |

| 0300            | 160                        |                |         |         | •       | •       | •       | •       | •       |  |

| 0570            | 216                        |                |         |         |         | •       | •       | •       | •       |  |

| 0980            | 280                        |                |         |         |         | •       | •       | •       | •       |  |

| 1500            | 344                        |                |         |         |         |         |         | •       | •       |  |

| 2250            | 420                        |                |         |         |         |         |         |         | •       |  |

| Body Siz        | e (mm)                     | 9.5 x 10.5     | 15 x 19 | 14 x 20 | 14 x 20 | 28 x 28 | 28 x 28 | 28 x 28 | 28 x 28 |  |

| Lead Pito       | h (mm)                     | 0.8            | 1       | 0.8     | 0.65    | 0.8     | 0.65    | 0.65    | 0.65    |  |

<sup>[1]</sup> I/O pads can be used for input, output, bidirectional, power, or ground signals.

# MSM38S0000 Cu-Alloy QFP and TQFP Package Menu

| Master Slice |                         | QFP (Cu-Alloy) |         |         |         | TQFP    |                   |                   |                   |         |                    |

|--------------|-------------------------|----------------|---------|---------|---------|---------|-------------------|-------------------|-------------------|---------|--------------------|

| MSM38S       | I/O Pads <sup>[1]</sup> | 176            | 208     | 240     | 272     | 304     | 44 <sup>[2]</sup> | 64 <sup>[2]</sup> | 80 <sup>[2]</sup> | 100 [2] | 144 <sup>[3]</sup> |

| 0110         | 100                     |                |         |         |         |         | •                 | •                 | •                 | •       |                    |

| 0210         | 136                     |                |         |         |         |         | •                 | •                 | •                 | •       | •                  |

| 0300         | 160                     | •              |         |         |         |         |                   | •                 | •                 | •       | •                  |

| 0570         | 216                     | •              | •       |         |         |         |                   |                   | •                 | •       | •                  |

| 0980         | 280                     | •              | •       | •       |         |         |                   |                   |                   |         | •                  |

| 1500         | 344                     | •              | •       | •       | •       |         |                   |                   |                   |         | •                  |

| 2250         | 420                     | •              | •       | •       | •       | •       |                   |                   |                   |         |                    |

| Body Siz     | e (mm)                  | 24 x 24        | 28 x 28 | 32 x 32 | 36 x 36 | 40 x 40 | 10 x 10           | 10 x 10           | 12 x 12           | 14 x 14 | 20 x 20            |

| Lead Pito    | ch (mm)                 | 0.5            | 0.5     | 0.5     | 0.5     | 0.5     | 0.8               | 0.5               | 0.5               | 0.5     | 0.5                |

<sup>[1]</sup> I/O Pads can be used for input, output, bidirectional, power, or ground signals.

<sup>● =</sup> Available now

<sup>[2] 1.0</sup>mm thick

<sup>[3] 1.4</sup>mm thick

<sup>● =</sup> Available now

# MSM38S0000 PLCC and CPGA Package Menu

| Master Slice    |                         | PL   | .cc   | CPGA  |       |       |       |       |  |  |  |

|-----------------|-------------------------|------|-------|-------|-------|-------|-------|-------|--|--|--|

| MSM38S          | I/O Pads <sup>[1]</sup> | 44   | 84    | 88    | 132   | 176   | 208   | 401   |  |  |  |

| 0110            | 100                     | •    |       | •     |       |       |       |       |  |  |  |

| 0210            | 136                     | •    | •     | •     | •     |       |       |       |  |  |  |

| 0300            | 160                     | •    | •     | •     | •     |       |       |       |  |  |  |

| 0570            | 216                     |      | •     |       | •     | •     |       |       |  |  |  |

| 0980            | 280                     |      |       |       | •     | •     | •     |       |  |  |  |

| 1500            | 344                     |      |       |       | •     | •     | •     |       |  |  |  |

| 2250            | 420                     |      |       |       | •     |       |       | •     |  |  |  |

| Body Siz        | Body Size (mm)          |      | 28x28 | 33x33 | 35x35 | 38x38 | 44x44 | 50x50 |  |  |  |

| Lead Pitch (mm) |                         | 1.27 | 1.27  | 2.54  | 2.54  | 2.54  | 2.54  | 1.27  |  |  |  |

<sup>[1]</sup> I/O Pads can be used for input, output, bi-directional, power or ground.

<sup>• =</sup> Available now

# MSM98S000 QFP Package Menu

| Master          | 1/0         | PQFP (42-Alloy)  |            |            |            |            |            |            | PQFP (Cu-Alloy) |            |            |            | TQFP       |            |            |            |            |            |

|-----------------|-------------|------------------|------------|------------|------------|------------|------------|------------|-----------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|

| Slice<br>MSM98S | Pads<br>[1] | 44               | 60         | 80         | 100        | 128        | 136        | 144        | 160             | 176        | 208        | 240        | 272        | 304        | 44         | 64         | 80         | 100        |

| 020x020         | 80          | 0                | 0          | 0          |            |            |            |            |                 |            |            |            |            |            | 0          | 0          | 0          |            |

| 023x023         | 92          | •                | 0          | O          |            |            |            |            |                 |            |            |            |            |            | 0          | 0          | •          |            |

| 026x026         | 104         | •                | 0          | 0          | 0          |            |            |            |                 |            |            |            |            |            | •          | )          | )          | •          |

| 029x029         | 116         | 0                | 0          | O          | 0          |            |            |            |                 |            |            |            |            |            | •          | 0          | •          | •          |

| 032x032         | 128         | 0                | 0          | O          | 0          | •          |            |            |                 |            |            |            |            |            | •          | 0          | 0          | •          |

| 035x035         | 140         | 0                | 0          | O          | 0          | •          | •          |            |                 |            |            |            |            |            | 0          | •          | •          | 0          |

| 038x038         | 152         | 0                | 0          | •          | 0          | •          | •          | 0          |                 |            |            |            |            |            |            | •          | 0          | •          |

| 041x041         | 164         | 0                | 0          | •          | •          | •          | •          | •          | 0               |            |            |            |            |            |            | 0          | •          | О          |

| 044x044         | 176         | 0                | 0          | О          | 0          | •          | •          | •          | 0               |            |            |            |            |            |            |            | 0          | •          |

| 047x047         | 188         | 0                | 0          | О          | •          | •          | •          | •          | •               | 0          |            |            |            |            |            |            | •          | •          |

| 050x050         | 200         | 0                | 0          | О          | 0          | 0          | •          | •          | •               | 0          |            |            |            |            |            |            | •          | О          |

| 053x053         | 212         | 0                | 0          | О          | 0          | •          | •          | •          | •               | 0          | 0          |            |            |            |            |            | •          | О          |

| 056x056         | 224         | 0                | 0          | О          | 0          | •          | •          | •          | •               | 0          | •          |            |            |            |            |            | •          | •          |

| 059x059         | 236         | 0                | 0          | О          | 0          | •          | 0          | •          | •               | •          | •          |            |            |            |            |            | 0          | •          |

| 062x062         | 248         | 0                | 0          | О          | •          | •          | •          | •          | •               | 0          | 0          |            |            |            |            |            | 0          | •          |

| 065x065         | 260         | 0                | 0          | О          | 0          | •          | •          | •          | •               | 0          | •          | 0          |            |            |            |            | 0          | •          |

| 068x068         | 272         | 0                | О          | 0          | 0          | 0          | •          | •          | •               | •          | •          | •          |            |            |            |            | 0          | 0          |

| 071x071         | 284         |                  |            |            |            | •          | •          | •          | •               | О          | О          | 0          |            |            |            |            |            |            |

| 074x074         | 296         |                  |            |            |            | •          | •          | •          | •               | О          | О          | 0          |            |            |            |            |            |            |

| 077x077         | 308         |                  |            |            |            | •          | •          | •          | •               | О          | •          | 0          |            |            |            |            |            |            |

| 080x080         | 320         |                  |            |            |            | •          | •          | •          | •               | О          | •          | 0          |            |            |            |            |            |            |

| 083x083         | 332         |                  |            |            |            | •          | •          | •          | •               | 0          | •          | 0          |            |            |            |            |            |            |

| 086x086         | 344         |                  |            |            |            | 0          | 0          | •          | 0               | •          | •          | •          | •          |            |            |            |            |            |

| 089x089         | 356         |                  |            |            |            | 0          | •          | 0          | 0               | •          | •          | •          | 0          |            |            |            |            |            |

| 092x092         | 368         |                  |            |            |            | •          | •          | •          | 0               | O          | •          | •          | 0          |            |            |            |            |            |

| 095x095         | 380         |                  |            |            |            | •          | 0          | •          | •               | O          | •          | 0          | 0          |            |            |            |            |            |

| 098x098         | 392         |                  |            |            |            | •          | 0          | •          | •               | 0          | 0          | 0          | 0          |            |            |            |            |            |

| 101x101         | 404         |                  |            |            |            | 0          | •          | 0          | •               | 0          | 0          | 0          | 0          |            |            |            |            |            |

| 104x104         | 416         |                  |            |            |            | 0          | •          | 0          | •               | •          | •          | 0          | •          | •          |            |            |            |            |

| Body Size       |             | 9.5<br>x<br>10.5 | 15<br>x 19 | 14<br>x 20 | 14<br>x 20 | 28<br>x 28 | 28<br>x 28 | 28<br>x 28 | 28<br>x 28      | 28<br>x 28 | 24<br>x 24 | 32<br>x 32 | 36<br>x 36 | 40<br>x 40 | 10<br>x 10 | 10<br>x 10 | 12<br>x 12 | 14<br>x 14 |

| Lead Pitch (n   | nm)         | 0.8              | 1          | 0.8        | 0.65       | 0.8        | 0.65       | 0.65       | 0.65            | 0.5        | 0.5        | 0.5        | 0.5        | 0.5        | 0.8        | 0.5        | 0.5        | 0.5        |

<sup>[1]</sup> I/O pads can be used for input, output, bidirectional, power, or ground connections.

<sup>● =</sup> Available now

O = In development

# MSM98S000 PLCC and CPGA Package Menu

| Master Slice    |              | Pl      | .CC     | CPGA    |         |         |         |         |  |  |

|-----------------|--------------|---------|---------|---------|---------|---------|---------|---------|--|--|

| MSM98S          | I/O Pads [1] | 44      | 84      | 72      | 88      | 132     | 176     | 208     |  |  |

| 020x020         | 80           | 0       |         | О       |         |         |         |         |  |  |

| 023x023         | 92           | 0       |         | О       | О       |         |         |         |  |  |

| 026x026         | 104          | 0       |         | О       | О       |         |         |         |  |  |

| 029x029         | 116          | •       | •       | О       | •       |         |         |         |  |  |

| 032x032         | 128          | •       | •       | О       | •       | О       |         |         |  |  |

| 035x035         | 140          | •       | •       | О       | •       | О       |         |         |  |  |

| 038x038         | 152          |         | •       | О       | •       | О       |         |         |  |  |

| 041x041         | 164          |         | •       | О       | •       | О       |         |         |  |  |

| 044x044         | 176          |         | •       | О       | •       | •       |         |         |  |  |

| 047x047         | 188          |         | •       | 0       | •       | •       | 0       |         |  |  |

| 050x050         | 200          |         | •       | •       | •       | •       | О       |         |  |  |

| 053x053         | 212          |         | •       | •       | •       | •       | О       |         |  |  |

| 056x056         | 224          |         | •       | •       | О       | •       | О       | 0       |  |  |

| 059x059         | 236          |         | •       | •       | О       | •       | О       | 0       |  |  |

| 062x062         | 248          |         | •       | •       | О       | •       | О       | 0       |  |  |

| 065x065         | 260          |         | •       | •       | О       | •       | 0       | 0       |  |  |

| 068x068         | 272          |         | •       | •       | О       | •       | •       | 0       |  |  |

| 071x071         | 284          |         | •       | •       | О       | •       | •       | 0       |  |  |

| 074x074         | 296          |         |         | •       | О       | •       | •       | 0       |  |  |

| 077x077         | 308          |         |         | О       | О       | •       | •       | 0       |  |  |

| 080x080         | 320          |         |         | 0       | 0       | •       | •       | •       |  |  |

| 083x083         | 332          |         |         | 0       | 0       | •       | •       | •       |  |  |

| 086x086         | 344          |         |         | О       | О       | •       | •       | •       |  |  |

| 089x089         | 356          |         |         | 0       | 0       | •       | •       | •       |  |  |

| 092x092         | 368          |         |         | 0       | 0       | •       | •       | •       |  |  |

| 095x095         | 380          |         |         | 0       | 0       | •       | •       | •       |  |  |

| 098x098         | 392          |         |         | 0       | 0       | •       | 0       | •       |  |  |

| 101x101         | 404          |         |         | 0       | 0       | •       | 0       | •       |  |  |

| 104x104         | 416          |         |         | 0       | 0       | •       | 0       | •       |  |  |

| Body Size       | •            | 17 x 17 | 28 x 28 | 28 x 28 | 33 x 33 | 35 x 35 | 38 x 38 | 44 x 44 |  |  |

| Lead Pitch (mm) |              | 1.27    | 1.27    | 2.54    | 2.54    | 2.54    | 2.54    | 2.54    |  |  |

<sup>[1]</sup> I/O pads can be used for input, output, bidirectional, power, or ground signals.

<sup>=</sup> Available now

O = In development

# OKI REGIONAL SALES OFFICES

#### **Northwest Area**

785 N. Mary Avenue Sunnyvale, CA 94086 Tel: 408/720-8940 Fax: 408/720-8965

#### **Southwest Area**

2302 Martin Street Suite 250 Irvine, CA 92715 Tel: 714/752-1843 Fax: 714/752-2423

#### **Central Area**

2007 N. Collins Blvd. Suite 303 Richardson, TX 75080 Tel: 214/690-6868 Fax: 214/690-8233

#### **Southeast Area**

1590 Adamson Parkway Suite 220 Morrow, GA 30260

Tel: 404/960-9660 Fax: 404/960-9682

#### **Eastern Area**

Shattuck Office Center 138 River Road Andover, MA 01810 Tel: 508/688-8687 Fax: 508/688-8896

#### **Automotive Electronics**

17177 N. Laurel Park Drive Suite 433 Livonia, MI 48152

Tel: 313/464-7200 Fax: 313/464-1724

#### FOR OKI LITERATURE:

Call toll free 1-800-OKI-6388 (6 a.m. to 5 p.m. Pacific Time)

OKI Stock No: 010400-002

# **OKI** Semiconductor

## **Corporate Headquarters**

785 N. Mary Avenue Sunnyvale, CA 94086-2909

Tel: 408/720-1900 Fax: 408/720-1918