# **OKI Semiconductor**

**FEDL7224-001FULL-01**Issue Date: Sep. 28, 2005

# ML7224-001TC

4ch VoIP CODEC

#### **GENERAL DESCRIPTION**

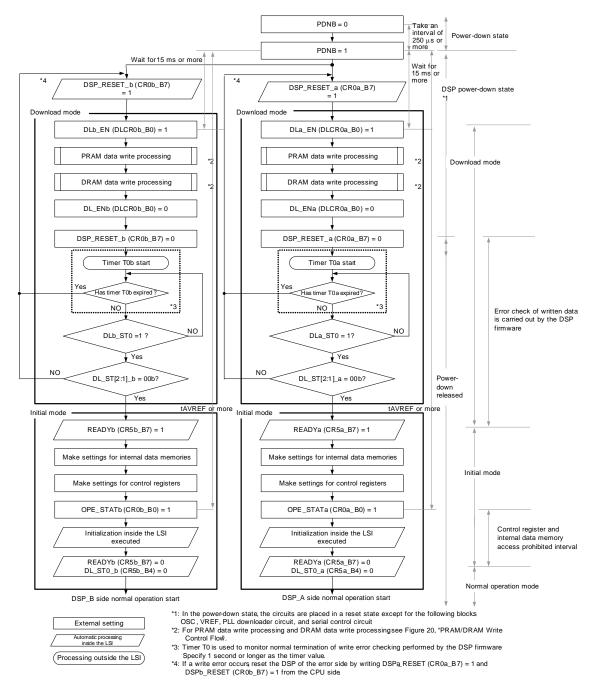

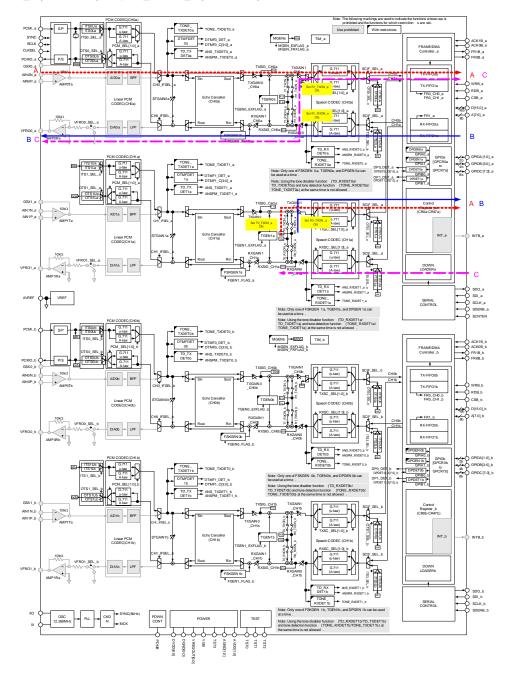

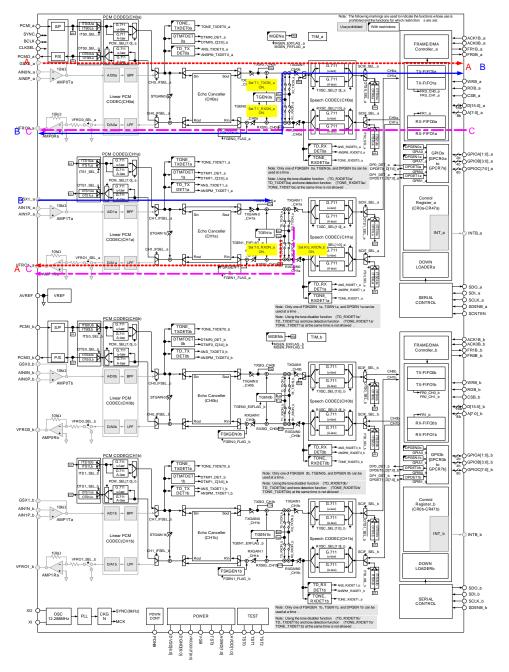

The ML7224-001 is a VoIP codec that has speech codecs with four channels. These speech codecs support the PLC (Packet Loss Concealment) function, with the coding format selectable between G.711 ( $\mu$ -law) and G.711 (A-law). The ML7224-001 is equipped with an echo canceller that supports a delay of 32 ms for each channel; it also has functions such as FSK generation, DTMF detection/generation, and tone detection/generation. The ML7224-001 is an LSI device best suited to add multichannel VoIP capability to a TA, router and others.

Note that because this LSI device employs the method of downloading the DSP firmware from outside of the LSI to a built-in memory, it is capable of supporting functional expansion by changing the DSP firmware.

#### **FEATURES**

- Speech codecs (with 4 channels):

- Selectable between ITU-T G.711 (64 kbps) μ-law and A-law

- Supports ITU-T G.711 Appendix I compliant PLC (Packet Loss Concealment) function

- Interface for transferring speech CODEC transmit/receive data:

- Selectable between FIFO buffer interface and PCM interface\*

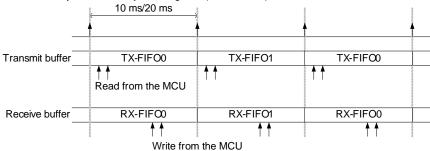

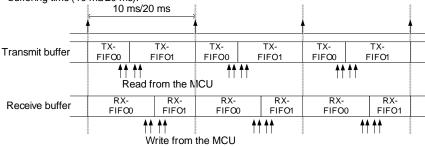

- FIFO buffer interface:

- Number of interfaces

2 (one for CH0a/CH1a and the other for CH0b/CH1b)

FIFO buffer size

CH0a/CH1a: 640 bytes, CH0b/CH1b: 640 bytes

- Frame/DMA (slave) interface can be selected

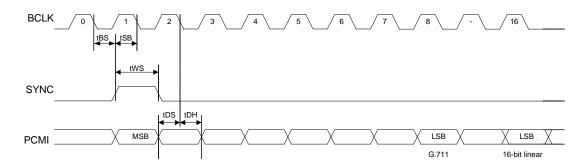

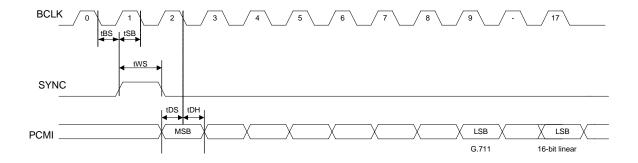

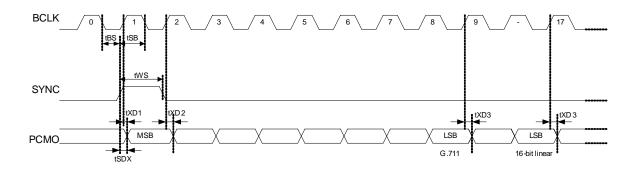

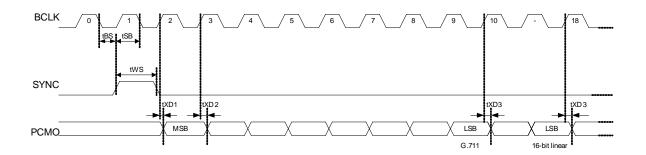

- PCM interface

- Number of interfaces

2 (one for CH0a/CH1a and the other for CH0b/CH1b)

Serial transmission rate

128 kHz to 2.048 MHz (fixed at 2.048 MHz during output)

- 1-time-slot bit width : Fixed to 16 bits

- Time slot assignment : A maximum of 16 slots can be assigned (when BCLK = 2.048 MHz)

- Input time slot selection : Arbitrary 4 slots maximum can be selected (for each block)

Output time slot selection : Arbitrary 2 slots maximum can be selected (for each block)

- Front-end interface

- Selectable between analog interface and PCM interface\*1

(Note) When a PCM interface is selected, data is input or output by multiplexing time slots on the PCM interface above. ITU-T G.711 (64 kbps)  $\mu$ -law or A-law can be selected as the coding format for this purpose.

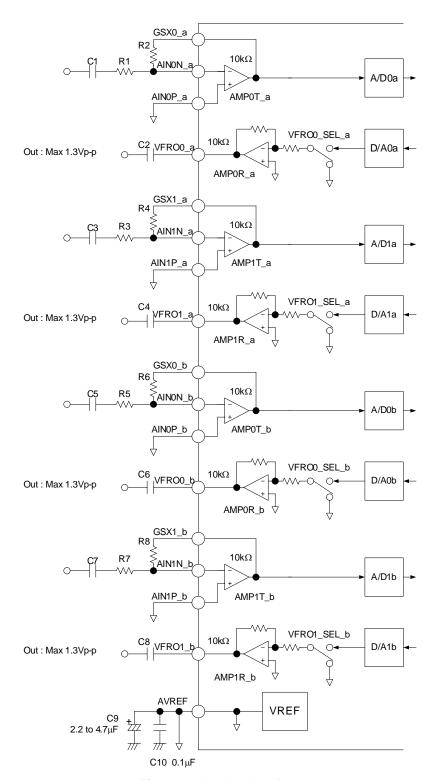

- Analog interface<sup>\*1</sup>

- Number of interfaces : 4 with one input amplifier and one output amplifier incorporated for each channel (10  $k\Omega$  driving)

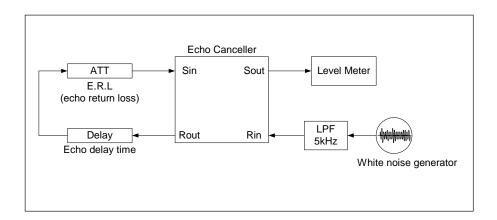

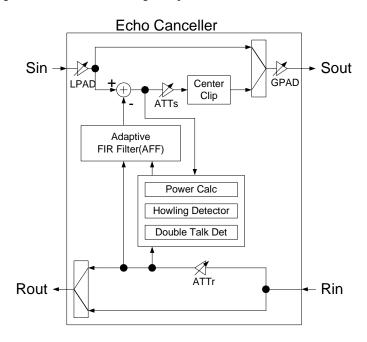

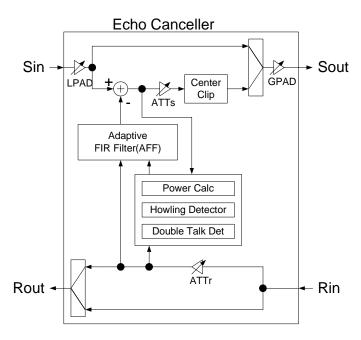

- Echo canceller for 32 ms delay (One block installed per channel.)

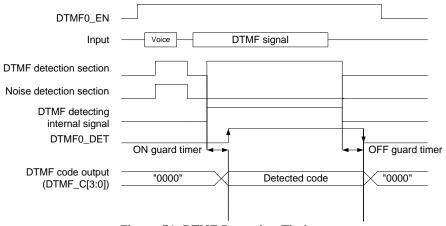

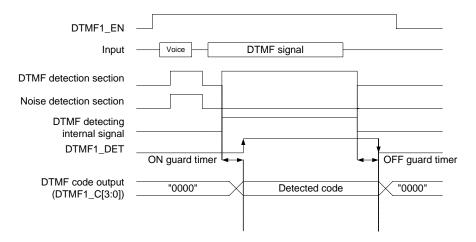

- DTMF detection function (One block installed per channel.)

- DTMF generation function (One block installed per channel\*2. The DTMF signal can be generated by the tone generation function.)

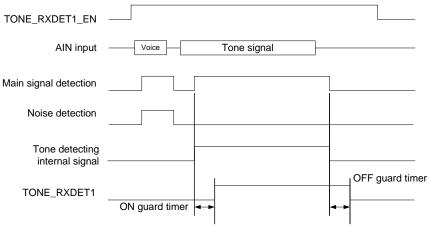

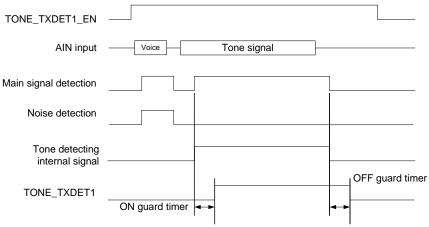

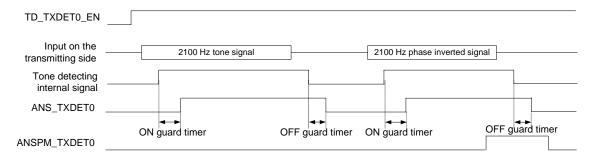

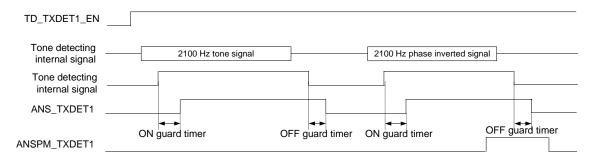

- 2100 Hz single tone/phase inversion detection function (Two blocks installed per channel\*3.)

- Tone detection function (400Hz. Detecting frequency can be changed. Two blocks installed per channel\*3.)

- Tone generation function (One block installed per channel\*2.)

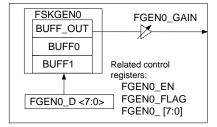

- FSK generation function (One block installed per channel\*2.)

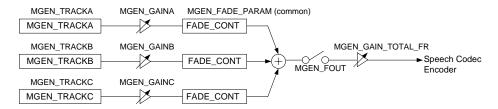

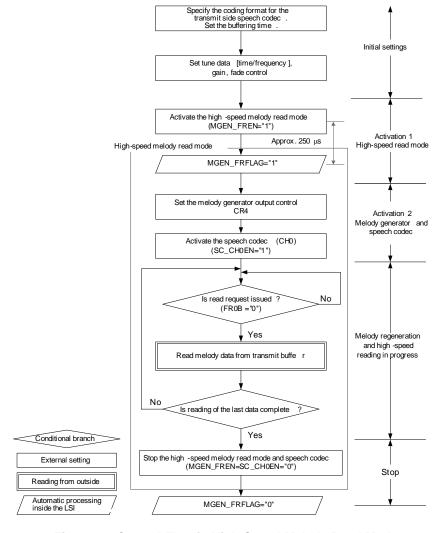

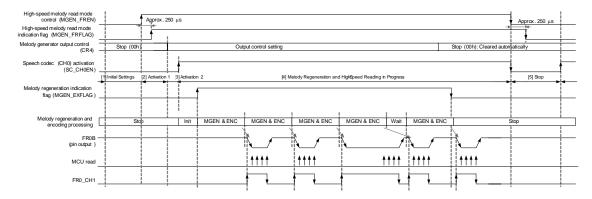

- Meody generation function (One block installed for every two channels\*4.)

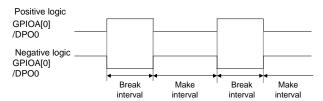

- Dial pulse detection function (One block installed per channel.): Secondary function of a general-purpose input/output port

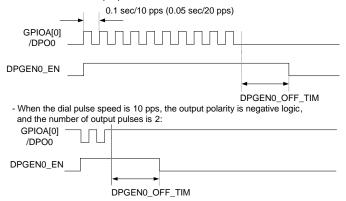

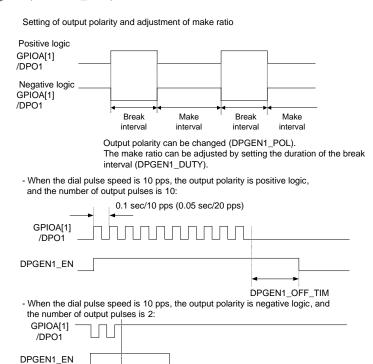

• Dial pulse transmission function (One block installed per channel\*2.): Secondary function of a general-purpose input/output port

- 16-bit timer (One block installed for every two channels.)

- Equipped with an interface for serial control

- Allows downloading of DSP firmware

- General-purpose input/output port:

28 ports (some of them have a secondary function)

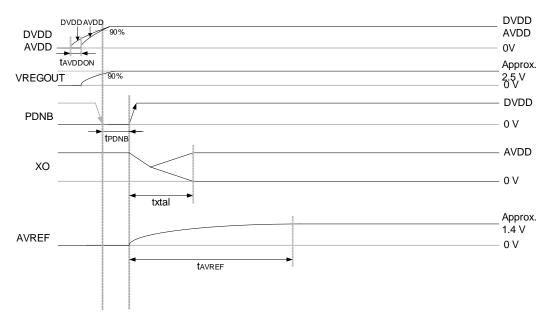

• Power supply voltage:

Digital power supply voltage (DVDD0, 1, 2, 3, 4, 5, 6) : 3.0 to 3.6V Analog power supply voltage (AVDD0,1) : 3.0 to 3.6V

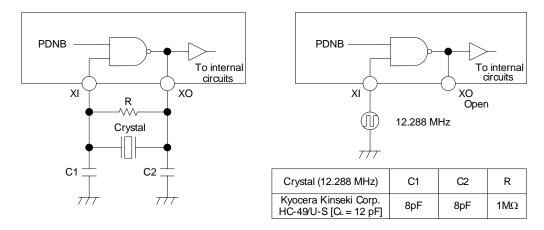

• Master clock frequency:

12.288 MHz (crystal resonator/external input)

- Power down control by hardware or software

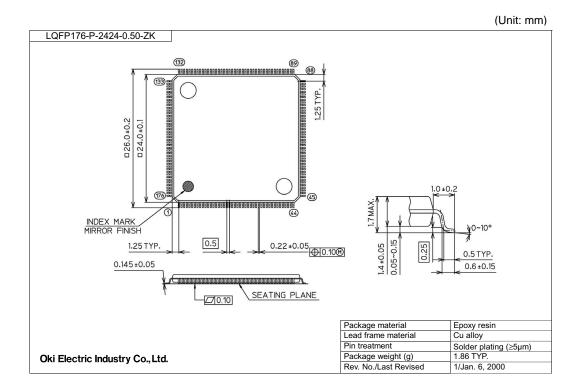

- Package:

176-pin plastic LQFP (LQFP176-P-2424-0.50-ZK)

\*1

Selecting an analog interface is prohibited in the ML7224-001. Also, selecting a PCM interface as a speech codec interface is not supported.

\*2:

Only one of the FSK generation function, tone generation function (DTMF generation function) and dial pulse transmission function can be used at a time per channel. Note that using more than one generation function at the same time is not used.

\*3:

Using the  $2100\,\mathrm{Hz}$  single tone /phase inversion detection function and the tone detection function for each channel at the same time is not allowed.

\*4:

If the melody generation function is used, stop all the functions described below on the DSP side that generates melodies.

In addition, when starting a speech codec, do not start it on the channel 1 side (SC\_CH1EN = 1).

- Tone generation function (TGEN0/TGEN1)

- Tone detection function (TONE\_RXDET0/TONE\_TXDET0, TONE\_RXDET1/TONE\_TXDET1)

- FSK generation function (FSKGEN0/FSKGEN1)

- Tone disabler detection function (TD RXDET0/TD TXDET0, TD RXDET1/TD TXDET1)

- DTMF detection function (DTMF\_DET0/DTMF\_DET1)

- Echo canceller (EC0/EC1)

- Dial pulse detection function (DPDET0/DPDET1)

- Dial pulse transmission function (DPGEN0/DPGEN1)

- Timer (TIMER)

#### (Additional note)

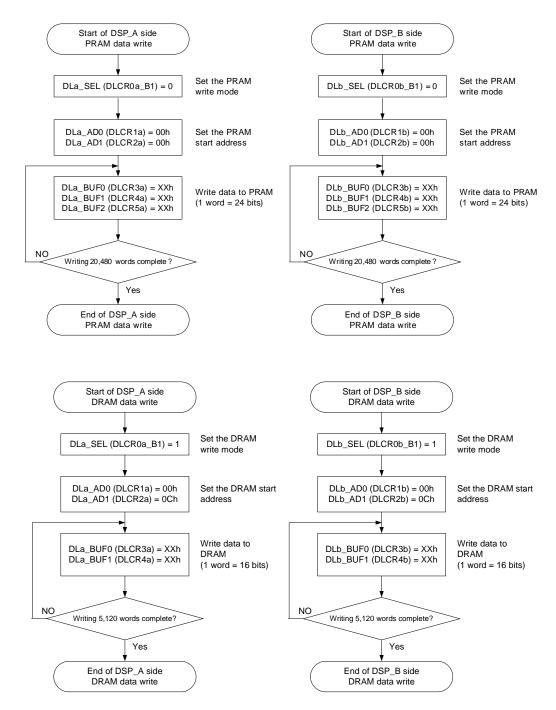

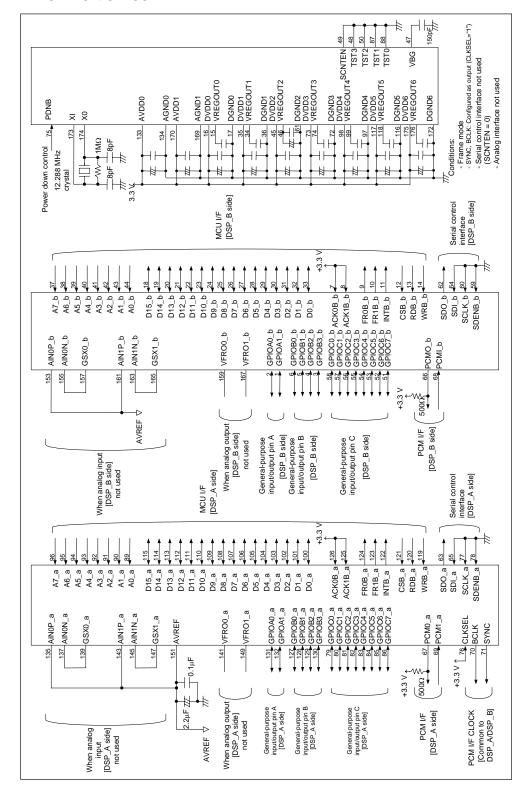

This LSI incorporates two DSPs. One DSP performs processing for two channels.

This document distinguishes these two DSPs as the DSP\_A side and the DSP\_B side, and \_a or \_b is affixed to the names of related pins, control registers and others.

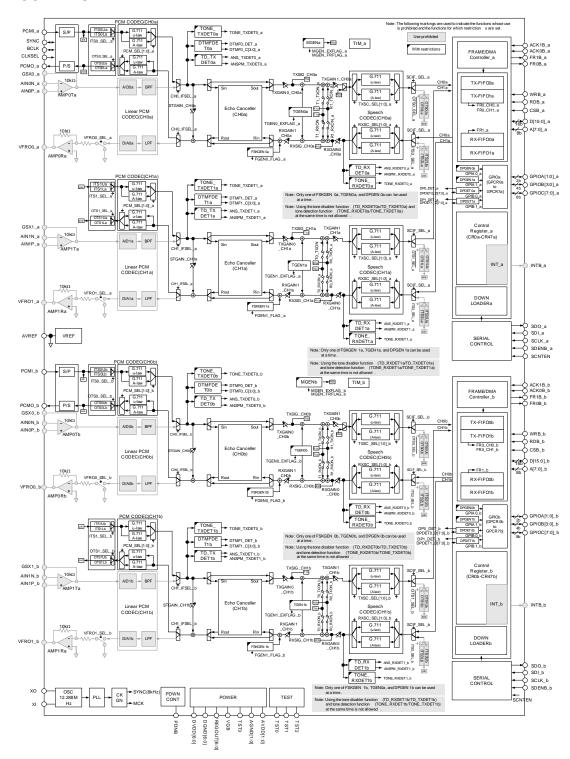

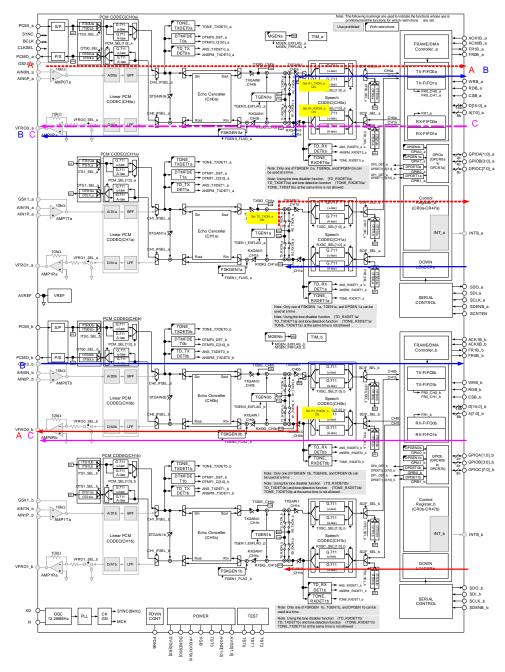

#### **BLOCK DIAGRAM**

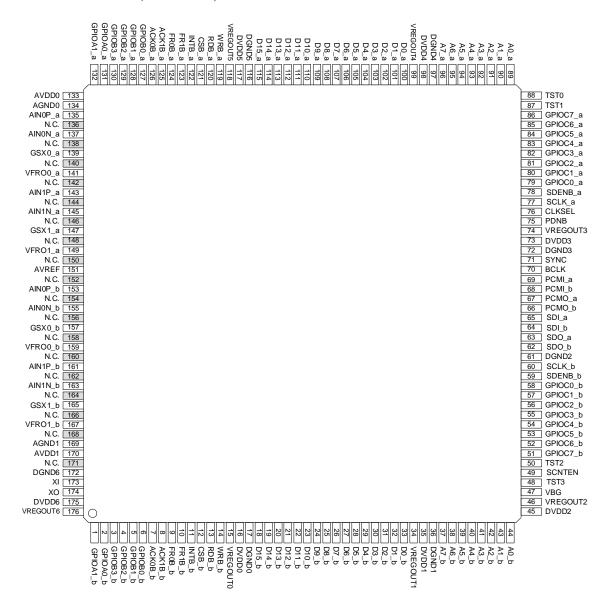

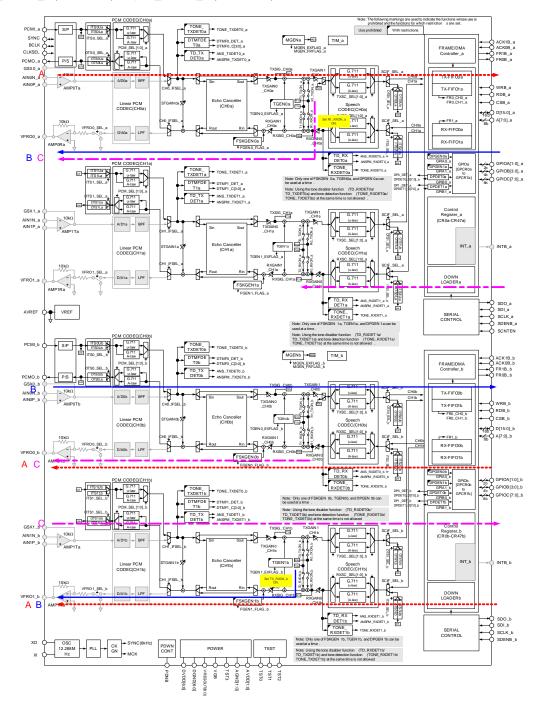

### PIN ASSIGNMENT (TOP VIEW)

176-Pin Plastic LQFP

# PIN DESCRIPTIONS

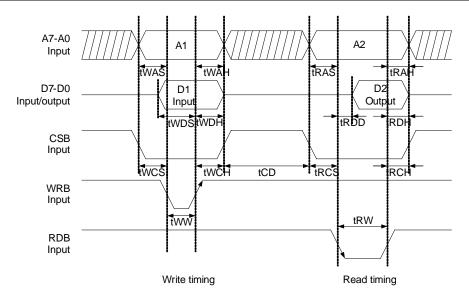

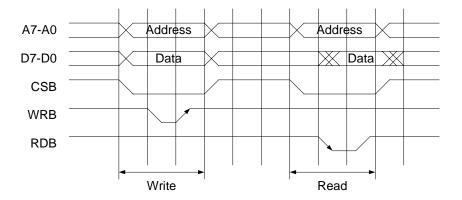

# **MCU Interface**

| Pin No. | Symbol | I/O | When PDNB = "0" | Description                                                                                          |

|---------|--------|-----|-----------------|------------------------------------------------------------------------------------------------------|

| 100     | D0_a   | I/O | I               | Data input/output for CH0a/CH1a                                                                      |

| 101     | D1_a   | I/O | I               | Data input/output for CH0a/CH1a                                                                      |

| 102     | D2_a   | I/O | I               | Data input/output for CH0a/CH1a                                                                      |

| 103     | D3_a   | I/O | I               | Data input/output for CH0a/CH1a                                                                      |

| 104     | D4_a   | I/O | I               | Data input/output for CH0a/CH1a                                                                      |

| 105     | D5_a   | I/O | I               | Data input/output for CH0a/CH1a                                                                      |

| 106     | D6_a   | I/O | I               | Data input/output for CH0a/CH1a                                                                      |

| 107     | D7_a   | I/O | I               | Data input/output for CH0a/CH1a                                                                      |

| 108     | D8_a   | I/O | ı               | Data input/output for CH0a/CH1a. Fix the input level when using in 8-bit bus access (BW_SELa = "1"). |

| 109     | D9_a   | I/O | I               | Data input/output for CH0a/CH1a. Fix the input level when using in 8-bit bus access (BW_SELa = "1"). |

| 110     | D10_a  | I/O | I               | Data input/output for CH0a/CH1a. Fix the input level when using in 8-bit bus access (BW_SELa = "1"). |

| 111     | D11_a  | I/O | I               | Data input/output for CH0a/CH1a. Fix the input level when using in 8-bit bus access (BW_SELa = "1"). |

| 112     | D12_a  | I/O | I               | Data input/output for CH0a/CH1a. Fix the input level when using in 8-bit bus access (BW_SELa = "1"). |

| 113     | D13_a  | I/O | I               | Data input/output for CH0a/CH1a. Fix the input level when using in 8-bit bus access (BW_SELa = "1"). |

| 114     | D14_a  | I/O | I               | Data input/output for CH0a/CH1a. Fix the input level when using in 8-bit bus access (BW_SELa = "1"). |

| 115     | D15_a  | I/O | I               | Data input/output for CH0a/CH1a. Fix the input level when using in 8-bit bus access (BW_SELa = "1"). |

| 89      | A0_a   | I   | I               | Address input for CH0a/CH1a                                                                          |

| 90      | A1_a   | I   | I               | Address input for CH0a/CH1a                                                                          |

| 91      | A2_a   | I   | I               | Address input for CH0a/CH1a                                                                          |

| 92      | A3_a   | I   | I               | Address input for CH0a/CH1a                                                                          |

| 93      | A4_a   | I   | I               | Address input for CH0a/CH1a                                                                          |

| 94      | A5_a   | I   | I               | Address input for CH0a/CH1a                                                                          |

| 95      | A6_a   | I   | I               | Address input for CH0a/CH1a                                                                          |

| 96      | A7_a   | I   | I               | Address input for CH0a/CH1a                                                                          |

| 121     | CSB_a  | I   | I               | Chip select input for CH0a/CH1a                                                                      |

| 120     | RDB_a  | I   | I               | Read enable input for CH0a/CH1a                                                                      |

| 119     | WRB_a  | I   |                 | Write enable input for CH0a/CH1a                                                                     |

# MCU Interface (continued)

| Pin No. | Symbol | I/O | When PDNB = "0" | Description                                                                                          |

|---------|--------|-----|-----------------|------------------------------------------------------------------------------------------------------|

| 33      | D0_b   | I/O | I               | Data input/output for CH0b/CH1b                                                                      |

| 32      | D1_b   | I/O | I               | Data input/output for CH0b/CH1b                                                                      |

| 31      | D2_b   | I/O | I               | Data input/output for CH0b/CH1b                                                                      |

| 30      | D3_b   | I/O | I               | Data input/output for CH0b/CH1b                                                                      |

| 29      | D4_b   | I/O | I               | Data input/output for CH0b/CH1b                                                                      |

| 28      | D5_b   | I/O | I               | Data input/output for CH0b/CH1b                                                                      |

| 27      | D6_b   | I/O | I               | Data input/output for CH0b/CH1b                                                                      |

| 26      | D7_b   | I/O | I               | Data input/output for CH0b/CH1b                                                                      |

| 25      | D8_b   | I/O | I               | Data input/output for CH0b/CH1b. Fix the input level when using in 8-bit bus access (BW_SELb = "1"). |

| 24      | D9_b   | I/O | I               | Data input/output for CH0b/CH1b. Fix the input level when using in 8-bit bus access (BW_SELb = "1"). |

| 23      | D10_b  | I/O | I               | Data input/output for CH0b/CH1b. Fix the input level when using in 8-bit bus access (BW_SELb = "1"). |

| 22      | D11_b  | I/O | I               | Data input/output for CH0b/CH1b. Fix the input level when using in 8-bit bus access (BW_SELb = "1"). |

| 21      | D12_b  | I/O | I               | Data input/output for CH0b/CH1b. Fix the input level when using in 8-bit bus access (BW_SELb = "1"). |

| 20      | D13_b  | I/O | I               | Data input/output for CH0b/CH1b. Fix the input level when using in 8-bit bus access (BW_SELb = "1"). |

| 19      | D14_b  | I/O | I               | Data input/output for CH0b/CH1b. Fix the input level when using in 8-bit bus access (BW_SELb = "1"). |

| 18      | D15_b  | I/O | I               | Data input/output for CH0b/CH1b. Fix the input level when using in 8-bit bus access (BW_SELb = "1"). |

| 44      | A0_b   | I   |                 | Address input for CH0b/CH1b                                                                          |

| 43      | A1_b   | I   | I               | Address input for CH0b/CH1b                                                                          |

| 42      | A2_b   | I   | I               | Address input for CH0b/CH1b                                                                          |

| 41      | A3_b   | I   |                 | Address input for CH0b/CH1b                                                                          |

| 40      | A4_b   | I   | I               | Address input for CH0b/CH1b                                                                          |

| 39      | A5_b   | I   | I               | Address input for CH0b/CH1b                                                                          |

| 38      | A6_b   | I   | I               | Address input for CH0b/CH1b                                                                          |

| 37      | A7_b   | I   | I               | Address input for CH0b/CH1b                                                                          |

| 12      | CSB_b  | I   | I               | Chip select input for CH0b/CH1b                                                                      |

| 13      | RDB_b  | I   | I               | Read enable input for CH0b/CH1b                                                                      |

| 14      | WRB_b  | I   | I               | Write enable input for CH0b/CH1b                                                                     |

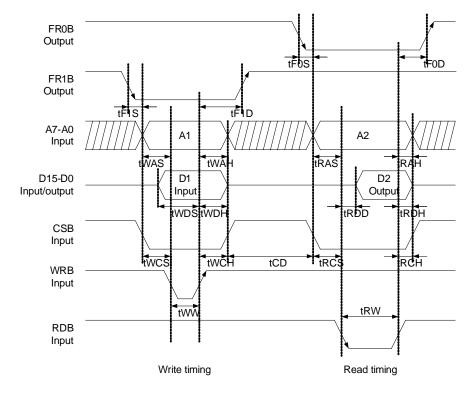

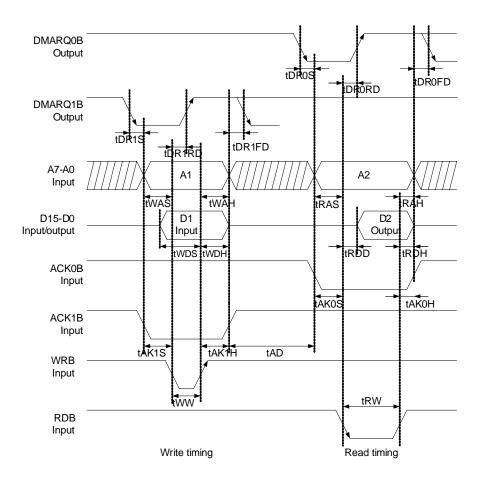

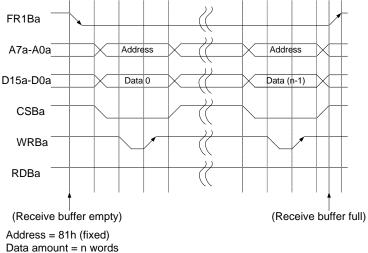

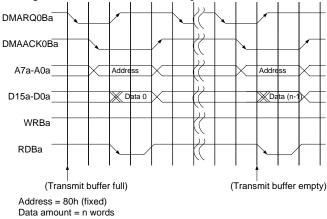

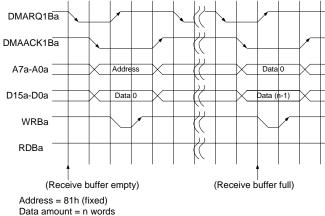

# FRAM/DMA Interface

| Pin No. | Symbol                | I/O | When PDNB = "0" | Description                                                                                                                                                   |

|---------|-----------------------|-----|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 126     | ACK0B_a               | I   | ı               | Transmit buffer DMA access acknowledge signal input for CH0a/CH1a                                                                                             |

| 125     | ACK1B_a               | I   | I               | Receive buffer DMA access acknowledge signal input for CH0a/CH1a                                                                                              |

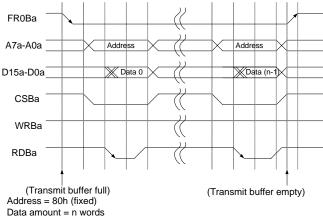

| 124     | FR0B_a<br>(DMARQ0B_a) | 0   | "H"             | FR0B:(FD_SEL = "0") Transmit buffer frame signal output for CH0a/CH1a DMARQ0B: (FD_SEL = "1") Transmit buffer DMA access request signal output for CH0a/CH1a  |

| 123     | FR1B_a<br>(DMARQ1B_a) | 0   | "H"             | FR1B: (FD_SEL = "0") Receive buffer frame signal output for CH0a/CH1a DMARQ1B: (FD_SEL = "1") Receive buffer DMA access request signal output for CH0a/CH1a   |

| 7       | ACK0B_b               | I   | I               | Transmit buffer DMA access acknowledge signal input for CH0b/CH1b                                                                                             |

| 8       | ACK1B_b               | I   | I               | Receive buffer DMA access acknowledge signal input for CH0b/CH1b                                                                                              |

| 9       | FR0B_b<br>(DMARQ0B_b) | 0   | "H"             | FR0B: (FD_SEL = "0") Transmit buffer frame signal output for CH0b/CH1b DMARQ0B: (FD_SEL = "1") Transmit buffer DMA access request signal output for CH0b/CH1b |

| 10      | FR1B_b<br>(DMARQ1B_b) | 0   | "H"             | FR1B: (FD_SEL = "0") Receive buffer frame signal output for CH0b/CH1b DMARQ1B: (FD_SEL = "1") Receive buffer DMA access request signal output for CH0b/CH1b   |

## Interrupt

| Pin No. | Symbol | I/O | When PDNB = "0" | Description                                                                       |

|---------|--------|-----|-----------------|-----------------------------------------------------------------------------------|

| 122     | INTB_a | 0   | 1 "H"           | Interrupt request output for CH0a/CH1a (Not supported in this code. Use it open.) |

| 11      | INTB_b | 0   | I "H"           | Interrupt request output for CH0b/CH1b (Not supported in this code. Use it open.) |

# **Analog Interface**

| Pin No. | Symbol  | I/O | When PDNB = "0" | Description                                                    |

|---------|---------|-----|-----------------|----------------------------------------------------------------|

| 135     | AIN0P_a | I   | I               | Transmit amplifier non-inverting input for CH0a                |

| 137     | AIN0N_a | I   | I               | Transmit amplifier inverting input for CH0a                    |

| 139     | GSX0_a  | 0   | "Hi-Z"          | Transmit amplifier output for CH0a (10 kΩ drive)               |

| 141     | VFRO0_a | 0   | "Hi-Z"          | Receive amplifier output for CH0a (10 kΩ drive)                |

| 143     | AIN1P_a |     | I               | Transmit amplifier non-inverting input for CH1a                |

| 145     | AIN1N_a |     | I               | Transmit amplifier inverting input for CH1a                    |

| 147     | GSX1_a  | 0   | "Hi-Z"          | Transmit amplifier output for CH1a (10 kΩ drive)               |

| 149     | VFRO1_a | 0   | "Hi-Z"          | Receive amplifier output for CH1a (10 kΩ drive)                |

| 153     | AIN0P_b |     | I               | Transmit amplifier non-inverting input for CH0b                |

| 155     | AIN0N_b | I   | I               | Transmit amplifier inverting input for CH0b                    |

| 157     | GSX0_b  | 0   | "Hi-Z"          | Transmit amplifier output for CH0b (10 kΩ drive)               |

| 159     | VFRO0_b | 0   | "Hi-Z"          | Receive amplifier output for CH0b (10 kΩ drive)                |

| 161     | AIN1P_b | I   | I               | Transmit amplifier non-inverting input for CH1b                |

| 163     | AIN1N_b | I   | I               | Transmit amplifier inverting input for CH1b                    |

| 165     | GSX1_b  | 0   | "Hi-Z"          | Transmit amplifier output for CH1b (10 kΩ drive)               |

| 167     | VFRO1_b | 0   | "Hi-Z"          | Receive amplifier output for CH1b (10 kΩ drive)                |

| 151     | AVREF   | 0   | "L"             | Analog signal ground electric potential output (approx. 1.4 V) |

# **Oscillator Circuit**

| Pin No. | Symbol | I/O | When PDNB = "0" | Description                                                 |

|---------|--------|-----|-----------------|-------------------------------------------------------------|

| 173     | XI     | I   | I               | For 12.288 MHz crystal oscillator or 12.288 MHz clock input |

| 174     | XO     | 0   | "H"             | For 12.288 MHz crystal oscillator                           |

## **Power Down Control**

| Pin No. | Symbol | I/O | When PDNB = "0" | Description                                                          |

|---------|--------|-----|-----------------|----------------------------------------------------------------------|

| 75      | PDNB   | I   | "0"             | Power down control input "0": Power down reset "1": Normal operation |

# **PCM Interface**

| Pin No. | Symbol | I/O | When PDNB = "0" | Description                                                                                        |

|---------|--------|-----|-----------------|----------------------------------------------------------------------------------------------------|

| 67      | PCMO_a | 0   | "Hi-Z"          | PCM signal output for CH0a/CH1a [open drain output pin]                                            |

| 69      | PCMI_a | I   | I               | PCM signal input for CH0a/CH1a                                                                     |

| 66      | PCMO_b | 0   | "Hi-Z"          | PCM signal output for CH0b/CH1b [open drain output pin]                                            |

| 68      | PCMI_b | I   | I               | PCM signal input for CH0b/CH1b                                                                     |

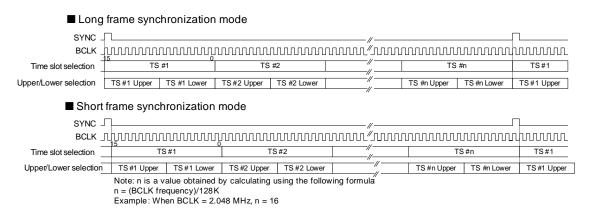

| 70      | BCLK   | I/O | I               | CLKSEL = "0": PCM shift clock input                                                                |

| 70 BCLK | BCLK   |     | "L"             | CLKSEL = "1": PCM shift clock output                                                               |

| 71      | SYNC   | I/O | I               | CLKSEL = "0": PCM synchronous signal 8 kHz input                                                   |

| / 1     | STING  | 1/0 | "L"             | CLKSEL = "1": PCM synchronous signal 8kHz output                                                   |

| 76      | CLKSEL | I   | I               | SYNC and BCLK I/O control input "0": SYNC and BCLK become inputs "1": SYNC and BCLK become outputs |

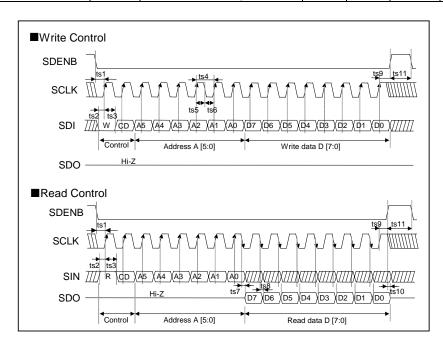

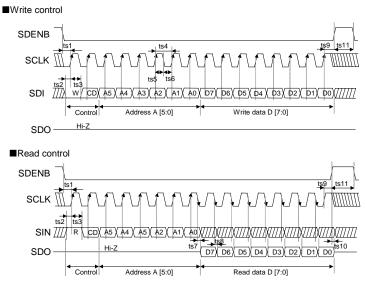

## **Serial Control Interface**

| Pin No. | Symbol  | I/O | When PDNB = "0" | Description                                                 |

|---------|---------|-----|-----------------|-------------------------------------------------------------|

| 63      | SDO_a   | 0   | "Hi-Z"          | Serial control output for CH0a/CH1a [open drain output pin] |

| 65      | SDI_a   | I   | I               | Serial control input for CH0a/CH1a                          |

| 77      | SCLK_a  | I   | I               | Serial control clock input for CH0a/CH1a                    |

| 78      | SDENB_a | I   | I               | Serial control data enable input for CH0a/CH1a              |

| 62      | SDO_b   | 0   | "Hi-Z"          | Serial control output for CH0b/CH1b [open drain output pin] |

| 64      | SDI_b   | I   | I               | Serial control input for CH0b/CH1b                          |

| 60      | SCLK_b  | I   | I               | Serial control clock input for CH0b/CH1b                    |

| 59      | SDENB_b | I   | I               | Serial control data enable input for CH0b/CH1b              |

| 49      | SCNTEN  | I   | I               | Serial control enable setting                               |

# **General-Purpose Input/Output Ports**

| SPIOAU_a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Pin No. | Symbol       | I/O  | When PDNB = "0" | Description                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------|------|-----------------|---------------------------------------------------------|

| tolerant pin]  132 GPIOA1_a I/O I General-purpose input/output port A1 for CH0a/CH1a [5 tolerant pin]  127 GPIOB0_a I/O I General-purpose input/output port B0 for CH0a/CH1a [5 tolerant pin]  128 GPIOB1_a I/O I General-purpose input/output port B1 for CH0a/CH1a [5 tolerant pin]  129 GPIOB2_a I/O I General-purpose input/output port B2 for CH0a/CH1a [5 tolerant pin]  130 GPIOB3_a I/O I General-purpose input/output port B3 for CH0a/CH1a [5 tolerant pin]  79 GPIOC0_a I/O I General-purpose input/output port C0 for CH0a/CH1a [5 tolerant pin]  80 GPIOC1_a I/O I General-purpose input/output port C0 for CH0a/CH1a [5 tolerant pin]  81 GPIOC3_a I/O I General-purpose input/output port C1 for CH0a/CH1a [8] GPIOC3_a I/O I General-purpose input/output port C2 for CH0a/CH1a [8] GPIOC4_a I/O I General-purpose input/output port C3 for CH0a/CH1a [8] GPIOC5_a I/O I General-purpose input/output port C3 for CH0a/CH1a [8] GPIOC6_a I/O I General-purpose input/output port C5 for CH0a/CH1a [8] GPIOC6_a I/O I General-purpose input/output port C5 for CH0a/CH1a [8] GPIOC6_a I/O I General-purpose input/output port C5 for CH0a/CH1a [8] GPIOC6_a I/O I General-purpose input/output port C5 for CH0a/CH1a [8] GPIOC6_a I/O I General-purpose input/output port C5 for CH0a/CH1a [8] GPIOC6_a I/O I General-purpose input/output port C6 for CH0a/CH1a [8] GPIOC6_b I/O I General-purpose input/output port C6 for CH0a/CH1a [9] General-purpose input/output port C6 for CH0a/CH1a [9] General-purpose input/output port A1 for CH0b/CH1b [5 tolerant pin] [9] General-purpose input/output port A2 for CH0b/CH1b [5 tolerant pin] [9] General-purpose input/output port B2 for CH0b/CH1b [5 tolerant pin] [9] General-purpose input/output port B3 for CH0b/CH1b [5 tolerant pin] [9] General-purpose input/output port B3 for CH0b/CH1b [5 tolerant pin] [9] General-purpose input/output port C2 for CH0b/CH1b [5 tolerant pin] [9] General-purpose input/output port C2 for CH0b/CH1b [5 tolerant pin] [9] General-purpose input/output port C2 for CH0b/CH1b [5 tolerant pin] [9] General-purpo | 131     | GPIOA0 a     | I/O  |                 | General-purpose input/output port A0 for CH0a/CH1a [5 V |

| Tolerant pin   Tolerant pin   Tolerant pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         | 01 10/10_a   | 1/0  | '               | 1 4                                                     |

| tolerant pin]  GPIOBO_a I/O I General-purpose input/output port B0 for CH0a/CH1a [5 tolerant pin]  128 GPIOB1_a I/O I General-purpose input/output port B1 for CH0a/CH1a [5 tolerant pin]  129 GPIOB2_a I/O I General-purpose input/output port B2 for CH0a/CH1a [5 tolerant pin]  130 GPIOB3_a I/O I General-purpose input/output port B3 for CH0a/CH1a [5 tolerant pin]  79 GPIOC0_a I/O I General-purpose input/output port C0 for CH0a/CH1a [5 tolerant pin]  80 GPIOC1_a I/O I General-purpose input/output port C1 for CH0a/CH1a [81 GPIOC2_a I/O I General-purpose input/output port C2 for CH0a/CH1a [82 GPIOC3_a I/O I General-purpose input/output port C3 for CH0a/CH1a [83 GPIOC4_a I/O I General-purpose input/output port C3 for CH0a/CH1a [84 GPIOC5_a I/O I General-purpose input/output port C3 for CH0a/CH1a [85 GPIOC6_a I/O I General-purpose input/output port C5 for CH0a/CH1a [86 GPIOC7_a I/O I General-purpose input/output port C5 for CH0a/CH1a [5 tolerant pin] [5 GPIOA0_b I/O I General-purpose input/output port C7 for CH0a/CH1a [5 tolerant pin] [5 GPIOB0_b I/O I General-purpose input/output port C7 for CH0a/CH1b [5 tolerant pin] [6 GPIOB0_b I/O I General-purpose input/output port A1 for CH0b/CH1b [5 tolerant pin] [7 General-purpose input/output port B1 for CH0b/CH1b [5 tolerant pin] [7 General-purpose input/output port B2 for CH0b/CH1b [5 tolerant pin] [7 General-purpose input/output port B3 for CH0b/CH1b [5 tolerant pin] [7 General-purpose input/output port B3 for CH0b/CH1b [5 tolerant pin] [7 General-purpose input/output port B2 for CH0b/CH1b [5 tolerant pin] [7 General-purpose input/output port B3 for CH0b/CH1b [5 tolerant pin] [7 General-purpose input/output port B3 for CH0b/CH1b [5 tolerant pin] [7 General-purpose input/output port B3 for CH0b/CH1b [5 tolerant pin] [7 General-purpose input/output port C3 for CH0b/CH1b [5 tolerant pin] [7 General-purpose input/output port C3 for CH0b/CH1b [5 tolerant pin] [7 General-purpose input/output port C3 for CH0b/CH1b [5 tolerant pin] [7 General-purpose input/output port C3 for CH0b/CH | 132     | GPIOA1 a     | I/O  | 1               |                                                         |

| tolerant pin]  GPIOB0_a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |              | ., 0 | ·               | 1 1                                                     |

| Tolerant pin   General-purpose input/output port B1 for CH0a/CH1a   Stolerant pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 127     | GPIOB0 a     | I/O  | 1               |                                                         |

| tolerant pin]  GPIOB1_a I/O I General-purpose input/output port B2 for CH0a/CH1a [5 tolerant pin]  GPIOB3_a I/O I General-purpose input/output port B3 for CH0a/CH1a [5 tolerant pin]  GPIOC0_a I/O I General-purpose input/output port C0 for CH0a/CH1a [5 tolerant pin]  GPIOC1_a I/O I General-purpose input/output port C1 for CH0a/CH1a B1 GPIOC2_a I/O I General-purpose input/output port C2 for CH0a/CH1a B2 GPIOC3_a I/O I General-purpose input/output port C2 for CH0a/CH1a B3 GPIOC4_a I/O I General-purpose input/output port C3 for CH0a/CH1a B4 GPIOC5_a I/O I General-purpose input/output port C3 for CH0a/CH1a B4 GPIOC5_a I/O I General-purpose input/output port C3 for CH0a/CH1a B5 GPIOC6_a I/O I General-purpose input/output port C5 for CH0a/CH1a B6 GPIOC7_a I/O I General-purpose input/output port C5 for CH0a/CH1a B6 GPIOC6_b I/O I General-purpose input/output port C7 for CH0a/CH1a B6 GPIOC6_b I/O I General-purpose input/output port C7 for CH0a/CH1a B6 GPIOC6_b I/O I General-purpose input/output port A0 for CH0a/CH1a B6 GPIOC6_b I/O I General-purpose input/output port A1 for CH0b/CH1b [5 tolerant pin]  GPIOB1_b I/O I General-purpose input/output port B1 for CH0b/CH1b [5 tolerant pin]  GPIOB2_b I/O I General-purpose input/output port B2 for CH0b/CH1b [5 tolerant pin]  GPIOB3_b I/O I General-purpose input/output port B3 for CH0b/CH1b [5 tolerant pin]  GPIOB3_b I/O I General-purpose input/output port B3 for CH0b/CH1b [5 tolerant pin]  GPIOC6_b I/O I General-purpose input/output port C7 for CH0b/CH1b [5 tolerant pin]  GPIOC6_b I/O I General-purpose input/output port C7 for CH0b/CH1b [5 tolerant pin]  GPIOC6_b I/O I General-purpose input/output port C7 for CH0b/CH1b [5 tolerant pin]  GPIOC6_b I/O I General-purpose input/output port C7 for CH0b/CH1b [5 tolerant pin]  GPIOC6_b I/O I General-purpose input/output port C7 for CH0b/CH1b [5 tolerant pin]  GPIOC6_b I/O I General-purpose input/output port C7 for CH0b/CH1b [5 tolerant pin] General-purpose input/output port C7 for CH0b/CH1b [5 tolerant pin] General-purpose input/output  |         | <del>-</del> |      |                 | 1 1                                                     |

| 129   GPIOB2_a   I/O   I   General-purpose input/output port B2 for CH0a/CH1a [5 tolerant pin]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 128     | GPIOB1_a     | I/O  | 1               |                                                         |

| tolerant pin]    Sepioric   Compact   Compact  | -       |              |      |                 |                                                         |

| GPIOB3_a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 129     | GPIOB2_a     | I/O  | I               |                                                         |

| tolerant pin]  79    GPIOC0_a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -       |              |      |                 |                                                         |

| 79 GPIOCO_a I/O I General-purpose input/output port C0 for CH0a/CH1a 80 GPIOC1_a I/O I General-purpose input/output port C1 for CH0a/CH1a 81 GPIOC2_a I/O I General-purpose input/output port C2 for CH0a/CH1a 82 GPIOC3_a I/O I General-purpose input/output port C3 for CH0a/CH1a 83 GPIOC4_a I/O I General-purpose input/output port C3 for CH0a/CH1a 84 GPIOC5_a I/O I General-purpose input/output port C5 for CH0a/CH1a 85 GPIOC6_a I/O I General-purpose input/output port C5 for CH0a/CH1a 85 GPIOC6_a I/O I General-purpose input/output port C6 for CH0a/CH1a 86 GPIOC7_a I/O I General-purpose input/output port C7 for CH0a/CH1a 86 GPIOA_b I/O I General-purpose input/output port C7 for CH0a/CH1a 86 GPIOA_b I/O I General-purpose input/output port A0 for CH0b/CH1b [5 tolerant pin]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 130     | GPIOB3_a     | I/O  | I               |                                                         |

| 80 GPIOC1_a I/O I General-purpose input/output port C1 for CH0a/CH1a 81 GPIOC2_a I/O I General-purpose input/output port C2 for CH0a/CH1a 82 GPIOC3_a I/O I General-purpose input/output port C3 for CH0a/CH1a 83 GPIOC4_a I/O I General-purpose input/output port C4 for CH0a/CH1a 84 GPIOC5_a I/O I General-purpose input/output port C5 for CH0a/CH1a 85 GPIOC6_a I/O I General-purpose input/output port C6 for CH0a/CH1a 86 GPIOC7_a I/O I General-purpose input/output port C6 for CH0a/CH1a 2 GPIOA0_b I/O I General-purpose input/output port C7 for CH0a/CH1a 5 GPIOA1_b I/O I General-purpose input/output port A0 for CH0b/CH1b [5 tolerant pin] 6 GPIOB0_b I/O I General-purpose input/output port A1 for CH0b/CH1b [5 tolerant pin] 5 GPIOB1_b I/O I General-purpose input/output port B1 for CH0b/CH1b [5 tolerant pin] 4 GPIOB2_b I/O I General-purpose input/output port B2 for CH0b/CH1b [5 tolerant pin] 5 GPIOB3_b I/O I General-purpose input/output port B3 for CH0b/CH1b [5 tolerant pin] 6 GPIOB3_b I/O I General-purpose input/output port B3 for CH0b/CH1b [5 tolerant pin] 6 GPIOB3_b I/O I General-purpose input/output port C0 for CH0b/CH1b [5 tolerant pin] 6 GPIOC3_b I/O I General-purpose input/output port C0 for CH0b/CH1b [5 tolerant pin] 6 GPIOC3_b I/O I General-purpose input/output port C1 for CH0b/CH1b [5 tolerant pin] 6 GPIOC3_b I/O I General-purpose input/output port C3 for CH0b/CH1b [5 tolerant pin] General-purpose input/output port C3 for CH0b/CH1b [5 tolerant pin] General-purpose input/output port C3 for CH0b/CH1b [5 tolerant pin] General-purpose input/output port C4 for CH0b/CH1b [5 tolerant pin] General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC3_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC3_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b                                               | 79      | GPIOC0 a     | I/O  | 1               | , ,                                                     |

| 81 GPIOC2_a I/O I General-purpose input/output port C2 for CH0a/CH1a 82 GPIOC3_a I/O I General-purpose input/output port C3 for CH0a/CH1a 83 GPIOC4_a I/O I General-purpose input/output port C4 for CH0a/CH1a 84 GPIOC5_a I/O I General-purpose input/output port C5 for CH0a/CH1a 85 GPIOC6_a I/O I General-purpose input/output port C6 for CH0a/CH1a 86 GPIOC7_a I/O I General-purpose input/output port C7 for CH0a/CH1a 2 GPIOA0_b I/O I General-purpose input/output port A0 for CH0b/CH1b [5 tolerant pin] 4 GPIOB0_b I/O I General-purpose input/output port B0 for CH0b/CH1b [5 tolerant pin] 5 GPIOB1_b I/O I General-purpose input/output port B1 for CH0b/CH1b [5 tolerant pin] 6 GPIOB2_b I/O I General-purpose input/output port B2 for CH0b/CH1b [5 tolerant pin] 7 GPIOB3_b I/O I General-purpose input/output port B3 for CH0b/CH1b [5 tolerant pin] 8 GPIOC0_b I/O I General-purpose input/output port B3 for CH0b/CH1b [5 tolerant pin] 9 General-purpose input/output port B3 for CH0b/CH1b [5 tolerant pin] 9 General-purpose input/output port B3 for CH0b/CH1b [5 tolerant pin] 9 General-purpose input/output port C0 for CH0b/CH1b [5 tolerant pin] 9 General-purpose input/output port C0 for CH0b/CH1b [5 tolerant pin] 9 General-purpose input/output port C0 for CH0b/CH1b [5 tolerant pin] General-purpose input/output port C0 for CH0b/CH1b [5 tolerant pin] General-purpose input/output port C0 for CH0b/CH1b [5 tolerant pin] General-purpose input/output port C0 for CH0b/CH1b [5 GPIOC0_b I/O I General-purpose input/output port C0 for CH0b/CH1b [5 GPIOC0_b I/O I General-purpose input/output port C0 for CH0b/CH1b [5 GPIOC0_b I/O I General-purpose input/output port C0 for CH0b/CH1b [5 GPIOC0_b I/O I General-purpose input/output port C0 for CH0b/CH1b [5 GPIOC0_b I/O I General-purpose input/output port C0 for CH0b/CH1b [5 GPIOC0_b I/O I General-purpose input/output port C0 for CH0b/CH1b [5 GPIOC0_b I/O I General-purpose input/output port C0 for CH0b/CH1b [5 GPIOC0_b I/O I General-purpose input/output port C0 for CH0b/CH1b [5 GPIOC0_b I/O I General-purpose |         |              |      | †               |                                                         |

| B2 GPIOC3_a I/O I General-purpose input/output port C3 for CH0a/CH1a B3 GPIOC4_a I/O I General-purpose input/output port C4 for CH0a/CH1a B4 GPIOC5_a I/O I General-purpose input/output port C5 for CH0a/CH1a B5 GPIOC6_a I/O I General-purpose input/output port C6 for CH0a/CH1a B6 GPIOC7_a I/O I General-purpose input/output port C7 for CH0a/CH1a B6 GPIOA0_b I/O I General-purpose input/output port A0 for CH0b/CH1b [5 tolerant pin] B6 GPIOB0_b I/O I General-purpose input/output port A1 for CH0b/CH1b [5 tolerant pin] B6 GPIOB0_b I/O I General-purpose input/output port B0 for CH0b/CH1b [5 tolerant pin] B7 GPIOB1_b I/O I General-purpose input/output port B1 for CH0b/CH1b [5 tolerant pin] B8 GPIOB2_b I/O I General-purpose input/output port B2 for CH0b/CH1b [5 tolerant pin] B8 GPIOC0_b I/O I General-purpose input/output port B3 for CH0b/CH1b [5 tolerant pin] B8 GPIOC1_b I/O I General-purpose input/output port C0 for CH0b/CH1b [5 tolerant pin] B8 GPIOC2_b I/O I General-purpose input/output port C1 for CH0b/CH1b [5 tolerant pin] B7 GPIOC3_b I/O I General-purpose input/output port C3 for CH0b/CH1b [5 tolerant pin] B8 GPIOC3_b I/O I General-purpose input/output port C3 for CH0b/CH1b [5 tolerant-purpose input/output port C3 for CH0b/CH1b [5 tolerant-purpose input/output port C4 for CH0b/CH1b [5 tolerant-purpose input/output port C3 for CH0b/CH1b [5 tolerant-purpose input/output port C3 for CH0b/CH1b [5 tolerant-purpose input/output port C3 for CH0b/CH1b [5 tolerant-purpose input/output port C4 for CH0b/CH1b [5 tolerant-purpose input/output port C4 for CH0b/CH1b [5 tolerant-purpose input/output port C5 for CH0b/CH1b [5 tolerant-purpose input/output  |         |              |      | Ī               |                                                         |

| B3 GPIOC4_a I/O I General-purpose input/output port C4 for CH0a/CH1a B4 GPIOC5_a I/O I General-purpose input/output port C5 for CH0a/CH1a B5 GPIOC6_a I/O I General-purpose input/output port C6 for CH0a/CH1a B6 GPIOC7_a I/O I General-purpose input/output port C7 for CH0a/CH1a B6 GPIOC7_a I/O I General-purpose input/output port C7 for CH0a/CH1a B6 GPIOA0_b I/O I General-purpose input/output port A0 for CH0b/CH1b [5 tolerant pin] B6 GPIOB0_b I/O I General-purpose input/output port A1 for CH0b/CH1b [5 tolerant pin] B7 GPIOB1_b I/O I General-purpose input/output port B0 for CH0b/CH1b [5 tolerant pin] B8 GPIOB2_b I/O I General-purpose input/output port B1 for CH0b/CH1b [5 tolerant pin] B8 GPIOC0_b I/O I General-purpose input/output port B2 for CH0b/CH1b [5 tolerant pin] B8 GPIOC0_b I/O I General-purpose input/output port B3 for CH0b/CH1b [5 tolerant pin] B9 GPIOC2_b I/O I General-purpose input/output port C0 for CH0b/CH1b [5 tolerant pin] B9 GPIOC2_b I/O I General-purpose input/output port C1 for CH0b/CH1b [5 GPIOC3_b I/O I General-purpose input/output port C2 for CH0b/CH1b [5 GPIOC3_b I/O I General-purpose input/output port C3 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C3 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C3 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I GPIOC5_b I/O I GPIOC5_b I/O I GPIOC5_b I/O I G | 82      |              | I/O  | I               |                                                         |

| 85 GPIOC6_a I/O I General-purpose input/output port C6 for CH0a/CH1a 86 GPIOC7_a I/O I General-purpose input/output port C7 for CH0a/CH1a 2 GPIOA0_b I/O I General-purpose input/output port A0 for CH0b/CH1b [5 tolerant pin]  1 GPIOA1_b I/O I General-purpose input/output port A1 for CH0b/CH1b [5 tolerant pin]  6 GPIOB0_b I/O I General-purpose input/output port B0 for CH0b/CH1b [5 tolerant pin]  5 GPIOB1_b I/O I General-purpose input/output port B1 for CH0b/CH1b [5 tolerant pin]  4 GPIOB2_b I/O I General-purpose input/output port B2 for CH0b/CH1b [5 tolerant pin]  3 GPIOB3_b I/O I General-purpose input/output port B3 for CH0b/CH1b [5 tolerant pin]]  58 GPIOC0_b I/O I General-purpose input/output port C0 for CH0b/CH1b [5 tolerant pin]]  58 GPIOC1_b I/O I General-purpose input/output port C1 for CH0b/CH1b [5 tolerant pin]]  56 GPIOC2_b I/O I General-purpose input/output port C2 for CH0b/CH1b [5 GPIOC3_b I/O I General-purpose input/output port C3 for CH0b/CH1b [5 GPIOC4_b I/O I General-purpose input/output port C3 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C3 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 83      |              | I/O  | ı               |                                                         |

| B6 GPIOC7_a I/O I General-purpose input/output port C7 for CH0a/CH1a  2 GPIOA0_b I/O I General-purpose input/output port A0 for CH0b/CH1b [5 tolerant pin]  1 GPIOA1_b I/O I General-purpose input/output port A1 for CH0b/CH1b [5 tolerant pin]  6 GPIOB0_b I/O I General-purpose input/output port B0 for CH0b/CH1b [5 tolerant pin]  5 GPIOB1_b I/O I General-purpose input/output port B1 for CH0b/CH1b [5 tolerant pin]  4 GPIOB2_b I/O I General-purpose input/output port B2 for CH0b/CH1b [5 tolerant pin]  3 GPIOB3_b I/O I General-purpose input/output port B3 for CH0b/CH1b [5 tolerant pin]  58 GPIOC0_b I/O I General-purpose input/output port C0 for CH0b/CH1b [5 tolerant pin]  59 GPIOC1_b I/O I General-purpose input/output port C1 for CH0b/CH1b [5 tolerant pin]  50 GPIOC2_b I/O I General-purpose input/output port C2 for CH0b/CH1b [5 tolerant pin]  50 GPIOC3_b I/O I General-purpose input/output port C3 for CH0b/CH1b [5 tolerant pin]  50 GPIOC3_b I/O I General-purpose input/output port C3 for CH0b/CH1b [5 tolerant pin]  51 GPIOC3_b I/O I General-purpose input/output port C3 for CH0b/CH1b [5 tolerant pin]  52 GPIOC3_b I/O I General-purpose input/output port C3 for CH0b/CH1b [5 tolerant pin] [5 tolerant pin]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 84      | GPIOC5_a     | I/O  | I               | General-purpose input/output port C5 for CH0a/CH1a      |

| GPIOA0_b I/O I General-purpose input/output port A0 for CH0b/CH1b [5 tolerant pin]  GPIOA1_b I/O I General-purpose input/output port A1 for CH0b/CH1b [5 tolerant pin]  GPIOB0_b I/O I General-purpose input/output port B0 for CH0b/CH1b [5 tolerant pin]  GPIOB1_b I/O I General-purpose input/output port B1 for CH0b/CH1b [5 tolerant pin]  GPIOB2_b I/O I General-purpose input/output port B2 for CH0b/CH1b [5 tolerant pin]  GPIOB3_b I/O I General-purpose input/output port B3 for CH0b/CH1b [5 tolerant pin]  GPIOC0_b I/O I General-purpose input/output port C0 for CH0b/CH1b [5 tolerant pin]  GPIOC1_b I/O I General-purpose input/output port C1 for CH0b/CH1b  GPIOC2_b I/O I General-purpose input/output port C2 for CH0b/CH1b  GPIOC3_b I/O I General-purpose input/output port C3 for CH0b/CH1b  GPIOC4_b I/O I General-purpose input/output port C3 for CH0b/CH1b  GPIOC4_b I/O I General-purpose input/output port C4 for CH0b/CH1b  GPIOC5_b I/O I General-purpose input/output port C4 for CH0b/CH1b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 85      | GPIOC6_a     | I/O  | I               | General-purpose input/output port C6 for CH0a/CH1a      |

| tolerant pin]  GPIOA1_b I/O I General-purpose input/output port A1 for CH0b/CH1b [5 tolerant pin]  GPIOB0_b I/O I General-purpose input/output port B0 for CH0b/CH1b [5 tolerant pin]  GPIOB1_b I/O I General-purpose input/output port B1 for CH0b/CH1b [5 tolerant pin]  GPIOB2_b I/O I General-purpose input/output port B2 for CH0b/CH1b [5 tolerant pin]  GPIOB3_b I/O I General-purpose input/output port B3 for CH0b/CH1b [5 tolerant pin]  GPIOC0_b I/O I General-purpose input/output port C0 for CH0b/CH1b [5 tolerant pin]  GRIOC1_b I/O I General-purpose input/output port C1 for CH0b/CH1b [5 tolerant pin]  GRIOC2_b I/O I General-purpose input/output port C2 for CH0b/CH1b [5 GPIOC3_b I/O I General-purpose input/output port C3 for CH0b/CH1b [5 GPIOC4_b I/O I General-purpose input/output port C3 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C4 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C4 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I GPIOC5_b I/O I GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I GPI | 86      | GPIOC7_a     | I/O  | I               | General-purpose input/output port C7 for CH0a/CH1a      |

| 1 GPIOA1_b I/O I General-purpose input/output port A1 for CH0b/CH1b [5 tolerant pin]  6 GPIOB0_b I/O I General-purpose input/output port B0 for CH0b/CH1b [5 tolerant pin]  5 GPIOB1_b I/O I General-purpose input/output port B1 for CH0b/CH1b [5 tolerant pin]  4 GPIOB2_b I/O I General-purpose input/output port B2 for CH0b/CH1b [5 tolerant pin]  3 GPIOB3_b I/O I General-purpose input/output port B3 for CH0b/CH1b [5 tolerant pin]  58 GPIOC0_b I/O I General-purpose input/output port C0 for CH0b/CH1b [5 tolerant pin]  57 GPIOC1_b I/O I General-purpose input/output port C1 for CH0b/CH1b [5 GPIOC2_b I/O I General-purpose input/output port C2 for CH0b/CH1b [5 GPIOC3_b I/O I General-purpose input/output port C3 for CH0b/CH1b [5 GPIOC4_b I/O I General-purpose input/output port C3 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C4 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2       | CDIOA0 b     | 1/0  |                 | General-purpose input/output port A0 for CH0b/CH1b [5 V |

| tolerant pin]  GPIOB0_b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         | GPIOAU_D     | 1/0  | l               |                                                         |

| 6 GPIOB0_b I/O I General-purpose input/output port B0 for CH0b/CH1b [5 tolerant pin]  5 GPIOB1_b I/O I General-purpose input/output port B1 for CH0b/CH1b [5 tolerant pin]  4 GPIOB2_b I/O I General-purpose input/output port B2 for CH0b/CH1b [5 tolerant pin]  3 GPIOB3_b I/O I General-purpose input/output port B3 for CH0b/CH1b [5 tolerant pin]  58 GPIOC0_b I/O I General-purpose input/output port C0 for CH0b/CH1b [5 tolerant pin]  57 GPIOC1_b I/O I General-purpose input/output port C1 for CH0b/CH1b [5 GPIOC2_b I/O I General-purpose input/output port C2 for CH0b/CH1b [5 GPIOC3_b I/O I General-purpose input/output port C3 for CH0b/CH1b [5 GPIOC4_b I/O I General-purpose input/output port C3 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C4 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I GPIOC5_b I/O  | 1       | GPIOA1 h     | 1/0  |                 | General-purpose input/output port A1 for CH0b/CH1b [5 V |

| 6 GPIOB0_b I/O I tolerant pin]  5 GPIOB1_b I/O I General-purpose input/output port B1 for CH0b/CH1b [5 tolerant pin]  4 GPIOB2_b I/O I General-purpose input/output port B2 for CH0b/CH1b [5 tolerant pin]  3 GPIOB3_b I/O I General-purpose input/output port B3 for CH0b/CH1b [5 tolerant pin]  58 GPIOC0_b I/O I General-purpose input/output port C0 for CH0b/CH1b  57 GPIOC1_b I/O I General-purpose input/output port C1 for CH0b/CH1b  56 GPIOC2_b I/O I General-purpose input/output port C2 for CH0b/CH1b  55 GPIOC3_b I/O I General-purpose input/output port C3 for CH0b/CH1b  54 GPIOC4_b I/O I General-purpose input/output port C4 for CH0b/CH1b  53 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         | OI IOAI_b    | 1/0  | '               | 1 1                                                     |

| 5 GPIOB1_b I/O I General-purpose input/output port B1 for CH0b/CH1b [5 tolerant pin]  4 GPIOB2_b I/O I General-purpose input/output port B2 for CH0b/CH1b [5 tolerant pin]  3 GPIOB3_b I/O I General-purpose input/output port B3 for CH0b/CH1b [5 tolerant pin]  58 GPIOC0_b I/O I General-purpose input/output port C0 for CH0b/CH1b [5 tolerant pin]  57 GPIOC1_b I/O I General-purpose input/output port C1 for CH0b/CH1b [5 GPIOC2_b I/O I General-purpose input/output port C2 for CH0b/CH1b [5 GPIOC3_b I/O I General-purpose input/output port C3 for CH0b/CH1b [5 GPIOC4_b I/O I General-purpose input/output port C3 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C4 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b [5 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6       | GPIOR0 h     | I/O  | 1               |                                                         |

| tolerant pin]  4 GPIOB2_b I/O I General-purpose input/output port B2 for CH0b/CH1b [5 tolerant pin]  3 GPIOB3_b I/O I General-purpose input/output port B3 for CH0b/CH1b [5 tolerant pin]  58 GPIOC0_b I/O I General-purpose input/output port C0 for CH0b/CH1b  57 GPIOC1_b I/O I General-purpose input/output port C1 for CH0b/CH1b  56 GPIOC2_b I/O I General-purpose input/output port C2 for CH0b/CH1b  55 GPIOC3_b I/O I General-purpose input/output port C3 for CH0b/CH1b  54 GPIOC4_b I/O I General-purpose input/output port C4 for CH0b/CH1b  57 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b  58 GPIOC5_b I/O I General-purpose input/output port C5 for CH0b/CH1b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |              | ., 0 |                 | 1 1                                                     |