# Oki, Network Solutions for a Global Society

# **OKI Semiconductor**

**FEDL7731-02-11** Issue Date: Sep. 2, 2003

# MSM7731-02

Dual Echo Canceler & Noise Canceler with Dual Codec for Hands-Free

#### **GENERAL DESCRIPTION**

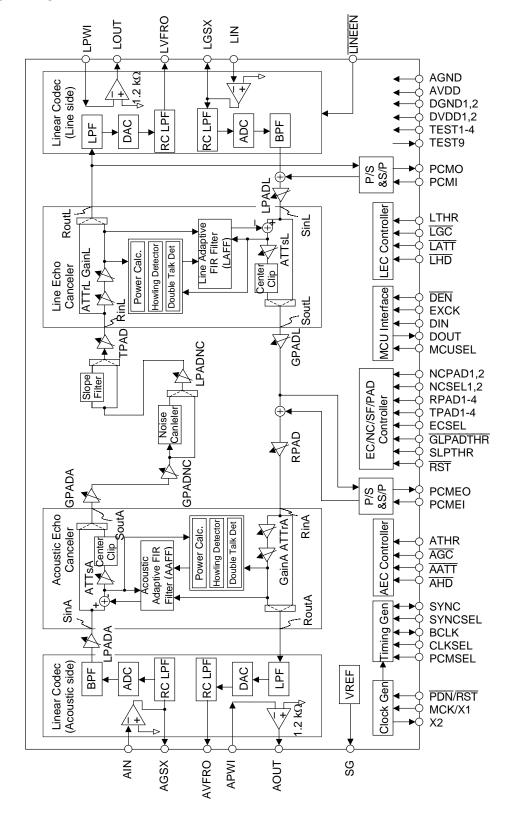

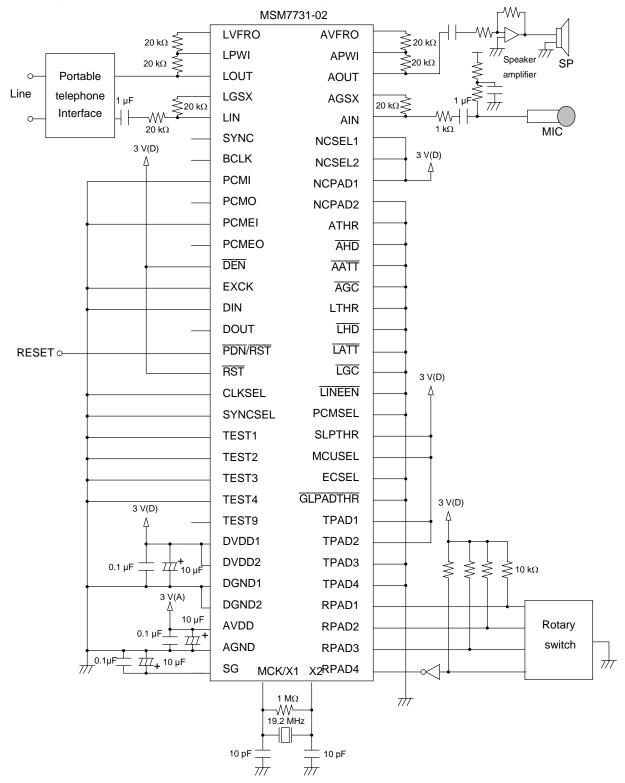

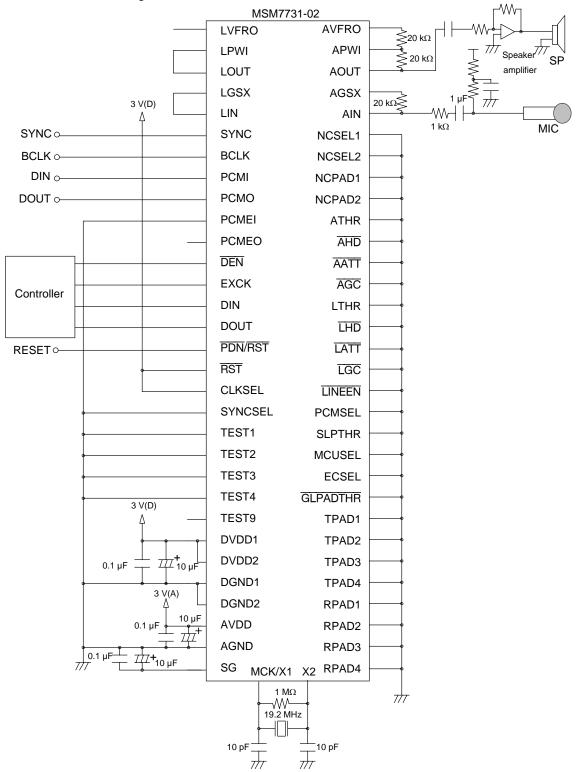

The MSM7731 is an IC device developed for portable, handsfree communication with built-in line echo canceler, acoustic echo canceler, and transmission signal noise canceler. Built-in to the voice signal interface is a linear CODEC for the analog interface on the acoustic-side, and a linear CODEC for the analog interface on the line-side. On the line-side, in addition to the analog interface, there is also a  $\mu$ -law PCM/16-bit linear digital interface. Equipped with gain and mute controls for data transmission and reception, a  $\mu$ -law PCM/16-bit linear digital interface for memo recording and message output, and transfer clock and sync clock generators for digital communication, this device is ideally suited for a handsfree system.

#### **FEATURES**

• Single 3 V Power Supply Operation (2.7 to 3.6 V)

• Built-in 2-channel (line and acoustic) echo canceler

Echo attenuation : 35 dB (typ.) for white noise

Cancelable echo delay time :

Line echo canceler + acoustic echo canceler : Tlined = 27 ms (max.)

Tacoud = 59 ms - Tlined (max.)

Acoustic echo canceler only : Tacoud = 59 ms (max.)

• Built-in transmission signal noise canceler

Noise attenuation : 17 dB (typ.) for white noise 40 dB (typ.) for single tone

• Built-in 2-channel CODEC

Synchronous transmission and reception enables full duplex operation

• Built-in analog input gain amp stage (max. gain = 30 dB)

• Analog output configuration: Push-pull drive (can drive a 1.2 k $\Omega$  load)

• Built-in transmit slope filter

• Digital interface coding formats : μ-law PCM, 16-bit linear (2's complement)

• Digital interface sync formats : Normal-sync, short-frame-sync

• Built-in digital transmission clock generators

Sync clock (SYNC) : 8 kHz output

Transmission clock (BCLK) : 64 kHz output (µ-law PCM)/128 kHz output (16-bit linear)

· Digital transmission rate

External input : 64 to 2048 kbps

Internal generation : 64 kbps (μ-law PCM)/128 kbps (16-bit linear)

• Fixed digital interface sync clock (SYNC) enables automatic power-down

• Master clock frequency : 19.2 MHz Compatible with crystal oscillator and crystal

• Low power consumption

Operating mode : typ. 35 mA (when  $V_{DD} = 3.0 \text{ V}$  in a silent mode) Power down operation : typ. 0.02 mA (when  $V_{DD} = 3.0 \text{ V}$  in a silent mode)

Control by both the serial microcomputer interface and parallel port is possible

Transmit/receive mute function, transmit/receive programmable gain setting

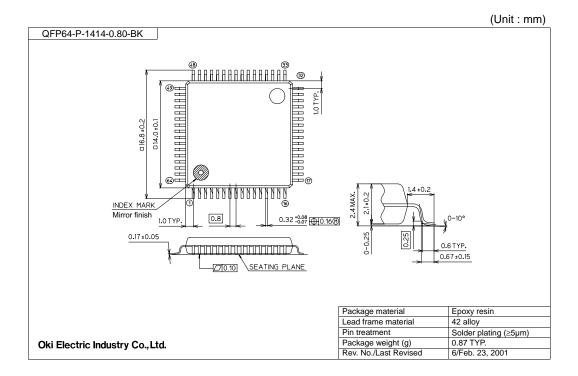

• Package : 64-pin plastic QFP (QFP64-P-1414-0.80-BK)(MSM7731-02GA)

# **BLOCK DIAGRAM**

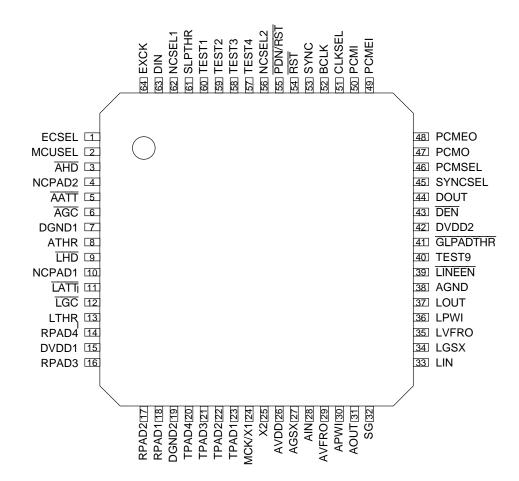

# PIN CONFIGURATION (TOP VIEW)

64-Pin Plastic QFP

# PIN FUNCTIONAL DESCRIPTION

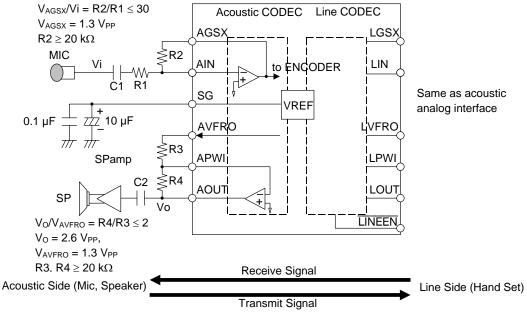

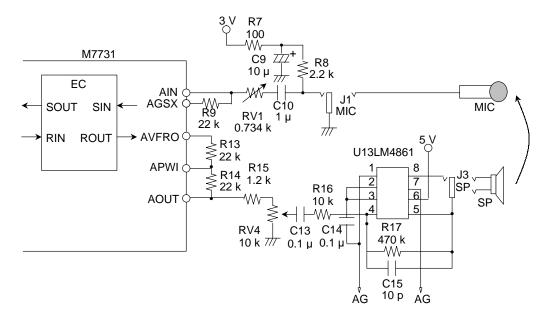

#### AIN, AGSX

These are the acoustic analog input and level adjusting pins. The AIN pin is connected to the inverting input of the internal amp and the AGSX pin is connected to the amp output. For level adjustment, refer to the diagram below (Figure 1). At power-down reset, the AGSX pin goes to a high impedance state.

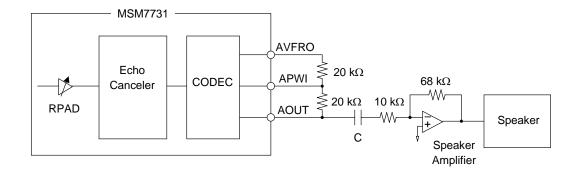

# AVFRO, AOUT, APWI

These are acoustic analog output and level adjusting pins. The AVFRO pin is an audio output and can directly drive  $20 \text{ k}\Omega$ . The AOUT pin is an analog output and can directly drive a load of  $1.2 \text{ k}\Omega$ . For level adjustment, refer to the diagram below (Figure 1). At power-down reset, these output pins go to a high impedance state.

# LIN, LGSX

These are the line analog input and level adjusting pins. The LIN pin is connected to the inverting input of the internal amp and the LGSX pin is connected to the amp output. For level adjustment, refer to the diagram below (Figure 1). At power-down reset, the LGSX pin goes to a high impedance state. If LIN is not used, short the LIN and LGSX together.

#### LVFRO, LOUT, LPWI

These are acoustic analog output and level adjusting pins. The LVFRO pin is an audio output and can directly drive  $20 \text{ k}\Omega$ . The LOUT pin is an analog output and can directly drive a load of  $1.2 \text{ k}\Omega$ . For level adjustment, refer to the diagram below (Figure 1). At power-down reset, these output pins go to a high impedance state. If LOUT is not used, short the LPWI and LOUT pins together.

# **LINEEN**

This is the power-down control pin for the line CODEC. A logic "0" continues normal operation and a logic "1" power down only the line CODEC. If the line CODEC is not used, power down the line CODEC and short the LIN pin to the LGSX pin and the LPWI pin to the LOUT pin. This procedure results in the low consumption of electrical power. At power-down, the output pins go to a high impedance state. If the pin setting is changed, reset must be activated by either the  $\overline{\text{PDN/RST}}$  pin or the PDN/RST bit (CR0-B7). This pin is ORed with CR0-B5 of the control register. Refer to the section "RELATIONSHIP BETWEEN PINS AND CONTROL REGISTERS".

Figure 1 Analog Interface

#### **AGND**

This is analog ground pin.

#### DGND1, DGND2

These are the digital ground pins.

#### $AV_{DD}$

This is the analog +3 V power supply pin.

# $DV_{DD1}$ , $DV_{DD2}$

These are the digital +3 V power supply pins.

#### SG

This is the output pin for the analog signal ground potential. The output voltage is approximately 1.4 V. Insert 10  $\mu F$  and 0.1  $\mu F$  ceramic bypass capacitors between the AGND and SG pin. At power-down rest, this output becomes 0 V.

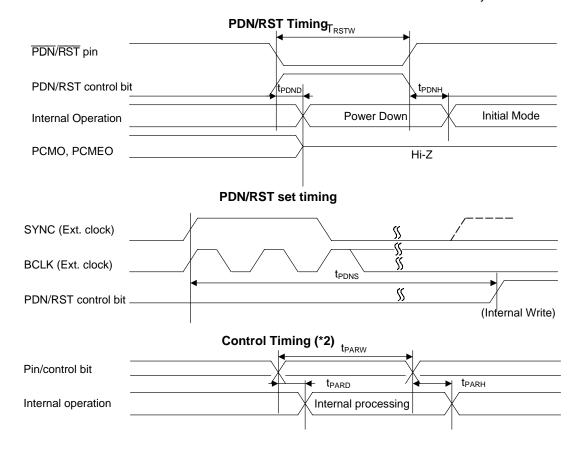

# PDN/RST

This is the power-down reset control input pin. If a logic "0" is input to this pin, the device enters the power-down state. At this time, all control register bits, internal variables, and coefficients of echo cancelers and noise cancelers will be reset. After the power-down reset state is released, the device enters the initial mode (refer to the CR0 control register description). During normal operation, set this pin to a logic "1". The PDN/RST pin is ORed (negative logic) with CR0-B7 of the control register. Refer to the section "RELATIONSHIP BETWEEN PINS AND CONTROL REGISTERS".

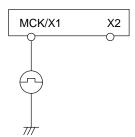

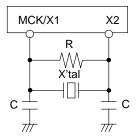

#### MCK/X1

This is the master clock input pin. The clock frequency is 19.2 MHz. The input clock may be asynchronous with respect to the SYNC signal or the BCLK signal. Refer to Figure 2 (a) for an example application of an external clock and Figure 2 (b) for an example oscillator circuit.

## X2

This is the crystal oscillator output pin. If an existing external clock is to be used, leave this pin open and input the clock to the MCK pin. Refer to Figure 2 (b) for an example oscillator circuit.

| X'tal (19.2 MHz) | С     | R    |

|------------------|-------|------|

| HC-49/U          | 10 pF | 1 ΜΩ |

Figure 2 (a) External Clock Application Example

Figure2 (b) Oscillator Circuit Example

# **SYNC**

This is the 8 kHz sync signal I/O pin for digital data communication. This pin is switched to unction as an input or output by the CLKSEL pin. If the internal clock mode is selected by the CLKSEL pin, an 8 kHz clock synchronized to be BCLK signal is output and digital data communication is performed. If the external clock mode is selected by the CLKSEL pin, this pin becomes an input that requires an 8 kHz clock input synchronized to be BCLK pin, and digital data communication is performed based on this input clock. This pin enables automatic power-down control. Fixing this pin to a logic "1" or logic "0" causes this device to enter the power-down state. Two kinds of power-down modes can be selected by the SYPDN (CR11-B0) bit of the control register. For the power-down mode, refer to the description of control register CR11.

#### **BCLK**

This is the shift clock I/O pin for digital data communication. This pin is switched to function as an input or output by the CLKSEL pin.

If the internal clock mode is selected by the CLKSEL pin, a 64 kHz or 128 kHz clock synchronized to the SYNC signal is output and digital data communication is performed. Regardless of the PCMSEL (CR11-B1) setting, when this pin is set to a logic "1", the BCLK-pin outputs 64kHz clocks; when this pin is set to a logic "0", the BCLK-pin outputs 128kHz clocks.

If the external clock mode is selected by the CLKSEL pin, this pin becomes an input that requires a clock input synchronized to the SYNC. In this case, the clock frequency range is from 64 kHz to 2048 kHz.

#### **CLKSEL**

This pin selects internal or external clock modes for the SYNC and BCLK signals. A logic "0" selects the internal clock mode. At this time, SYNC and BCLK pins are configured as output pins and each internally generated clock is output to perform digital data communication. A logic "1" selects the external clock mode and configures the SYNC and BCLK pins as input pins. At this time, digital data communication is performed with the externally input SYNC and BCLK clocks. If digital data communication is not used, set this pin to a logic "0" to select internal clocks. If the pin setting is changed, reset must be activated by either the  $\overline{\text{PDN/RST}}$  pin or the PDN/RST bit (CR0-B7).

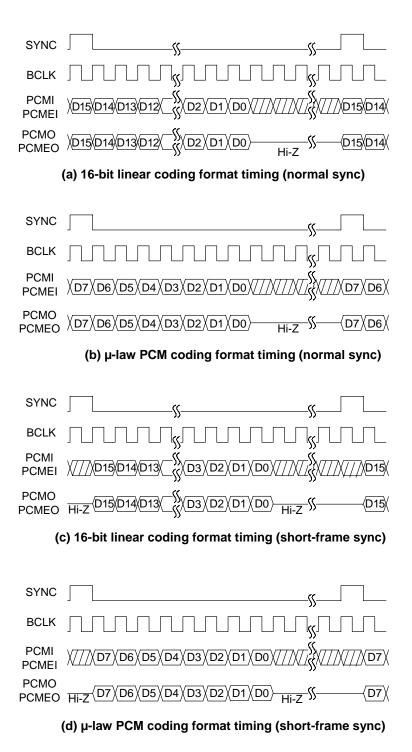

#### **PCMI**

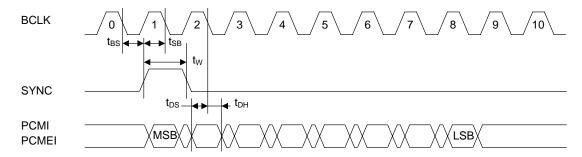

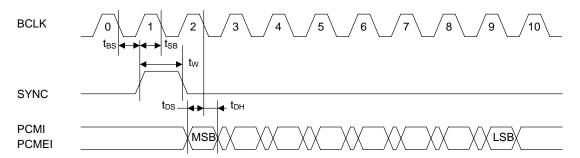

This is the digital receive signal input pin on the line-side. This input signal is shifted at the rising edge of the BCLK signal and input. The beginning of digital data is identified on the rising edge of the SYNC signal. The coding format can be selected as  $\mu$ -law PCM or 16-bit linear (2's complement) by the PCMSEL pin or PCMSEL (CR11-B1) bit. If the PCMI pin is not used, set it to a logic "1" if  $\mu$ -law PCM has been selected, or a logic "0" if 16-bit linear mode has been selected. The sync format can be selected as normal-sync or short-frame-sync by the SYNCSEL pin. Refer to Figure 3 for the timing. This digital input signal is added internally to the CODEC digital output signal. Be careful of overflow when using the CODEC.

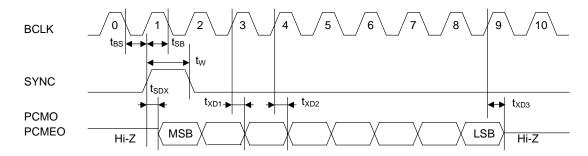

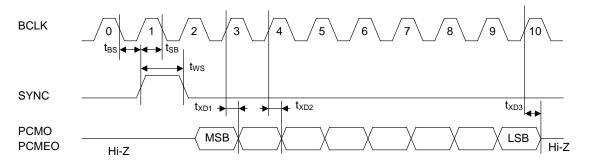

#### **PCMO**

This is the digital transmit signal output pin on the line-side. This output signal is synchronized to the rising edge of the BCLK and SYNC signals and then output. When not used for output, this pin is in the high impedance state. It is at high impedance during the power-down reset and the initial modes. The coding format can be selected as  $\mu$ -law PCM or 16-bit linear (2's complement) by the PCMSEL pin or PCMSEL (CR11-B1) bit. The sync format can be selected as normal-sync or short-frame-sync by the SYNCSEL pin. Refer to Figure 3 for the timing.

#### **PCMEI**

This is the massage signal input pin. Use this pin when a massage is output to the speaker on the acoustic-side. This input signal is shifted at the rising edge of the BCLK signal and then input. The beginning of digital data is identified on the rising edge of the SYNC signal. The coding format can be selected as  $\mu$ -law PCM or 16-bit linear (2's complement) by the PCMSEL pin or PCMSEL (CR11-B1) bit. If the PCMEI pin is not used, set it to a logic "1" if  $\mu$ -law PCM has been selected, or a logic "0" if 16-bit linear mode has been selected. The sync format can be selected as normal-sync or short-frame sync by the SYNCSEL pin. Timing is the same as for the PCMI pin (refer to Figure 3). This digital input signal is added internally to the echo canceler output signal. Be careful of overflow during telephone conversations.

#### **PCMEO**

This output pin is for memo recording. Use it with the memo function. This output signal is synchronized to the rising edge of the BCLK an SYNC signals and then output. When not used for output, this pin is in the high impedance state. It is also at high impedance during the power-down reset and the initial modes. The coding format can be selected as  $\mu$ -law PCM or 16-bit linear (2's complement) by the PCMSEL pin or PCMSEL (CR11-B1) bit. The sync format can be selected as normal-sync or short-frame-sync by the SYNCSEL pin. Timing is the same as for the PCMO pin (refer to Figure 3).

#### SYNCSEL

This is the sync timing selection pin for digital data communication. A logic "0" selects normal-sync timing and a logic "1" selects short-frame-sync timing. Refer Figure 3 for the timing. If the pin setting is changed, reset must be activated by either the  $\overline{\text{PDN}}/\overline{\text{RST}}$  pin or the PDN/RST bit (CR0-B7)

#### **PCMSEL**

This is the coding format selection pin for digital data communication. A logic "1" selects  $\mu$ -law PCM and a logic "0" selects 16-bit linear (2's complement) coding format. When an internal clock is selected, the BCLK signal determines the output clock frequency. If the digital interface is not used, set this pin to logic "0" to select 16-bit linear coding format.

If the pin setting is changed, reset must be performed by either the  $\overline{PDN/RST}$  pin or the PDN/RST bit (CR0-B7). This pin is logically ORed with the PCMSEL bit (CR11-B1) although the BCLK output frequency in an internal clock mode is solely as per this pin regardless of the PCMSEL bit (CR11-B1). Refer to the section "RELATIONSHIP BETWEEN PINS AND CONTROL REGISTERS".

# **SLPTHR**

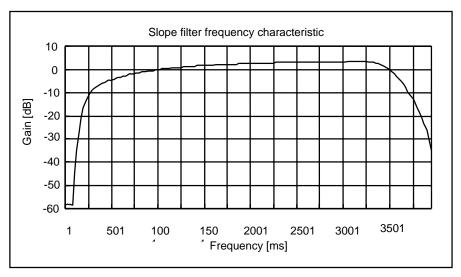

This is the "through mode" control pin for the transmit slope filter. In the "through mode", the filter is halted and data is directly output. A logic "0" selects the normal mode (slope filter operation) and a logic "1" selects the "through mode". The slope filter decreases noises of low frequencies and improves speech quality. Refer to the slope filter frequency characteristics. Because data is shifted into this pin in synchronization with the rising edge of the SYNC signal, hold the data at the pin for 250  $\mu s$  or longer. For further details, refer to the electrical characteristics. This pin is ORed with the CR1-B1 bit of the control register. Refer to the section "RELATIONSHIP BETWEEN PINS AND CONTROL REGISTERS".

Figure 3 Digital Interface Timing

#### **ECSEL**

This is the echo canceler mode selection pin. A logic "1" selects the single echo canceler mode and a logic "0" selects the dual echo canceler mode. If the pin setting is changed, reset must be activated by either the  $\overline{PDN/RST}$  pin or the PDN/RST bit (CR0-B7). If the single echo canceler mode is selected, echo canceler control on the line-side is unnecessary. This pin is ORed with the CR0-B0 bit of the control register. Refer to the section "RELATIONSHIP BETWEEN PINS AND CONTROL REGISTERS".

#### LTHR/ATHR

This is the "through mode" control pin for the echo canceler. In the "through mode", SinL/A and RinL/A data is directly output to SoutL/A and RoutL/A respectively while each respective echo coefficient is maintained. A logic "0" selects the normal mode (echo canceler operation) and a logic "1" selects the "through mode". In the through mode, the functions of HD, HLD, ATT and GC are invalid. Because data is shifted into this pin in synchronization with the rising edge of the SYNC signal, hold the data at the pin for 250  $\mu$ s or longer. This pin is ORed with the CR4-B7 and CR5-B7 bits of the control register. Refer to the section "RELATIONSHIP BETWEEN PINS AND CONTROL REGISTERS".

# **LHD/AHD**

This pin turns ON or OFF the function to detect and cancel the howling that occurs in an acoustic system such as a handsfree communication system. A logic "0" turns the function ON and a logic "1" turns the function OFF. This function is valid when the LTHR/ATHR pin is in the normal mode. Because data is shifted into this pin in synchronization with the rising edge of the SYNC signal, hold the data at the pin for 250  $\mu$ s or longer. This pin is ORed with the CR4-B4 and CR4-B4 and CR5-B4 bits of the control register. Refer to the section "RELATIONSHIP BETWEEN PINS AND CONTROL REGISTERS".

# **LATT**

This pin turns ON or OFF the ATT function to prevent howling by means of attenuators (ATTsL, ATTrL) provided in the RinL inputs and SoutL outputs of the echo canceler. A logic "0" turns ON and a logic "1" turns OFF the ATT function. If input is only to RinL, the ATTsL for SoutL is activated. If input is only to SinL, or if there is input to both SinL and RinL, the ATTrL for RinL input is activated. The ATT value of each attenuator is approximately 6 dB. This function is valid when the LTHR pin is in the normal mode. Because data is shifted into this pin in synchronization with the rising edge of the SYNC signal, hold the data at the pin for 250  $\mu$ s or longer. This pin setting is logically ORed with the CR4-B1 bit of the control register. Refer to the section "RELATIONSHIP BETWEEN PINS AND CONTROL REGISTERS".

#### **AATT**

This is the ATT atlenuation selection pin to prevent howling by means of attenuators (ATTsA, ATTrA) provided in the RinA inputs and SoutA outputs of the echo canceler. A logic "0" selects 6 dB and a logic "1" selects 12 dB. If input is only to RinA, the ATTsA for SoutA is activated. If input is only to SinA, or if there is input to both SinA and RinA, the ATTrA for RinA input is activated. This function is valid when the ATHR pin is in the normal mode. Because data is shifted into this pin in synchronization with the rising edge of the SYNC signal, hold the data at the pin for 250  $\mu$ s or longer. This pin setting is logically ORed with the CR5-B1 bit of the control register. Refer to the section "RELATIONSHIP BETWEEN PINS AND CONTROL REGISTERS".

#### **LGC/AGC**

This pin turns ON or OFF the gain control function to control the input level and prevent howling by means of gain controls (GainL/A) provided in the RinL/A inputs of the echo canceler. The gain controller adjusts the RinL/A input level when it is -10 dBm0 or above, and it has the control range of 0 to -8.5 dB. A logic "0" turns the function ON and a logic "1" turns the function OFF. This function is valid when the LTHR/ATHR pin is in the mormal mode. Because data is shifted into this pin in synchronization with the rising edge of the SYNC signal, hold the data at the pin for 250  $\mu$ s or longer. This pin is ORed with the CR4-B0 and CR5-B0 bits of the control register. Refer to the section "RELATIONSHIP BETWEEN PINS AND CONTROL REGISTERS".

#### Notes:

Lxx/Axx : In the above, Lxx refers to line echo canceler control pins and Axx to acoustic echo canceler control pins.

xxL/xxA : In the above pin descriptions, xxL refers to line echo canceler functions and xxA to acoustic echo canceler functions.

#### **GLPADTHR**

This is the mode control pin for the attenuators (LPADL/A) provided in the SinL/A inputs and the amplifiers (GPADL/A) provided in the SoutL/A outputs of the echo canceler. A logic "0" selects the "through mode" and a logic "1" selects the normal mode (PAD operation). The levels are set by the CR10 register. Settings of  $\pm$  18,  $\pm$  12,  $\pm$  6 and 0 dB are possible. The default setting is  $\pm$  12 dB. If the echo return loss (value of returned echo) is amplified, set the LPAD level such that echo return loss will be attenuated. It is recommended to set the GPAD level to the positive level equal to the LPAD level. If the pin setting is changed, the coefficient reset must be activated by either the  $\overline{RST}$  pin or the RST bit (CR0-B6). Because data is shifted into this pin in synchronization with the rising edge of the SYNC signal, hold the data at the pin for 250  $\mu$ s or longer. This pin is ORed with the CR1-B2 bit of the control register. Refer to the section "RELATIONSHIP BETWEEN PINS AND CONTROL REGISTERS".

## $\overline{RST}$

This input pin resets coefficients of the echo canceler and noise canceler. A logic "0" causes the reset state to be entered. At this time, the filter coefficients for the echo canceler and noise canceler are reset. Control register contents are preserved. While reset is being processed, there is not sound. During normal operation, set this pin to a logic "1". Use this pin in cases where the echo path changes (due to line switching during a telephone conversation, etc.), or when resuming telephone communication. Because data is shifted into this pin in synchronization with the rising edge of the SYNC signal, hold the data at the pin for 250 µs or longer. This pin is ORed (negative logic) with the CR0-B6 bit of the control register. Refer to the section "RELATIONSHIP BETWEEN PINS AND CONTROL REGISTERS".

#### NCSEL1, NCSEL2

These are the noise attenuation selection pins. In the "through mode" the noise canceler is halted and data is directly output. In the "normal mode" the noise canceler operates normally. Since the noise attenuation in the normal mode is selected after the initial mode has been released, the change of the noise attenuation during normal operation is invalid. If the noise attenuation is changed, reset must be activated by the  $\overline{\text{RDN/RST}}$  pin or the PDN/RST bit (CR0-B7). Changing to the through mode during normal operation and returning to the normal mode are possible. The NCSEL1 pin is ORed with the CR1-B0 bit of the control register and the NCSEL2 pin is ORed with the CR12-B2 bit of the control register. Refer to the section "RELATIONSHIP BETWEEN PINS AND CONTROL REGISTERS".

#### Note:

Since there is a trade-off between noise attenuation and sound quality after canceling the noise, select the noise attenuation appropriate to the sound quality.

| NCSEL2 | NCSEL1 | NC Mode      | Attenuation (dB) | Quality   |

|--------|--------|--------------|------------------|-----------|

| 0      | 0      | Normal Mode  | 17               | Better    |

| 1      | 1      | Normal Mode  | 13.5             | <b>\$</b> |

| 1      | 0      | Normal Mode  | 8                | Best      |

| 0      | 1      | Through Mode | _                | _         |

#### NCPAD1, NCPAD2

These are the noise canceler I/O gain adjusting pins. The gain adjustment is valid for tone control after canceling the noise. The bigger the input level of the noise canceler is, the better the sound quality is. The NCPAD1 pin is ORed with the CR4-B2 bit of the control register and the NCPAD2 pin is ORed with the CR5-B2 bit of the control register. Refer to the section "RELATIONSHIP BETWEEN PINS AND CONTROL REGISTERS".

| NCPAD2 | NCPAD1 | GPADNC (dB) | LPADNC (dB) |

|--------|--------|-------------|-------------|

| 0      | 0      | 0           | 0           |

| 0      | 1      | 6           | -6          |

| 1      | 0      | 12          | -12         |

| 1      | 1      | 18          | -18         |

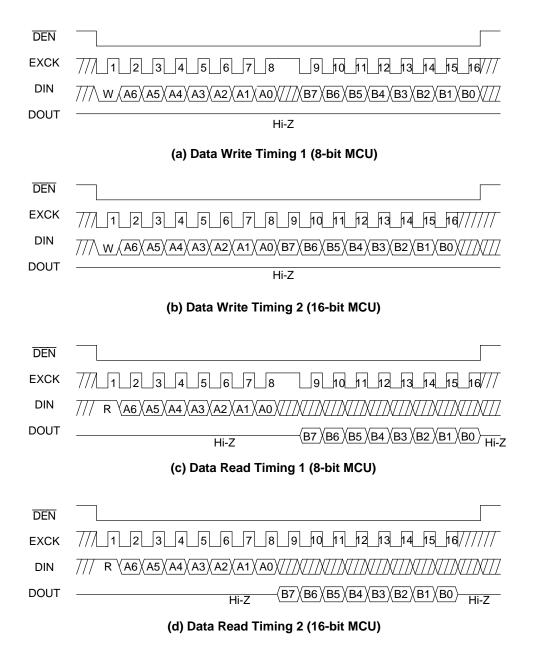

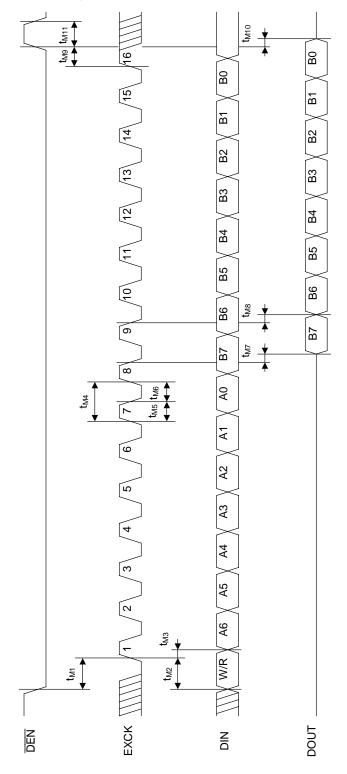

# **DEN**, EXCK, DIN, DOUT

This is the serial port for the microcontroller interface. 13 bytes of control registers are provided in this IC device. There pins are used to write and read data from an external microcontroller. The  $\overline{DEN}$  pin is an enable signal input pin, the EXCK pin is a clock signal input pin for data shifting, the DIN pin is an address and data input pin, the DOUT pin is a data output pin. If the mirrocontroller interface is not used, set the  $\overline{DEN}$  pin to a logic "1" and the EXCK and DIN pins to a logic "0". In addition, use the MCUSEL pin to specify the "unused" setting of the microcontroller interface. Figure 4 shows the input timing.

#### **MCUSEL**

This pin selects whether the microcontroller interface is used or unused. A logic "0" specifies that the microcontroller interface is used and a logic "1" specifies that it is not used. If the microcontroller interface is not used, this pin must be set to a logic "1". This pin is ORed with the CR0-B1 bit of the control register. Refer to the section "RELATIONSHIP BETWEEN PINS AND CONTROL REGISTERS".

Figure 4 Microcontroller Interface I/O Timing

# RPAD4, RPAD3, RPAD2, RPAD1

These are the receive signal gain adjusting and mute setting pins. Refer to Table 1 for the settings. Set these pins to a logic "0" when controlling by the control register. Because data is shifted into this pin in synchronization with the rising edge of the SYNC signal, hold the data at the pin for 250  $\mu$ s or longer. For further details, refer to the electrical characteristics. These pins are ORed with the CR2-B3, B2, B1 and B0 bits of the control register. Refer to the section "RELATIONSHIP BETWEEN PINS AND CONTROL REGISTERS".

# TPAD4, TPAD3, TPAD2, TPAD1

These are the transmit signal gain adjusting and mute setting pins. Refer to Table 1 for the settings. Set these pins to a logic "0" when controlling by the control register. Because data is shifted into this pin in synchronization with the rising edge of the SYNC signal, hold the data at the pin for 250  $\mu$ s or longer. For further details, refer to the electrical characteristics. These pins are ORed with the CR3-B3, B2, B1 and B0 bits of the control register. Refer to the section "RELATIONSHIP BETWEEN PINS AND CONTROL REGISTERS".

Table 1 RPAD/TPAD Setting

| RPAD4 | RPAD3 | RPAD2 | RPAD1 |

|-------|-------|-------|-------|

| 0     | 1     | 1     | 1     |

| 0     | 1     | 1     | 0     |

| 0     | 1     | 0     | 1     |

| 0     | 1     | 0     | 0     |

| 0     | 0     | 1     | 1     |

| 0     | 0     | 1     | 0     |

| 0     | 0     | 0     | 1     |

| 0     | 0     | 0     | 0     |

| 1     | 1     | 1     | 1     |

| 1     | 1     | 1     | 0     |

| 1     | 1     | 0     | 1     |

| 1     | 1     | 0     | 0     |

| 1     | 0     | 1     | 1     |

| 1     | 0     | 1     | 0     |

| 1     | 0     | 0     | 1     |

| 1     | 0     | 0     | 0     |

| TPAD4 | TPAD3 | TPAD2 | TPAD1 | Level  |

|-------|-------|-------|-------|--------|

| 0     | 1     | 1     | 1     | 21 dB  |

| 0     | 1     | 1     | 0     | 18 dB  |

| 0     | 1     | 0     | 1     | 15 dB  |

| 0     | 1     | 0     | 0     | 12 dB  |

| 0     | 0     | 1     | 1     | 9 dB   |

| 0     | 0     | 1     | 0     | 6 dB   |

| 0     | 0     | 0     | 1     | 3 dB   |

| 0     | 0     | 0     | 0     | 0 dB   |

| 1     | 1     | 1     | 1     | −3 dB  |

| 1     | 1     | 1     | 0     | −6 dB  |

| 1     | 1     | 0     | 1     | –9 dB  |

| 1     | 1     | 0     | 0     | –12 dB |

| 1     | 0     | 1     | 1     | –15 dB |

| 1     | 0     | 1     | 0     | –18 dB |

| 1     | 0     | 0     | 1     | –21 dB |

| 1     | 0     | 0     | 0     | MUTE   |

#### TEST1-4

Test inputs. Set these pins to a logic "0".

# TEST9

Test output.

# ABSOLUTE MAXIMUM RATINGS

| Parameter                     | Symbol           | Condition | Rating                       | Unit |

|-------------------------------|------------------|-----------|------------------------------|------|

| Power Supply Voltage          | $V_{DD}$         | _         | -0.3 to +5.0                 | V    |

| Analog/Digital Input Voltage  | V <sub>IN</sub>  | _         | −0.3 to V <sub>DD</sub> +0.3 | V    |

| Analog/Digital output Voltage | V <sub>OUT</sub> | _         | −0.3 to V <sub>DD</sub> +0.3 | V    |

| Storage Temperature           | T <sub>STG</sub> | _         | -55 to +150                  | °C   |

# RECOMMENDED OPERATING CONDITION

| Parameter                       | Symbol            | Condition                     | Min.                 | Тур.  | Max.                 | Unit |

|---------------------------------|-------------------|-------------------------------|----------------------|-------|----------------------|------|

| Power Supply Voltage            | $V_{DD}$          | _                             | 2.7                  | _     | 3.6                  | V    |

| Operating Temperature           | Ta                | _                             | -40                  | +25   | +85                  | °C   |

|                                 |                   | SYNC, BCLK input pins         | 0.5×V <sub>DD</sub>  |       |                      |      |

| Input High Voltage              | $V_{IH}$          | MCK/X1 input pin              | 0.65×V <sub>DD</sub> | _     | $V_{DD}$             | V    |

|                                 |                   | Other digital input pins      | 0.45×V <sub>DD</sub> |       |                      |      |

| logeth low Voltage              | \/                | MCK/X1 input pin              | 0                    |       | 0.35×V <sub>DD</sub> | V    |

| Input Low Voltage               | V <sub>IL</sub>   | Other digital input pins      | 0                    | _     | 0.16×V <sub>DD</sub> | V    |

| Digital Input Rise Time         | t <sub>IR</sub>   | All digital inputs            | _                    | _     | 20                   | ns   |

| Digital Input Fall Time         | t <sub>lf</sub>   | All digital inputs            | _                    | _     | 20                   | ns   |

| Master Clock Frequency          | f <sub>MCK</sub>  | MCK/X1                        | -100 ppm             | +19.2 | +100 ppm             | MHz  |

| Master Clock Duty Ratio         | D <sub>MCK</sub>  | MCK/X1                        | 40                   | 50    | 60                   | %    |

| Bit Clock Frequency             | f <sub>BCK</sub>  | BCLK (during input)           | 64                   | _     | 2048                 | kHz  |

| Bit Clock Duty Ratio            | D <sub>CK</sub>   | BCLK (during input)           | 40                   | 50    | 60                   | %    |

| Synchronous Signal<br>Frequency | f <sub>SYNC</sub> | SYNC (during input)           | -100 ppm             | 8     | +100 ppm             | kHz  |

| Synchronous Signal Width        | t <sub>WS</sub>   | SYNC (during input)           | 1 BCLK               | _     | 100                  | μs   |

| Transmit/Receive Sync           | t <sub>BS</sub>   | BCLK to SYNC (during input)   | 100                  | _     | _                    | ns   |

| Signal Setting Time             | t <sub>SB</sub>   | SYNC to BCLK (during input)   | 100                  | _     | _                    | ns   |

|                                 | R <sub>DL</sub>   | DOUT, PCMO, PCMEO             | 1                    | _     | _                    | kΩ   |

| Digital Output Load             | C <sub>DL1</sub>  | DOUT, PCMO, PCMEO             | _                    | _     | 50                   | pF   |

|                                 | C <sub>DL2</sub>  | SYNC, BCLK<br>(during output) |                      |       | 20                   | pF   |

| Bypass Condenser for SG         | C <sub>SG</sub>   | SG to AG                      | 10+0.1               | _     | _                    | μF   |

# **ELECTRICAL CHARACTERISTICS**

# **DC** Characteristics

$(V_{DD} = 2.7 \text{ to } 3.6 \text{ V}, \text{Ta} = -40 \text{ to } +85^{\circ}\text{C})$

| Parameter                            | Symbol           | Condition                                               | Min.                | Тур. | Max.     | Unit |

|--------------------------------------|------------------|---------------------------------------------------------|---------------------|------|----------|------|

| Power Supply Current 1               | I <sub>DD1</sub> | Operating, no signal (V <sub>DD</sub> = 3.0 V)          | _                   | 35   | 50       | mA   |

| Power Supply Current 2               | I <sub>DD2</sub> | Power down mode<br>(V <sub>DD</sub> = 3.0 V, MCK = 0 V) | _                   | 0.02 | 1        | mA   |

| Input Lookage Current                | I <sub>IH</sub>  | $V_{I} = V_{DD}$                                        | _                   | _    | 2        | μΑ   |

| Input Leakage Current                | I <sub>IL</sub>  | V <sub>I</sub> = 0 V                                    | _                   | _    | 2        | μΑ   |

| High Level Digital Output<br>Voltage | V <sub>OH</sub>  | I <sub>OH</sub> = 0.4 mA<br>(other than ×2)             | 0.7×V <sub>DD</sub> | _    | $V_{DD}$ | V    |

| Low Level Digital Output<br>Voltage  | V <sub>OL</sub>  | I <sub>OL</sub> = 3.2 mA<br>(other than ×2)             | —0                  | 0.2  | 0.4      | V    |

| Digital Output Leakage<br>Current    | Io               | DOUT, PCMO, PCMEO                                       | _                   | _    | 10       | μА   |

| Input Capacitance                    | C <sub>IN</sub>  | _                                                       | _                   | 5    | _        | pF   |

# **Analog Interface Characteristics**

$(V_{DD} = 2.7 \text{ to } 3.6 \text{ V}, \text{Ta} = -40 \text{ to } +85^{\circ}\text{C})$

| Parameter                 | Symbol            | Co             | ondition                    | Min. | Тур. | Max. | Unit |

|---------------------------|-------------------|----------------|-----------------------------|------|------|------|------|

| Input Desistance          | R <sub>INA</sub>  | AIN, APWI      |                             | 10   |      | ĺ    | MΩ   |

| Input Resistance          | R <sub>INL</sub>  | LIN, LPWI      |                             | 10   | _    |      | MΩ   |

|                           | R <sub>LA1</sub>  | AGSX, AV       | FRO                         | 20   | _    | _    | kΩ   |

| Output Load Booistones    | R <sub>LA2</sub>  | AOUT           |                             | 1.2  | _    | _    | kΩ   |

| Output Load Resistance    | R <sub>LL1</sub>  | LGSX, LVF      | RO                          | 20   | _    | _    | kΩ   |

|                           | R <sub>LL2</sub>  | LOUT           |                             | 1.2  |      |      | kΩ   |

| Output Load Canacitance   | C <sub>LA1</sub>  | AGSX, AV       | FRO, AOUT                   | _    | _    | 100  | pF   |

| Output Load Capacitance   | C <sub>LL1</sub>  | LGSX, LVF      | LGSX, LVFRO, LOUT           |      | _    | 100  | pF   |

|                           | V <sub>OA1</sub>  | AGSX,<br>AVFRO | $R_L = 20 \text{ k}\Omega$  | _    | _    | 1.3  | Vpp  |

| Output Valtage Level (*4) | V <sub>OA2</sub>  | AOUT           | $R_L = 1.2 \text{ k}\Omega$ | _    | _    | 2.6  | Vpp  |

| Output Voltage Level (*1) | V <sub>OL1</sub>  | LGSX,<br>LVFRO | $R_L = 20 \text{ k }\Omega$ | _    | _    | 1.3  | Vpp  |

|                           | V <sub>OL2</sub>  | LOUT           | $R_L = 1.2 \text{ k}\Omega$ | _    | _    | 2.6  | Vpp  |

|                           | V <sub>OFA1</sub> | AVFRO          |                             | -100 |      | +100 | mV   |

| Offeet Voltage            | V <sub>OFA2</sub> | AOUT           |                             | -20  |      | +20  | mV   |

| Offset Voltage            | $V_{OFL1}$        | LVFRO          |                             | -100 | _    | +100 | mV   |

|                           | V <sub>OFL2</sub> | LOUT           |                             | -20  |      | +20  | mV   |

| SG Output Voltage         | V <sub>SG</sub>   | SG             |                             |      | 1.4  | _    | V    |

| SG Output Impedance       | R <sub>SG</sub>   | SG             |                             | _    | 40   | 80   | kΩ   |

Note\*1:  $0.320 \text{ Vrms} = 0 \text{ dBm0}, +3.14 \text{ dBm0} = 1.30 \text{ V}_{PP}$

# **Digital Interface Characteristics (1/3)**

$(V_{DD} = 2.7 \text{ to } 3.6 \text{ V}, \text{Ta} = -40 \text{ to } +85^{\circ}\text{C})$

| Parameter                                 | Symbol            | Condition                           | Min. | Тур. | Max.  | Unit |

|-------------------------------------------|-------------------|-------------------------------------|------|------|-------|------|

| Power-down/Reset Signal                   | 4                 | PDN/RST pin                         | 1    |      |       |      |

| Pulse Width                               | t <sub>RSTW</sub> | PDN/RST control bit                 | 1.6  |      |       | μS   |

| Power-down/Reset Start<br>Time            | t <sub>PDND</sub> | PDN/RST pin and PDN/RST control bit | _    | _    | 50    | nS   |

| Power down/Reset End Time                 | t <sub>PDNH</sub> | PDN/RST pin and PDN/RST control bit | _    | _    | 200+α | mS   |

| Power-down/Reset Internal<br>Setting Time | t <sub>PDNS</sub> | SYNC pin (input mode)               | 140  | _    | 180   | μS   |

| Control Pulse Width                       | t <sub>PARW</sub> |                                     | 250  | _    | _     | μS   |

| Control Start Time                        | t <sub>PARD</sub> | (*2)                                | _    | _    | 250   | μS   |

| Control End Time                          | t <sub>PARH</sub> |                                     | _    | _    | 250   | μS   |

$\alpha\text{:}$  Crystal activation

Note\*2: Applies to the following pins/control bits:

<u>LINEEN</u>, SLPTHR, NCTHR, <u>GLPADTHR</u>, TPAD6-1, RPAD6-1, <u>RST</u>, ATHR, <u>AATT</u>, AHLD, <u>AHD</u>, <u>AGC</u>, LTHR, <u>LATT</u>, LHLD, <u>LHD</u>, <u>LGC</u> pins, and control bits.

# **Digital Interface Characteristics (2/3)**

$(V_{DD} = 2.7 \text{ to } 3.6 \text{ V}, \text{Ta} = -40 \text{ to } +85^{\circ}\text{C})$

|                           |                   |                                                         | ( - 00 = |      | .,   | ,    |

|---------------------------|-------------------|---------------------------------------------------------|----------|------|------|------|

| Parameter                 | Symbol            | Condition                                               | Min.     | Тур. | Max. | Unit |

| Bit Clock Fraguency       | 4                 | $C_{DL} = 20 \text{ pF}$ (output mode, PCM)             | _        | 64   |      | kHz  |

| Bit Clock Frequency       | f <sub>BCK</sub>  | $C_{DL} = 20 \text{ pF}$ (output mode, linear)          | _        | 128  |      | kHz  |

| Bit Clock Duty Ratio      | D <sub>CK</sub>   | C <sub>DL</sub> = 20 pF (output mode)                   | 40       | 50   | 60   | %    |

| Sync signal frequency     | f <sub>SYNC</sub> | C <sub>DL</sub> = 20 pF (output mode)                   | _        | 8    | ı    | kHz  |

| Sync signal Duty Ratio    | D <sub>SYNC</sub> | C <sub>DL</sub> = 20 pF (output mode)                   | 40       | 50   | 60   | %    |

| Transmit/Receive Sync     | t <sub>BS</sub>   | BCLK to SYNC (output mode)                              | 100      | _    | _    | ns   |

| Signal Setting Time       | t <sub>SB</sub>   | SYNC to BCLK (output mode)                              | 100      | _    | _    | ns   |

| Input Setup Time          | t <sub>DS</sub>   | _                                                       | 100      | _    |      | ns   |

| Input Hold Time           | t <sub>DH</sub>   | _                                                       | 100      | _    |      | ns   |

| Digital Output Delay Time | t <sub>SDX</sub>  | $R_{DL} = 1 \text{ k}\Omega$ , $C_{DL} = 50 \text{ pF}$ | _        | _    | 100  | ns   |

| Digital Output Delay Time | t <sub>XD1</sub>  | $R_{DL} = 1 \text{ k}\Omega, C_{DL} = 50 \text{ pF}$    | _        | _    | 100  | ns   |

| Digital Output Hold Time  | t <sub>XD2</sub>  | $R_{DL} = 1 \text{ k}\Omega$ , $C_{DL} = 50 \text{ pF}$ | _        | _    | 100  | ns   |

| Digital Output Hold Time  | t <sub>XD3</sub>  | $R_{DL} = 1 \text{ k}\Omega$ , $C_{DL} = 50 \text{ pF}$ | _        | _    | 100  | ns   |

# **Digital Input Timing (Normal-sync)**

# **Digital Input Timing (Short-frame-sync)**

# **Digital Output Timing (Normal-sync)**

# **Digital Output Timing (Short-frame-sync)**

# **Digital Interface Characteristics (3/3)**

$(V_{DD} = 2.7 \text{ to } 3.6 \text{ V}, \text{ Ta} = -40 \text{ to } +85^{\circ}\text{C})$

| Parameter                                       | Symbol            | Condition                                            | Min. | Тур. | Max. | Unit |

|-------------------------------------------------|-------------------|------------------------------------------------------|------|------|------|------|

|                                                 | t <sub>M1</sub>   | _                                                    | 20   | _    |      | ns   |

|                                                 | t <sub>M2</sub>   | _                                                    | 20   |      |      | ns   |

|                                                 | t <sub>M3</sub>   | _                                                    | 50   |      |      | ns   |

|                                                 | t <sub>M4</sub>   | _                                                    | 100  |      |      | ns   |

| MOULE CON POST                                  | t <sub>M5</sub>   | _                                                    | 50   |      |      | ns   |

| MCU Interface Digital Input/Output Setting Time | t <sub>M6</sub>   | _                                                    | 50   |      | ı    | ns   |

| input output octaing Time                       | t <sub>M7</sub>   | $R_D = 1 \text{ k}\Omega$ , $C_{DL} = 20 \text{ pF}$ | _    |      | 30   | ns   |

|                                                 | t <sub>M8</sub>   | $R_D = 1 \text{ k}\Omega$ , $C_{DL} = 20 \text{ pF}$ | 0    |      |      | ns   |

|                                                 | t <sub>M9</sub>   | _                                                    | 50   |      | ı    | ns   |

|                                                 | t <sub>M10</sub>  | $R_D = 1 \text{ k}\Omega$ , $C_{DL} = 20 \text{ pF}$ | _    |      | 30   | ns   |

|                                                 | t <sub>M11</sub>  | _                                                    | 100  |      |      | ns   |

| EXCK Clock Frequency                            | f <sub>EXCK</sub> | _                                                    | _    | _    | 10   | MHz  |

# **Microcontroller Interface I/O Timing**

# AC Characteristic (Line side CODEC/Acoustic side CODEC)

$(V_{DD} = 2.7 \text{ to } 3.6 \text{ V}, \text{Ta} = -40 \text{ to } +85^{\circ}\text{C})$

|                                       |                     |                            |                               | , ,             | V DD — 2.1 | 10 0.0  | v, ia – to     | , to 100 O |

|---------------------------------------|---------------------|----------------------------|-------------------------------|-----------------|------------|---------|----------------|------------|

|                                       |                     |                            | Condition                     |                 |            |         |                |            |

| Parameter                             | Symbol              | Freq. (Hz)                 | Level<br>(dBm0)               | Others          | Min.       | Тур.    | Max.           | Unit       |

|                                       | L <sub>oss</sub> T1 | 0 to 60                    | , ,                           |                 | 25         | _       | _              |            |

|                                       | L <sub>oss</sub> T2 | 300 to 3000                |                               |                 | -0.15      | _       | +0.20          |            |

| Transmit Frequency                    | LossT3              | 1020                       |                               | (*0)            |            | Referen | ice            | -ID        |

| Response                              | L <sub>OSS</sub> T4 | 3300                       | 0                             | (*3)            | -0.15      | _       | +0.80          | dB         |

|                                       | LossT5              | 3400                       |                               |                 | 0          | _       | 0.80           |            |

|                                       | LossT6              | 3968.75                    |                               |                 | 13         | _       | _              |            |

|                                       | LossR1              | 0 to 3000                  |                               |                 | -0.15      | _       | +0.20          |            |

| Possivo Fraguenov                     | L <sub>oss</sub> R2 | 1020                       |                               |                 |            | Referen | ice            |            |

| Receive Frequency<br>Response         | LossR3              | 3300                       | 0                             | (*3)            | -0.15      | _       | +0.80          | dB         |

| Response                              | LossR4              | 3400                       |                               |                 | 0          | _       | 0.80           |            |

|                                       | L <sub>OSS</sub> R5 | 3968.75                    |                               |                 | 13         | _       | _              |            |

|                                       | SD T1               |                            | 3                             |                 | 35         | _       | _              |            |

| Transmit Signal to                    | SD T2               |                            | 0                             |                 | 35         | _       | _              |            |

| Distortion Ratio                      | SD T3               | 1020                       | -30                           | (*3, *4)        | 35         | _       | _              | dB         |

| DISTOLLION RALIO                      | SD T4               | ]                          | -40                           |                 | 28         | _       | _              |            |

|                                       | SD T5               |                            | -45                           |                 | 23         | _       | _              |            |

|                                       | SD R1               |                            | 3                             |                 | 35         | _       | _              |            |

| Doggiva Cianal to                     | SD R2               | ]                          | 0                             |                 | 35         | _       | _              |            |

| Receive Signal to Distortion Ratio    | SD R3               | 1020                       | -30                           | (*3, *4)        | 35         | _       | _              | dB         |

| Distortion Ivatio                     | SD R4               |                            | -40                           |                 | 28         | _       | —              |            |

|                                       | SD R5               |                            | -45                           |                 | 23         | _       | _              |            |

|                                       | GT T1               |                            | 3                             |                 | -0.2       | _       | +0.2           |            |

| Transmit Gain                         | GT T2               |                            | -10                           |                 |            | Referen | ice            |            |

| Tracking                              | GT T3               | 1020                       | -40                           | (*3)            | -0.2       | _       | +0.2           | dB         |

| Tracking                              | GT T4               |                            | -50                           |                 | -0.5       | _       | +0.5           |            |

|                                       | GT T5               |                            | -55                           |                 | -1.2       | _       | +1.2           |            |

|                                       | GT R1               |                            | 3                             |                 | -0.2       | _       | +0.2           |            |

| Receive Gain                          | GT R2               |                            | -10                           |                 |            | Referer | ice            |            |

| Tracking                              | GT R3               | 1020                       | -40                           | (*3)            | -0.2       | _       | +0.2           | dB         |

| Tracking                              | GT R4               |                            | -50                           |                 | -0.5       | _       | +0.5           |            |

|                                       | GT R5               |                            | -55                           |                 | -1.2       |         | +1.2           |            |

| Idla Channal Naisa                    | N <sub>IDLT</sub>   | _                          | _                             | (*3, *4)        | _          | _       | -68<br>(-75.7) | dBm0p      |

| Idle Channel Noise                    | N <sub>IDLR</sub>   | _                          | _                             | (*3, *4)        | _          | _       | -72<br>(-79.7) | (dBmp)     |

| Absolute Cignal                       | A <sub>VT</sub>     |                            |                               | A/LGSX (*3)     | 0.285      | 0.32    | 0.359          | Vrms       |

| Absolute Signal<br>Amplitude          | A <sub>VR</sub>     | 1020                       | 0                             | A/LVFRO<br>(*3) | 0.285      | 0.32    | 0.359          | Vrms       |

| Dawer Currely Mate                    | P <sub>SRRT</sub>   | Naiss Fra                  | Noise                         | , ,             | 30         | _       | _              | dB         |

| Power Supply Noise<br>Rejection Ratio | P <sub>SRRR</sub>   | Noise Freq:<br>0 to 50 kHz | Level:<br>50 mV <sub>PP</sub> | (*3)            | 30         | _       | _              | dB         |

|                                       |                     | •                          | •                             |                 | •          | •       |                |            |

Note:

\*3. CODEC input/output gain = 1

\*4. P-message weighted filter used 0.320 Vrms = 0 dBm0 = -7.7 dBm

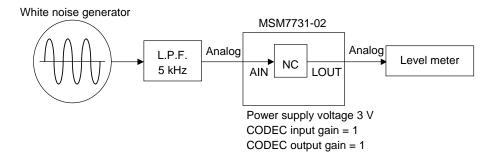

# **Noise Canceler Characteristics**

$(V_{DD} = 2.7 \text{ to } 3.6 \text{ V}, \text{Ta} = -40 \text{ to } +85^{\circ}\text{C})$

| Parameter         | Symbol           | Condition               | Min. | Тур. | Max. | Unit |

|-------------------|------------------|-------------------------|------|------|------|------|

| Noise Attenuation | N <sub>res</sub> | White Noise, voice band | 13   | 17   | _    | dB   |

# **Measurement System Block Diagram**

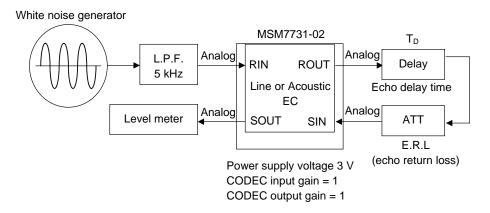

#### **Echo Canceler Characteristics**

$(V_{DD} = 2.7 \text{ to } 3.6 \text{ V}, \text{Ta} = -40 \text{ to } +85^{\circ}\text{C})$

| Parameter                     | Symbol             | Condition                                                               | Min. | Тур. | Max.                 | Unit |

|-------------------------------|--------------------|-------------------------------------------------------------------------|------|------|----------------------|------|

| Echo Attenuation              | E <sub>res</sub>   | Acoustic Line side (when CODEC or 16-bit linear data interface is used) | _    | 35   | _                    | dB   |

|                               |                    | Line side (µ-law PCM used)                                              |      | 30   |                      |      |

|                               | T <sub>acoud</sub> | Single mode                                                             |      | _    | 59                   | mS   |

| Cancelable Echo<br>Delay Time | T <sub>acoud</sub> | Dual mode (acoustic side)                                               | _    | _    | 59-T <sub>line</sub> | mS   |

|                               | T <sub>lined</sub> | Dual mode (line side)                                                   | _    | _    | 27                   | mS   |

# **Measurement System Block Diagram**

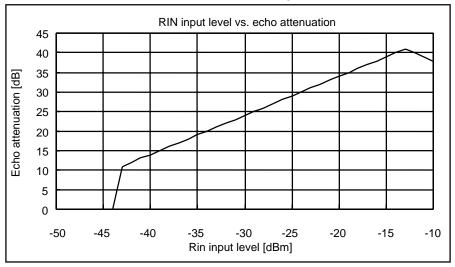

# Rin input level vs. echo attenuation

(Measuring Conditions) Rin signal : 5 kHz band white noise

E.R.L : -6 dBDelay time : 4 ms

ATT, GC : OFF

Noise floor : -60 dBm (P-message filter unused)

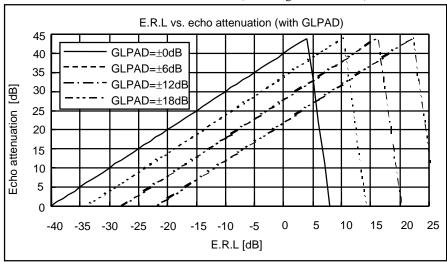

# E.R.L level vs. echo attenuation (with GLPAD)

(Measuring Condition) Rin signal : 5 kHz band white noise

Rin input level : -20 dBm (with GLPAD =  $\pm 0 \text{ dB}$ )

: -26 dBm (with GLPAD =  $\pm 6$  dB) : -32 dBm (with GLPAD =  $\pm 12$  dB) : -38 dBm (with GLPAD =  $\pm 18$  dB)

Delay time : 4 mS

ATT, GC : OFF

Noise floor : -60 dBm (P-message filter unused)

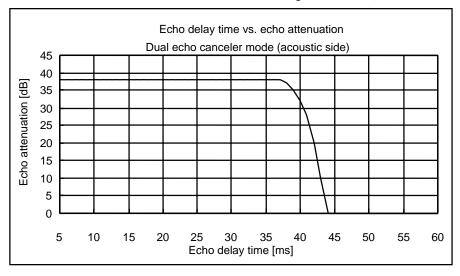

# Echo delay time vs. echo attenuation (Dual echo canceler mode/acoustic side)

(Measuring Condition) Rin signal : 5 kHz band white noise

Rin input level : -16 dBmE.R.L : -6 dB

ATT, GC : OFF

Noise floor : -60 dBm (P-message filter unused)

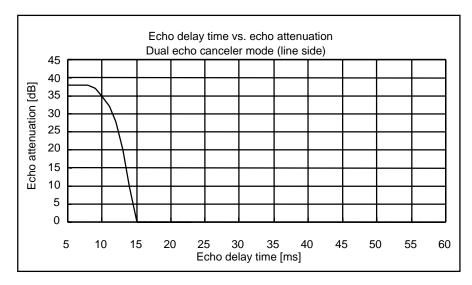

# Echo delay time vs. echo attenuation (Dual echo canceler mode/line side)

(Measuring Condition) Rin signal : 5 kHz band white noise

Rin input level : -16 dBmE.R.L : -6 dB

ATT, GC : OFF

Noise floor : -60 dBm (P-message filter unused)

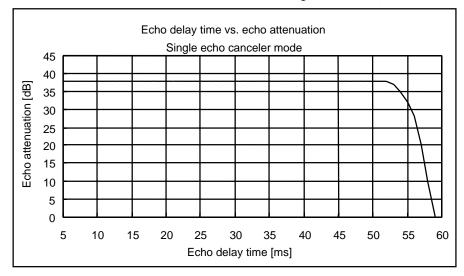

# Echo delay time vs. echo attenuation (Single echo canceler mode)

(Measuring Condition) Rin signal : 5 kHz band white noise

Rin input level : -16 dBm E.R.L : -6 dB

ATT, GC : OFF

Noise floor : -60 dBm (P-message filter unused)

# Slope filter frequency characteristic (with CODEC filter frequency characteristic)

(Measuring Condition) Rin input level : -16 dBm

Noise floor : -60 dBm (P-message filter unused)

# Echo Canceler Characteristics Data 1 (Line Echo, White Noise)

(Measuring Condition) Rin signal : 5 kHz band white noise

Rin input level : -20 dBm E.R.L : 0 dB

ATT, GC : OFF

Noise floor : -60 dBm (P-message filter unused)

Echo attenuation = 40 dB

# Echo Canceler Characteristics Data 2 (Line Echo, Voice)

(Measuring Condition) Rin signal : voice

Rin input level : about -20 dBm

E.R.L : 0 dB

ATT, GC : OFF

Noise floor : -60 dBm (P-message filter unused)

Echo attenuation = 34 dB

# Echo Canceler Characteristics Data 3 (Acoustic echo, Voice)

(Measuring Condition) Rin signal : voice

Rin input level : about -20 dBm

Speaker output level : 80 dB (A) (at 1 m)

Distance from microphone and speaker : 5 cm

GC : OFF

ATT, Noise Canceler : OFF

Noise floor : -60 dBm (P-message filter unused)

Echo attenuation = 34 dB

# Measurement System Block Diagram (Acoustic Echo)

# **FUNCTIONAL DESCRIPTION**

# **Control Registers**

**Table 2 Control Register Map**

| Reg  |    |    | А  | ddres | ss |    |    |          |        |          | Con              | tents  |           |              |             | R/W  |

|------|----|----|----|-------|----|----|----|----------|--------|----------|------------------|--------|-----------|--------------|-------------|------|

| Name | A6 | A5 | A4 | А3    | A2 | A1 | A0 | В7       | В6     | B5       | B4               | В3     | B2        | B1           | В0          | R/VV |

| CR0  | 0  | 0  | 0  | 0     | 0  | 0  | 0  | *PDN/RST | *RST   | *#LINEEN | #CLKEN           | #PCMEN | #PCMEEN   | OPE *#MCUSEL | OPE *#ECSEL | R/W  |

| CR1  | 0  | 0  | 0  | 0     | 0  | 0  | 1  | #DMWR    | _      | _        | _                | _      | *GLPADTHR | *SLPTHR      | *#NCSEL1    | R/W  |

| CR2  | 0  | 0  | 0  | 0     | 0  | 1  | 0  | -        | 1      | RPAD6    | RPAD5            | *RPAD4 | *RPAD3    | *RPAD2       | *RPAD1      | R/W  |

| CR3  | 0  | 0  | 0  | 0     | 0  | 1  | 1  | -        | -      | TPAD6    | TPAD5            | *TPAD4 | *TPAD3    | *TPAD2       | *TPAD1      | R/W  |

| CR4  | 0  | 0  | 0  | 0     | 1  | 0  | 0  | *LTHR    | _      | LHLD     | * <del>LHD</del> | LCLP   | *NCPAD1   | *LATT        | *LGC        | R/W  |

| CR5  | 0  | 0  | 0  | 0     | 1  | 0  | 1  | *ATHR    | _      | AHLD     | *AHD             | ACLP   | *NCPAD2   | *AATT        | *AGC        | R/W  |

| CR6  | 0  | 0  | 0  | 0     | 1  | 1  | 0  | A15      | A14    | A13      | A12              | A11    | A10       | A9           | A8          | R/W  |

| CR7  | 0  | 0  | 0  | 0     | 1  | 1  | 1  | A7       | A6     | A5       | A4               | А3     | A2        | A1           | A0          | R/W  |

| CR8  | 0  | 0  | 0  | 1     | 0  | 0  | 0  | D15      | D14    | D13      | D12              | D11    | D10       | D9           | D8          | R/W  |

| CR9  | 0  | 0  | 0  | 1     | 0  | 0  | 1  | D7       | D6     | D5       | D4               | D3     | D2        | D1           | D0          | R/W  |

| CR10 | 0  | 0  | 0  | 1     | 0  | 1  | 0  | GPADA2   | GPADA1 | LPADA2   | LPADA1           | GPADL2 | GPADL1    | LPADL2       | LPADL1      | R/W  |

| CR11 | 0  | 0  | 0  | 1     | 0  | 1  | 1  | READY    | _      | _        | _                | _      | _         | *#PCMSEL     | #SYPDN      | R/W  |

| CR12 | 0  | 0  | 0  | 1     | 1  | 0  | 0  | _        | -      | -        | -                | _      | *#NCSEL2  | -            | _           | R/W  |

# Note

- \* : Shared control bits with port (pin)

- -: Reserved bits. Do not change the initial value ("0").

- #: Control bit that can be changed only in the initial mode.

#### (1) CR0 (basic operating mode setting)

|                       | В7      | В6  | B5     | B4    | В3    | B2     | B1            | В0           |

|-----------------------|---------|-----|--------|-------|-------|--------|---------------|--------------|

| CR0                   | PDN/RST | RST | LINEEN | CLKEN | PCMEN | PMCEEN | OPE<br>MCUSEL | OPE<br>ECSEL |

| Initial<br>Value (*5) | 0       | 0   | 0      | 0     | 0     | 0      | 0             | 0            |

Note\*5: Initial values are the values set when reset is activated by the PDN/RST pin. (Initial values are also set in the same manner, except for CR0-B7, when reset by the PDN/RST bit of B7.)

B7 Power-down and Reset 0: power-on 1: power-down reset

During power-down reset, this device enters the power-down state. At this time all control register bits, internal variables, and the coefficients for the echo canceler and noise canceler are reset. After power-down reset is released, this device enters the initial mode. This bit is internally ORed with the inverted  $\overline{PDN/RST}$  signal. Refer to the section "RELATIONSHIP BETWEEN PINS AND CONTROL REGISTERS".

B6 Reset control 0: normal operation 1: reset

At reset, the coefficients for the echo canceler and noise canceler and noise canceler are reset. Control register contents preserved. While reset is being processed, there is no sound. Use this bit in cases where the echo path changes (due to line switching during a telephone conversation, etc.), or when resuming telephone communication. Because data is read by this bit in synchronization with the rising edge of the SYNC signal, hold the data in the bit for 250 µs or longer. This bit is internally ORed with the inverted RST signal. Refer to the section "RELATIONSHIP BETWEEN PINS AND CONTROL REGISTERS".

- B5 Line CODEC power-down control 0: normal operation 1: power-down During power-down, the line CODEC is in the power-down state, the line CODEC output pin is at high impedance and line CODEC input pin is internally processed as an idle pattern input. This bit is internally ORed with the LINEEN pin. When the line CODEC is not used, this control results in low consumption of electrical power. This bit can only be set to "0" or "1" during power-down reset and initial mode. Refer to the section "RELATIONSHIP BETWEEN PINS AND CONTROL REGISTERS".

- B4 SYNC, BCLK output control 0: ON 1: OFF

When OFF, the SYNC and BCLK output pins are in the high impedance state. This control is valid when the CLKSEL pin is at a logic "0" and has selected the internal clock mode. When the SYNC and BCLK clocks are not used externally, this control results in low consumption of electrical power. This bit can only be set to "0" or "1" during power-down reset and the initial mode.

- B3 PCMI/O control 0:ON 1: OFF

When OFF, the PCMO output pin is in the high impedance state and the PCMI input pin is internally processed as an idle pattern input. When the line digital interface is not used, this control results in low consumption of electrical power.

This bit can only be set to "0" or "1" during power-down reset and the initial mode.

- B2 PCMEI/O control 0:ON 1: OFF

When OFF, the PCMEO output pin is in the high impedance state and the PCMEI input pin is internally processed as an idle pattern input. When the line digital interface is not used, this control results in low consumption of electrical power.

This bit can only be set to "0" or "1" during power-down reset and the initial mode.

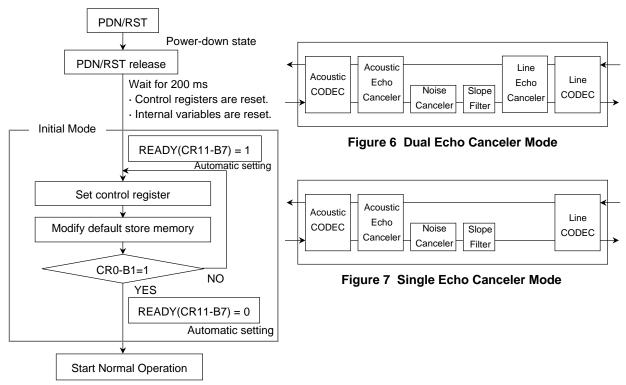

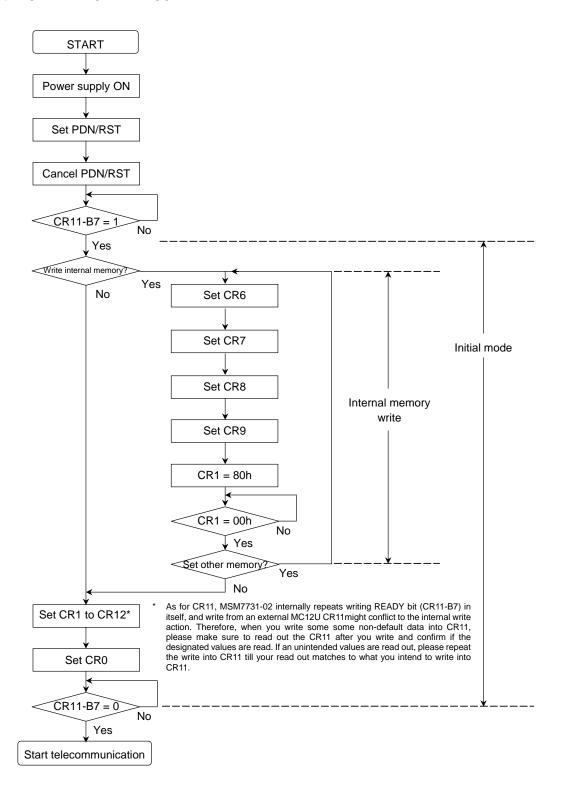

# B1, B0 Operation mode selection

#### (0, 0): Initial mode

Approximately 200 ms after power-down reset is released, the initial mode is entered.

Only in this mode can the contents of the internal default value store memory be modified and CR0-B5 to CR0-B0, CR1-B7, CR1-B0, CR11-B1, CR11-B0, and CR12-B2 be set. In this mode, digital signal output pins are at high impedance, digital communication input pins are internally processed as idle pattern inputs, and neither the echo canceler nor the noise canceler operates. This mode is skipped when the MCUSEL pin is a logic "1". This mode is released by setting the modes shown below. Refer to the flow chart of Figure 5.

#### (1, 0): Dual echo canceler mode

The acoustic echo canceler, line echo canceler and other functions can be operated by control from the control registers. Refer to Figure 6.

The initial setting for cancelable echo delay time is as follows:

Acoustic delay time = 44 ms

Line delay time = 15 ms

#### (1, 1): Single echo canceler mode

The acoustic echo canceler and other functions can be operated by control from the control registers. Control of the line echo canceler is unnecessary in this mode .Refer to Figure 7.

The initial setting for cancelable echo delay time is as follows:

Acoustic delay time = 59 ms

(Other): Reserved bit (cannot be used)

Note: The MCUSEL pin is internally ORed with B1, and the ECSEL pin is internally ORed with B0. To return to the initial mode after it has been released, activate power-down reset.

Figure 5 Initial Mode Flowchart

#### (2) CR1

|               | B7   | В6 | B5 | B4 | В3 | B2       | B1     | В0     |

|---------------|------|----|----|----|----|----------|--------|--------|

| CR1           | DMWR | _  | _  | _  | _  | GLPADTHR | SLPTHR | NCSEL1 |

| Initial Value | 0    | 0  | 0  | 0  | 0  | 0        | 0      | 0      |

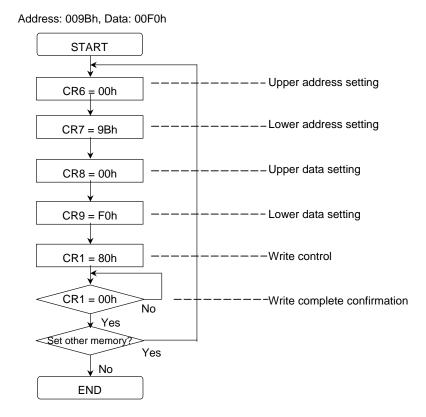

B7 Internal data memory write control 0: write inhibited 1: write

In internal data memory, the data set in CR8 (D15 to D8) and CR9 (D7 to D0) is written to the memory address set in CR6 (A15 to A8) and CR7 (A7 to A0).

Writing is possible only during the initial mode.

For further details, refer to the internal data memory access method.

B6, B5, B4, B3 Reserved bits. Modification of initial values is inhibited.

B2 Echo Canceler I/O PAD control 0: "through mode" 1: normal mode

This bit controls the attenuators (LPADL/A) provided in the SinL/A inputs and the amplifiers (GPADL/A) provided in the SoutL/A outputs of the echo canceler. Levels are set by the CR10 register, and  $\pm 18, \pm 12, \pm 6$  and 0 dB can be set. The default value is  $\pm 12$  dB. Use this bit when the echo return loss (value of returned echo) is amplified. If the pin setting is changed, the coefficient reset must be activated by either the  $\overline{RST}$  pin or the RST bit (CR0-B6). Because data is read by this bit in synchronization with the rising edge of the SYNC signal, hold the data in the bit for 250  $\mu$ s or longer. This bit is internally ORed with the  $\overline{GLPADTHR}$  pin.

- B1 Slope filter control 0: normal mode (slope filter operation) 1: "through mode"

This bit controls operation of the transmit slope filter. In the "through mode", the filter is halted and data is output directly. The slope filter decreases noises of low frequencies and improves the speech quality. Refer to the frequency characteristics of slope filter. Because data is read by this bit in synchronization with the rising edge of the SYNC signal, hold the data in the bit for 250 μs or longer. This bit is internally ORed with the SLPTHR pin.

- Noise attenuation selection control 0: normal mode 1: "through mode"

This bit selects the noise attenuation of the noise canceler. In the "through mode", the noise canceler is halted and data is output directly. In the "normal mode" the noise canceler operates normally. Since the noise attenuation in the normal mode is selected after the initial mode has been released, the change of the noise attenuation during normal operation is invalid. If the noise attenuation is changed, reset must be activated by the RDN/RST pin or the PDN/RST bit (CR0-B7). Changing to the through mode during normal operation and returning to the normal mode are possible. This bit is internally ORed with NCSEL1 pin. (Refer to the NCSEL2 pin of CR12-B2.)

Note: Since there is a trade-off between noise attenuation and sound quality after canceling the noise, select the noise attenuation appropriate to the sound quality.

| NCSEL2 | NCSEL1 | NC Mode      | Attenuation (dB) | Quality   |

|--------|--------|--------------|------------------|-----------|

| 0      | 0      | Normal Mode  | 17               | Better    |

| 1      | 1      | Normal Mode  | 13.5             | <b>\$</b> |

| 1      | 0      | Normal Mode  | 8                | Best      |

| 0      | 1      | Through Mode | _                | _         |

# (3) CR2 (Receive side level control)

|               | B7 | B6 | B5    | B4    | В3    | B2    | B1    | В0    |

|---------------|----|----|-------|-------|-------|-------|-------|-------|

| CR2           | _  | _  | RPAD6 | RPAD5 | RPAD4 | RPAD3 | RPAD2 | RPAD1 |

| Initial Value | 0  | 0  | 0     | 0     | 0     | 0     | 0     | 0     |

B7, B6 Reserved bit. Modification of initial values is inhibited.

# B5, B4, B3, B2, B1,B0 Receive side level setting (RPAD)

These bits adjust the receive signal gain and set the mute level. Notice that only the mute level setting differs from pin control. Because data is read by these bits in synchronization with the rising edge of the SYNC signal, hold the data in these bits for 250 µs or longer.

When using this register, set the TPAD, 3, 2, 1 pins to a logic "0".

(0, 0, 1, 0, 1, 0): 30 dB (0, 0, 1, 0, 0, 1): 27 dB (0, 0, 1, 0, 0, 0): 24 dB (0, 0, 0, 1, 1, 1): 21 dB (0, 0, 0, 1, 1, 0): 18 dB (0, 0, 0, 1, 0, 1): 15 dB (0, 0, 0, 1, 0, 0): 12 dB (0, 0, 0, 0, 1, 1): 9 dB (0, 0, 0, 0, 1, 0): 6 dB (0, 0, 0, 0, 0, 1): 3 dB (0, 0, 0, 0, 0, 0): 0 dB (1, 1, 1, 1, 1, 1): -3 dB(1, 1, 1, 1, 1, 0): -6 dB(1, 1, 1, 1, 0, 1): -9 dB(1, 1, 1, 1, 0, 0): -12 dB(1, 1, 1, 0, 1, 1): -15 dB(1, 1, 1, 0, 1, 0): -18 dB(1, 1, 1, 0, 0, 1): -21 dB (1, 1, 1, 0, 0, 0): -24 dB(1, 1, 0, 1, 1, 1): -27 dB(1, 1, 0, 1, 1, 0):  $-30 \, dB$ (1, 1, 0, 1, 0, 1): -33 dB(1, 1, 0, 1, 0, 0):  $-36 \, dB$ (1, 1, 0, 0, 1, 1):  $-39 \, dB$ (1, 1, 0, 0, 1, 0): -42 dB(1, 1, 0, 0, 0, 1): -45 dB(1, 1, 0, 0, 0, 0): -48 dB(1, 0, 1, 1, 1, 1): -51 dB(1, 0, 1, 1, 1, 0): -54 dB(1, 0, 1, 1, 0, 1):  $-57 \, dB$ (1, 0, 1, 1, 0, 0):  $-60 \, dB$ (1, 0, 1, 0, 1, 1): MUTE

# (4) CR3 (Transmit Gain Adjustment)

|               | В7 | B6 | B5    | B4    | В3    | B2    | B1    | В0    |

|---------------|----|----|-------|-------|-------|-------|-------|-------|

| CR3           | _  | _  | TPAD6 | TPAD5 | TPAD4 | TPAD3 | TPAD2 | TPAD1 |

| Initial Value | 0  | 0  | 0     | 0     | 0     | 0     | 0     | 0     |

B7, B6 Reserved bits. Modification of initial values is inhibited.

# B5, B4, B3, B2, B1, B0 Transmit side level setting (TPAD)

These bits adjust the transmit signal gain and set the mute level. Notice that only the mute level setting differs from pin control. Because data is read by these bits in synchronization with the rising edge of the SYNC signal, hold the data in these bits for 250 µs or longer.

When using this register, set the TPAD4, 3, 2, 1 pins to a logic "0".

(0, 0, 1, 0, 1, 0): 30 dB (0, 0, 1, 0, 0, 1): 27 dB (0, 0, 1, 0, 0, 0): 24 dB (0, 0, 0, 1, 1, 1): 21 dB (0, 0, 0, 1, 1, 0): 18 dB (0, 0, 0, 1, 0, 1): 15 dB (0, 0, 0, 1, 0, 0): 12 dB (0, 0, 0, 0, 1, 1): 9 dB (0, 0, 0, 0, 1, 0): 6 dB (0, 0, 0, 0, 0, 1): 3 dB (0, 0, 0, 0, 0, 0): 0 dB(1, 1, 1, 1, 1, 1): -3 dB(1, 1, 1, 1, 1, 0):  $-6 \, dB$ (1, 1, 1, 1, 0, 1): -9 dB(1, 1, 1, 1, 0, 0): -12 dB(1, 1, 1, 0, 1, 1): -15 dB(1, 1, 1, 0, 1, 0): -18 dB(1, 1, 1, 0, 0, 1): -21 dB(1, 1, 1, 0, 0, 0): -24 dB(1, 1, 0, 1, 1, 1): -27 dB(1, 1, 0, 1, 1, 0):  $-30 \, dB$ (1, 1, 0, 1, 0, 1): -33 dB(1, 1, 0, 1, 0, 0):  $-36 \, dB$ (1, 1, 0, 0, 1, 1): -39 dB(1, 1, 0, 0, 1, 0): -42 dB(1, 1, 0, 0, 0, 1): -45 dB(1, 1, 0, 0, 0, 0): -48 dB(1, 0, 1, 1, 1, 1): -51 dB(1, 0, 1, 1, 1, 0): -54 dB(1, 0, 1, 1, 0, 1):  $-57 \, dB$ (1, 0, 1, 1, 0, 0):  $-60 \, dB$ (1, 0, 1, 0, 1, 1): MUTE

#### (5) CR4 (Line echo canceler setting)

|               | B7   | B6 | B5   | B4  | В3   | B2     | B1   | В0  |

|---------------|------|----|------|-----|------|--------|------|-----|

| CR4           | LTHR | _  | LHLD | LHD | LCLP | NCPAD1 | LATT | LGC |

| Initial Value | 0    | 0  | 0    | 0   | 0    | 0      | 0    | 0   |

B7 "Through mode" control 1: "through mode" 0: normal mode (echo canceler operation) This is the "through mode" control bit for the line echo canceler. In the "through mode", RinL and SinL data is output directly to RoutL and SoutL respectively while each echo coefficient is maintained . In the through mode, the functions of  $\overline{LHD}$ , LHLD,  $\overline{LATT}$  and  $\overline{LGC}$  are invalid. Because data is read by this bit in synchronization with the rising edge of the SYNC signal, hold the data in the bit for 250  $\mu s$  or longer.

This bit is internally ORed with the LTHR pin.

- B6 Reserved bit. Modification of initial values is inhibited.

- B5 Coefficient update control 1: fixed coefficients0: updated coefficients

This bit selects whether the adaptive FIR filter (AFR) coefficients for the line echo canceler will be updated. This unction is valid when the ATHR pin is in the normal mode.

Because data is read into this bit by synchronization with the rising edge of the SYNC signal, hold the data at the bit for 250 μs or longer.

- B4 Howling detector control 1: OFF 0: ON

This bit controls the function to detect and cancel the howling that occurs in an acoustic system such as a handsfree communication system. This function is valid when the LTHR pin is in the normal mode. Because this bit is read in synchronization with the rising edge of the SYNC signal, hold the data in the

This bit is internally ORed with the  $\overline{LHD}$  pin.

bit for 250 µs or longer.

bit for 250 µs or longer.

- B3 Center clip control 1: ON 0: OFF

When the SoutL output of the line echo canceler is -57 dBm0 or less, the center clip function forcibly sets it to the minimum positive value. This function is valid when the LTHR pin is in the normal mode.

Because this bit is read in synchronization with the rising edge of the SYNC signal, hold the data in the

- B2 NCPAD control

This bit adjusts the noise canceler I/O gain. The gain adjustment is valid for tone control after canceling the noise. The bigger the input level of the noise canceler is, the better the sound quality is. Because this bit is read in synchronization with the rising edge of the SYNC signal, hold the data in the bit for 250  $\mu s$  or longer. This bit is internally ORed with the NCPAD1 pin. (Refer to the NCPAD2 pin of CR5-B2.)

| NCPAD2 | NCPAD1 | GPADNC (dB) | LPADNC (dB) |

|--------|--------|-------------|-------------|

| 0      | 0      | 0           | 0           |

| 0      | 1      | 6           | -6          |

| 1      | 0      | 12          | -12         |

| 1      | 1      | 18          | -18         |

B1 Attenuator control 1: ATT OFF 0: ATT ON

This bit turns ON or OFF the ATT function to prevent howling by means of attenuators (ATTsL, ATTrL) provided in the RinL input and SoutL output of the line echo canceler.

If input is only to RinL, the ATT for SoutL (ATTsL) is activated. If input is only to SinL, or if there is input to both SinL and RinL, the ATT for RinL input (ATTrL) is activated. The ATT value of each attenuator is approximately 6 dB. This function is valid when the LTHR pin is in the normal mode. Because this bit is read in synchronization with the rising edge of the SYNC signal, hold the data in the bit for  $250~\mu s$  or longer.

This bit is internally ORed with the LATT pin.

B0 Gain controller 1: GC OFF 0: GC ON

This bit turns ON or OFF the gain control function to control the RinL input level and prevent howling by means of a gain controller (GainL) provided in the RinL input of the line echo canceler.

The gain controller adjusts the RIN input level when it is -10 dBm0 or above, and it has the control range of 0 to -8.5 dB. This function is valid when the LTHR pin is in the normal mode. Because this bit is read in synchronization with the rising edge of the SYNC signal, hold the data in the bit for  $250 \,\mu s$  or longer.

This bit is internally ORed with the  $\overline{LGC}$  pin.

#### (6) CR5 (Acoustic echo canceler setting)

|               | B7   | В6 | B5   | B4  | В3   | B2     | B1   | В0  |

|---------------|------|----|------|-----|------|--------|------|-----|

| CR5           | ATHR | _  | AHLD | AHD | ACLP | NCPAD2 | AATT | AGC |

| Initial Value | 0    | 0  | 0    | 0   | 0    | 0      | 0    | 0   |

B7 "Through mode" control 1: "through mode" 0: normal mode (echo canceler operation)

This is the "Through mode" control bit for the acoustic echo canceler. In the "through mode", RinA and SinA data is output directly to RoutA and SoutA respectively while each echo coefficient is maintained.

In the through mode, the functions of AHD, AHLD, AATT and AGC are invalid. Because this bit is read in synchronization with the rising edge of the SYNC signal, hold the data in the bit for 250 μs or longer.

This bit is internally ORed with the ATHR pin.

- B6 Reserved bit. Modification of initial values is inhibited.

- B5 Coefficient update control 1: fixed coefficients0: updated coefficients

This bit selects whether the adaptive FIR filter (AFR) coefficients for the acoustic echo canceler will be updated. This function is valid when the ATHR pin is in the normal mode.

Because this bit is read in synchronization with the rising edge of the SYNC signal, hold the data in the bit for 250 µs or longer.

- B4 Howling detector control 1: OFF 0: ON

This bit controls the function to detect and cancel the howling that occurs in an acoustic system such as a handsfree communication system. This function is valid when the ATHR pin is in the normal mode. Because this bit is read in synchronization with the rising edge of the SYNC signal, hold the data in the bit for  $250 \, \mu s$  or longer.

This bit is internally ORed with the  $\overline{AHD}$  pin.

B3 Center clip control 1: ON 0: OFF

When the SoutA output of the acoustic echo canceler is -57 dBm0 or less, the center clip function forcibly sets it to the minimum positive value. This function is valid when the ATHR pin is in the normal mode.

Because this bit is read in synchronization with the rising edge of the SYNC signal, hold the data in the bit for  $250 \,\mu s$  or longer.

B2 NCPAD control

This bit adjusts the noise canceler I/O gain. The gain adjustment is valid for tone control after canceling the noise. The bigger the input level of the noise canceler is, the better the sound quality is. Because this bit is read in synchronization with the rising edge of the SYNC signal, hold the data in the bit for 250  $\mu$ s or longer. This bit is internally ORed with the NCPAD2 pin. (Refer to the NCPAD1 pin of CR4-B2.)

| NCPAD2 | NCPAD1 | GPADNC (dB) | LPADNC (dB) |

|--------|--------|-------------|-------------|

| 0      | 0      | 0           | 0           |

| 0      | 1      | 6           | -6          |

| 1      | 0      | 12          | -12         |

| 1      | 1      | 18          | -18         |

B1 Attenuator control 1: ATT 12 dB 0: ATT 6 dB

This bit selects the attenuation of the ATT function to prevent howling by means of attenuators (ATTsA, ATTrA) provided in the RinA input and SoutA output of the acoustic echo canceler.

If input is only to RinA, the ATT for SoutA (ATTsA) is activated. If input is only to SinA, or if there is input to both SinA and RinA, the ATT for RinA input (ATTrA) is activated. The ATT value of each attenuator is approximately 6 dB or 12 dB. This function is valid when the ATHR pin is in the normal mode. Because this bit is read in synchronization with the rising edge of the SYNC signal, hold the data in the bit for  $250~\mu s$  or longer.

This bit is internally ORed with the  $\overline{AATT}$  pin.

B0 Gain controller control 1: GC OFF 0: GC ON

This bit turns ON or OFF the gain control function to control the RinA input level and prevent howling by means of a gain controller (GainA) provided in the RinA input of the acoustic echo canceler.