# AKM

## - Preliminary - AK4561 16bit CODEC with built-in ALC and MIC/HP-Amp

## GENERAL DESCRIPTION

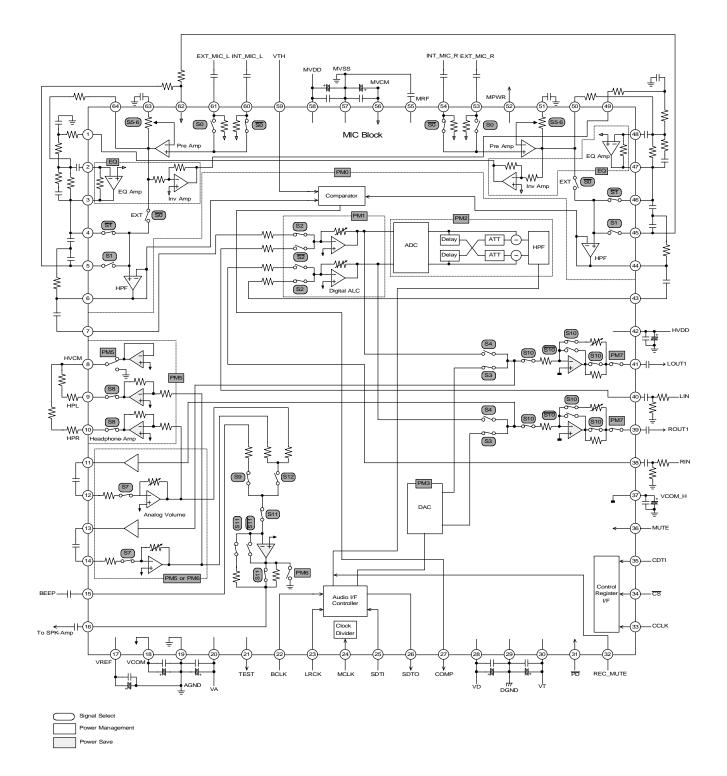

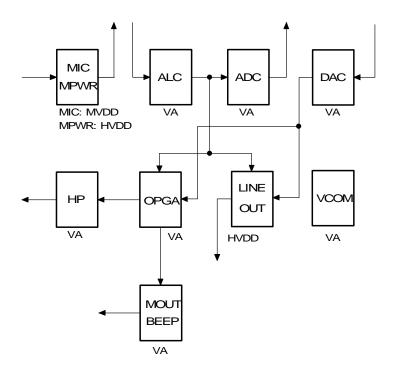

AK4561 is a 16bit stereo CODEC with a built-in Microphone-Amp, Headphone-Amp. Input circuits include Microphone/LINE inputs selector, power supply for microphone, Pre-Amp, HPF-Amp, EQ-Amp and ALC (Automatic Level Control) circuit, and output circuits include LINEOUT buffer, Analog Volume and Headphone-Amp. As Multi-Power-Supply-System can be set a suitable power supply voltage in each block, the AK4561 is compatible with high performance and low power dissipation. The package is a 64pin TQFP, therefore, a new system can be a smaller board area than a current system is composed of 2 or 3 chips.

## FEATURE

- 1. Resolution: 16bits

- 2. Recording Function

- 3-Input Selector (Internal MIC, External MIC and LINE)

- MIC-Amp

- Pre-Amp, EQ-Amp, HPF-Amp for wind-noise

- Digital ALC (Automatic Level Control) circuit

- FADEIN/FADEOUT

- Digital Delay circuit

- Digital HPF for offset cancellation (fc=3.7Hz@fs=48kHz)

- 3. Playback Function

- Digital De-emphasis Filter (tc=50/15µs, fs = 32kHz, 44.1kHz and 48kHz)

- LINEOUT Buffer: +2dBV

- Analog Volume

- 0dB  $\sim$  -50dB, Mute

- Headphone-Amp

- Output Level: -5.5dBV@VA=2.8V, R∟=55Ω

- Monaural Output Buffer

- BEEP Signal Input

- 4. Analog Through Mode

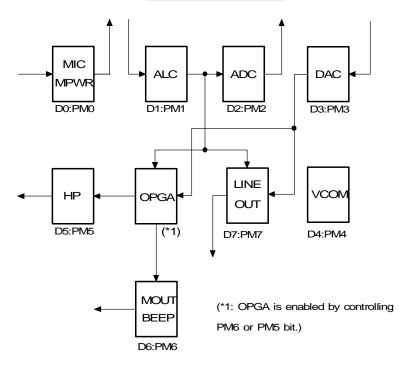

- 5. Power Management

- 6. ADC Characteristics (LINEIN  $\rightarrow$  ALC  $\rightarrow$  ADC)

- S/(N+D): 78dB, DR=S/N: 86dB

- 7. DAC Characteristics (DAC  $\rightarrow$  LINEOUT)

- S/(N+D): 76dB, DR=S/N: 88dB

- 8. Master Clock: 256fs/384fs

- 9. Sampling Rate: 8kHz ~50kHz

- 10. Audio Data Interface Format: MSB-First, 2's compliment (AK4550 Compatible) • ADC: 16bit MSB justified, DAC: 16bit LSB justified

- 11. Ta = -20 ~ 85°C

- 12. Power Supply

- CODEC, Analog Volume, Headphone-Amp: 2.6 ~ 3.3V (typ. 2.8V)

- LINEOUT: 3.8 ~ 5.5V (typ. 4.5V)

- MIC-Amp: 2.6 ~ 5.0V (typ. 2.8V)

- Digital I/F: 1.8 ~ 3.3V (typ. 2.8V)

- 13. Power Supply Current

- All Circuit Power On: 37mA

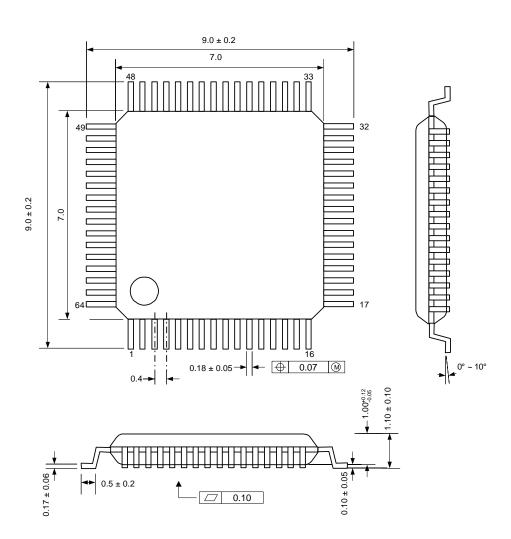

- 14. Package: 64pin TQFP, 0.4mm Pitch

ASAHI KASEI

[AK4561]

Figure 1. AK4561 Block Diagram

## Ordering Guide

| AK4561VQ |  |

|----------|--|

| AKD4561  |  |

-20 ~ +85 °C Evaluation Board 64pin TQFP (0.4mm pitch)

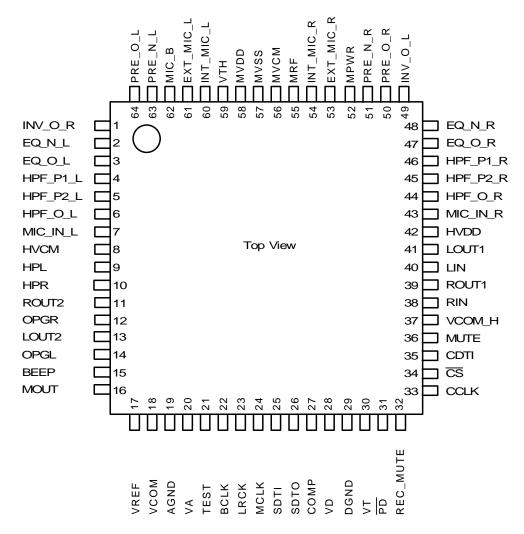

#### Pin layout

|    | PIN/FUNCTION |     |                                                              |  |  |  |  |  |  |

|----|--------------|-----|--------------------------------------------------------------|--|--|--|--|--|--|

| No | Pin Name     | I/O | Function                                                     |  |  |  |  |  |  |

|    | er Supply    | 1/0 | Function                                                     |  |  |  |  |  |  |

| 17 | VREF         | 0   | ADC, DAC Reference Level, 0.5 x VA                           |  |  |  |  |  |  |

| 18 | VCOM         | 0   | Common Voltage Output Pin, 0.5 x VA                          |  |  |  |  |  |  |

| 19 | AGND         | -   | Analog Ground Pin                                            |  |  |  |  |  |  |

| 20 | VA           | -   | Analog Power Supply Pin, +2.8V                               |  |  |  |  |  |  |

| 28 | VD           | -   | Digital Power Supply Pin, +2.8V                              |  |  |  |  |  |  |

| 29 | DGND         | _   | Digital Ground Pin                                           |  |  |  |  |  |  |

| 30 | VT           | -   | Digital I/F Power Supply Pin, +2.8V                          |  |  |  |  |  |  |

| 37 | VCOM_H       | 0   | LINEOUT Common Voltage Output Pin, 0.5 x HVDD                |  |  |  |  |  |  |

| 42 | HVDD         | -   | LINEOUT Power Supply Pin, +4.5V                              |  |  |  |  |  |  |

| 52 | MPWR         | 0   | MIC Power Supply Pin, +2.0V, Idd=3mA(max)                    |  |  |  |  |  |  |

|    | MRF          | 0   | MIC Power Supply Fin, 12.01, Indestin (Index)                |  |  |  |  |  |  |

| 56 | MVCM         | 0   | MIC Block Common Voltage Output Pin, 0.5 X MVDD              |  |  |  |  |  |  |

|    | MVSS         | -   | MIC Block Ground Pin                                         |  |  |  |  |  |  |

| 58 | MVDD         | _   | MIC Block Power Supply Pin                                   |  |  |  |  |  |  |

|    | ation Clock  |     |                                                              |  |  |  |  |  |  |

|    | BCLK         | Ι   | Audio Serial Data Clock Pin                                  |  |  |  |  |  |  |

|    | LRCK         | I   | Input/Output Channel Clock Pin                               |  |  |  |  |  |  |

|    | MCLK         | I   | Master Clock Input Pin                                       |  |  |  |  |  |  |

| 25 | SDTI         | I   | Audio Serial Data Input Pin                                  |  |  |  |  |  |  |

|    | SDTO         | 0   | Audio Serial Data Input I II<br>Audio Serial Data Output Pin |  |  |  |  |  |  |

|    | Block        | 0   |                                                              |  |  |  |  |  |  |

| 1  | INV_O_R      | 0   | Rch Inverter-Amp Output Pin                                  |  |  |  |  |  |  |

|    | EQ_N_L       | I   | Lch EQ-Amp Negative Input Pin                                |  |  |  |  |  |  |

| 3  | EQ_O_L       | 0   | Lch EQ-Amp Output Pin                                        |  |  |  |  |  |  |

| 4  | HPF_P1_L     | I   | Lch HPF-Amp Positive #1 Input Pin                            |  |  |  |  |  |  |

| 5  | HPF_P2_L     | I   | Lch HPF-Amp Positive #2 Input Pin                            |  |  |  |  |  |  |

| 6  | HPF_O_L      | 0   | Lch HPF Output Pin                                           |  |  |  |  |  |  |

| 44 | HPF_O_R      | 0   | Rch HPF Output Pin                                           |  |  |  |  |  |  |

| 45 | HPF_P2_L     | I   | Lch HPF-Amp Positive #2 Input Pin                            |  |  |  |  |  |  |

| 46 | HPF_P1_L     | I   | Lch HPF-Amp Positive #1 Input Pin                            |  |  |  |  |  |  |

| 47 | EQ_O_R       | 0   | Rch EQ-Amp Output Pin                                        |  |  |  |  |  |  |

| 48 | EQ_N_R       | I   | Rch EQ-Amp Negative Input Pin                                |  |  |  |  |  |  |

| 49 | INV_O_L      | 0   | Lch Inverter-Amp Output Pin                                  |  |  |  |  |  |  |

| 50 | PRE_O_R      | 0   | Rch Pre-Amp Output Pin                                       |  |  |  |  |  |  |

|    | PRE_N_R      | I   | Rch Pre-Amp Negative Input Pin                               |  |  |  |  |  |  |

| 53 | EXT_MIC_R    | I   | External MIC Rch Input Pin                                   |  |  |  |  |  |  |

| 54 | INT_MIC_R    | I   | Internal MIC Rch Input Pin                                   |  |  |  |  |  |  |

| 60 | INT_MIC_L    | I   | Internal MIC Lch Input Pin                                   |  |  |  |  |  |  |

| 61 | EXT_MIC_L    | I   | External MIC Lch Input Pin                                   |  |  |  |  |  |  |

| 62 | MIC_B        | I   | MIC-Amp Bias Pin                                             |  |  |  |  |  |  |

| 63 | PRE_N_L      | I   | Lch Pre-Amp Negative Input Pin                               |  |  |  |  |  |  |

| 64 | PRE_O_L      | 0   | Lch Pre-Amp Output Pin                                       |  |  |  |  |  |  |

| υт | LT.UL_0_L    | 0   |                                                              |  |  |  |  |  |  |

Note: All input pins should not be left floating.

| Cont | rol Data Interface |   |                                                                        |

|------|--------------------|---|------------------------------------------------------------------------|

| 33   | CCLK               | Ι | Control Clock Input Pin                                                |

| 34   | CS                 | Ι | Chip Select Pin                                                        |

| 35   | CDTI               | Ι | Control Data Input Pin                                                 |

| ALC  | Block              |   |                                                                        |

| 7    | MIC_IN_L           | Ι | Lch MIC Input Pin                                                      |

| 38   | RIN                | Ι | Rch Line Input Pin                                                     |

| 40   | LIN                | Ι | Lch Line Input Pin                                                     |

| 43   | MIC_IN_R           | Ι | Rch MIC Input Pin                                                      |

| DAC  |                    |   |                                                                        |

| 11   | ROUT2              | 0 | Rch #2 Line Output Pin, -5.5dBV@VA=2.8V                                |

| 13   | LOUT2              | 0 | Lch #2 Line Output Pin, -5.5dBV@VA=2.8V                                |

| 39   | ROUT1              | 0 | Rch #1 Line Output Pin, +2dBV@VA=2.8V, VOL=+7.5dB                      |

| 41   | LOUT1              | 0 | Lch #1 Line Output Pin, +2dBV@VA=2.8V, VOL=+7.5dB                      |

| Anal | og Volume          |   |                                                                        |

| 12   | OPGR               | Ι | Rch Analog Volume Input Pin                                            |

| 14   | OPGL               | Ι | Lch Analog Volume Input Pin                                            |

| Head | phone Amp          |   |                                                                        |

| 8    | HVCM               | 0 | Headphone-Amp Common Voltage Output Pin                                |

| 9    | HPL                | 0 | Lch Headphone-Amp Output Pin                                           |

| 10   | HPR                | 0 | Rch Headphone-Amp Output Pin                                           |

|      | r Amp              |   |                                                                        |

|      | MOUT               | 0 | Mixing Analog Output Pin                                               |

| Othe | r Functions        |   |                                                                        |

| 15   | BEEP               | Ι | Beep Signal Input Pin                                                  |

| 21   | TEST               | 0 | Test pin                                                               |

| 27   | COMP               | 0 | Comparator Output Pin                                                  |

| 31   | PD                 | Ι | Power Down & Reset Pin, "L": Power-down & Reset, "H": Normal operation |

| 32   | REC_MUTE           | Ι | Rec Mute Pin, "L": Normal Operation, "H": ADC Output Data Mute         |

| 36   | MUTE               | Ι | Mute Pin, "L": Normal Operation, "H": Mute                             |

| 59   | VTH                | Ι | Comparator Threshold Voltage Input Pin                                 |

Note: All input pins should not be left floating.

|                     | ABSOLUTE I             | MAXIMUM RA    | ΓING |         |       |

|---------------------|------------------------|---------------|------|---------|-------|

| (AGND, DGND, N      | (VSS=0V;Note 1)        |               |      |         |       |

| Parameter           |                        | Symbol        | min  | max     | Units |

| Power Supplies      | Analog 1 (VA pin)      | VA            | -0.3 | 6.0     | V     |

|                     | Analog 2 (HVDD pin)    | HVDD          | -0.3 | 6.0     | V     |

|                     | MIC (MVDD pin)         | MIC           | -0.3 | 6.0     | V     |

|                     | Digital 1 (VD pin)     | VD            | -0.3 | 6.0     | V     |

|                     | Digital 2 (VT pin)     | VT            | -0.3 | 6.0     | V     |

|                     | DGND – AGND   (Note 2) | $\Delta GND1$ | -    | 0.3     | V     |

|                     | MVDD – AGND   (Note 2) | $\Delta GND2$ | -    | 0.3     | V     |

| Input Current (Any  | pines except supplies) | IIN           | -    | ±10     | mA    |

| Analog Input Volta  | age (Note 3)           | VINA1         | -0.3 | VA+0.3  | V     |

|                     | (Note 4)               | VINA2         | -0.3 | MIC+0.3 | V     |

| Digital Input Volta | ge (Note 5)            | VIND1         | -0.3 | VD+0.3  | V     |

| - •                 | (Note 6)               | VIND2         | -0.3 | VT+0.3  | V     |

| Ambient Temperat    | ure                    | Та            | -20  | 85      | °C    |

| Storage Temperatu   | re                     | Tstg          | -65  | 150     | °C    |

Note 1. All voltages with respect to ground.

Note 2. "DGND and AGND" and "MVSS and AGND" are the same voltage.

Note 3. Analog input pins except EXT\_MIC\_L, EXT\_MIC\_R, INT\_MIC\_L, INT\_MIC\_R, EQ\_N1\_L, EQ\_N1\_R, EQ\_N2\_L, EQ\_N2\_R, HPF\_P\_L, HPF\_P\_R and MIC\_B.

Note 4. EXT\_MIC\_L, EXT\_MIC\_R, INT\_MIC\_L, INT\_MIC\_R, EQ\_N1\_L, EQ\_N1\_R, EQ\_N2\_L, EQ\_N2\_R, HPF\_P\_L, HPF\_P\_R and MIC\_B pins

Note 5. MCLK, LRCK, BCLK and SDTI pins

Note 6. CS, CCLK, CDTI, PD, REC\_MUTE and MUTE pins

WARNING: Operation at or beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

## RECOMMEND OPERATING CONDITIONS

| Parameter |                     | Symbol | min | typ | max | Units |

|-----------|---------------------|--------|-----|-----|-----|-------|

| Power     | Analog 1 (VA pin)   | VA     | 2.6 | 2.8 | 3.3 | V     |

| Supplies  | Analog 2 (HVDD pin) | HVDD   | 3.8 | 4.5 | 5.5 | V     |

|           | MIC (MIC pin)       | MIC    | 2.6 | 2.8 | 5.0 | V     |

|           | Digital 1 (VD pin)  | VD     | 2.6 | 2.8 | 3.3 | V     |

|           | Digital 2 (VT pin)  | VT     | 1.8 | 2.8 | 3.3 | V     |

Note 1. All voltages with respect to ground.

\* AKM assumes no responsibility for the usage beyond the conditions in this datasheet.

#### ANALOG CHARACTERISTICS

(Ta=25°C; VA=VD=MVDD=VT=2.8V, HVDD=4.5V; AGND=DGND=MVSS=0V; fs=48kHz; Input Ergquency =1kHz: Measurement width=20Hz ~ 20kHz; unless otherwise specified)

| Input Frequency =1kHz; Measurement width=20Hz ~ 20kHz; unles<br>Parameter | min      | <u> </u> | mov  | Units |

|---------------------------------------------------------------------------|----------|----------|------|-------|

|                                                                           | 11111    | typ      | max  | Units |

| Pre-Amp Characteristics:                                                  |          |          |      |       |

| Input Resistance: Positive Input Pin (Note 7)                             |          | 100      |      | kΩ    |

| Negative Input Pin (Note 8)                                               |          | 1.5      |      | kΩ    |

| Maximum Output Voltage (Note 9)                                           |          |          | -3.2 | dBV   |

| Output Voltage (Input Voltage = -26dBV, Gain = +16dB) (Note 10)           |          | -10      |      | dBV   |

| Step (+12, +16, +20, +24dB)                                               |          | +4       |      | dB    |

| Load Resistance                                                           | 2        |          |      | kΩ    |

| Load Capacitance (Note 11)                                                |          |          | 20   | pF    |

| Inverter-Amp Characteristics: (Gain:0dB)                                  |          |          |      |       |

| Maximum Output Voltage (Note 9)                                           |          |          | -3.2 | dBV   |

| Load Resistance                                                           | 3        |          |      | kΩ    |

| Load Capacitance (Note 11)                                                |          |          | 20   | pF    |

| EQ-Amp Characteristics: (Gain:0dB)                                        |          |          |      |       |

| Maximum Output Voltage (Note 9)                                           |          |          | -3.2 | dBV   |

| Load Resistance                                                           | 3        |          |      | kΩ    |

| Load Capacitance (Note 11)                                                |          |          | 20   | pF    |

| HPF-Amp Characteristics: (Gain: 0dB)                                      |          |          |      |       |

| Maximum Output Voltage (Note 9)                                           |          |          | -3.2 | dBV   |

| Load Resistance                                                           | 3        |          |      | kΩ    |

| Load Capacitance (Note 11)                                                |          |          | 20   | pF    |

| MIC Block Characteristics: Measured via HPF_O_L/HPF_O_R (N                | lote 10) |          |      |       |

| S/(N+D) (-10dBV Output) (Note 12)                                         |          | 60       |      | dB    |

| (Note 10)                                                                 |          | 60       |      | dB    |

| Output Noise Voltage (No signal input, $Rg = 1k\Omega$ ) (Note 12)        |          | -94      |      | dBV   |

| (Note 10)                                                                 |          | -99      |      | dBV   |

| Interchannel Gain Mismatch (Note 12)                                      |          | 0.5      |      | dB    |

| (Note 10)                                                                 |          | 0.5      |      | dB    |

| Interchannel Isolation (Note 12)                                          |          | 70       |      | dB    |

| (Note 10)                                                                 |          | 70       |      | dB    |

| MIC Power Supply Characteristics:                                         |          |          | •    |       |

| Output Voltage (5kΩ Load)                                                 |          | 2.0      |      | V     |

| Output Current                                                            |          |          | 3    | mA    |

Note 7. INT\_MIC\_L, INT\_MIC\_R, EXT\_MIC\_L and EXT\_MIC\_R pins

Note 8. Gain of Pre-Amp is +16dB. Input resistance of Pre-Amp is changed by gain.

Gain=12dB: 2.4k ± 30%Ω, Gain=20dB: 950 ± 30%Ω, Gain=24dB: 600 ± 30%Ω

Note 9. Maximum output voltage is typically (MVDD x 0.7) V.

Note 10. Pre-Amp(Gain:+16dB)  $\rightarrow$  HPF-Amp (Gain:0dB, HPF OFF)

Note 11. When output pin drives some capacitive load, some resistor should be added in series between output pin and capacitive load.

Note 12. Pre-Amp (Gain: +16dB)  $\rightarrow$  Inverter-Amp (Gain: +0dB)  $\rightarrow$  EQ-Amp (Input/Feedback resistance: 5k $\Omega$ )  $\rightarrow$  HPF-Amp (Gain: 0dB, HPF OFF)

| Parameter                                                  |                                       |                       |             | typ    | max  | Units |

|------------------------------------------------------------|---------------------------------------|-----------------------|-------------|--------|------|-------|

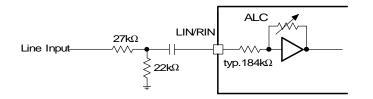

| ALC Charac                                                 | teristics (IPGA):                     |                       |             |        |      |       |

| Maximum Inp                                                | out Voltage (Note 13)                 |                       |             |        | -0.5 | dBV   |

| Input Resistan                                             | nce:                                  |                       |             |        |      |       |

| Input Resistance:<br>MIC(MIC_IN_L,MIC_IN_R pins) (Note 14) |                                       |                       |             | 9      | 13   | kΩ    |

| LINE(L                                                     | 117                                   | 184                   | 260         | kΩ     |      |       |

| Step Size                                                  | MIC                                   | LINE                  |             |        |      |       |

|                                                            | +26dB ~ -10dB                         | $+0dB \sim -36dB$     | 0.1         | 0.5    |      | dB    |

|                                                            | -10dB ~ -18dB                         | -36dB ~ -44dB         | 0.1         | 1      |      | dB    |

|                                                            | -18dB ~ -30dB                         | -44dB ~ $-56$ dB      | 0.1         | 2      |      | dB    |

|                                                            | -30dB ~ -42dB                         | -56dB ~ -68dB         | -           | 2      | -    | dB    |

|                                                            | -42dB ~ -54dB                         | -68dB ~ -80dB         | -           | 4      | -    | dB    |

| ADC Analog                                                 | Input Characteristics: In             | put from LIN/RIN, ALC | = OFF, IPGA | = 0 dB |      |       |

| Resolution                                                 |                                       |                       |             |        | 16   | Bits  |

| Input Voltage                                              | (Note 16)                             |                       | -5.5        |        | dBV  |       |

| S/(N+D)(-0.50                                              | dBFS Output)                          |                       |             | 78     |      | dB    |

| DR (-60dBFS                                                | Output, A-Weighted)                   |                       |             | 86     |      | dB    |

| S/N (A-Weighted)                                           |                                       |                       |             | 86     |      | dB    |

| Interchannel Isolation                                     |                                       |                       |             | 80     |      | dB    |

| Interchannel C                                             | Gain Mismatch                         |                       |             | 0.5    |      | dB    |

| DAC Analog                                                 | Characteristics: Measure              | ed via LOUT1/ROUT1, V | OL=+7.5dB   |        |      |       |

| Resolution                                                 |                                       |                       |             |        | 16   | Bits  |

| S/(N+D) (0dI                                               | BFS Input)                            |                       |             | 76     |      | dB    |

| DR (-60dBFS                                                | Input, A-Weighted)                    |                       |             | 88     |      | dB    |

| S/N (A-Weigh                                               | hted)                                 |                       |             | 88     |      | dB    |

| Output Voltag                                              | ge (Note 16)                          |                       |             | +2     |      | dBV   |

| Interchannel I                                             | solation                              |                       |             | 80     |      | dB    |

| Interchannel C                                             | Gain Mismatch                         |                       |             | 0.5    |      | dB    |

| Load Resistan                                              | ice                                   |                       | 10          |        |      | kΩ    |

| Load Capacita                                              | ance (Note 17)                        |                       |             |        | 20   | pF    |

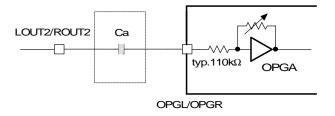

| Analog Volu                                                | me Characteristics (OPG               | A):                   |             |        |      |       |

| Input Resistan                                             | nce (OPGL,OPGR pins) (                | Note 18)              | 44          | 110    | 205  | kΩ    |

| Step Size: +00                                             | dB ~ -16dB                            |                       | 0.1         | 1      |      | dB    |

| -160                                                       | dB ~ -38dB                            |                       | 0.1         | 2      |      | dB    |

| -38                                                        | dB ~ -50dB                            |                       | -           | 4      | -    | dB    |

| <b>BEEP Input:</b>                                         | (BEEP pin)                            |                       |             |        |      |       |

| Maximum Inp                                                | out Voltage (Note 16)                 |                       |             |        | -5.5 | dBV   |

| Input Resistan                                             | · · · · · · · · · · · · · · · · · · · |                       |             | 50     |      | kΩ    |

Note 13. When the ALC operation is enabled, maximum input voltage becomes typically (VA - 0.1V) Vpp. 2.7Vpp = -0.5dBV @VA=2.8V

Note 14. Input resistance of MIC changes from  $8k\Omega$  to  $10k\Omega$  by setting GAIN value, typically.

Note 15. Input resistance of LINE changes from  $168k\Omega$  to  $200k\Omega$  by setting GAIN value, typically.

Note 16. Input/Output voltage is proportional to VA voltage. 0.54 x VA.

Note 17. When output pin drives some capacitive load, some resistor should be added in series between output pin and capacitive load.

Note 18. Input resistance of OPGA changes from  $63k\Omega$  to  $158k\Omega$  by setting GAIN value, typically.

| Parameter                                                     | min            | typ           | max      | Units |

|---------------------------------------------------------------|----------------|---------------|----------|-------|

| Headphone-Amp Characteristics: $R_L = 47 + 8\Omega$ (Note 19) |                |               |          |       |

| Output Voltage (-5.5dBV Input) (Note 16)                      |                | -5.5          |          | dBV   |

| S/(N+D) (-5.5dBV Output)                                      |                | 40            |          | dB    |

| Output Noise Voltage (OPGA=MUTE, A-Weighted)                  |                | -86           |          | dBV   |

| Interchannel Isolation                                        |                | 40            |          | dB    |

| Interchannel Gain Mismatch                                    |                | 0.5           |          | dB    |

| Load Resistance                                               | 55             |               |          | Ω     |

| Load Capacitance (Note 17)                                    |                |               | 20       | pF    |

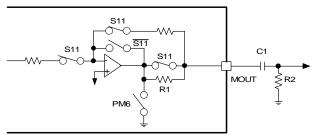

| Monaural Output: (MOUT pin) (Note 20)                         |                |               |          |       |

| Output Voltage (-5.5dBV Input) (Note 21)                      |                | -11.5         |          | dBV   |

| S/(N+D) (-5.5dBV Output)                                      |                | 80            |          | dB    |

| S/N (A-weighted)                                              |                | 90            |          | dB    |

| Load Resistance                                               | 5              |               |          | kΩ    |

| Load Capacitance (Note 17)                                    |                |               | 20       | pF    |

| Power Supply Current                                          |                |               |          |       |

| Power Up $(\overline{PD} = "H")$                              |                |               |          |       |

| All Circuit Power-Up: (PM7-0 bit all "1")                     |                |               |          |       |

| VA: Headphone-Amp No input (S8 = "1")                         |                | 21            |          | mA    |

| VD+VT: (DLYE bit = "1")                                       |                | 5             |          | mA    |

| MVDD: (Note 22)                                               |                | 9             |          | mA    |

| HVDD: (S10 = "1") (Note 23)                                   |                | 3             |          | mA    |

| ALC + ADC: (PM4=PM2=PM1= "1") (Note 23)                       |                |               |          |       |

| VA:                                                           |                | 9             |          | mA    |

| VD+VT: (DLYE bit = "1")                                       |                | 4             |          | mA    |

| HVDD                                                          | -              | 0.5           | -        | mA    |

| DAC + OPGA + MOUT + LINEOUT: (PM7=PM6=PM4=PM                  | [3= "1") (Note | e 23)         |          |       |

| VA:                                                           |                | 10            |          | mA    |

| VD+VT:                                                        |                | 2             |          | mA    |

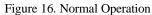

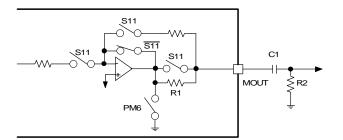

| HVDD: LINEOUT Normal Operation (S10 = "1")                    |                | 2             |          | mA    |

| LINEOUT Power-Save-Mode (S10 = "0")                           | -              | 0.2           | -        | mA    |

| DAC + OPGA+ MOUT + LINEOUT + HP-Amp: (PM7=PM6                 | =PM5=PM4=      | =PM3= "1") (N | Note 23) | -     |

| VA: Headphone-Amp Normal Operation (S8 = "1"),                |                |               |          |       |

| No Input                                                      |                | 14            |          | mA    |

| Headphone-Amp Power-Save-Mode (S8 = "0")                      | -              | 11            | -        | mA    |

| VD+VT:                                                        |                | 2             |          | mA    |

| HVDD: (S10 = "1")                                             | -              | 2             | -        | mA    |

| Power Down ( $\overline{PD} = "L"$ )                          |                |               |          |       |

| VA+VD+HVDD+MVDD (Note 24)                                     |                | 200           |          | μΑ    |

Note 19. Input from OPGL and OPGR pins. Analog Volume (OPGA=0dB) → Headphone Amplifier

Note 20. Input from OPGL and OPGR pins. Analog Volume (OPGA=0dB) → Monaural Amplifier

Note 21. Lch = -5.5dBV, Rch = no input or Rch = -5.5dBV, Lch = no input

Note 22. MPWR pin supplies 0mA.

Note 23. Then power supply current of MVDD is 0.2mA (typ.).

Note 24. In case of power-down, digital input pins of MCLK, BCLK, LRCK and SDTI are held "VD" or "DGND". Digital input pins of CCLK, REC\_MUTE, CCLK, CS, CDTI and MUTE are held "VT" or "DGND". PD pin is held "DGND".

Rev. 0.9

|                               | FIL         | TER CHARA      | CTERISTIC | S    |       |       |

|-------------------------------|-------------|----------------|-----------|------|-------|-------|

| (Ta=25°C; VA=VD=2.6 ~ 3.3V;   | fs=48kHz; D | e-emphasis = C | )FF)      |      |       |       |

| Parameter                     |             | Symbol         | min       | typ  | max   | Units |

| ADC Digital Filter (LPF):     |             |                |           |      |       |       |

| Passband (Note 25)            | ±0.1dB      | PB             | 0         |      | 18.9  | kHz   |

|                               | -1.0dB      |                | -         | 21.8 | -     | kHz   |

|                               | -3.0dB      |                | -         | 23.0 | -     | kHz   |

| Stopband (Note 25)            | •           | SB             | 29.4      |      |       | kHz   |

| Passband Ripple               |             | PR             |           |      | ±0.1  | dB    |

| Stopband Attenuation          |             | SA             | 65        |      |       | dB    |

| Group Delay (Note 26)         |             | GD             | -         | 17.0 | -     | 1/fs  |

| Group Delay Distortion        |             | $\Delta GD$    |           | 0    |       | us    |

| ADC Digital Filter (HPF):     |             |                |           |      |       |       |

| Frequency Response (Note 25)  | -3.0dB      | FR             | -         | 3.7  | -     | Hz    |

|                               | -0.56dB     |                | -         | 10   | -     | Hz    |

|                               | -0.15dB     |                | -         | 20   | -     | Hz    |

| DAC Digital Filter:           |             |                |           |      |       |       |

| Passband (Note 25)            | ±0.1dB      | PB             | 0         |      | 21.7  | kHz   |

|                               | -6.0dB      |                | -         | 24.0 | -     | kHz   |

| Stopband (Note 25)            | 1           | SB             | 26.2      |      |       | kHz   |

| Passband Ripple               |             | PR             |           |      | ±0.06 | dB    |

| Stopband Attenuation          |             | SA             | 43        |      |       | dB    |

| Group Delay (Note 26)         |             | GD             | -         | 14.8 | -     | 1/fs  |

| DAC Digital Filter + Analog F | ilter:      |                |           |      |       |       |

| Frequency Response            | 0~20.0kHz   | FR             |           | ±0.5 |       | dB    |

Note 25. The passband and stopband frequencies scale with fs (system sampling rate). For example, ADC is PB=0.454\*fs (@-1.0dB), DAC is PB=0.454\*fs (@-0.1dB).

Note 26. The calculating delay time which occured by digital filtering, This time is from the input of analog signal to setting the 16 bit data of both channels on input register to the output register of ADC. And this time include group delay of HPF. For DAC, this time is from setting the 16 bit data of both channels on input register to the output of analog signal.

Rev. 0.9

| DC CHARACTERISTICS                              |        |        |     |       |       |  |  |  |  |

|-------------------------------------------------|--------|--------|-----|-------|-------|--|--|--|--|

| (Ta=25°C; VA=VD=2.6 ~ 3.3V; VT=1.8 ~ 3.3V)      |        |        |     |       |       |  |  |  |  |

| Parameter                                       | Symbol | min    | typ | max   | Units |  |  |  |  |

| High-Level Input Voltage (Note 27)              | VIH    | 1.5    | -   | -     | V     |  |  |  |  |

| Low-Level Input Voltage (Note 27)               | VIL    | -      | -   | 0.6   | V     |  |  |  |  |

| High-Level Output Voltage (Note 28) Iout=-200µA | VOH1   | VD-0.2 | -   | -     | V     |  |  |  |  |

| Low-Level Output Voltage (Note 28) Iout=200µA   | VOL1   | -      | -   | 0.2   | V     |  |  |  |  |

| High-Level Output Voltage (Note 29)             | VOH2   | 75%VT  | -   | -     | V     |  |  |  |  |

| Low-Level Output Voltage (Note 29)              | VOL2   | -      | -   | 25%VT | V     |  |  |  |  |

| Input Leakage Current                           | Iin    | -      | -   | ±10   | μΑ    |  |  |  |  |

Note 27. MCLK, BCLK, LRCK and SDTI pins Note 28. SDTO and COMP pins

Note 29. CS, CCLK, CDTI, PD, REC\_MUTE and MUTE pins

Downloaded from Elcodis.com electronic components distributor

| SWITCHING CHARACTERISTICS                                             |        |       |        |      |       |  |  |  |  |

|-----------------------------------------------------------------------|--------|-------|--------|------|-------|--|--|--|--|

| $(Ta=25^{\circ}C; VA=VD=2.6 \sim 3.3V; VT=1.8 \sim 3.3V; C_{L}=20pF)$ |        |       |        |      |       |  |  |  |  |

| Parameter                                                             | Symbol | min   | typ    | max  | Units |  |  |  |  |

| Control Clock Frequency                                               |        |       |        |      |       |  |  |  |  |

| Master Clock(MCLK) 256fs: Frequency                                   | fCLK   | 2.048 | 12.288 | 12.8 | MHz   |  |  |  |  |

| Pulse Width Low                                                       | tCLKL  | 28    |        |      | ns    |  |  |  |  |

| Pulse Width High                                                      | tCLKH  | 28    |        |      | ns    |  |  |  |  |

| 384fs: Frequency                                                      | fCLK   | 3.072 | 18.432 | 19.2 | MHz   |  |  |  |  |

| Pulse Width Low                                                       | tCLKL  | 23    |        |      | ns    |  |  |  |  |

| Pulse Width High                                                      | tCLKH  | 23    |        |      | ns    |  |  |  |  |

| Channel Select Clock (LRCK): Frequency                                | fs     | 8     | 48     | 50   | kHz   |  |  |  |  |

| Duty                                                                  | Duty   | 45    | 50     | 55   | %     |  |  |  |  |

| Audio Interface Timing                                                |        |       |        |      |       |  |  |  |  |

| BCLK Period                                                           | tBLK   | 312.5 |        |      | ns    |  |  |  |  |

| BCLK Pulse Width Low                                                  | tBLKL  | 130   |        |      | ns    |  |  |  |  |

| Pulse Width High                                                      | tBLKH  | 130   |        |      | ns    |  |  |  |  |

| LRCK Edge to BCLK "↑" (Note 30)                                       | tLRB   | 50    |        |      | ns    |  |  |  |  |

| BCLK " <sup>↑</sup> " to LRCK Edge (Note 30)                          | tBLR   | 50    |        |      | ns    |  |  |  |  |

| LRCK to SDTO(MSB) Delay Time                                          | tLRM   |       |        | 80   | ns    |  |  |  |  |

| BCLK " $\downarrow$ " to SDTO Delay Time                              | tBSD   |       |        | 80   | ns    |  |  |  |  |

| SDTI Latch Hold Time                                                  | tSDH   | 50    |        |      | ns    |  |  |  |  |

| SDTI Latch Set up Time                                                | tSDS   | 50    |        |      | ns    |  |  |  |  |

| Control Interface Timing                                              |        |       |        |      |       |  |  |  |  |

| CCLK Period                                                           | tCCK   | 200   |        |      | ns    |  |  |  |  |

| CCLK Pulse Width Low                                                  | tCCKL  | 80    |        |      | ns    |  |  |  |  |

| Pulse Width High                                                      | tCCKH  | 80    |        |      | ns    |  |  |  |  |

| CDTI Latch Set Up Time                                                | tCDS   | 50    |        |      | ns    |  |  |  |  |

| CDTI Latch Hold Time                                                  | tCDH   | 50    |        |      | ns    |  |  |  |  |

| CS "H" Time                                                           | tCSW   | 150   |        |      | ns    |  |  |  |  |

| $\overline{\text{CS}}$ " $\downarrow$ " to CCLK " $\uparrow$ "        | tCSS   | 50    |        |      | ns    |  |  |  |  |

| CCLK " $\uparrow$ " to CS " $\uparrow$ "                              | tCSH   | 50    |        |      | ns    |  |  |  |  |

| Reset Timing                                                          |        |       |        |      |       |  |  |  |  |

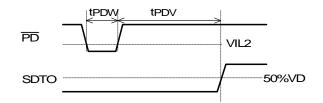

| PD Pulse Width                                                        | tPDW   | 150   |        |      | ns    |  |  |  |  |

| PD " $\uparrow$ " to SDTO Delay Time (Note 31)                        | tPDV   |       | 8224   |      | 1/fs  |  |  |  |  |

Note 30. BCLK rising edge must not occur at the same time as LRCK edge.

Note 31. These cycles are the numbers of LRCK rising from PDN pin rising.

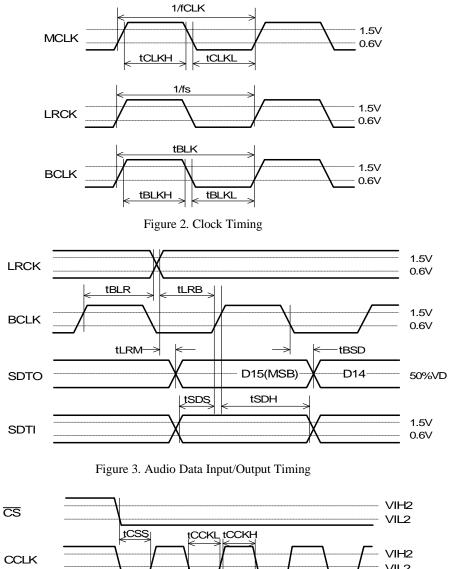

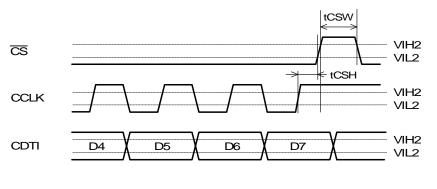

## Timing Diagram

Figure 4. WRITE Command Input Timing 1

Figure 5. WRITE Data Input Timing 2

Figure 6. Reset Timing

## **OPERATION OVERVIEW**

#### System Clock

The clock which are required to operate are MCLK (256fs/384fs), LRCK (fs), BCLK (32fs~). The master clock (MCLK) should be synchronized with LRCK but the phase is free of care.

The MCLK can be input 256fs or 384fs. When 384fs is input, the internal master clock is divided into 2/3 automatically. \* fs is sampling frequency.

When the synchronization is out of phase by changing the clock frequencies during normal operation, the AK4561 may occur click noise. In case of DAC, click noise is avoided by setting the inputs to "0".

All external clocks (MCLK, BCLK and LRCK) should always be present. If these clocks are not provided, the AK4561 may draw excess current and it is not possible to operate properly because utilizes dynamic refreshed logic internally. If the external clocks are not present, the AK4561 should be in the power-down mode. (Refer to the "Power Management Mode".)

#### System Reset

AK4561 should be reset once by bringing PD pin "L" upon power-up. After the system reset operation, the all internal AK4561 registers become initial value.

Initializing cycle is 8224/fs=171.3ms@fs=48kHz. During initializing cycle, the ADC digital data outputs of both channels are forced to a 2's compliment, "0". Output data of ADC settles data equivalent for analog input signal after initializing cycle. This cycle is not for DAC.

As a normal initializing cycle may not be executed, nothing writes at address 02H during initializing cycle.

#### Digital High Pass Filter

The ADC has HPF for the DC offset cancel. The cut-off frequency of HPF is 3.7Hz (@fs=48kHz) and it is -0.15dB at 22Hz. It also scales with the sampling frequency (fs).

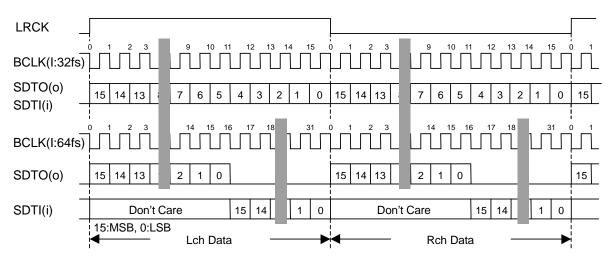

## Audio Interface Format

Data is shifted in/out the SDTI/SDTO pins using BCLK and LRCK inputs. The serial data is MSB-first, 2's compliment format, ADC is MSB justified and DAC is LSB justified.

Figure 7. Audio Data Timing

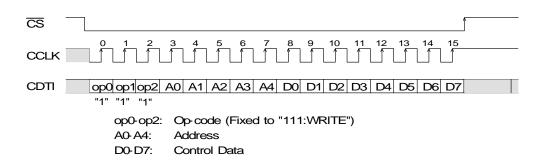

## Control Register Timing

The data on the 3-wire serial interface consists of op-code (3bit), address (LSB-first, 5bit) and control data (LSB-first, 8bit). The Transmitting data is output to each bit by " $\downarrow$ " of CCLK, the receiving data is latched by " $\uparrow$ " of CCLK. Writing data becomes effective by " $\uparrow$ " of CS. CS should be held to "H" at no access.

<u>CCLK always need 16 edges of " $\uparrow$ " during <u>CS</u> = "L" Address except 00H~0BH are inhibited. Writing of the control registers are invalid when op2-0 bits are except "111".</u>

Figure 8. Control Data Timing

#### Register Map

The following registers are reset at  $\overline{PD}$  pin = "L", then inhibits writing.

| Addr | Register Name            | D7    | D6    | D5    | D4    | D3         | D2    | D1         | D0         |

|------|--------------------------|-------|-------|-------|-------|------------|-------|------------|------------|

| 00H  | Signal Select 1          | EQ    | S6    | S5    | S4    | <b>S</b> 3 | S2    | <b>S</b> 1 | <b>S</b> 0 |

| 01H  | Signal Select 2          | 0     | 0     | S12   | S11   | S10        | S9    | <b>S</b> 8 | <b>S</b> 7 |

| 02H  | Power Management Control | PM7   | PM6   | PM5   | PM4   | PM3        | PM2   | PM1        | PM0        |

| 03H  | Mode Control             | FS    | VOL2  | VOL1  | VOL0  | MONO1      | MONO0 | DEM1       | DEM0       |

| 04H  | Timer Select             | FDTM1 | FDTM0 | ZTM1  | ZTM0  | WTM1       | WTM0  | LTM1       | LTM0       |

| 05H  | ALC Mode Control 1       | 0     | 0     | ZELM  | LMAT1 | LMAT0      | FDATT | RATT       | LMTH       |

| 06H  | ALC Mode Control 2       | 0     | REF6  | REF5  | REF4  | REF3       | REF2  | REF1       | REF0       |

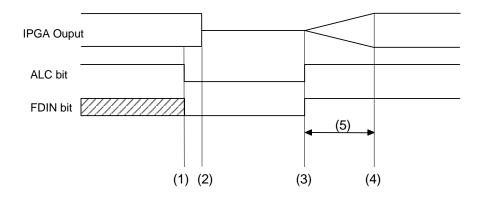

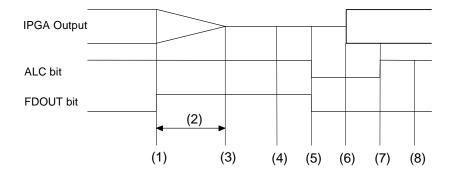

| 07H  | Operation Mode           | 0     | 0     | FR    | COMP  | 0          | FDIN  | FDOUT      | ALC        |

| 08H  | Input PGA Control        | 0     | IPGA6 | IPGA5 | IPGA4 | IPGA3      | IPGA2 | IPGA1      | IPGA0      |

| 09H  | Output PGA Control       | 0     | 0     | 0     | OPGA4 | OPGA3      | OPGA2 | OPGA1      | OPGA0      |

| 0AH  | Digital Delay 1          | DLYE  | DLY6  | DLY5  | DLY4  | DLY3       | DLY2  | DLY1       | DLY0       |

| 0BH  | Digital Delay 2          | 0     | 0     | 0     | 0     | COE3       | COE2  | COE1       | COE0       |

#### Table 1. AK4561 Register Map

#### Signal Select 1

| Addr | Register Name   | D7 | D6 | D5 | D4 | D3         | D2 | D1         | D0         |

|------|-----------------|----|----|----|----|------------|----|------------|------------|

| 00H  | Signal Select 1 | EQ | S6 | S5 | S4 | <b>S</b> 3 | S2 | <b>S</b> 1 | <b>S</b> 0 |

|      | RESET           | 1  | 0  | 1  | 0  | 1          | 0  | 0          | 0          |

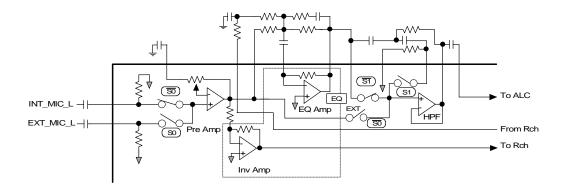

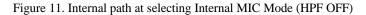

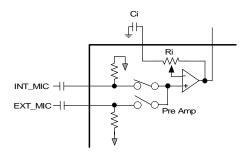

S0: Select Internal / External MIC (Refer to Figure 11 and Figure 12)

0: Internal MIC (RESET)

1: External MIC

S1: Select HPF-Amp

0: Disable (RESET)

1: Enable

When S1 bit is "0", HPF-Amp becomes a unity gain buffer.

When External MIC (S0 bit = "1") is selected, S1 bit is ignored.

S2: Select input signal of ALC and change gain table of IPGA.

0: MIC (RESET)

1: LINE

S4-3: Select input signal of LINEOUT or Analog Volume (OPGA)

ON/OFF of DAC is selected by S3 bit, and ON/OFF of Analog Through Mode is selected by S4 bit.

00: All input signals are OFF. Then output voltage becomes common voltage.

01:DAC (RESET)

10: Analog Through Mode (Output signal of ALC)

11: Output signal of DAC and Analog Through are mixed.

S6-5: Select gain of Pre-Amp; +12dB ~ +24dB; 4dB step

| S6                         | S5 | Gain  |       |  |  |  |  |  |

|----------------------------|----|-------|-------|--|--|--|--|--|

| 0                          | 0  | +12dB |       |  |  |  |  |  |

| 0                          | 1  | +16dB | RESET |  |  |  |  |  |

| 1                          | 0  | +20dB |       |  |  |  |  |  |

| 1                          | 1  | +24dB |       |  |  |  |  |  |

| Table 2 Dro Amp Cain Table |    |       |       |  |  |  |  |  |

Table 2. Pre-Amp Gain Table

EQ: Power management of EQ-Amp and Inverter-Amp

0: OFF. EQ-Amp and Inverter-Amp are always powered-down, then EQ bit is not relative. 1: ON. EQ-Amp and Inverter-Amp are powered-up/down by PM0 bit. (RESET)

#### Note: Pop noise may occur when EQ or S6-0 bits are changed.

## Signal Select 2

| AddrRegister NameD7D6D5D4D3D2D1D001HSignal Select 200\$12\$11\$10\$9\$8\$57RESET00010100S7: Select input signal of analog volume (OPGA)<br>0: OFF. OPGA output voltage becomes VCOM voltage (RESET)<br>1: ON. OPGA is provided to the signal selected by \$4-3 bits (DAC or Analog Through Mode<br>\$8: Select output signal of Headphone-Amp<br>0: OFF. Power-Save-Mode. HPL/HPR pins become Hi-z and HVCM pin is provided to VCO<br>voltage. (RESET)<br>1: ON\$9: Select input signal of BEEP<br>0: OFF<br>1: ON0: OFF (RESET)<br>Power-Save-Mode. LINEOUT is provided to VCOM_H voltage.<br>1: ON\$10: Select LINEOUT<br>0: OFF (RESET)<br>Power-Save-Mode. INEOUT is provided to VCOM_H voltage.<br>1: ON\$11: Select monaural output (Mixing = (L+R)/2)<br>0: OFF (RESET)<br>Power-Save-Mode, monaural output is provided to VCOM voltage.<br>1: ON\$12: Select monaural input<br>0: OFF (RESET)<br>POwer-Save-Mode, monaural output is provided to VCOM voltage.<br>1: ON\$12: Select monaural input<br>0: OFF (RESET)<br>POwer-Save-Inde, monaural output is provided to VCOM voltage.<br>1: ON\$12: Select monaural input<br>0: OFF (RESET)<br>1: ON. Output signal of analog volume is provided to monaural amplifier. |                                                                          |                              | r          |              |              |             |             |           |            |           |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------|------------|--------------|--------------|-------------|-------------|-----------|------------|-----------|--|

| RESET       0       0       0       1       0       1       0       0         S7: Select input signal of analog volume (OPGA)       0: OFF. OPGA output voltage becomes VCOM voltage (RESET)       1: ON. OPGA is provided to the signal selected by S4-3 bits (DAC or Analog Through Mode S8: Select output signal of Headphone-Amp       0: OFF. Power-Save-Mode. HPL/HPR pins become Hi-z and HVCM pin is provided to VCO voltage. (RESET)         1: ON       0: OFF. Power-Save-Mode. HPL/HPR pins become Hi-z and HVCM pin is provided to VCO voltage. (RESET)       1: ON         S9: Select input signal of BEEP       0: OFF       1: ON (RESET)         S10: Select LINEOUT       0: OFF (RESET)         Power-Save-Mode. LINEOUT is provided to VCOM_H voltage.       1: ON         S11: Select monaural output (Mixing = (L+R)/2)       0: OFF (RESET)         Power-Save-Mode, monaural output is provided to VCOM voltage.       1: ON         S12: Select monaural input       0: OFF (RESET)         0: OFF (RESET)       Power-Save-Mode, monaural output is provided to VCOM voltage.         1: ON       S12: Select monaural input         0: OFF (RESET)       0: OFF (RESET)                              | Addr                                                                     | Register Name                | D7         | D6           | D5           | D4          | D3          | D2        | D1         | D0        |  |

| <ul> <li>S7: Select input signal of analog volume (OPGA) <ul> <li>0: OFF. OPGA output voltage becomes VCOM voltage (RESET)</li> <li>1: ON. OPGA is provided to the signal selected by S4-3 bits (DAC or Analog Through Mode S8: Select output signal of Headphone-Amp</li> <li>0: OFF. Power-Save-Mode. HPL/HPR pins become Hi-z and HVCM pin is provided to VCO voltage. (RESET)</li> <li>1: ON</li> </ul> </li> <li>S9: Select input signal of BEEP <ul> <li>0: OFF</li> <li>1: ON (RESET)</li> </ul> </li> <li>S10: Select LINEOUT <ul> <li>0: OFF (RESET)</li> <li>Power-Save-Mode. LINEOUT is provided to VCOM_H voltage.</li> <li>1: ON</li> </ul> </li> <li>S11: Select monaural output (Mixing = (L+R)/2) <ul> <li>0: OFF (RESET)</li> <li>Power-Save-Mode, monaural output is provided to VCOM voltage.</li> <li>1: ON</li> </ul> </li> <li>S12: Select monaural input <ul> <li>0: OFF (RESET)</li> <li>OFF (RESET)</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                             | 01H                                                                      | Signal Select 2              | 0          | 0            | S12          | S11         | S10         | S9        | S8         | S7        |  |

| <ul> <li>0: OFF. OPGA output voltage becomes VCOM voltage (RESET) <ol> <li>ON. OPGA is provided to the signal selected by S4-3 bits (DAC or Analog Through Mode S8: Select output signal of Headphone-Amp</li> <li>0: OFF. Power-Save-Mode. HPL/HPR pins become Hi-z and HVCM pin is provided to VCO voltage. (RESET)</li> <li>1: ON</li> </ol> </li> <li>S9: Select input signal of BEEP <ol> <li>OFF</li> <li>ON (RESET)</li> </ol> </li> <li>S10: Select LINEOUT <ol> <li>OFF (RESET)</li> <li>Power-Save-Mode. LINEOUT is provided to VCOM_H voltage.</li> <li>ON</li> </ol> </li> <li>S11: Select monaural output (Mixing = (L+R)/2) <ol> <li>OFF (RESET)</li> <li>Power-Save-Mode, monaural output is provided to VCOM voltage.</li> <li>ON</li> </ol> </li> <li>S12: Select monaural input <ol> <li>OFF (RESET)</li> </ol> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                   |                                                                          | RESET                        | 0          | 0            | 0            | 1           | 0           | 1         | 0          | 0         |  |

| <ul> <li>1: ON. OPGA is provided to the signal selected by S4-3 bits (DAC or Analog Through Mode S8: Select output signal of Headphone-Amp <ul> <li>0: OFF. Power-Save-Mode. HPL/HPR pins become Hi-z and HVCM pin is provided to VCO voltage. (RESET)</li> <li>1: ON</li> </ul> </li> <li>S9: Select input signal of BEEP <ul> <li>0: OFF</li> <li>1: ON (RESET)</li> </ul> </li> <li>S10: Select LINEOUT <ul> <li>0: OFF (RESET)</li> <li>Power-Save-Mode. LINEOUT is provided to VCOM_H voltage.</li> <li>1: ON</li> </ul> </li> <li>S11: Select monaural output (Mixing = (L+R)/2) <ul> <li>0: OFF (RESET)</li> <li>Power-Save-Mode, monaural output is provided to VCOM voltage.</li> <li>1: ON</li> </ul> </li> <li>S12: Select monaural input <ul> <li>0: OFF (RESET)</li> <li>0: OFF (RESET)</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                     | S7: Select input signal of analog volume (OPGA)                          |                              |            |              |              |             |             |           |            |           |  |

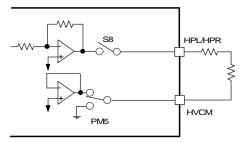

| S8: Select output signal of Headphone-Amp<br>0: OFF. Power-Save-Mode. HPL/HPR pins become Hi-z and HVCM pin is provided to VCO<br>voltage. (RESET)<br>1: ON S9: Select input signal of BEEP<br>0: OFF<br>1: ON (RESET) S10: Select LINEOUT<br>0: OFF (RESET)<br>Power-Save-Mode. LINEOUT is provided to VCOM_H voltage.<br>1: ON S11: Select monaural output (Mixing = (L+R)/2)<br>0: OFF (RESET)<br>Power-Save-Mode, monaural output is provided to VCOM voltage.<br>1: ON S12: Select monaural input<br>0: OFF (RESET)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0: OFF. OPGA output voltage becomes VCOM voltage (RESET)                 |                              |            |              |              |             |             |           |            |           |  |

| <ul> <li>0: OFF. Power-Save-Mode. HPL/HPR pins become Hi-z and HVCM pin is provided to VCO voltage. (RESET) <ol> <li>ON</li> </ol> </li> <li>S9: Select input signal of BEEP <ol> <li>ON (RESET)</li> </ol> </li> <li>S10: Select LINEOUT <ol> <li>OFF (RESET)</li> <li>Power-Save-Mode. LINEOUT is provided to VCOM_H voltage. <ol> <li>ON</li> </ol> </li> <li>S11: Select monaural output (Mixing = (L+R)/2) <ol> <li>OFF (RESET)</li> <li>Power-Save-Mode, monaural output is provided to VCOM voltage. <ol> <li>ON</li> </ol> </li> <li>S12: Select monaural input <ol> <li>OFF (RESET)</li> </ol> </li> </ol></li></ol></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                          | 1: ON. OP                    | GA is prov | vided to the | signal sel   | ected by S4 | -3 bits (DA | AC or Ana | log Throug | gh Mode). |  |

| voltage. (RESET)<br>1: ON<br>S9: Select input signal of BEEP<br>0: OFF<br>1: ON (RESET)<br>S10: Select LINEOUT<br>0: OFF (RESET)<br>Power-Save-Mode. LINEOUT is provided to VCOM_H voltage.<br>1: ON<br>S11: Select monaural output (Mixing = (L+R)/2)<br>0: OFF (RESET)<br>Power-Save-Mode, monaural output is provided to VCOM voltage.<br>1: ON<br>S12: Select monaural input<br>0: OFF (RESET)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | S8                                                                       | : Select output signal of He | adphone-A  | mp           |              |             |             |           |            |           |  |

| 1: ON<br>S9: Select input signal of BEEP<br>0: OFF<br>1: ON (RESET)<br>S10: Select LINEOUT<br>0: OFF (RESET)<br>Power-Save-Mode. LINEOUT is provided to VCOM_H voltage.<br>1: ON<br>S11: Select monaural output (Mixing = (L+R)/2)<br>0: OFF (RESET)<br>Power-Save-Mode, monaural output is provided to VCOM voltage.<br>1: ON<br>S12: Select monaural input<br>0: OFF (RESET)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                          | 0: OFF. Po                   | wer-Save-  | Mode. HP     | L/HPR pin    | s become H  | li-z and H  | VCM pin i | s provided | to VCOM   |  |

| <ul> <li>S9: Select input signal of BEEP <ul> <li>0: OFF</li> <li>1: ON (RESET)</li> </ul> </li> <li>S10: Select LINEOUT <ul> <li>0: OFF (RESET)</li> <li>Power-Save-Mode. LINEOUT is provided to VCOM_H voltage.</li> <li>1: ON</li> </ul> </li> <li>S11: Select monaural output (Mixing = (L+R)/2) <ul> <li>0: OFF (RESET)</li> <li>Power-Save-Mode, monaural output is provided to VCOM voltage.</li> <li>1: ON</li> </ul> </li> <li>S12: Select monaural input <ul> <li>0: OFF (RESET)</li> <li>OFF (RESET)</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                          | voltage. (R                  | ESET)      |              |              |             |             |           |            |           |  |

| 0: OFF<br>1: ON (RESET)<br>S10: Select LINEOUT<br>0: OFF (RESET)<br>Power-Save-Mode. LINEOUT is provided to VCOM_H voltage.<br>1: ON<br>S11: Select monaural output (Mixing = (L+R)/2)<br>0: OFF (RESET)<br>Power-Save-Mode, monaural output is provided to VCOM voltage.<br>1: ON<br>S12: Select monaural input<br>0: OFF (RESET)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                          | 1: ON                        |            |              |              |             |             |           |            |           |  |

| 1: ON (RESET)<br>S10: Select LINEOUT<br>0: OFF (RESET)<br>Power-Save-Mode. LINEOUT is provided to VCOM_H voltage.<br>1: ON<br>S11: Select monaural output (Mixing = (L+R)/2)<br>0: OFF (RESET)<br>Power-Save-Mode, monaural output is provided to VCOM voltage.<br>1: ON<br>S12: Select monaural input<br>0: OFF (RESET)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | S9                                                                       | : Select input signal of BEE | EΡ         |              |              |             |             |           |            |           |  |

| <ul> <li>S10: Select LINEOUT <ul> <li>0: OFF (RESET)</li> <li>Power-Save-Mode. LINEOUT is provided to VCOM_H voltage.</li> <li>1: ON</li> </ul> </li> <li>S11: Select monaural output (Mixing = (L+R)/2) <ul> <li>0: OFF (RESET)</li> <li>Power-Save-Mode, monaural output is provided to VCOM voltage.</li> <li>1: ON</li> </ul> </li> <li>S12: Select monaural input <ul> <li>0: OFF (RESET)</li> <li>0: OFF (RESET)</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                          | 0: OFF                       |            |              |              |             |             |           |            |           |  |

| 0: OFF (RESET)<br>Power-Save-Mode. LINEOUT is provided to VCOM_H voltage.<br>1: ON<br>S11: Select monaural output (Mixing = (L+R)/2)<br>0: OFF (RESET)<br>Power-Save-Mode, monaural output is provided to VCOM voltage.<br>1: ON<br>S12: Select monaural input<br>0: OFF (RESET)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                          | 1: ON (RE                    | SET)       |              |              |             |             |           |            |           |  |

| Power-Save-Mode. LINEOUT is provided to VCOM_H voltage.<br>1: ON<br>S11: Select monaural output (Mixing = (L+R)/2)<br>0: OFF (RESET)<br>Power-Save-Mode, monaural output is provided to VCOM voltage.<br>1: ON<br>S12: Select monaural input<br>0: OFF (RESET)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | S1                                                                       |                              |            |              |              |             |             |           |            |           |  |

| 1: ON<br>S11: Select monaural output (Mixing = (L+R)/2)<br>0: OFF (RESET)<br>Power-Save-Mode, monaural output is provided to VCOM voltage.<br>1: ON<br>S12: Select monaural input<br>0: OFF (RESET)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                          |                              | ,          |              |              |             |             |           |            |           |  |

| S11: Select monaural output (Mixing = (L+R)/2)<br>0: OFF (RESET)<br>Power-Save-Mode, monaural output is provided to VCOM voltage.<br>1: ON<br>S12: Select monaural input<br>0: OFF (RESET)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                          |                              | e-Mode. L  | INEOUT i     | s provided   | to VCOM     | _H voltage  | •         |            |           |  |

| 0: OFF (RESET)<br>Power-Save-Mode, monaural output is provided to VCOM voltage.<br>1: ON<br>S12: Select monaural input<br>0: OFF (RESET)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                          |                              |            |              |              |             |             |           |            |           |  |

| Power-Save-Mode, monaural output is provided to VCOM voltage.<br>1: ON<br>S12: Select monaural input<br>0: OFF (RESET)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | S1                                                                       |                              |            | (L+R)/2)     |              |             |             |           |            |           |  |

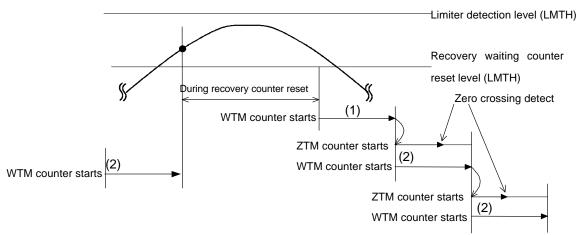

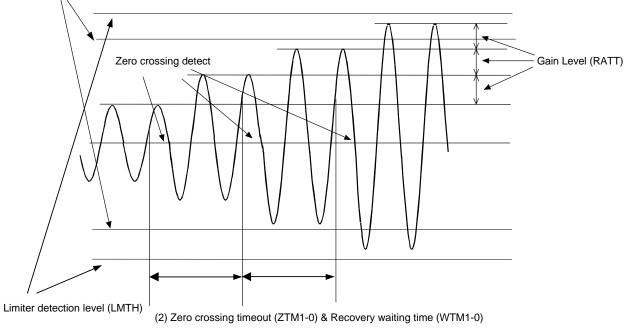

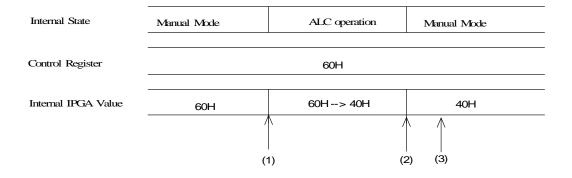

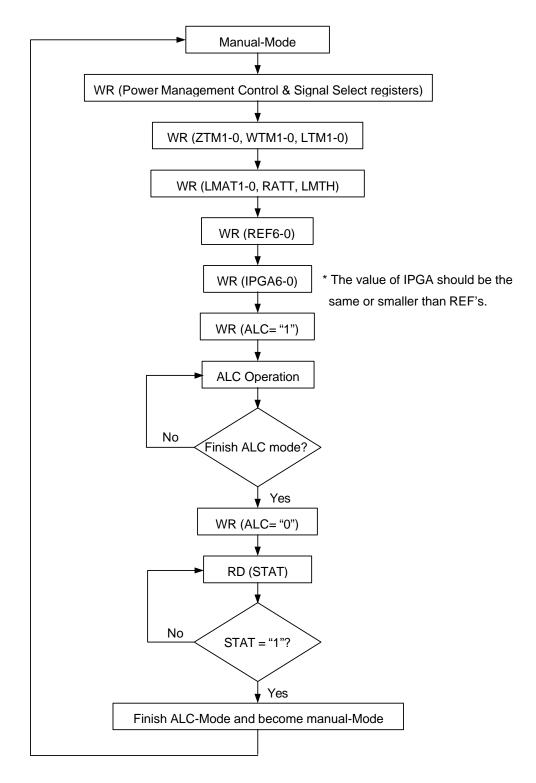

| 1: ON<br>S12: Select monaural input<br>0: OFF (RESET)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                          |                              | ,          |              |              |             |             |           |            |           |  |