# SANYO Semiconductors DATA SHEET

## LC01700PW — <sup>CMOS LSI</sup> FM tuner IC for VICS

#### Overview

LC01700PW is an FM tuner IC for vehicle-mounted VICS incorporating FM FE, IF, OP AMP, PLL. VICS tuner can be developed by one chip.

This IC can make up a small FM tuner module mounted for navigation.

#### Features

- Dedicated FM tuner IC for VICS in Japan and RDS in Europe.

- Variable gain LNA incorporated.

- A pulse counter detection method employed in the FM detection circuit. No adjustment necessary.

- Less number of external parts.

- BUS control tuner IC enabling control with I<sup>2</sup>C BUS.

- OP AMP provided to adjust the composite frequency level appropriate to VICS and RDS.

- 6Bit-ADC incorporated to enable digital output of S meter.

#### Functions

• FM-FE+IF+OP AMP+PLL

## Specifications

#### Absolute Maximum Ratings at Ta = 25°C

| Parameter                   | Symbol              | Conditions | Ratings     | Unit |

|-----------------------------|---------------------|------------|-------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max |            | 6           | V    |

| Maximum input voltage       | V <sub>DD</sub> H   |            | 6           | V    |

| Maximum output voltage      | V <sub>DD</sub> L   |            | 6           | V    |

| Allowable power dissipation | Pd max              | Ta ≤ 85°C  | 400         | mW   |

| Operating temperature       | Topr                |            | -40 to +85  | °C   |

| Storage temperature         | Tstg                |            | -50 to +150 | °C   |

Any and all SANYO Semiconductor Co.,Ltd. products described or contained herein are, with regard to "standard application", intended for the use as general electronics equipment (home appliances, AV equipment, communication device, office equipment, industrial equipment etc.). The products mentioned herein shall not be intended for use for any "special application" (medical equipment whose purpose is to sustain life, aerospace instrument, nuclear control device, burning appliances, transportation machine, traffic signal system, safety equipment etc.) that shall require extremely high level of reliability and can directly threaten human lives in case of failure or malfunction of the product or may cause harm to human bodies, nor shall they grant any guarantee thereof. If you should intend to use our products for applications outside the standard applications, please consult with us prior to the intended use. If there is no consultation or inquiry before the intended use, our customer shall be solely responsible for the use.

Specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

## SANYO Semiconductor Co., Ltd.

www.semiconductor-sanyo.com/network

#### **Operating supply voltage range** at $Ta = 25^{\circ}C$

| Parameter Symb             |                 | Conditions                                | Ratings    | Unit |

|----------------------------|-----------------|-------------------------------------------|------------|------|

| Recommended supply voltage | V <sub>DD</sub> | Not to exceed the absolute maximum rating | 4.5 to 5.5 | V    |

| Supply voltage range       | V <sub>DD</sub> |                                           | 5.0        | V    |

#### Serial interface voltage level

$\mathsf{V}_{DD}$  : Communications bus voltage

| -                                         |                 |                     |     |      |                    |      |  |

|-------------------------------------------|-----------------|---------------------|-----|------|--------------------|------|--|

| Parameter                                 | Symbol          | Quarket Quark's are |     | Unit |                    |      |  |

| Parameter                                 | Symbol          | Symbol Conditions   |     | typ  | max                | Unit |  |

| High level input voltage                  | VIH             |                     | 2.4 |      | V <sub>DD</sub>    | V    |  |

| Low level input voltage                   | VIL             |                     | 0.0 |      | 0.7                | V    |  |

| High level output voltage<br>(open drain) | VOH             |                     |     |      | V <sub>DD</sub> *  | V    |  |

| Low level output voltage<br>(open.drain)  | V <sub>OL</sub> |                     | 0.0 |      | 0.2V <sub>DD</sub> | V    |  |

\* High level output voltage causes the open drain to become the high-impedance state.

Since the drain is pulled up to  $V_{DD}$ , the voltage is equal to  $V_{DD}$ .

Electrical Characteristics at Ta = 25°C, unless otherwise specified. fc = 83MHz, Vin =  $60dB\mu VEMF$ , fm = 1kHz, Audio filter : HPF =100Hz, LPF = 15kHz

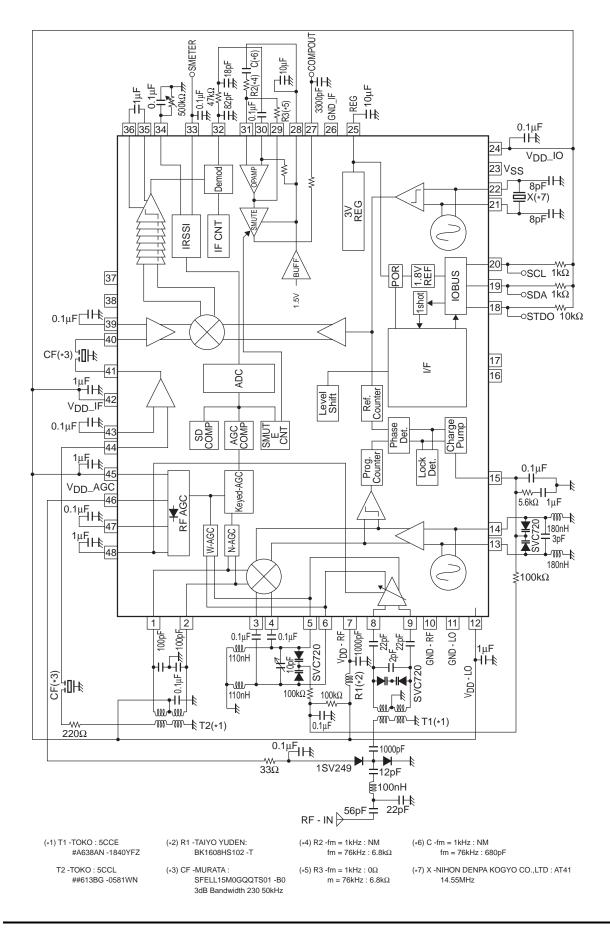

> Sample application circuit (Sample application circuit) look-up Register map <writing> look-up

| Parameter                   | Ci irrah al       | Conditions                                                                                                   |     | Ratings     |     |         |  |

|-----------------------------|-------------------|--------------------------------------------------------------------------------------------------------------|-----|-------------|-----|---------|--|

| Parameter                   | Symbol Conditions |                                                                                                              | min | min typ max |     | Unit    |  |

| S/N 30dB sensitivity        | SN30              | 22.5kHz dev, fm = 1kHz, S/N = 30dB input level                                                               |     | 15          | 20  | dBµVEMF |  |

| S/N 10dB sensitivity *1     | SN10              | 7.5kHz dev, fm = 76kHz, S/N = 10dB input level *2                                                            |     | 25          |     | dBµVEMF |  |

| Seek sensitivity (LO)       | Seek              | 22.5kHz dev, Vin = 40dB $\mu$ VEMF<br>Vsm = 2.0V adjustment<br>Pin 18 (STDO) Lo $\rightarrow$ Hi input level | 15  | 22          | 29  | dBμVEMF |  |

| S/N ratio 1                 | SN_1              | 22.5kHz dev, fm = 1kHz                                                                                       | 50  | 60          |     | dB      |  |

| S/N ratio 2                 | SN_2              | 7.5kHz dev, fm = 76kHz *2                                                                                    |     | 35          |     | dB      |  |

| Total harmonic distortion 1 | THD_1             | 22.5kHz dev, fm = 1kHz                                                                                       |     | 0.1         | 1   | %       |  |

| Total harmonic distortion 2 | THD_2             | 75.0kHz dev, fm = 1kHz                                                                                       |     | 0.2         | 1   | %       |  |

| Total harmonic distortion 3 | THD_3             | 22.5kHz dev, fm = 1kHz, Vin = 120dBµVEMF                                                                     |     | 0.1         | 1   | %       |  |

| Image removal ratio         | Image             | 22.5kHz dev, fm = 1kHz                                                                                       | 40  | 50          |     | dB      |  |

| AM suppression ratio        | AMR               | AM 30% mod                                                                                                   | 45  | 55          |     | dB      |  |

| Audio output level 1        | Vo_1              | 75.0kHz dev, fm = 1kHz                                                                                       | 170 | 270         | 430 | mVrms   |  |

| Audio output level 2        | Vo_2              | 7.5kHz dev, fm = 76kHz *2                                                                                    | 16  | 25          | 40  | mVrms   |  |

| Current drain               | IDD               | Input at no signal                                                                                           |     | 30          | 45  | mA      |  |

\*1 S/N = 10dB at BER = 1%

\*2 Audio filter : HPF = 100Hz, LPF = OFF

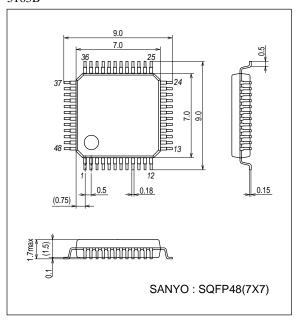

## **Package Dimensions**

unit : mm (typ) 3163B

## Sample Application Circuit (Block Diagram)

## **Pin Description**

| Pin No. | Pin Name            | Туре   | Description                                                                     |

|---------|---------------------|--------|---------------------------------------------------------------------------------|

| 1       | MIX_ON              | OUT    | 1stMIX signal output (-)                                                        |

| 2       | MIX_OP              | OUT    | 1stMIX signal output (+)                                                        |

| 3       | MIX_IP              | IN     | 1stMIX signal input (+)                                                         |

| 4       | MIX_IN              | IN     | 1stMIX signal input (-)                                                         |

| 5       | LNA_ON              | OUT    | LNA signal output (-)                                                           |

| 6       | LNA_OP              | OUT    | LNA signal output (+)                                                           |

| 7       | V <sub>DD_</sub> RF | POWER  | RF block power                                                                  |

| 8       | FM_IP               | IN     | FM signal input (+)                                                             |

| 9       | FM_IN               | IN     | FM signal input (-)                                                             |

| 10      | GND_RF              | GND    | RF block GND                                                                    |

| 11      | GND_LO              | GND    | LO block GND                                                                    |

| 12      | V <sub>DD</sub> _LO | POWER  | LO block power                                                                  |

| 13      | LOSC2               | IN/OUT | VCO resonant load pin 2                                                         |

| 14      | LOSC1               | IN/OUT | VCO resonant load pin 1                                                         |

| 15      | VT                  | OUT    | Charge pump output                                                              |

| 16      | NC1                 | NC     | NC                                                                              |

| 17      | NC2                 | NC     | NC                                                                              |

| 18      | STDO                | OUT    | Monitor output/reset detection output                                           |

| 19      | SDA                 | IN/OUT | Serial data I/O (I <sup>2</sup> C)                                              |

| 20      | SCL                 | IN     | Serial clock input (I <sup>2</sup> C)                                           |

| 21      | XOSC2               | IN/OUT | Crystal oscillator pin 2                                                        |

| 22      | XOSC1               | IN/OUT | Crystal oscillator pin 1                                                        |

| 23      | V <sub>SS</sub>     | GND    | Digital block GND                                                               |

| 24      | V <sub>DD</sub> _IO | POWER  | 5V power for interface                                                          |

| 25      | V <sub>DD</sub>     | OUT    | Digital block power (built-in regulator output)                                 |

| 26      | GND_IF              | GND    | IF block GND                                                                    |

| 27      | COMPOUT             | OUT    | Composite signal output                                                         |

| 28      | DETREF              | IN/OUT | FM detection signal amplifier reference voltage                                 |

| 29      | DETADJ              | OUT    | FM detection signal amplitude adjustment                                        |

| 30      | DETINP              | IN     | FM detection signal amplifier input (+)                                         |

| 31      | DETINN              | IN     | FM detection signal amplifier input (-)                                         |

| 32      | FDO                 | OUT    | FM detection circuit output                                                     |

| 33      | SMETER              | IN/OUT | S meter output                                                                  |

| 34      | CRSSI               | IN/OUT | Connection of smoothing capacitor for S-meter/S-meter output voltage adjustment |

| 35      | LIM2                | IN/OUT | Limiter offset canceling capacitor connection 2                                 |

| 36      | LIM1                | IN/OUT | Limiter offset canceling capacitor connection 1                                 |

| 37      | NC3                 | NC     | NC                                                                              |

| 38      | NC4                 | NC     | NC                                                                              |

| 39      | IF2nd_IN            | IN     | 2ndMIX signal input (-)                                                         |

| 40      | IF2nd_IP            | IN     | 2ndMIX signal input (+)                                                         |

| 41      | IF1stOUT            | OUT    | 1st IF amplifier signal output                                                  |

| 41      | V <sub>DD</sub> _IF | POWER  | IF block power                                                                  |

| 42      | IF1st IN            | IN     | 1st IF amplifier signal input (-)                                               |

| 43      | IF1st_IP            | IN     | 1st IF amplifier signal input (+)                                               |

| 44      | V <sub>DD</sub> AGC | POWER  | Pin diode AGC circuit power                                                     |

|         |                     | -      |                                                                                 |

| 46      | FMAGC               |        | FM pin diode driver output                                                      |

| 47      | CAGC                | IN/OUT | AGC circuit smoothing capacitor connection 2                                    |

## **Communications Specifications**

#### Communications specifications are shown below :

#### Serial Interface(I<sup>2</sup>C-bus) ; Serial interface (I<sup>2</sup>C-bus)

Send/receive is made via  $I^2C$ -bus that consists of two bus lines, each being a serial • data • line (SDA) and serial • clock • line (SCL). This bus enables 8-bit bi-directional serial data transmission at maximum 400kbit/s (fast mode). This is not compatible with the Hs mode.

#### 1. Terms used in I<sup>2</sup>C

The following terms are used in  $I^2C$ .

| Terms       | Description                                                                                   |

|-------------|-----------------------------------------------------------------------------------------------|

| Transmitter | Device to send data to the bus                                                                |

| Receiver    | Device to receive data from the bus                                                           |

| Master      | Device to start data transmission, to generate the clock signal, and to end data transmission |

| Slave       | Device whose address is designated by the master                                              |

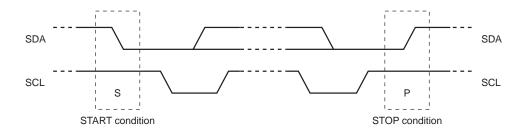

#### 2. "Start" and "Stop" conditions

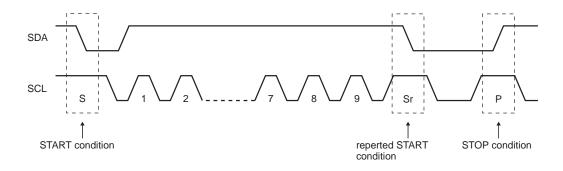

"Start" condition must be satisfied at start of data communications and "Stop" condition must be satisfied at end of communications.

The condition in which the SDA line changes from "H" to "L" with SCL at "H" is called the "Start" line. The condition in which the SDA line changes from "L" to "H" with SCL at "H" is called the "Stop" condition.

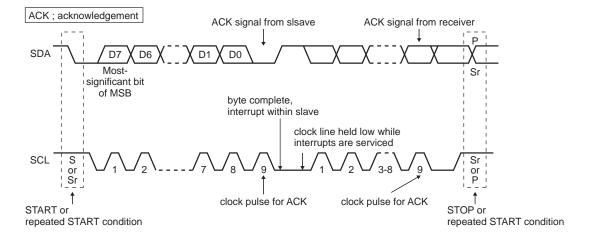

#### 3. Data transmission

The length of each byte output to the SDA line is always 8 bits. An acknowledge bit is always necessary after each byte, Data is transmitted sequentially from the most significant bit (MSB).

During data transfer, the slave address is transmitted after the "Start" condition (S). Data transfer is always ended by the "Stop" condition (P) generated by the master.

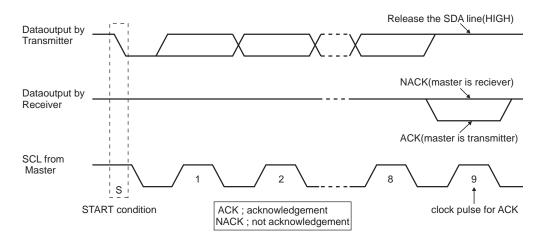

#### 4. Acknowledge (Confirmation of reception)

When the master generates the acknowledge clock pulse, the transmitter opens the SDA line (SDA line entering the "H" state). When the acknowledge clock pulse is in the "H" state, the receiver sets the SDA line to "L" each time it receives one byte (eight bits) of data. When the master functions as receiver, the master informs the end of data to the slave by omitting acknowledgement at the end of data sent from the slave.

#### 5. Software reset

After power ON, enter the signal as follows to avoid malfunction. If the communication is interrupted (microcomputer reset, etc.), entry of the following signal enables normal operation.

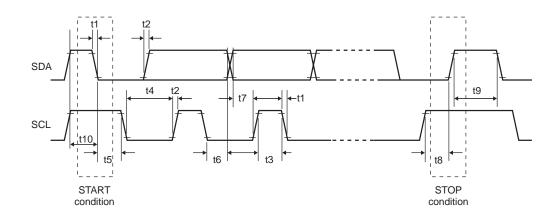

#### 6. Electrical Specification and Timing for I/O Stages

#### **Bus line characteristics**

|                                                |        | FAST-    | MODE |      | For                       |

|------------------------------------------------|--------|----------|------|------|---------------------------|

| Parameter                                      | Symbol | min      | max  | unit | SCL = 100kHz<br>(Example) |

| SCL clock frequency                            | fSCL   | -        | 400  | kHz  | 100                       |

| SDA, SCL fall time                             | t1     | 20+0.1Cb | 300  | ns   | -                         |

| SDA, SCL rise time                             | t2     | 20+0.1Cb | 300  | ns   | -                         |

| SCL "H" time                                   | t3     | 0.6      | -    | μs   | 3                         |

| SCL "L" time                                   | t4     | 1.3      | -    | μs   | 7                         |

| "Start" condition hold time                    | t5     | 0.6      | -    | μs   | 10                        |

| Data hold time For I <sup>2</sup> C bus device | t6     | 0.3      | -    | μs   | -                         |

| Data setup time                                | t7     | 0.1      | -    | μs   | 3                         |

| "Stop" condition setup time                    | t8     | 0.6      | -    | μs   | 10                        |

| "Stop"-"Start" bus free time                   | t9     | 1.3      | -    | μs   | 20                        |

| "Start" condition setup time                   | t10    | 0.6      | -    | μs   | -                         |

| Bus line capacitive load                       | Cb     | -        | 400  | pF   | -                         |

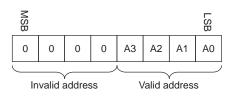

#### 7. Definition of each bit in one byte

#### 7-1. Slave address

The slave address consists of a fixed seven-bit address "1110010" unique to the chip and the eighth bit or a data direction bit (R/W): Send (Write) when this bit is "0" and Receive (Read) when this bit is "1".

| R/W   | BIT |

|-------|-----|

| READ  | 1   |

| WRITE | 0   |

#### 7-2. Register address

Since the total number of internal registers is 16, 4-bit data set on the MSB side becomes invalid.

#### 7-3. Register data

Each register data consists of eight bits.

| MSB |    |    |    |    |    |    | LSB |

|-----|----|----|----|----|----|----|-----|

| D7  | D6 | D5 | D4 | D3 | D2 | D1 | D0  |

#### 8. Command Format

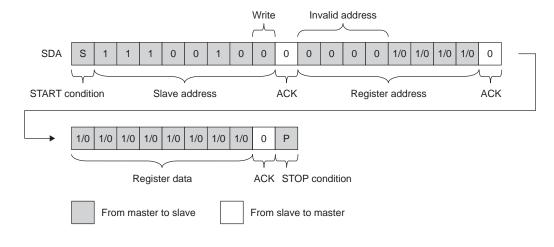

#### 8-1. Individual register • data writing

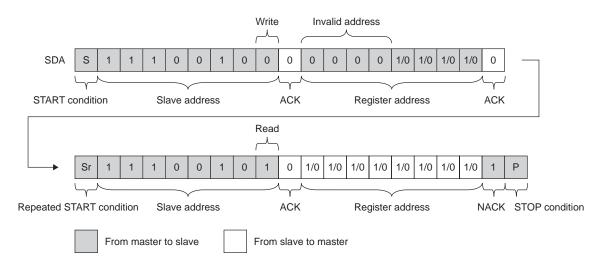

8-2. Individual register • data reading

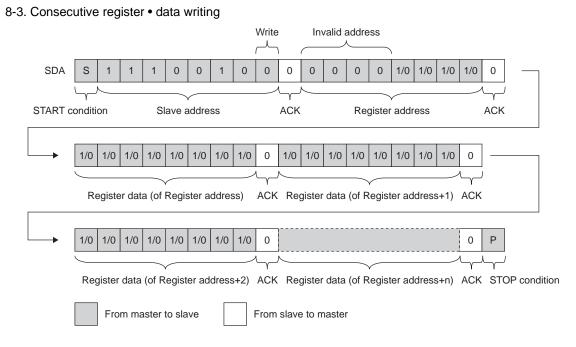

Continuous data transmission after transmission of initially-set address data of register • data writing sequence enables writing of data in the consecutive register • data area. In this case, the register • address increases by one address from the initially-set address of the sequence and continues increasing till the "Stop" condition (P) is generated.

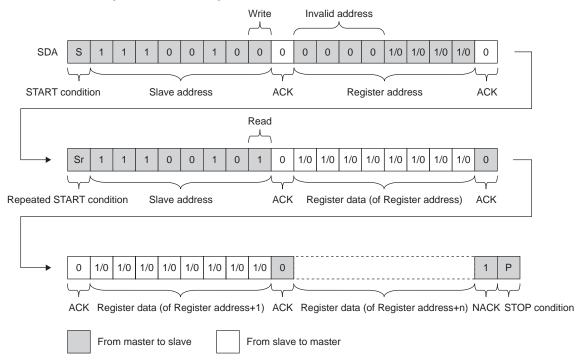

When the master returns ACK (0 data) after reading of the initial register • address • data of read sequence, the register • address increases by one address, enabling consecutive reading of data corresponding to each register address. If the master does not return ACK (0 data), the register address does not increase.

#### 8-4. Consecutive register • data reading

|                     |                                                                                                                                               | ap <writ< th=""><th></th><th></th><th>* Register value : Decima</th><th>1</th></writ<> |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                           | * Register value : Decima                                                    | 1                          |  |  |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------|--|--|--|

| Register<br>address | Bit                                                                                                                                           | Name                                                                                   | Functions                                                                                                                                                                                                                            | B                                                                                                                                                                                                                                                         | lit operation                                                                | Defau<br>value             |  |  |  |

| 0                   | 7                                                                                                                                             | PE                                                                                     | Power enable (all blocks)                                                                                                                                                                                                            | 0:OFF                                                                                                                                                                                                                                                     | 1:ON                                                                         | 1                          |  |  |  |

|                     | 6                                                                                                                                             | SWSTD                                                                                  | Selection of digital signal monitor pin output                                                                                                                                                                                       | 0:RSTDET 1:SD                                                                                                                                                                                                                                             | 2:LDO 3:KAGC                                                                 | 1                          |  |  |  |

|                     | 5                                                                                                                                             |                                                                                        | /reset detection output                                                                                                                                                                                                              | 4:IFCNT_CLK                                                                                                                                                                                                                                               | 5:RSSI_CLK                                                                   |                            |  |  |  |

|                     | 4                                                                                                                                             |                                                                                        |                                                                                                                                                                                                                                      | 6:PROCNTR                                                                                                                                                                                                                                                 | 7:REFCNTR                                                                    |                            |  |  |  |

|                     | 3                                                                                                                                             | LOBIAS                                                                                 | Oscillation level adjustment                                                                                                                                                                                                         | 0:Oscillation level sma                                                                                                                                                                                                                                   | all                                                                          | 0                          |  |  |  |

|                     | 2                                                                                                                                             |                                                                                        |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                           |                                                                              |                            |  |  |  |

|                     | 1                                                                                                                                             |                                                                                        |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                           |                                                                              |                            |  |  |  |

|                     | 0                                                                                                                                             |                                                                                        |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                           | 15:Oscillation level large                                                   |                            |  |  |  |

| 1                   | 7                                                                                                                                             | SDREG                                                                                  | LO/DX changeover (seek determination level                                                                                                                                                                                           | 15:10dBμV                                                                                                                                                                                                                                                 |                                                                              | 25                         |  |  |  |

|                     | 6                                                                                                                                             |                                                                                        | adjustment)                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                           |                                                                              |                            |  |  |  |

|                     | 5                                                                                                                                             |                                                                                        |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                           | *1dB STEP                                                                    |                            |  |  |  |

|                     | 4                                                                                                                                             |                                                                                        |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                           |                                                                              |                            |  |  |  |

|                     | 3                                                                                                                                             |                                                                                        |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                           | 55:50dBµV                                                                    |                            |  |  |  |

|                     | 2                                                                                                                                             |                                                                                        |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                           | (As for value reference value)                                               |                            |  |  |  |

|                     | 1                                                                                                                                             | CTE                                                                                    | 2ndIF count measurement start control                                                                                                                                                                                                | 0:OFF                                                                                                                                                                                                                                                     | 1:ON (automatically OFF)                                                     | 0                          |  |  |  |

|                     | 0                                                                                                                                             | RSTDET                                                                                 | Initial register writing for reset detection                                                                                                                                                                                         | 0:Reset                                                                                                                                                                                                                                                   | 1:Normal                                                                     | 1                          |  |  |  |

| 2                   | 7                                                                                                                                             | PCNT                                                                                   | PLL synthesizer program data                                                                                                                                                                                                         | 0:LSB                                                                                                                                                                                                                                                     |                                                                              |                            |  |  |  |

|                     | 6                                                                                                                                             |                                                                                        |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                           |                                                                              |                            |  |  |  |

|                     | 5                                                                                                                                             |                                                                                        |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                           |                                                                              |                            |  |  |  |

| 3                   | 4                                                                                                                                             |                                                                                        |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                           |                                                                              |                            |  |  |  |

|                     | 3                                                                                                                                             |                                                                                        | PCNT – Receiver frequency + 1stl frequency (upper local setting)                                                                                                                                                                     |                                                                                                                                                                                                                                                           |                                                                              |                            |  |  |  |

|                     | 2                                                                                                                                             |                                                                                        | $PCNT = \frac{\text{Receiver frequency} + 1\text{stl frequency}}{50\text{kHz}} (\text{upperlocal setting})$                                                                                                                          |                                                                                                                                                                                                                                                           |                                                                              |                            |  |  |  |

|                     | 1                                                                                                                                             |                                                                                        |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                           |                                                                              |                            |  |  |  |

|                     | 0                                                                                                                                             |                                                                                        | $PCNT = \frac{\text{Receiver frequ}}{1}$                                                                                                                                                                                             | ency + 1stl frequenc                                                                                                                                                                                                                                      | v                                                                            |                            |  |  |  |

| 3                   | 7                                                                                                                                             |                                                                                        |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                           |                                                                              |                            |  |  |  |

|                     |                                                                                                                                               |                                                                                        | PCN1 =                                                                                                                                                                                                                               | 50kHz                                                                                                                                                                                                                                                     | (lowerlocal setting)                                                         |                            |  |  |  |

|                     | 6                                                                                                                                             |                                                                                        | PCN1 =                                                                                                                                                                                                                               | 50kHz                                                                                                                                                                                                                                                     | (lowerlocal setting)                                                         |                            |  |  |  |

|                     | 5                                                                                                                                             |                                                                                        | PCN1 =                                                                                                                                                                                                                               | 50kHz                                                                                                                                                                                                                                                     | (lowerlocal setting)                                                         |                            |  |  |  |

|                     | 5<br>4                                                                                                                                        |                                                                                        | PCN1 =                                                                                                                                                                                                                               | 50kHz                                                                                                                                                                                                                                                     | (lowerlocal setting)                                                         |                            |  |  |  |

|                     | 5<br>4<br>3                                                                                                                                   |                                                                                        | PCN1 =                                                                                                                                                                                                                               | 50kHz                                                                                                                                                                                                                                                     | (lowerlocal setting)                                                         |                            |  |  |  |

|                     | 5<br>4<br>3<br>2                                                                                                                              |                                                                                        | PCN1 =                                                                                                                                                                                                                               | 50kHz                                                                                                                                                                                                                                                     | (lowerlocal setting)                                                         |                            |  |  |  |

|                     | 5<br>4<br>3<br>2<br>1                                                                                                                         |                                                                                        | PCN1 =                                                                                                                                                                                                                               | 50kHz                                                                                                                                                                                                                                                     | (lowerlocal setting)                                                         |                            |  |  |  |

| - 4                 | 5<br>4<br>3<br>2<br>1<br>0                                                                                                                    | ot                                                                                     |                                                                                                                                                                                                                                      | 50kHz                                                                                                                                                                                                                                                     |                                                                              |                            |  |  |  |

| 4                   | 5<br>4<br>3<br>2<br>1<br>0<br>7                                                                                                               | GT                                                                                     | PCN1 =                                                                                                                                                                                                                               | 0:4ms                                                                                                                                                                                                                                                     | 1:8ms                                                                        | 0                          |  |  |  |

| 4                   | 5<br>4<br>3<br>2<br>1<br>0<br>7<br>6                                                                                                          |                                                                                        | 2ndIF count time selection                                                                                                                                                                                                           | 0:4ms<br>2:32ms                                                                                                                                                                                                                                           | 1:8ms<br>3:64ms                                                              |                            |  |  |  |

| 4                   | 5<br>4<br>3<br>2<br>1<br>0<br>7<br>6<br>5                                                                                                     | GT                                                                                     |                                                                                                                                                                                                                                      | 0:4ms<br>2:32ms<br>0:10.95MHz                                                                                                                                                                                                                             | 1:8ms<br>3:64ms<br>1:11.25MHz                                                | 0                          |  |  |  |

| 4                   | 5<br>4<br>3<br>2<br>1<br>0<br>7<br>6<br>5<br>4                                                                                                |                                                                                        | 2ndIF count time selection                                                                                                                                                                                                           | 0:4ms<br>2:32ms<br>0:10.95MHz<br>2:14.55MHz                                                                                                                                                                                                               | 1:8ms<br>3:64ms<br>1:11.25MHz<br>3:14.75MHz                                  |                            |  |  |  |

| 4                   | 5<br>4<br>3<br>2<br>1<br>0<br>7<br>6<br>5<br>4<br>3                                                                                           | CSEL                                                                                   | 2ndIF count time selection<br>PLL master clock signal selection                                                                                                                                                                      | 0:4ms<br>2:32ms<br>0:10.95MHz<br>2:14.55MHz<br>4:21.15MHz                                                                                                                                                                                                 | 1:8ms<br>3:64ms<br>1:11.25MHz                                                | 2                          |  |  |  |

| 4                   | 5<br>4<br>3<br>2<br>1<br>0<br>7<br>6<br>5<br>4<br>3<br>2                                                                                      |                                                                                        | 2ndIF count time selection                                                                                                                                                                                                           | 0:4ms<br>2:32ms<br>0:10.95MHz<br>2:14.55MHz                                                                                                                                                                                                               | 1:8ms<br>3:64ms<br>1:11.25MHz<br>3:14.75MHz                                  |                            |  |  |  |

| 4                   | 5<br>4<br>3<br>2<br>1<br>0<br>7<br>6<br>5<br>4<br>3                                                                                           | CSEL                                                                                   | 2ndIF count time selection<br>PLL master clock signal selection                                                                                                                                                                      | 0:4ms<br>2:32ms<br>0:10.95MHz<br>2:14.55MHz<br>4:21.15MHz                                                                                                                                                                                                 | 1:8ms<br>3:64ms<br>1:11.25MHz<br>3:14.75MHz                                  | 2                          |  |  |  |

| 4                   | 5<br>4<br>3<br>2<br>1<br>0<br>7<br>6<br>5<br>4<br>3<br>2<br>1                                                                                 | CSEL                                                                                   | 2ndIF count time selection<br>PLL master clock signal selection                                                                                                                                                                      | 0:4ms<br>2:32ms<br>0:10.95MHz<br>2:14.55MHz<br>4:21.15MHz                                                                                                                                                                                                 | 1:8ms<br>3:64ms<br>1:11.25MHz<br>3:14.75MHz                                  | 2                          |  |  |  |

|                     | 5<br>4<br>3<br>2<br>1<br>0<br>7<br>6<br>5<br>4<br>3<br>2<br>1<br>0<br>0                                                                       | CSEL                                                                                   | 2ndIF count time selection         PLL master clock signal selection         PLL comparative frequency setting                                                                                                                       | 0:4ms         2:32ms         0:10.95MHz         2:14.55MHz         4:21.15MHz         0:50kHz                                                                                                                                                             | 1:8ms<br>3:64ms<br>1:11.25MHz<br>3:14.75MHz                                  | 2                          |  |  |  |

|                     | 5<br>4<br>3<br>2<br>1<br>0<br>7<br>6<br>5<br>4<br>3<br>2<br>1<br>0<br>7                                                                       | CSEL<br>FSEL<br>RSEL                                                                   | 2ndIF count time selection         PLL master clock signal selection         PLL comparative frequency setting         PLL REF reference frequency selection                                                                         | 50kHz         0:4ms         2:32ms         0:10.95MHz         2:14.55MHz         4:21.15MHz         0:50kHz         0:50kHz                                                                                                                               | 1:8ms<br>3:64ms<br>1:11.25MHz<br>3:14.75MHz                                  | 2 0 0                      |  |  |  |

|                     | 5<br>4<br>3<br>2<br>1<br>0<br>7<br>6<br>5<br>4<br>3<br>2<br>1<br>0<br>7<br>6                                                                  | CSEL<br>FSEL<br>RSEL<br>ADCLK                                                          | 2ndIF count time selection         PLL master clock signal selection         PLL comparative frequency setting         PLL REF reference frequency selection         RSSIADC clock frequency changeover                              | 0:4ms         2:32ms         0:10.95MHz         2:14.55MHz         4:21.15MHz         0:50kHz         0:50kHz         0:50kHz         0:800kHz                                                                                                            | 1:8ms<br>3:64ms<br>1:11.25MHz<br>3:14.75MHz<br>5:21.45MHz                    | 2<br>0<br>0<br>0           |  |  |  |

|                     | 5<br>4<br>3<br>2<br>1<br>0<br>7<br>6<br>5<br>4<br>3<br>2<br>1<br>0<br>7<br>6<br>5<br>5<br>5<br>5<br>5                                         | CSEL<br>FSEL<br>RSEL<br>ADCLK                                                          | 2ndIF count time selection         PLL master clock signal selection         PLL comparative frequency setting         PLL REF reference frequency selection         RSSIADC clock frequency changeover                              | 50kHz         0:4ms         2:32ms         0:10.95MHz         2:14.55MHz         4:21.15MHz         0:50kHz         0:50kHz         0:50kHz         0:50kHz         0:50kHz         0:50kHz         0:50kHz         0:50kHz         0:50kHz         0:0ns | 1:8ms<br>3:64ms<br>1:11.25MHz<br>3:14.75MHz<br>5:21.45MHz<br>1:2ns           | 2<br>0<br>0<br>0           |  |  |  |

|                     | 5<br>4<br>3<br>2<br>1<br>0<br>7<br>6<br>5<br>4<br>3<br>2<br>1<br>0<br>7<br>6<br>5<br>5<br>4<br>4                                              | CSEL<br>FSEL<br>RSEL<br>ADCLK<br>DZSEL                                                 | 2ndIF count time selection         PLL master clock signal selection         PLL comparative frequency setting         PLL REF reference frequency selection         RSSIADC clock frequency changeover         Dead zone adjustment | 50kHz         0:4ms         2:32ms         0:10.95MHz         2:14.55MHz         4:21.15MHz         0:50kHz         0:50kHz         0:50kHz         0:50kHz         0:50kHz         0:50kHz         0:50kHz         0:50kHz         0:0ns         2:10ns  | 1:8ms<br>3:64ms<br>1:11.25MHz<br>3:14.75MHz<br>5:21.45MHz<br>1:2ns           | 2<br>0<br>0<br>0<br>0<br>0 |  |  |  |

|                     | 5<br>4<br>3<br>2<br>1<br>0<br>7<br>6<br>5<br>4<br>3<br>2<br>1<br>0<br>7<br>6<br>5<br>4<br>3<br>3<br>2<br>1<br>0<br>7<br>6<br>5<br>4<br>3<br>3 | CSEL<br>FSEL<br>RSEL<br>ADCLK<br>DZSEL                                                 | 2ndIF count time selection         PLL master clock signal selection         PLL comparative frequency setting         PLL REF reference frequency selection         RSSIADC clock frequency changeover         Dead zone adjustment | 50kHz         0:4ms         2:32ms         0:10.95MHz         2:14.55MHz         4:21.15MHz         0:50kHz         0:50kHz         0:50kHz         0:50kHz         0:50kHz         0:50kHz         0:50kHz         0:50kHz         0:0ns         2:10ns  | 1:8ms<br>3:64ms<br>1:11.25MHz<br>3:14.75MHz<br>5:21.45MHz<br>1:2ns<br>3:20ns | 2<br>0<br>0<br>0<br>0<br>0 |  |  |  |

| Register | · 1 | eceding page. |                                                                |                            | * Register value : Decima      | Defau |

|----------|-----|---------------|----------------------------------------------------------------|----------------------------|--------------------------------|-------|

| address  | Bit | Name          | Functions                                                      | Bit                        | operation                      | value |

| 6        | 7   |               |                                                                | 0:Fixing                   |                                | 0     |

|          | 6   | PEVCO         | Power enable (VCO)                                             | 0:OFF                      | 1:ON                           | 1     |

|          | 5   | BGRTEST       | BGR (RFAGC circuit) inspection mode<br>changeover              | 0:OFF                      | 1:ON                           | 0     |

|          | 4   |               |                                                                | 0:Fixing                   |                                | 0     |

|          | 3   | SMTREG        | Softmute start point adjustment                                | 0:Softmute function OFF    |                                | 10    |

|          | 2   |               |                                                                | 1:-4dBµV                   | *2dB STEP                      |       |

|          | 1   |               |                                                                |                            | 15:24dBμV                      |       |

|          | 0   |               |                                                                |                            | (As for value reference value) |       |

| 7        | 7   | RSSIGAIN      | RSSI detection sensitivity adjustment                          | 0:31mV/dB                  | *1mV/dB STEP                   | 4     |

|          | 6   |               | *RSSI output gradient                                          |                            | 7:38mV/dB                      |       |

|          | 5   |               |                                                                |                            | (As for value reference value) |       |

| 4        | 4   | RSSITMP       | RSSI detection temperature characteristics<br>adjustment       | 0:4dB                      | *0.5dB STEP                    | 3     |

|          | 3   |               | *Front-end circuit temperature characteristics<br>compensation |                            | 7:7.5dB                        |       |

|          | 2   |               |                                                                |                            | (As for value reference value) |       |

|          | 1   |               |                                                                | 0:Fixing                   |                                | 0     |

|          | 0   |               |                                                                |                            |                                |       |

| 8        | 7   | WAGC          | W_AGC sensitivity adjustment                                   | 0:Sensitivity low          | *1.1dB STEP                    | 15    |

|          | 6   |               |                                                                |                            |                                |       |

|          | 5   |               |                                                                |                            |                                |       |

|          | 4   |               |                                                                |                            | 15:Sensitivity high            |       |

|          | 3   | NAGC          | N_AGC sensitivity adjustment                                   | 0:Sensitivity low          | *1.1dB STEP                    | 6     |

|          | 2   |               |                                                                |                            |                                |       |

|          | 1   |               |                                                                |                            |                                |       |

|          | 0   |               |                                                                |                            | 15:Sensitivity high            |       |

| 9        | 7   | KAGC          | Keyed-AGC judgment level adjustment                            | 0:-3dBµV                   |                                | 6     |

|          | 6   |               |                                                                |                            | *2dB STEP                      |       |

|          | 5   |               |                                                                |                            | 15:27dBμV                      |       |

|          | 4   |               |                                                                |                            | (As for value reference value) |       |

|          | 3   | WAGCSW        | W_AGC_ON/OFF                                                   | 0:OFF                      | 1:ON                           | 1     |

|          | 2   | NAGCSW        | N_AGC_ON/OFF                                                   | 0:OFF                      | 1:ON                           | 1     |

|          | 1   | ATTAGCSW      | ATT_AGC_ON/OFF                                                 | 0:OFF                      | 1:ON                           | 1     |

|          | 0   | LNAAGCSW      | LNA_AGC_ON/OFF                                                 | 0:OFF                      | 1:ON                           | 1     |

| 10       | 7   | KAGCSW        | Keyed-AGC_ON/OFF                                               | 0:OFF                      | 1:ON                           | 0     |

|          | 6   | WKAGCSW       | Keyed-W_AGC sensitivity changeover                             | 0:No sensitivity change    | 1:-10dB sensitivity change     | 0     |

|          | 5   | LNAG          | LNA gain adjustment                                            | 0:17dB                     | 1:19dB                         | 3     |

|          | 4   |               |                                                                | 2:21dB                     | 3:23dB                         |       |

|          | 3   | MIXG          | 1stMIX gain adjustment                                         | 0:-0.2dB                   | 1:2.8dB                        | 3     |

|          | 2   |               |                                                                | 2:4.5dB                    | 3:5.4dB                        |       |

|          | 1   | IFAG          | 1stIFA gain adjustment                                         | 0:7dB                      | 1:10dB                         | 3     |

| 14       | 0   |               |                                                                | 2:13dB                     | 3:16dB                         |       |

| 11       | 7   |               |                                                                | 0:Fixing                   |                                | 0     |

|          | 6   |               |                                                                |                            |                                |       |

|          | 5   | VORCARI       |                                                                |                            | mall                           |       |

|          | 4   | XOSCADJ       | Crystal oscillation level adjustment                           | 0:oscillation allowance, s | amail                          | 0     |

|          | 3   |               |                                                                |                            | 7. applieting allowers a       |       |

|          | 2   |               |                                                                | 0. Fining                  | 7:oscillation allowance, large |       |

| Ļ        | 1   |               |                                                                | 0:Fixing<br>0:Fixing       |                                | 0     |

| Continued f         | from pr | receding page. |                                   |                  | * Regis        | ster value : Decim | al notatior |

|---------------------|---------|----------------|-----------------------------------|------------------|----------------|--------------------|-------------|

| Register<br>address | Bit     | Name           | Functions                         | E                | Bit operation  |                    | Default     |

| 12                  | 7       | RMXG           | Composite output level adjustment | 0:3.1dB 1:3.7    | dB 2:4.4dB     | 3:5.2dB            | value<br>0  |

|                     | 6       | -              |                                   |                  |                |                    | -           |

|                     | 5       |                |                                   | 4:6.0dB 5:6.9    | dB 6:8.0dB     | 9:9.1dB            |             |

|                     | 4       | DEMODR         | Detection output level adjustment | 0:106mVrm 1:119m | /rms 2:151mVrr | ns 3:167mVrms      | 7           |

|                     | 3       |                |                                   | 4:212mVrm 5:230m | /rms 6:276mVrn | ns 7:297mVrms      |             |

|                     | 2       |                |                                   |                  | (As for value  | reference value)   |             |

|                     | 1       | PERF           | Power enable (RF block)           | 0:OFF            | 1:ON           |                    | 1           |

|                     | 0       | PEIF           | Power enable (IF block)           | 0:OFF            | 1:ON           |                    | 1           |

| 13                  | 7       | PEDEM          | Power enable (LIM/DEMOD)          | 0:OFF            | 1:ON           |                    | 1           |

|                     | 6       | PEAMP          | Power enable (audio amplifier)    | 0:OFF            | 1:ON           |                    | 1           |

|                     | 5       | PEXOSC         | Power enable (XOSC)               | 0:OFF            | 1:ON           |                    | 1           |

|                     | 4       | PELNA          | Power enable (LNA)                | 0:OFF            | 1:ON           |                    | 1           |

|                     | 3       | PELO1          | Power enable (LO block_VCOetc)    | 0:OFF            | 1:ON           |                    | 1           |

|                     | 2       | PELO2          | Power enable (LO block_LOBUFetc)  | 0:OFF            | 1:ON           |                    | 1           |

|                     | 1       | PEREFCNT       | Power enable (REF counter)        | 0:OFF            | 1:ON           |                    | 1           |

|                     | 0       | PERFAGC        | Power enable (RFAGC block)        | 0:OFF            | 1:ON           |                    | 1           |

| 14                  | 7       |                |                                   |                  |                |                    |             |

|                     | 6       |                |                                   |                  |                |                    |             |

|                     | 5       |                |                                   |                  |                |                    |             |

|                     | 4       |                |                                   |                  |                |                    |             |

|                     | 3       |                |                                   |                  |                |                    |             |

| l                   | 2       |                |                                   |                  |                |                    |             |

|                     | 1       |                |                                   |                  |                |                    |             |

|                     | 0       |                |                                   |                  |                |                    |             |

| 15                  | 7       |                |                                   |                  |                |                    |             |

|                     | 6       |                |                                   |                  |                |                    |             |

|                     | 5       |                |                                   |                  |                |                    |             |

|                     | 4       |                |                                   |                  |                |                    |             |

|                     | 3       |                |                                   |                  |                |                    |             |

|                     | 2       |                |                                   |                  |                |                    |             |

|                     | 1       |                |                                   |                  |                |                    |             |

|                     | 0       |                |                                   |                  |                |                    |             |

| Register<br>address         Bit         Name         Functions         Bit operation                              | Defau                 |

|-------------------------------------------------------------------------------------------------------------------|-----------------------|

|                                                                                                                   |                       |