# HS-22620RH

## August 1999 File Number 4349.1

## Rad Hard Dual, Wideband, High Input Impedance Uncompensated Operational Amplifier

Data Sheet

The HS-22620RH is a radiation hardened, dual bipolar operational amplifier that features very high input impedance coupled with wideband AC performance. The high resistance of the input stage is complemented by low offset voltage (6mV Max at 25°C) and low bias current (50nA Max at 25°C) to facilitate accurate signal processing. Offset voltage can be reduced further by means of an external nulling potentiometer. The stable closed loop gains greater than 10, the 20V/µs minimum slew rate at 25°C and the 80kV/V minimum open loop gain at 25°C, enable the HS-22620RH to perform high gain amplification of very fast, wideband signals. These dynamic characteristics, coupled with fast settling times, make these amplifiers ideally suited to pulse amplification designs as well as high frequency or video applications. The frequency response of the amplifier can be tailored to exact design requirements by means of an external bandwidth control capacitor.

#### Specifications for Rad Hard QML devices are controlled by the Defense Supply Center in Columbus (DSCC). The SMD numbers listed here must be used when ordering.

Detailed Electrical Specifications for these devices are contained in SMD 5962-97512. A "hot-link" is provided on our homepage for downloading. www.intersil.com/spacedefense/space.asp

## Features

- Electrically Screened to SMD # 5962-97512

- QML Qualified per MIL-PRF-38535 Requirements

- High Slew Rate ...... 20V/μs (Min)

- Low Input Bias Current...... 50nA (Max)

- Low Input Offset Voltage ......6mV (Max)

- Wide Gain Bandwidth Product  $(A_V \ge 10) \dots .100$  MHz (Typ)

- Output Short Circuit Protection

## Applications

- · Video and RF Amplifiers

- Pulse Amplifiers

- High-Q Active Filters

- High Speed Comparators

## **Ordering Information**

| ORDERING NUMBER   | INTERNAL<br>MKT. NUMBER | TEMP. RANGE<br>( <sup>o</sup> C) |

|-------------------|-------------------------|----------------------------------|

| 5962F9751201V9A   | HS0-22620RH-Q           | 25                               |

| 5962F9751201VXC   | HS9-22620RH-Q           | -55 to 125                       |

| HS9-22620RH/PROTO | HS9-22620RH/PROTO       | -55 to 125                       |

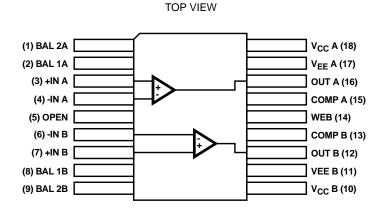

## Pinout

HS-22620RH (FLATPACK)

NOTE: Refer to SMD, Figure 1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. 1-888-INTERSIL or 321-724-7143 | Copyright © Intersil Corporation 1999

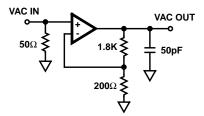

## Test Circuits and Waveforms

NOTE: Includes stray capacitances.

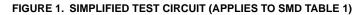

#### FIGURE 2. SLEW RATE WAVEFORM

NOTE: Measured on both positive and negative transitions. Capacitance at Compensation pin should be minimized.

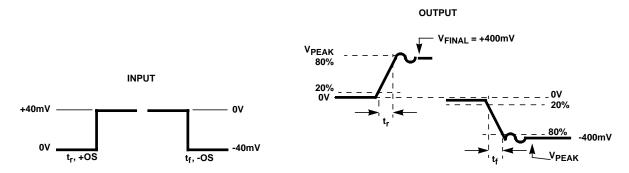

FIGURE 3. OVERSHOOT, RISE AND FALL TIME WAVEFORMS

2

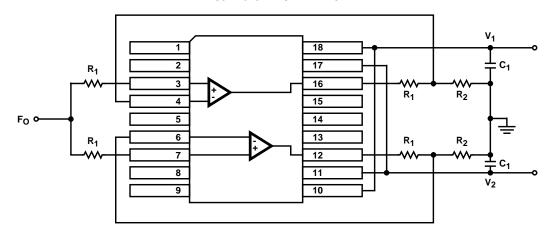

## Dynamic Burn-In Circuit

```

HS9-22620RH-Q FLATPACK

```

NOTES:

- 1.  $V_1 = +15V \pm 0.5V$ .

- 2.  $V_2 = -15V \pm 0.5V$ .

- 3.  $R_1 = 2.2k\Omega$ , 1/8W min (5%).

- 4.  $R_2 = 50\Omega$ , 1/8W min (2%).

- 5.  $C_1~$  = 0.1µF, 10%, one cap per V per socket.

- 6.  $F_0 = 10 \text{kHz}, \pm 10\%, 50\%$  duty cycle.

- 7.  $V_{IH}$  = +100mV ±10mV.

- 8.  $V_{IL}$  = -100mV ±10mV.

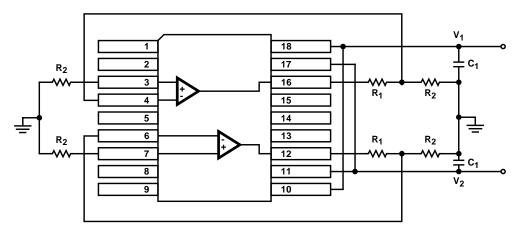

## Radiation Exposure Circuit

NOTES:

- 9.  $V_1 = +15V \pm 0.5V$ .

- 10.  $V_2 = -15V \pm 0.5V$ .

- 11.  $R_1 = 2.2k\Omega$ , 1/8W min (5%).

- 12.  $R_2 = 50\Omega$ , 1/8W min (2%).

- 13.  $C_1 = 0.1 \mu F$ , ±10%, one cap per V per socket.

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com

## **Die Characteristics**

#### DIE DIMENSIONS:

145 mils x 116 mils x 19 mils  $\pm 1$  mil 3670µm x 2950µm x 483µm  $\pm 25.4\mu m$

#### **INTERFACE MATERIALS:**

#### **Glassivation:**

Type: Nitride (S13N4) over Silox (SIO2, 5% Phos.) Silox Thickness: 12kÅ ±2kÅ Nitride Thickness: 3.5kÅ ±1.5kÅ

#### **Top Metallization:**

Type: Al, 1% Cu Thickness: 14kÅ ±2kÅ

#### Substrate:

Bipolar Bonded Wafer (EBHF)

#### **Backside Finish:**

Silicon

## Metallization Mask Layout

#### **ASSEMBLY RELATED INFORMATION:**

#### Substrate Potential (Powered Up):

Unbiased Silicon (WEB pad provided for substrate tie-off.)

### ADDITIONAL INFORMATION:

#### Worst Case Current Density:

<2 x 10<sup>5</sup> A/cm<sup>2</sup>

Transistor Count:

184

4