#### Description

The E7804 is a quad channel, monolithic ATE pin electronics solution manufactured in a high-performance BiCMOS process.

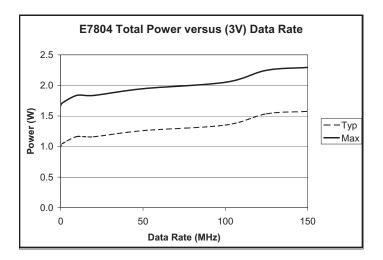

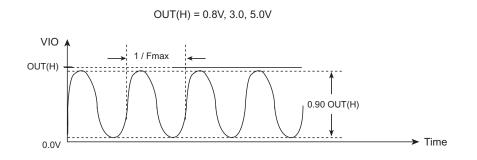

The E7804 operates up to 133 MHz with up to 3V signals, and 100 MHz with 5V signals.

Each channel has a three-statable driver capable of generating 5.4V swings over a –0.2V, +5.2V range. Drivers have independent high and low input levels that are buffered internally. Drivers feature a self-calibrating source impedance, programmable in the range  $48\Omega$  to  $110\Omega$ . The source impedance of all drivers matches R<sub>EREF</sub>/100, where R<sub>EREF</sub> is the external reference resistor. Each channel's dual comparator has a range of –2.0V to +5.5V.

A channel's driver and comparators are connected internally via high voltage switches to the VIO pin. These switches provide a means to disconnect the driver and comparator from the VIO pin.

The E7804 contains an independent network of high voltage switches intended to connect an external Parametric Measurement Unit (EPMU) to any channel (or channels) output on the channel's POUT pin. The EPMU can have a range of -4.75V to +9.75V, up to  $\pm40$  mA. Typically, a channel's VIO and POUT pins are connected together externally.

Each channel contains a continuity test circuit (CTC) with a switch to connect it to the channel's POUT pin. This circuit forces a current up to  $-250 \mu$ A, and tests the resulting voltage with a 0 to -2V programmable limit. The result is tested by the channel's comparator.

Each channel contains a  $2K\Omega$  pull-up resistor with a switch to connect to the channel's POUT pin.

The channel's function and connections are programmed using a serial interface. An individual channel's function can be programmed, or a function of any set of channels (of multiple E7804s) can be programmed in parallel where each channel can belong to none, one, or more (up to 8) sets.

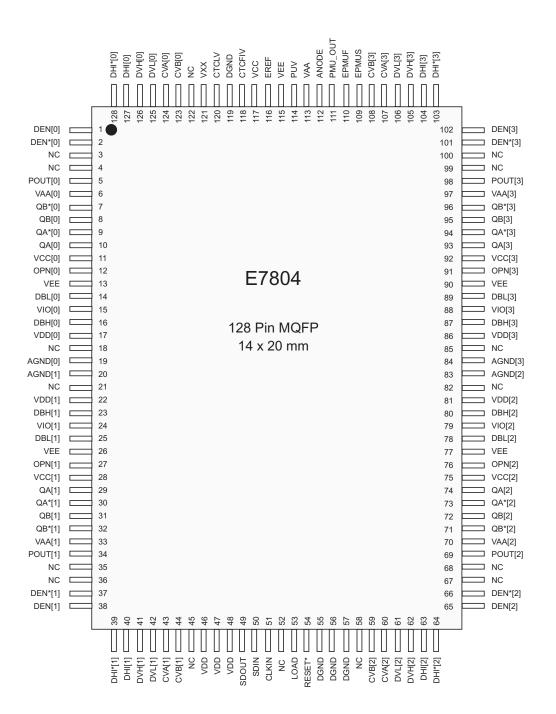

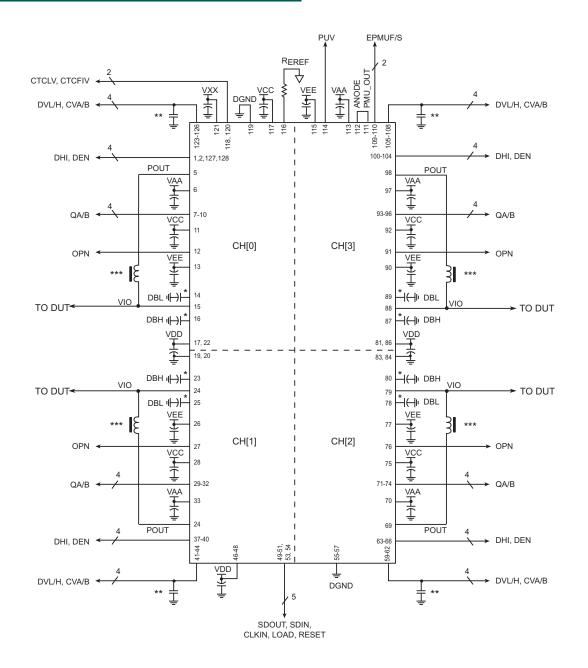

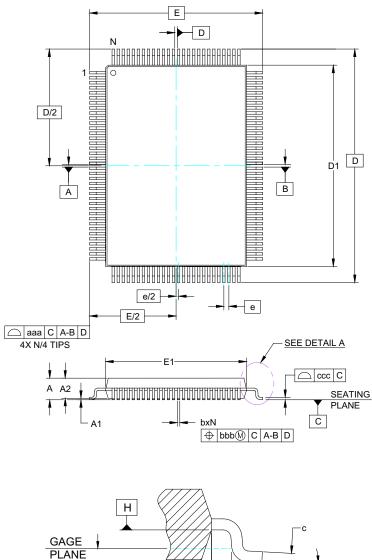

The E7804 features the inclusion of all four channels of pin electronics into a 128 pin package.

#### Features

- Four Integrated Three-Statable Drivers and Window Comparators

- Driver Voltage Range –0.2V, +5.2V

- Comparator Voltage Range –2.0V to +5.5V

- Internal Disconnect Switches

- Internal Switches to an External PMU, Range –4.75V to +9.75V, up to ±40 mA

- Per Pin Pull-Up/Down  $2K\Omega$  to (OV to +5V)

- Per Pin Continuity Test (Force Current up to -250 µA, Limit Voltage 0 to -2V)

- Self-Calibrating Driver Source Impedance to an External Reference (48Ω to 110Ω)

- Low Power Dissipation (250mW/channel quiescent)

- 128 Pin MQFP Package (with Internal Heat Spreader)

#### **Applications**

- Design for Test/Structural Pins in ATE

- Low Cost

- Logic Testers

- Memory Testers

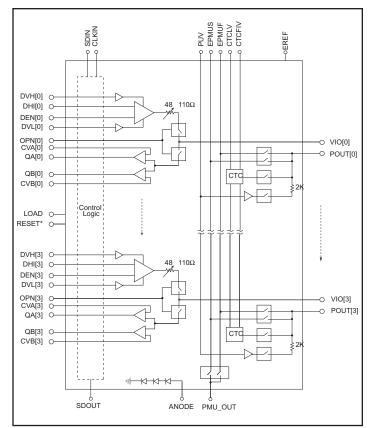

### Functional Block Diagram

### **PIN Description**

| Pin #                                | Pin Name       | Description                                                                                                                                                            |

|--------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Driver, Comparator                   |                |                                                                                                                                                                        |

| 12, 27, 76, 91                       | OPN[0:3]       | LV_TTL input that opens switches that disconnect the driver<br>and comparator from VIO. This input overrides the individual<br>switch register bits non destructively. |

| 15, 24, 79, 88                       | VIO[0:3]       | Device input/output of each channel.                                                                                                                                   |

| 127, 40, 63, 104<br>128, 39, 64, 103 | DHI, DHI*[0:3] | "Flex" differential input digital pins which select the driver high or low level.                                                                                      |

| 1, 38, 65, 102<br>2, 37, 66, 101     | DEN, DEN*[0:3] | "Flex" differential input pins which control the driver being active or in a high impedance state.                                                                     |

| 126, 41, 62, 105<br>125, 42, 61, 106 | DVH, DVL[0:3]  | High impedance analog voltage inputs which determine the driver high and low levels. Connect a 0.22µf capacitor to ground for bypassing reasons.                       |

| 16, 23, 80, 87<br>14, 25, 78, 89     | DBH, DBL[0:3]  | Driver level buffer outputs for high and low levels. Connect a 0.47 µF capacitor to ground for bypassing reasons.                                                      |

| 124, 43, 60, 107<br>123, 44, 59, 108 | CVA, CVB[0:3]  | Analog inputs which set the A and B comparator thresholds.                                                                                                             |

| 10, 29, 74, 93<br>9, 30, 73, 94      | QA, QA*[0:3]   | Differential digital outputs of comparator A.                                                                                                                          |

| 8, 31, 72, 95<br>7, 32, 71, 96       | QB, QB*[0:3]   | Differential digital outputs of comparator B.                                                                                                                          |

| РМИ                                  |                |                                                                                                                                                                        |

| 111                                  | PMU_OUT        | PMU test point for the anode of the thermal diode string.                                                                                                              |

| 5, 34, 69, 98                        | POUT[0:3]      | Parametric Measure Unit input/output of each channel.                                                                                                                  |

| 110                                  | EPMUF          | External parametric measurement for force input.                                                                                                                       |

| 109                                  | EPMUS          | External parametric measurement for sense input.                                                                                                                       |

| 114                                  | PUV            | Pull-up voltage input.                                                                                                                                                 |

| 120                                  | CTCLV          | Continuity test circuit limit voltage.                                                                                                                                 |

| 118                                  | CTCFIV         | Continuity test circuit force current voltage.                                                                                                                         |

| Control                              |                |                                                                                                                                                                        |

| 54                                   | RESET*         | Active low chip reset. Resets the internal registers. It is an asynchronous input not requiring any CLKIN transitions.                                                 |

| 51                                   | CLKIN          | Clock for the input data shift register.                                                                                                                               |

| 50                                   | SDIN           | Serial data input.                                                                                                                                                     |

| 49                                   | SDOUT          | Serial data out.                                                                                                                                                       |

| 53                                   | LOAD           | Loads input data into central register.                                                                                                                                |

# **TEST AND MEASUREMENT PRODUCTS**

# PIN Description (continued)

| Pin #                                                                | Pin Name  | Description                                                                                                                                                                                                                             |

|----------------------------------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Supplies                                                       |           |                                                                                                                                                                                                                                         |

| 11, 28, 75, 92                                                       | VCC[0:3]  | Analog positive power supply to channel high voltage circuitry (+8.25V).                                                                                                                                                                |

| 117                                                                  | VCC       | Analog positive power supply to high voltage circuitry (+8.25V).                                                                                                                                                                        |

| 6, 33, 70, 97                                                        | VAA[0:3]  | Analog positive power supply to channel circuitry (+5.0V nominal).                                                                                                                                                                      |

| 113                                                                  | VAA       | Analog positive power supply to core circuitry (+5.0V nominal).                                                                                                                                                                         |

| 13, 26, 77, 90, 115                                                  | VEE       | Analog negative power supply (–5.0V nominal).                                                                                                                                                                                           |

| 17, 22, 81, 86                                                       | VDD[0:3]  | Digital positive power supply to channel comparator outputs (+3.3V nominal).                                                                                                                                                            |

| 46, 47, 48                                                           | VDD       | Digital positive power supply for core logic (+3.3V nominal).                                                                                                                                                                           |

| 19, 20, 83, 84                                                       | AGND[0:3] | Analog ground for channels.                                                                                                                                                                                                             |

| 55, 56, 57, 119                                                      | DGND      | Digital ground for chip.                                                                                                                                                                                                                |

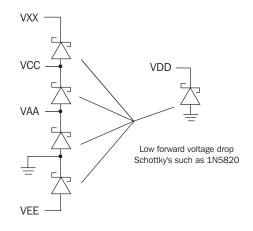

| 121                                                                  | VXX       | Switch positive power supply (VCC to VEE + 15V).                                                                                                                                                                                        |

| Miscellaneous                                                        |           |                                                                                                                                                                                                                                         |

| 116                                                                  | EREF      | External reference resistor input. REREF should be connected between EREF and AGND.                                                                                                                                                     |

| 112                                                                  | ANODE     | Anode terminal of the on-chip thermal diode string. The pin is ESD protected to VXX, so when measuring the forward drop of the diode string, VXX should be either floating or $\geq 2V$ . Cathode of diode string is connected to DGND. |

| 3, 4, 18, 21, 35, 36,<br>45, 52, 58, 67, 68,<br>82, 85, 99, 100, 122 | NC        | No connect pin. No connection is made internally. These pins can<br>be connected to a ground plane to assist in heat removal from the<br>package.                                                                                       |

Pin Description (continued)

# **Circuit Description**

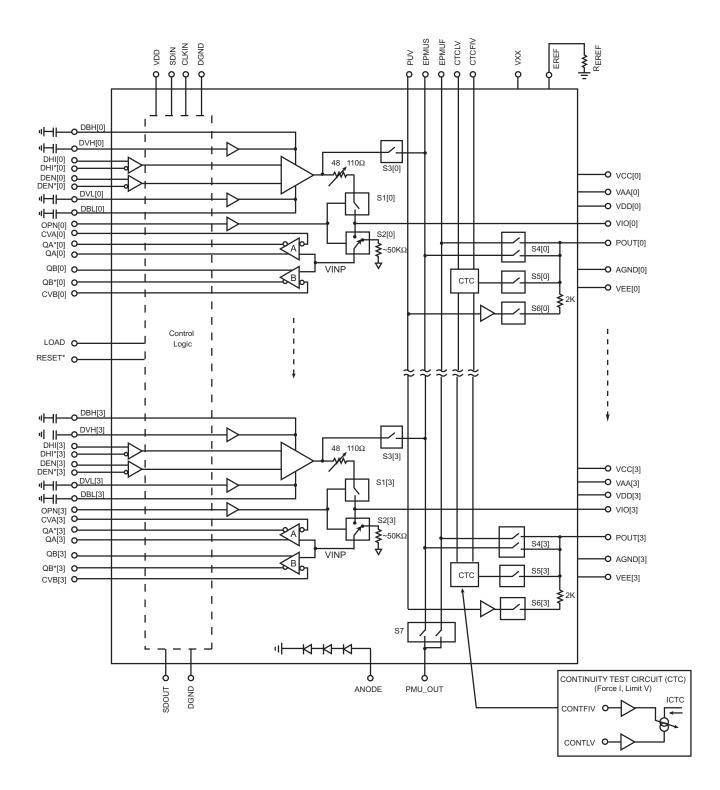

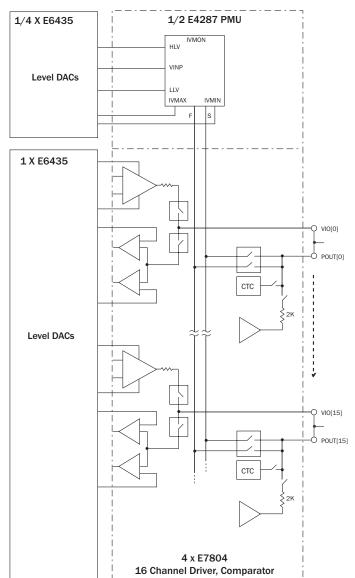

Figure 1. Detailed Block Diagram of E7804 Quad Driver and Window Comparator

# TEST AND MEASUREMENT PRODUCTS

# Circuit Description (continued)

#### Introduction

The four driver and window comparator channels of the E7804 are shown in Figure 1.

#### Driver

Refer to Table 1 showing the modes of operation of the driver.

Each channel's driver states of HiZ, force DVH voltage, force DVL voltage and Open can be controlled either by external input pins or via internal registers and bits programmed through the serial interface.

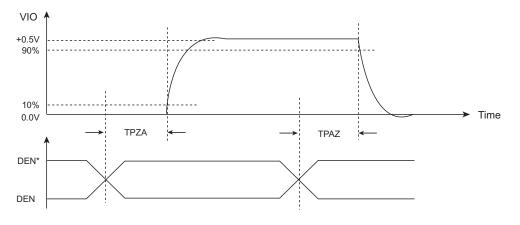

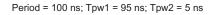

The HiZ/DVH/DVL states are controlled by the differential, external inputs, DHI/DHI\* and DEN/DEN\*. Each channel also has internal register bits (see Table 2, CH[0:3]\_Relays\_ &\_States registers) SDHI and SDEN that accomplish the same functions as DHI and DEN. The serial register has another bit, SEN (Serial Enable) that allows the SDI and SDEN bits to override the external input pins DHI and DEN. If SEN is a logical "0", the SDHI and SDEN bits are ignored.

The DHI/DHI\* and DEN/DEN\* inputs are LV\_TTL and differential LVDS, LV\_PECL compatible.

Unused DHI/DHI\* or DEN/DEN\* must be tied to valid logic levels.

#### **Optimizing Driver Waveforms**

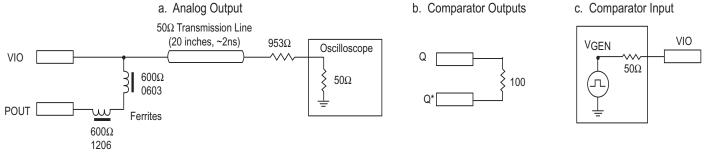

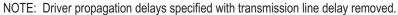

The driver output pin, VIO, will normally be connected to the parametric output pin, POUT, when designed into a system. See the recommended 7804 Hookup drawing farther on in this datasheet. The POUT pin has a lumped capacitance associated with it that will degrade the signal integrity of the driver output waveform if not properly compensated for. The recommendation is to insert ferrite devices between the connection of POUT to VIO to accomplish this. For more details on how and why this approach is used, please read Semtech Application Note #ATE-A3 ATE-to-DUT Interface: Using Ferrites to Replace Relays for Lower Cost and Improved Performance.

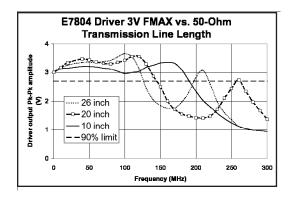

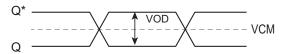

The driver output impedance has a reactive component to it and will not completely absorb reflections from an unterminated transmission line. This is common for all drivers, but more so in CMOS drivers than high speed bipolar stages. The figure here shows how transmission line length, here in the form of coaxial cable, will sum the reflections constructively and destructively to alter the peak-to-peak waveform excursions across frequency. More data on this performance and methods for optimizing signal integrity and extending Fmax will be available from Semtech staff. Check with Semtech for the latest information. From the graph below one can see that E7804 driver signals in excess of 150MHz are possible.

#### **Driver Levels**

Each channel's DVH and DVL are high input impedance voltage inputs which establish the channel driver's high and low levels. The driver's output range is -0.2V, +5.2V.

DVH to VIO and DVL to VIO offset errors are small, which allow the E7804 to be configured with common input levels to each channel (i.e. DVH[0:3] may be connected together externally, and the same for DVL[0:3]).

#### **Driver Source Impedance**

Drivers feature a self-calibrating source impedance calibrated to match an external resistor, REREF, connected between the EREF pin and analog ground. The source impedance can be chosen to calibrate in the range  $48\Omega$  to  $110\Omega$  using the calculation REREF/100.

A driver's source impedance is affected by its DVH and DVL levels, and therefore needs recalibrating whenever driver levels into the chip are changed. The calibration routine is initiated via the serial interface (see Table 2, calibrate\_output\_z register). When initiated, all channels are recalibrated in parallel.

# Circuit Description (continued)

#### **Driver Connect/Disconnect**

The driver output connects to the VIO output pin through an internal, normally open switch (S1). Refer to the Functional Block diagram in Figure 1 for Switch S1. This switch can be closed by serially programming the internal register bit for the appropriate channel (see Table 2, CH[0:3]\_Relays\_ &\_States registers) denoted as S1 to a logical "1". Logical "O" will open the switch. An external pin, OPN[0:3] one input for each channel, is combined with the register bit and will override the internal register bit and Open the S1 switch for the channel. In its low state, the OPN input will not override and force the switch closed however. (It should be noted that OPN=1 will also open S2 to disconnect the channel's window comparators from the VIO pin.) OPN is a fast way of disconnecting the lower voltage driver and comparator circuitry from the VIO pin. When the driver (and comparator) are disconnected, the voltage at VIO may be in the range of the VEE to VXX power supplies.

The high voltage disconnect switches permit an external Parametric Measurement Unit (PMU) to be connected to the VIO pin having a maximum range from VEE to VXX volts and up to  $\pm 40$  mA.

This high voltage isolation also permits an external driver to apply up to VXX volts (when switches S1 and S2 are open) for high voltage applications.

Each driver may also be connected, internally, to EPMUS in order to measure its output for purposes of calibrating the DVH/L levels via switch S3.

|        |        | OP        | OPN=1   |      |

|--------|--------|-----------|---------|------|

| Digita | Inputs | S1 Closed | S1 Open | Х    |

| DEN    | DHI    | VIO       | VIO     | VIO  |

| 1      | 0      | DVL       | Open    | Open |

| 1      | 1      | DVH       | Open    | Open |

| 0      | 0      | HiZ       | Open    | Open |

| 0      | 1      | HiZ       | Open    | Open |

| OPN | (Open Channel<br>Input) | Open | (Driver, Comp open/discon-<br>nected (see Table 3) |

|-----|-------------------------|------|----------------------------------------------------|

| DVL | (Driver Low)            | Х    | (Don't Care)                                       |

| DVH | (Driver High)           | S1   | (Driver Output Switch                              |

| HiZ | (High Impedance)        |      |                                                    |

#### Table 1. Driver Modes of Operation

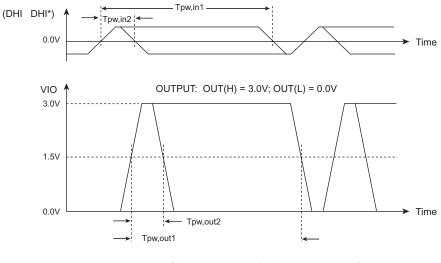

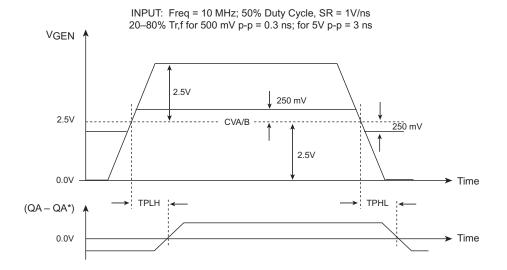

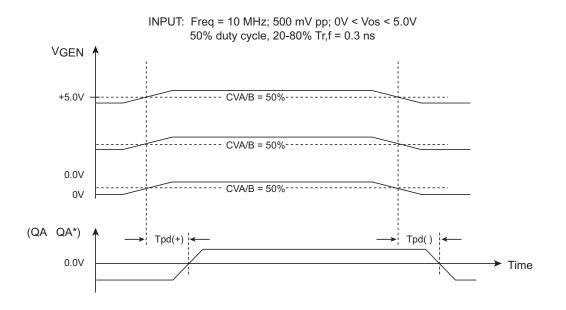

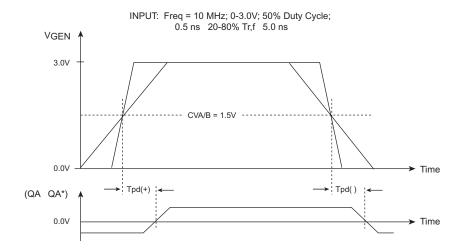

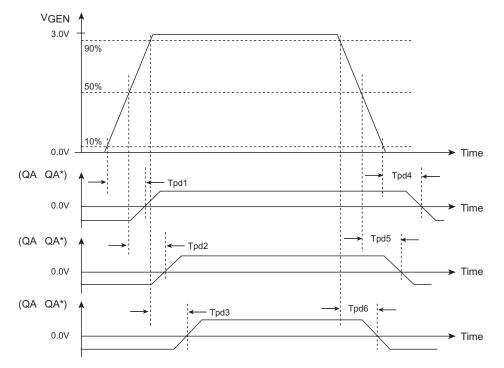

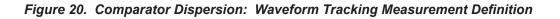

Each channel's two comparators, A and B, are combined to form a window comparator to determine whether its input, VINP, is above, below, or in between the two comparator thresholds (CVA and CVB). VINP is tied to the positive input of both comparators.

The CVA/B inputs should be driven from low impedance sources. There is an input non-linear current shift of ~15µA when the VINP signal to the comparator crosses polarity with respect to the CVA/B input. If the source impedance is too great, this could affect the accuracy of the compare points. The voltage source's output impedance should be below  $4K\Omega$  to avoid this. DAC or op amp outputs will have no issue with this. (If resistor dividers are used to create the CVA/B voltages, the voltage should be buffered to prevent this shift.)

VINP has a range of -2V, +5.5V, but is restricted to the range of the drivers whenever a comparator is connected to its driver (S1 and S2 switches both closed), namely -0.2V, +5.2V.

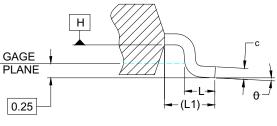

The comparator outputs are differential LVDS compatible on the QA/QA\* and QB/QB\* device pins. The output states of the comparators for each channel can also be read back using the serial interface. See Table 3, CH[0:3]\_switches\_&\_states read back instruction for the individual channels.

#### **Comparator Levels**

Each channel's CVA and CVB are the window comparator's two threshold levels. CVA and CVB are high impedance voltage inputs that determine the thresholds at which the window comparator changes state. CVA and CVB have a range of -2.0V, +5.5V.

#### **Comparator Connect/Disconnect**

The window comparator input (VINP) connects to the VIO pin through an internal switch (S2). This switch can be closed to VIO by serially programming the internal register bit for the appropriate channel (see Table 2, CH[0:3]\_switches\_&\_states registers) denoted as S2 to a logical "1". Logical "0" will open the switch from VIO. The comparator input is connected to approximately zero volts

EMTECH

#### Circuit Description (continued)

when disconnected from VIO through ~ $50K\Omega$ . To prevent the comparator outputs from switching due to noise when not in use, the CVA/B inputs should be parked >250mV from ground. An external pin, OPN[0:3] one input for each channel, is combined with the register bit, and will override the internal register bit and open the S2 switch for the channel. In its low state, the OPN input will not override and force the switch closed. (It should be noted that OPN=1 will also open S1 to disconnect the channel's driver output from the VIO pin.) OPN is a fast way of disconnecting the lower voltage driver and comparator circuitry from the VIO pin. When the comparator (and driver) are disconnected, the voltage at the VIO pin may be in the range of the VEE to VXX power supplies.

#### **Parametric Measurements**

The E7804 incorporates a switch matrix which permits an External Parametric Measurement Unit (EPMU) to be connected to one or more channel's POUT pin. The EPMU range is a function of the VEE and VXX power supplies with  $\pm 40$  mA capability. Typically, POUT is connected directly to the VIO pin or connected by an inductor so as to minimize the effect of the capacitance at the POUT pin on the driver's waveform and maximum frequency.

The EPMUF and EPMUS inputs are force and sense inputs respectively and connect to the POUT output pin through an internal, normally open, dual switch (S4). There is one dual switch for each channel [0:3]. This switch can be closed by serially programming the internal register bit for the appropriate channel (see Table 2, CH[0:3]\_switches\_&\_states registers) denoted as S4 to a logical "1". Logical "0" will open the switch. The switch and metal lines for the EMPUF path are sized to accommodate the higher currents (up to 40mA). Do not use EPMUS for higher currents. The EPMUS line is the Kelvin sense path for the external PMU.

#### **Continuity Test Circuit**

Each channel has a programmable Continuity Test Circuit (CTC) which can be switched to its POUT pin. The CTC sinks current in the range -15 to -250 µA as determined by the voltage of the CTCFIV input pin which is common to all CTC's.

The relationship between the CTCFIV input voltage and the resulting current produced by the CTC uses the resistor REREF, as a reference. This gives a good degree of voltage to current accuracy. The relationship is:

$\mathsf{ICTC} = -1.09 \, \star \, [\mathsf{CTCFIV}(\mathsf{V}) \, / \, \mathsf{REREF}(\Omega)].$

CTCLV input determines the voltage limit to which CTC may sink current. CTCLV has a range of 0 to -2.0V and is common to all channels' CTCs. With POUT, connected externally to VIO, then with CTC connected and sinking current, the resultant voltage at VIO can be tested by the channel's comparators. As this voltage could be as low as -2V, when performing a continuity test, a channel's driver should be disconnected in order to protect the driver, which has a range of -0.2V to +5.2V. The driver output should be disconnected by opening switch S1 when connecting the CTC to the POUT pin. The CTC connects to the POUT pin through the normally open switch S5. Switch S5 can be closed by serially programming a logical "1" via the internal register for the appropriate channel. See Table 2,"CH[0:3]\_switches\_&\_states write instruction for the individual channels.

Note that the CTC's use the external resistor on the EREF pin to calculate the ICTC test currents. The driver output impedance calibration also uses this reference. If any CTC is switched in-circuit (S5 closed), then attempting to calibrate the driver output impedance will fail and not occur. No change to the calibration values will take place.

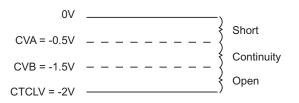

A typical continuity test will program the CTC's force current to  $-100 \mu$ A, its voltage limit at -2V, and CVA and CVB at -0.5V and -1.5V, respectively, so as to detect shorts, opens and continuity. typically, in this test, the DUT power supplies are all set to zero volts. The continuity test will determine if each pin of the DUT is connected to the pin channel in the tester without shorts to supplies or ground.

The tested pins will test good if the resulting voltage from a  $-100\mu$ A load on them results in  $\sim$  -0.7V. This is the voltage

Downloaded from Elcodis.com electronic components distributor

8

EMTECH

### Circuit Description (continued)

that will be present if the pin substrate or ESD diodes are present. A short can be detected if the resulting voltage is close to zero volts. An Open will be detected if the voltage goes close to -2V. The figure above ilustrates this test with the CVA = -0.5V and CVB = -1.5V.

#### **Pull-Up Resistor**

Each channel has a 2KW (typ.) pull-up resistor that can be switched to its POUT. The effective pull-up, including resistor and switch, is in the range 1KW to 3KW.

PUV is a single input and is buffered at each channel to the pull-up resistors. The buffer and resistor are capable of sourcing or sinking (pull-up or pull-down) currents for 0 to 5V external signals.

#### **Thermal Monitor**

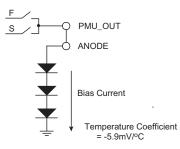

An on-chip thermal diode string of three diodes in series allows accurate die temperature measurements (see diagram below).

A bias current of  $100 \ \mu A$  is injected through the string, and the measured voltage corresponds to a specific junction temperature with the following equation:

$$Tj[\circ C] = (0.7195 - V_{ANODE}/3) / (0.001967)$$

The ANODE of the diodes may be switched internally to the EPMU bus such that temperature measurements can be performed by the EPMU. The connection to the diode string's ANODE pin for the EPMU is performed externally by shorting the PMU\_OUT pin to the ANODE pin. This external connection is available to make it possible to access the diode string when the device is not powered up. This is useful for calibration purposes of the diode string. The ANODE pin is internally ESD protected in the positive direction to VXX. To use the diode string, VXX needs to either be floating (unpowered operation) or  $\geq$ 2V.

#### **Programming Functional Description**

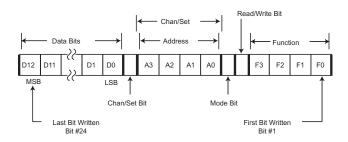

The E7804 features a serial data input programming structure to program the channels functions and switches, assign or invoke Set functions, as well as control more global chip functions such as Reset and Calibration. The majority of the functions are both Read and Write. The serial streams are all 24-bits long and are referred to as "instructions" because the serial streams are built up with address, function, read and select bits as well as data into the 24-bit stream which is clocked serially into the device.

The following is a description of the 24-bit instruction stream.

#### Data: 13 bits

This field contains the data to be written into various registers which control the function of the part, or the selected channel(s).

#### Channel/Set Address Select: 1 bit

This bit determines whether a single channel or a set of channels is being addressed.

- 0 = channel direct functions

- 1 = set of channels

#### Channel/Set Address: 4 bits

This field contains the address of the channel or set being operated on.

#### Mode: 1 bit

This determines whether the instruction refers to a chiplevel control (such as chip reset), or refers to a channel or set of channels.

- 0 = chip function

- 1 = channel or set function

# TEST AND MEASUREMENT PRODUCTS

# Circuit Description (continued)

#### Read/Write: 1 bit

This determines whether a particular address/function is being written or read. (Note that some functions are readonly or write-only).

0 = write a control/data register

1 = read back the contents of a register

#### Function: 4 bits

This determines which function within a channel or set is being set or read.

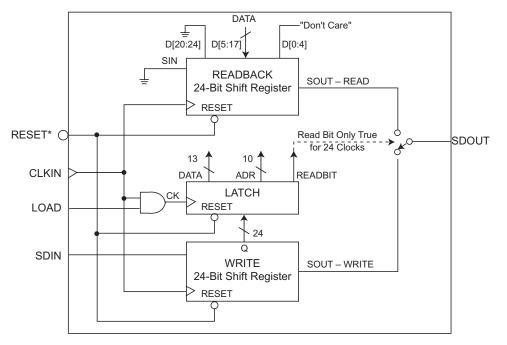

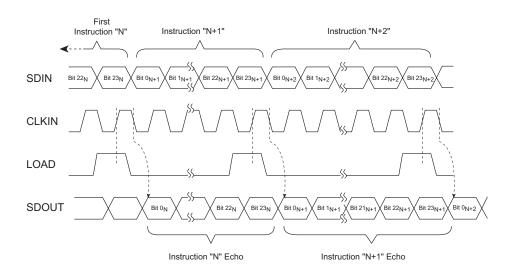

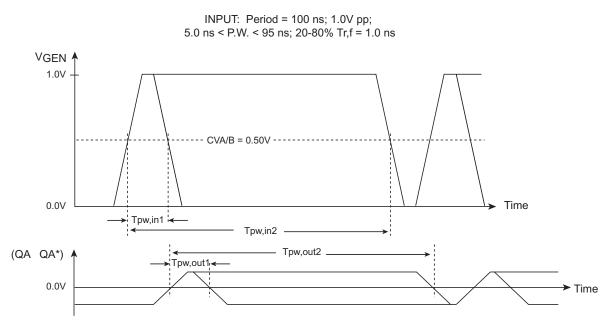

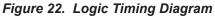

Refer to Figure 2 for a block diagram of the Write and Read logic for the serial programming. The serial data is input into the device SDIN pin. The data at SDIN is clocked in on the high-going edge of the CLKIN input signal. The data at the SDOUT pin is clocked out on the low-going edge of the CLKIN input signal for ease of "daisy chaining" multiple devices.

#### **RESET\***

There is a single input pin to the entire E7804 chip that will clear all on-chip registers and open all on-chip switches. This input pin, RESET\*, is active low and is asynchronous, not requiring any CLKIN transitions to operate. It is advised that, upon power-up in a system, this pin is either held low or cycled low for a brief time while the system and power supplies become stable in order to put the E7804 into a known starting state. After power-up, the RESET\* may be exercised or a soft reset instruction may be programmed.

#### Write Serial Data

Data is shifted into the WRITE shift register using CLKIN. The data stored in the shift register will be stored into the E7804 by asserting the LOAD input signal during the 24th CLKIN high-going edge. The LATCH will hold the instruction inside the E7804 for address decoding and data storage into the appropriate on-chip registers. **Seven** (7) more CLKIN high-going edges should be given after a LOAD for full decode and all instruction executions.

Refer to Figure 3 for a timing diagram of the writing operation. Notice that the SDOUT data that is clocked out on the low-going edge of CLKIN is a bit for bit representation of the data that had been shifted into the E7804 24 clock edges beforehand. This echoing of the data allows the user to "daisy chain" multiple E7804 devices to minimize the number of serial data streams that need to be implemented. The compromise is the length of time it takes to clock through all the 24-bit instructions for all the devices in the chain.

Figure 2. Block Diagram of Read and Write Shift Registers

Circuit Description (continued)

Figure 3. Serial Data Programming - Write Instruction

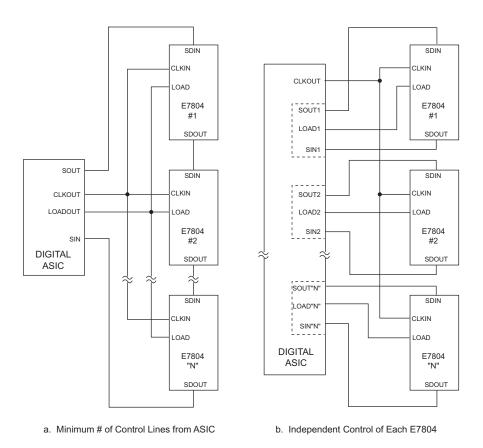

Figure 4 depicts two topologies to serially read and write multiple E7804 devices on a single assembly. Figure 4a daisy chains the serial I/O (SDOUT to SDIN) pins, and the CLKIN and LOAD functions are common for all the E7804s. This topology uses a minimum amount of I/O from the control logic. However, in order to read or write the E7804's an instruction string of 24 x N bits long needs to be created, clocked all the way through the devices, and a parallel LOAD signal asserted for all devices. NO\_OP instructions may be used for the devices that are not being addressed.

Figure 4b shows a topology from the control logic that offers rapid programming time and complete independence. This topology relies on enough I/O signals being available from the control logic. Notice that the CLKIN pins are still all common because independence is allowed by the individual LOAD signals to each E7804.

If it is determined that readback from the E7804s are not necessary, the control logic can be further simplified. Readback is not necessary for the operation of the E7804. It is offered as a good diagnostic tool and possible programming aid.

#### **Read Serial Data**

In order to readback data, an instruction is constructed with the Read\_Bit set to a logical "1" in the instruction

stream and written to the E7804. The instruction stream must be properly constructed for address and select bits to insure that the proper register will be accessed for readback. The data bits D0:D12 in this Read instruction are Don't\_Care.

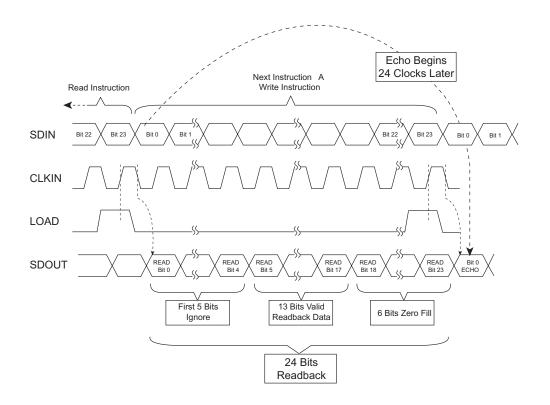

Refer to Figure 5 for a timing diagram of the readback process and Figure 2 for a block diagram of how the readback operation works. Once the LOAD signal is asserted on the 24th high-going CLKIN edge to latch in the READ instruction for a particular address, the internal READ line will assert true and switch the SDOUT pin to output data from the internal readback shift register. The readback data will immediately start to output from the SDOUT pin on the low-going edge of CLKIN. The readback will continue for 24 bits.

The first 5 bits of data readback should be ignored. The next 13 bits will be the requested register's readback data. Finally, the last 6 bits are logical zeros.

While clocking out the readback data, a new instruction can be simultaneously clocked in at SDIN. At the conclusion of the 24-bit readback, the SDOUT data will revert back to echoing the SDIN data shifted by 24 clocks.

Circuit Description (continued)

Figure 4. Serial Control of Multiple E7804s

Figure 5 depicts the conclusion of a Read instruction being written to the E7804. The first LOAD pulse straddling the rising edge of CLKIN latches in the Read instruction, echoing at SDOUT stops, and the readback of the register begins. After 24 low-going clocks, the data at SDOUT resumes echoing the written data at SDIN. Even without the second LOAD pulse, the echoing will begin. Figure 5 depicts a Write instruction following the Read. This could be another Read instruction, in which case the echoing of SDIN would not begin as indicated. Instead, another sequence of 24 readback bits would begin.

The readback data format and address are defined in Table 3. The Read operation will continue for 24 low-going clock edges. The SDOUT will begin outputting data from the write shift register after the 24th low-going clock edge.

#### Address Map

Table 2 shows the Write Table and Address Map. Across the top of the table are the 24 bits of data denoted as Bit #0 through Bit #23. Hex notation is also provided as well as the binary positions.

The instruction is constructed of 13 Data bits, 8 address bits, 2 select bits and a read bit. Figure 3 shows the bit pattern in the write instructions. The instructions are separated into 3 main groups. The Chip Functions, the Channel Functions and the Set Functions. Each instruction has a Register Name associated with it. In the pages following Table 2 are descriptions of each of the register names and, where applicable, a bit-by-bit description of the data. **TEST AND MEASUREMENT PRODUCTS** Circuit Description (continued)

EMTECH

#### **Chip Functions**

The Chip Functions group of instructions controls chip functions that are global in scope and not associated with a particular channel. Examples of these functions are the chip identification number and revision, the Reset function for chip wide reset, and initiation of calibration.

- *Function Address* Instructions in the group are denoted by this set of bits.

- *Read Bit*-- Set to "1" only if user intends to read back a register.

- *Chan Bit* Set to a "0" since this instruction group is not channel related.

- Chan/Set Adr These 4 bits are "don't care". Since these would select either a channel or set

- number, and these are Chip Functions, they don't apply.

- Set Select Bit This bit is a "don't care" for the Chip Functions group.

#### **Channel Functions**

The Channel Functions group of instructions address the functionality of individual registers and bits that are particular to specific channels of the E7804. Driver states, channel switches, calibration factors and set assignments are included in this group.

*Function Address* – These bits denote which function of the particular channels is being addressed.

- *Read Bit*-- Set to "1" only if user intends to read back a register.

- *Chan Bit* Set to a "1" because these instructions relate to specific channel registers.

- *Chan/Set Adr* These bits will denote which channel is being addressed for the particular function. Valid range is 0x0 through 0x3 for the E7804.

- Set Select Bit This bit is set to a "0" because this is the Channel Functions group.

Figure 5. Serial Data Programming - Readback Sequence

TEST AND MEASUREMENT PRODUCTS

# Circuit Description (continued)

#### **Set Functions**

Set Functions are a group of 8 instructions corresponding to the 8 available Sets that will configure any channel that has been assigned to that Set. The Set Functions are writeonly, but the effects of a Set instruction can be read back from the individual channel's registers. The Set is given control of any channel's driver states or switches. The Set concept is a way of programming all channels on any E7804 that have been assigned to that particular SET to a particular configuration with one instruction write cycle.

- Function Address These addresses should all be "0".

- *Read Bit*-- Set to "0" since there is no readback for set instructions.

- Chan Bit Set to a "1".

- Chan/Set Adr These bits will denote which set is being

- programmed. Valid set values are 0x0 through 0x7 corresponding to the eight valid SETs.

- Set Select Bit This bit is a "1" because this is the SET Functions group.

#### SET Programming

Referring to Table 2, a channel's SETs Register may be programmed via the CH[0:3]\_set\_assign instructions. This is an independent 8-bit register per channel which determines the SETs to which the channel belongs. A channel may belong to none, one, or any combination of up to 8 sets.

#### Programming the Driver's Source Impedance

Figure 1 shows that each driver's source impedance is programmable over a 48W to 110W range so as to match the impedance of the transmission line connecting VOP to the Device Under Test (DUT). The driver's source impedance is automatically programmed to match REREF/100, where REREF is the external reference resistor connected to the EREF pin.

Initiating the source match auto-calibration sequence is a "chip function" (Table 2). Auto-calibration is performed on all channels in parallel.

The Driver's source impedance is affected by its DVH and DVL levels and, therefore, auto-calibration should be initiated whenever driver levels are changed.

Following auto-calibration, a driver's source impedances match (REREF/100) W when its output is at (DVH + DVL) / 2. If the output voltages of the driver are reprogrammed, then it is advised to recalibrate to maintain the best accuracy.

Calibration will occur after writing the global function instruction calibrate\_output\_z. Calibration requires an additional 576 clock edges from CLKIN to complete the process. This is 24 instructions worth of clocks. Instructions for the device undergoing calibration may be any valid instruction except that which connects the CTC output to POUT, or simply applying the clocks without LOAD'ing instructions is also valid. At the end of the process, the new, calibrated output impedances will be applied to the driver output stage. The driver may be in the enabled or disabled state. If enabled, there could be a noticable perturbation on the output.

# Circuit Description (continued)

|                   |                      | Bit #    | 23    | 22   | 21  | 20 | 19         | 18           | 17           | 16       | 15       | 14       | 13       | 12       | 11       | 10  | 9   | 8        | 7      | 6      | 5     | 4    | 3  | 2        | 1        | 0            |

|-------------------|----------------------|----------|-------|------|-----|----|------------|--------------|--------------|----------|----------|----------|----------|----------|----------|-----|-----|----------|--------|--------|-------|------|----|----------|----------|--------------|

|                   | Hex Mul              |          | 20    | 010x |     | 20 | 10         |              | 0000         | 10       |          |          | 000      |          |          |     | 100 | Ū        |        |        | x0010 |      |    | 0x00     |          | Ť            |

|                   | Binary Po            | sition   | 8     | 4    | 2   | 1  | 8          | 4            | 2            | 1        | 8        | 4        | 2        | 1        | 8        | 4   | 2   | 1        | 8      | 4      | 2     | 1    | 8  | 4        | 2        | 1            |

|                   | Register Name        |          |       |      |     |    |            | Da           | ata Bits     | s        |          |          |          |          |          |     | c   | han/s    |        | lr     |       |      | F  | unctio   | n Adr    |              |

|                   | Write Only =         | wo       |       |      |     |    |            |              |              |          |          |          |          |          |          | Set |     |          |        |        | Chan  | Read |    |          |          |              |

|                   | Read Only =          | RO       | D12   |      |     |    |            |              |              |          |          |          |          |          | D0       | Sel |     |          |        |        | Bit   | Bit  |    |          |          |              |

|                   | Read/Write =         | R/W      | (MSB) | D11  | D10 | D9 | D8         | D7           | D6           | D5       | D4       | D3       | D2       | D1       | (LSB)    |     | A3  | A2       | A1     | A0     |       |      | F3 | F2       | F1 F     | F0           |

|                   | no_op                | WO       | 0     | 0    | 0   | 0  | 0          | 0            | 0            | 0        | 0        | 0        | 0        | 0        | 0        | 0   | 0   | 0        | 0      | 0      | 0     | 0    | 0  | 0        | 0        | 0 W1         |

|                   | chip_id              | RO       | -     | Ŭ    | Ů   | Ű  |            |              | ick Tab      |          |          | Ű        | ů        | Ű        | Ŭ        | x   | x   | x        | x      | x      | 0     | 1    | 0  | 0        | -        | 1 W2         |

| NS                | chip revision        | RO       |       |      |     |    |            |              | ck Tab       |          |          |          |          |          |          | x   | x   | x        | x      | x      | 0     | 1    | 0  | 0        | -        | 0 W3         |

| 2                 |                      | R/W      |       |      |     |    |            |              |              |          |          |          |          |          | CAL      | x   | x   | x        | x      | x      | 0     | 0/1  | 0  | 0        | _        | 1 W4         |

| NC                |                      | R/W      |       |      |     |    |            |              |              |          |          |          |          |          | S7       | x   | x   | x        | х      | х      | 0     | 0/1  | 0  | 1        | _        | 0 W5         |

| E                 | . =                  | R/W      |       |      |     |    |            |              |              | (        | 0x00 to  | 0xFF     |          |          |          | x   | x   | x        | x      | х      | 0     | 0/1  | 0  | 1        |          | 1 W6         |

| CHIP FUNCTIONS    | <b>o</b>             | R/W      |       |      |     |    |            |              |              |          |          |          |          |          | Z        | x   | x   | х        | х      | х      | 0     | 0/1  | 0  | 1        | _        | 0 W8         |

| °                 | reserved             |          |       |      |     |    |            |              |              |          |          |          |          |          |          | х   | х   | х        | х      | х      | 0     | 0/1  | C  | )111 -   | 1110     | W9           |

|                   | reset                | WO       |       |      |     |    |            |              |              |          |          |          |          | SETS     | ALL      | х   | х   | х        | х      | х      | 0     | 0    | 1  | 1        | 1        | 1 W1         |

|                   |                      |          |       |      |     |    |            |              |              |          |          |          |          |          |          |     |     |          |        |        |       |      |    | <u> </u> | <u> </u> | <b></b>      |

|                   | CH0_relays_&_states  | R/W      |       |      |     |    | INT        | SDEN         | SDHI         | S6       | S5       | S4       | S3       | S2       | S1       | 0   | 0   | 0        | 0      | 0      | 1     | 0/1  | 0  | 0        | 0        | 0 W1         |

|                   | · · · · · ·          | R/W      |       |      |     |    | INT        | SDEN         | SDH          | S6       | S5       | 54<br>S4 | S3       | S2       | S1       | 0   | 0   | 0        | 0      | 1      | 1     | 0/1  | 0  | 0        | -        | 0 W1         |

|                   |                      | R/W      |       |      |     |    | INT        | SDEN         | SDHI         | S6       | S5       | S4       | S3       | S2       | S1       | 0   | 0   | 0        | 1      | 0      | 1     | 0/1  | 0  | 0        | -        | 0 W1         |

|                   |                      | R/W      |       |      |     |    | INT        | SDEN         | SDHI         | S6       | S5       | S4       | S3       | S2       | S1       | 0   | 0   | 0        | 1      | 1      | 1     | 0/1  | 0  | 0        |          | 0 W1         |

|                   | reserved             | 10,11    |       |      |     |    |            | ODEN         | ODIII        | 00       | 00       | 04       | 00       | 02       | 01       | 0   |     | 0100 -   |        |        | 1     | 0/1  | 0  | 0        |          | 0 W1         |

|                   |                      | R/W      |       |      |     |    |            |              | in           | npedar   | nce ca   | libratio | n code   |          |          | 0   | 0   | 0        | 0      | 0      | 1     | 0/1  | 0  | 0        | -        | 1 W1         |

|                   |                      | R/W      |       |      |     |    |            |              |              |          | nce ca   |          |          |          |          | 0   | 0   | 0        | 0      | 1      | 1     | 0/1  | 0  | 0        | _        | 1 W1         |

|                   | CH2_DVH_calib_Z      | R/W      |       |      |     |    |            |              |              |          | nce ca   |          |          |          |          | 0   | 0   | 0        | 1      | 0      | 1     | 0/1  | 0  | 0        | _        | 1 W1         |

|                   |                      | R/W      |       |      |     |    |            |              | in           | npedai   | nce ca   | libratio | n code   | 9        |          | 0   | 0   | 0        | 1      | 1      | 1     | 0/1  | 0  | 0        | -        | 1 W1         |

| CHANNEL FUNCTIONS | reserved             |          |       |      |     |    |            |              |              | ,<br>    |          |          |          |          |          | 0   |     | 0100 -   |        |        | 1     | 0/1  | 0  | 0        |          | 1 W2         |

| Ĕ                 |                      | R/W      |       |      |     |    |            |              | in           | npedai   | nce ca   | libratio | n code   | ;        |          | 0   | 0   | 0        | 0      | 0      | 1     | 0/1  | 0  | 0        |          | 0 W2         |

| Ň                 |                      | R/W      |       |      |     |    |            |              | in           | npedai   | nce ca   | libratio | n code   | 9        |          | 0   | 0   | 0        | 0      | 1      | 1     | 0/1  | 0  | 0        | _        | 0 W2         |

| ц.<br>Ц.          | CH2_DVL_calib_Z      | R/W      |       |      |     |    |            |              | in           | npedar   | nce ca   | libratio | n code   | Э        |          | 0   | 0   | 0        | 1      | 0      | 1     | 0/1  | 0  | 0        | 1        | 0 W2         |

| N, N              | CH3_DVL_calib_Z      | R/W      |       |      |     |    |            |              | in           | npedai   | nce ca   | libratio | n code   | Э        |          | 0   | 0   | 0        | 1      | 1      | 1     | 0/1  | 0  | 0        | 1        | 0 W2         |

| Ι Å               | reserved             |          |       |      |     |    |            |              |              |          |          |          |          |          |          | 0   |     | 0100 ·   | - 1110 | )      | 1     | 0/1  | 0  | 0        | 1        | 0 W2         |

| Ū                 | CH0_sw_calib_Z       | R/W      |       |      |     |    |            |              |              | impe     | dance    | calibr   | ation o  | ode      |          | 0   | 0   | 0        | 0      | 0      | 1     | 0/1  | 0  | 0        | 1        | 1 W2         |

|                   | CH1_sw_calib_Z       | R/W      |       |      | ĺ   |    |            |              |              | impe     | edance   | calibr   | ation c  | ode      |          | 0   | 0   | 0        | 0      | 1      | 1     | 0/1  | 0  | 0        | 1        | 1 W2         |

|                   | CH2_sw_calib_Z       | R/W      |       |      |     |    |            |              |              | impe     | edance   | calibr   | ation d  | ode      |          | 0   | 0   | 0        | 1      | 0      | 1     | 0/1  | 0  | 0        | 1        | 1 W2         |

|                   | CH3_sw_calib_Z       | R/W      |       |      |     |    |            |              |              | impe     | edance   | calibr   | ation d  | ode      |          | 0   | 0   | 0        | 1      | 1      | 1     | 0/1  | 0  | 0        | 1        | 1 W2         |

|                   | reserved             |          |       |      |     |    |            |              |              |          |          |          |          |          |          | 0   |     | 0100 ·   | - 1110 | )      | 1     | 0/1  | 0  | 0        | 1        | 1 W3         |

|                   | CH0_set_assign       | R/W      |       |      |     |    |            | set7         | set6         | set5     | set4     | set3     | set2     | set1     | set0     | 0   | 0   | 0        | 0      | 0      | 1     | 0/1  | 1  | 1        | 1        | 1 W3         |

|                   | CH1_set_assign       | R/W      |       |      |     |    |            | set7         | set6         | set5     | set4     | set3     | set2     | set1     | set0     | 0   | 0   | 0        | 0      | 1      | 1     | 0/1  | 1  | 1        | 1        | 1 W3         |

|                   | CH2_set_assign       | R/W      |       |      |     |    |            | set7         | set6         | set5     | set4     | set3     | set2     | set1     | set0     | 0   | 0   | 0        | 1      | 0      | 1     | 0/1  | 1  | 1        | 1        | 1 W3         |

|                   | CH3_set_assign       | R/W      |       |      |     |    |            | set7         | set6         | set5     | set4     | set3     | set2     | set1     | set0     | 0   | 0   | 0        | 1      | 1      | 1     | 0/1  | 1  | 1        | 1        | 1 W3         |

|                   | Cato valava 8 atat   | 14/0     |       |      |     | _  | INIT       |              | 001.11       | 66       | 05       | 64       | 62       | 62       | 01       | 1   |     | 0        | 0      | 0      | 4     | 0    |    | 0        |          | 0            |

|                   | Set0_relays_&_states | W0       |       |      |     |    | INT        | SDEN         | SDHI         | S6       | S5       | S4       | S3       | S2       | S1       | 1   | 0   | 0        | 0      | 0      | 1     | -    | 0  | 0        | _        | 0 W3         |

| Ś                 | Set1_relays_&_states | W0<br>W0 |       |      |     |    | INT<br>INT | SDEN<br>SDEN | SDHI<br>SDHI | S6<br>S6 | S5<br>S5 | S4<br>S4 | S3<br>S3 | S2<br>S2 | S1<br>S1 | 1   | 0   | 0        | 0      | 1<br>0 | 1     | 0    | 0  | 0        | -        | 0 W3<br>0 W3 |

| FUNCTIONS         | Set2_relays_&_states |          |       |      |     |    |            |              | SDHI         |          |          | _        |          | S2<br>S2 |          |     |     |          |        | _      |       | 0    |    |          | _        | _            |

| C                 | Set3_relays_&_states | W0<br>W0 |       |      |     |    | INT<br>INT | SDEN<br>SDEN | SDHI         | S6<br>S6 | S5<br>S5 | S4<br>S4 | S3<br>S3 | S2<br>S2 | S1<br>S1 | 1   | 0   | 0        | 1      | 1<br>0 | 1     | 0    | 0  | 0        | _        | 0 W3<br>0 W3 |

| L N               | Set4_relays_&_states | W0       |       |      |     |    | INT        | SDEN         | SDHI         | 56<br>S6 | 55<br>S5 | 54<br>S4 | 53<br>53 | 52<br>S2 | S1<br>S1 | 1   | 0   | 1        | 0      | 1      | 1     | 0    | 0  | 0        | -        | _            |

| Ш                 | Set5_relays_&_states |          |       |      |     |    | INT        | SDEN         | -            |          |          | _        |          | 52<br>S2 | S1<br>S1 |     | _   | 1        | 1      | 0      |       |      | 0  | -        | _        |              |

| SE                | Set6_relays_&_states | W0<br>W0 |       |      |     |    | INT        | SDEN         | SDHI<br>SDHI | S6<br>S6 | S5<br>S5 | S4<br>S4 | S3<br>S3 | S2<br>S2 | S1<br>S1 | 1   | 0   |          |        | 0      | 1     | 0    | 0  | 0        |          | 0 W4<br>0 W4 |

|                   | Set7_relays_&_states | VVU      |       |      |     |    |            | SDEN         | SDHI         | 50       | 50       | 54       | 53       | 52       | 51       | 1   | 0   | 1 1000 - | 1      | I      | 1     | 0    | 0  | 0        | _        | 0 W4         |

|                   | reserved             |          |       |      |     |    |            |              |              |          |          |          |          |          |          | 1   |     | 1000     |        |        |       | U    | U  | U        | U        | 0 004        |

Table 2 . E7804 Instruction Table/Address Map

# **TEST AND MEASUREMENT PRODUCTS**

# Circuit Description (continued)

|                   |                       | Bit # | 23 | 22  | 21   | 20    | 19 | 18  | 17 | 16 | 15 | 14  | 13    | 12     | 11       | 10     | 9       | 8       | 7      | 6    | 5 | 4   | 3 | 2    | 1   | 0 | 1   |       |

|-------------------|-----------------------|-------|----|-----|------|-------|----|-----|----|----|----|-----|-------|--------|----------|--------|---------|---------|--------|------|---|-----|---|------|-----|---|-----|-------|

|                   | Register Name         |       |    | TRA | ILIN | G 0': | s  |     |    |    |    |     | VALID | DATA R | EADB     | ACK    |         |         |        |      |   | LE/ |   | IG B | ITS |   | 1   |       |

|                   |                       |       |    |     |      |       |    | MSE | 3  |    |    |     |       |        |          |        |         |         |        | LSB  |   |     |   |      |     |   |     | Notes |

| S                 | chip_id               | RO    | 0  | 0   | 0    | 0     | 0  | 1   | 1  | 1  | 1  | 0   | 0     | 1      | 1        | 1      | 1       | 1       | 0      | 0    | Х | Х   | Х | Х    | Х   | Х | R1  | 1     |

| Į į               | chip_revision         | RO    | 0  | 0   | 0    | 0     | 0  | 0   | 0  | 0  | 0  | 0   | 0     | 0      | 0        | 0      | 0       | 0       | 0      | 0    | Х | Х   | Х | Х    | Х   | Х | R2  | 2     |

| NC.               | calibrate_output_Z    | R/W   | 0  | 0   | 0    | 0     | 0  | 0   | 0  | 0  | 0  | 0   | 0     | 0      | 0        | 0      | 0       | 0       | 0      | CAL  | Х | Х   | Х | Х    | Х   | Х | R3  |       |

| GLOBAL FUNCTIONS  | chip_switches         | R/W   | 0  | 0   | 0    | 0     | 0  | 0   | 0  | 0  | 0  | 0   | 0     | 0      | 0        | 0      | 0       | 0       | 0      | S7   | Х | Х   | Х | Х    | Х   | Х | R4  |       |

| DBA               | global_calib_factor   | R/W   | 0  | 0   | 0    | 0     | 0  | 0   | 0  | 0  | 0  | 0   |       |        | 8-bit    | global | cal fac | tor     |        |      | Х | Х   | Х | Х    | Х   | Х | R5  |       |

| GLQ               | diagnostic (reserved) | R/W   | 0  | 0   | 0    | 0     | 0  | 0   | 0  | 0  | 0  | 0   | 0     | 0      | 0        | 0      | 0       | 0       | 0      | Z    | х | Х   | Х | Х    | Х   | Х | R6  |       |

|                   |                       |       |    |     |      |       |    |     |    |    |    |     |       |        |          |        |         |         |        |      |   |     |   |      |     |   |     |       |

|                   | CH0_switches_&_states | R/W   | 0  | 0   | 0    | 0     | 0  | 0   | 0  | QA | QB | SEN | SDEN  | SDHI   | S6       | S5     | S4      | S3      | S2     | S1   | Х | Х   | Х | Х    | Х   | Х | R7  |       |

|                   | CH1_switches_&_states | R/W   | 0  | 0   | 0    | 0     | 0  | 0   | 0  | QA | QB | SEN | SDEN  | SDHI   | S6       | S5     | S4      | S3      | S2     | S1   | Х | Х   | Х | Х    | Х   | Х | R8  |       |

|                   | CH2_switches_&_states | R/W   | 0  | 0   | 0    | 0     | 0  | 0   | 0  | QA | QB | SEN | SDEN  | SDHI   | S6       | S5     | S4      | S3      | S2     | S1   | Х | Х   | Х | Х    | Х   | Х | R9  |       |

|                   | CH3_switches_&_states | R/W   | 0  | 0   | 0    | 0     | 0  | 0   | 0  | QA | QB | SEN | SDEN  | SDHI   | S6       | S5     | S4      | S3      | S2     | S1   | Х | Х   | Х | Х    | Х   | Х | R10 |       |

|                   | CH0_DVH_calib_Z       | R/W   | 0  | 0   | 0    | 0     | 0  | 0   | 0  | 0  | 0  | 0   |       | 8-bit  | imped    | ance o | alibra  | tion co | de     |      | Х | Х   | Х | Х    | Х   | Х | R11 |       |

|                   | CH1_DVH_calib_Z       | R/W   | 0  | 0   | 0    | 0     | 0  | 0   | 0  | 0  | 0  | 0   |       | 8-bit  | imped    | ance o | alibra  | tion co | de     |      | Х | Х   | Х | Х    | Х   | Х | R12 |       |

|                   | CH2_DVH_calib_Z       | R/W   | 0  | 0   | 0    | 0     | 0  | 0   | 0  | 0  | 0  | 0   |       | 8-bit  | imped    | ance o | alibra  | tion co | de     |      | Х | Х   | Х | Х    | Х   | Х | R13 |       |

| SNC               | CH3_DVH_calib_Z       | R/W   | 0  | 0   | 0    | 0     | 0  | 0   | 0  | 0  | 0  | 0   |       | 8-bit  | imped    | ance o | alibra  | ion co  | de     |      | Х | Х   | Х | х    | Х   | Х | R14 |       |

| Ĕ                 | CH0_DVL_calib_Z       | R/W   | 0  | 0   | 0    | 0     | 0  | 0   | 0  | 0  | 0  | 0   |       | 8-bit  | imped    | ance o | alibra  | tion co | de     |      | Х | Х   | Х | Х    | Х   | Х | R15 |       |

| CHANNEL FUNCTIONS | CH1_DVL_calib_Z       | R/W   | 0  | 0   | 0    | 0     | 0  | 0   | 0  | 0  | 0  | 0   |       | 8-bit  | imped    | ance c | alibra  | ion co  | de     |      | Х | Х   | Х | х    | Х   | Х | R16 |       |

| Ē                 | CH2_DVL_calib_Z       | R/W   | 0  | 0   | 0    | 0     | 0  | 0   | 0  | 0  | 0  | 0   |       | 8-bit  | imped    | ance c | alibra  | ion co  | de     |      | Х | Х   | Х | х    | Х   | Х | R17 |       |

| NN                | CH3_DVL_calib_Z       | R/W   | 0  | 0   | 0    | 0     | 0  | 0   | 0  | 0  | 0  | 0   |       | 8-bit  | imped    | ance c | alibrat | ion co  | de     |      | х | х   | х | х    | х   | Х | R18 |       |

| CH/               | CH0_sw_calib_Z        | R/W   | 0  | 0   | 0    | 0     | 0  | 0   | 0  | 0  | 0  | 0   | 0     | 7      | '-bit in | npedar | nce cal | ibratio | n code | •    | Х | Х   | Х | Х    | Х   | Х | R19 |       |

|                   | CH1_sw_calib_Z        | R/W   | 0  | 0   | 0    | 0     | 0  | 0   | 0  | 0  | 0  | 0   | 0     | 7      | '-bit in | npedar | nce cal | ibratio | n code | •    | Х | Х   | Х | Х    | Х   | Х | R20 |       |

|                   | CH2_sw_calib_Z        | R/W   | 0  | 0   | 0    | 0     | 0  | 0   | 0  | 0  | 0  | 0   | 0     | 7      | '-bit in | npedar | nce cal | ibratio | n code | )    | Х | Х   | Х | Х    | Х   | Х | R21 |       |

|                   | CH3_sw_calib_Z        | R/W   | 0  | 0   | 0    | 0     | 0  | 0   | 0  | 0  | 0  | 0   | 0     | 7      | '-bit in | npedar | nce cal | ibratio | n code | )    | Х | Х   | Х | Х    | Х   | Х | R22 |       |

|                   | CH0_set_assign        | R/W   | 0  | 0   | 0    | 0     | 0  | 0   | 0  | 0  | 0  | 0   | set7  | set6   | set5     | set4   | set3    | set2    | set1   | set0 | Х | Х   | Х | Х    | Х   | Х | R23 |       |

|                   | CH1_set_assign        | R/W   | 0  | 0   | 0    | 0     | 0  | 0   | 0  | 0  | 0  | 0   | set7  | set6   | set5     | set4   | set3    | set2    | set1   | set0 | Х | Х   | Х | Х    | Х   | Х | R24 |       |

|                   | CH2_set_assign        | R/W   | 0  | 0   | 0    | 0     | 0  | 0   | 0  | 0  | 0  | 0   | set7  | set6   | set5     | set4   | set3    | set2    | set1   | set0 | Х | Х   | Х | Х    | Х   | Х | R25 |       |

|                   | CH3_set_assign        | R/W   | 0  | 0   | 0    | 0     | 0  | 0   | 0  | 0  | 0  | 0   | set7  | set6   | set5     | set4   | set3    | set2    | set1   | set0 | Х | Х   | Х | Х    | Х   | Х | R26 |       |

#### Notes:

1 Device part number = 7804 decimal = 0x1E7C hex

2 Rev A = 0x000, B = 0x001, ...

#### Table 3. Registers' Readback Bit Sequences

# Circuit Description (continued)

#### **Chip Functions**

| Register Name | no_op                                                                                                         | Function Address<br>Channel/Set Address<br>Channel Select Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0x00<br>don't care<br>0                                                                   | Set Select Bit<br>Mode                                                                    | 0 or 0<br>Write Only                                                                                                                                                                          |

|---------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Default Value | 0 0000 0000 0000                                                                                              | 0x00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                           | -                                                                                         |                                                                                                                                                                                               |

| Description   |                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                           |                                                                                           | LOAD is executed. It is useful if multiple<br>ut a parallel LOAD will occur for all devices on                                                                                                |

| Register Name | chip_id                                                                                                       | Function Address<br>Channel/Set Address<br>Channel Select Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0x01<br>don't care<br>0                                                                   | Set Select Bit<br>Mode                                                                    | 0 or 1<br>Read Only                                                                                                                                                                           |