AS5140H Data Sheet

# 10 Bit 360° Programmable Magnetic Rotary Encoder For High Ambient Temperatures

VDDV3V

Sin

Cos

**LDO 3.3V**

**Hall Array**

**Frontend**

**Amplifier**

**AS5140H**

# 1 General Description

The AS5140H is a contactless magnetic rotary encoder for accurate angular measurement over a full turn of 360° and over an extended ambient temperature range of -40°C to +150°C.

It is a system-on-chip, combining integrated Hall elements, analog front end and digital signal processing in a single device.

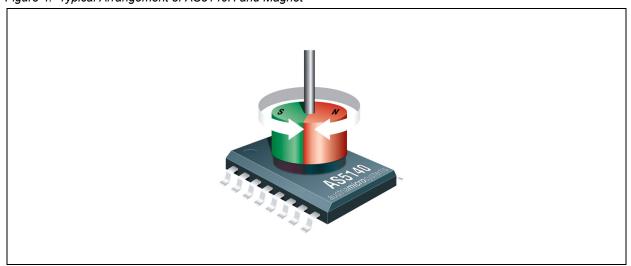

To measure the angle, only a simple two-pole magnet, rotating over the center of the chip, is required. The magnet may be placed above or below the IC.

The absolute angle measurement provides instant indication of the magnet's angular position with a resolution of 0.35° = 1024 positions per revolution. This digital data is available as a serial bit stream and as a PWM signal. Furthermore, a user-programmable incremental output is available.

An internal voltage regulator allows the AS5140H to operate at either 3.3 V or 5 V supplies.

The AS5140H is pin-compatible to the AS5040; however it uses low-voltage OTP programming cells with additional programming options.

Figure 1. Block Diagram

VDD5V -

# ■ Wide ambient temperature range: -40°C to +150°C 3 Applications The AS5140H is an ideal solution for automotive applications like engine compartment sensors, transmission gearbox encoder, throttle valve position control and for industrial applications like rotary sensors in high temperature environment. MagINCn MagDECn PWM Interface Absolute DO Absolute DO

CSN

CLK

A\_LSB\_U

B\_Dir\_V

Index\_W Proa

Interface

(SSI)

ĮĻ

ncrementa

Interface

Mag

# 2 Key Features

- Contactless high resolution rotational position encoding over a full turn of 360°

- Two digital 10-bit absolute outputs: Serial interface and Pulse width modulated (PWM) output

- Three incremental output modes: Quadrature A/B and Index output signal, Step / Direction and Index output signal, 3-phase commutation for brushless DC motors

- User programmable zero / index position

- Failure detection mode for magnet placement monitoring and loss of power supply

- Rotational speeds up to 10,000 rpm

- Pushbutton functionality detects movement of magnet in Z-axis

- Serial read-out of multiple interconnected AS5140H devices using Daisy Chain mode

- Fully automotive qualified to AEC-Q100, grade 0

**OTP**

Register

Programming

Parameters

# **Contents**

| 1 | General Description                               | 1   |

|---|---------------------------------------------------|-----|

| 2 | Key Features                                      | 1   |

| 3 | Applications                                      | 1   |

| 4 | Pin Assignments                                   | 4   |

|   | Pin Descriptions                                  | 4   |

| 5 | Absolute Maximum Ratings                          | 6   |

| 6 | Electrical Characteristics                        | 7   |

|   | Timing Characteristics                            | 10  |

| 7 | Detailed Description                              | 12  |

|   | 10-bit Absolute Angular Position Output           |     |

|   | Synchronous Serial Interface (SSI)                |     |

|   | Daisy Chain Mode                                  |     |

|   | Incremental Outputs                               | 15  |

|   | Quadrature A/B Output (Quad A/B Mode)             | 15  |

|   | LSB Output (Step/Direction Mode)                  | 16  |

|   | Incremental Output Hysteresis                     | 17  |

|   | Pulse Width Modulation (PWM) Output               |     |

|   | Analog Output                                     |     |

|   | Brushless DC Motor Commutation Mode               |     |

|   | Programming the AS5140H                           |     |

|   | OTP Memory Assignment                             |     |

|   | User Selectable Settings                          |     |

|   | OTP Default Setting  Redundant Programming Option |     |

|   | OTP Register Entry and Exit Condition             |     |

|   | Incremental Mode Programming                      |     |

|   | Zero Position Programming                         |     |

|   | Alignment Mode                                    |     |

|   | 3.3V / 5V Operation                               |     |

|   | Choosing the Proper Magnet                        |     |

|   | Physical Placement of the Magnet                  | 26  |

|   | Simulation Modeling                               | 27  |

|   | Failure Diagnostics                               | 28  |

|   | Magnetic Field Strength Diagnosis                 | 28  |

|   | Power Supply Failure Detection                    | 28  |

|   | Angular Output Tolerances                         | 29  |

|   | Accuracy                                          |     |

|   | Transition Noise                                  |     |

|   | High Speed Operation                              |     |

|   | Propagation Delays                                |     |

|   | Internal Timing Tolerance                         |     |

| 8 | ·                                                 | 34  |

| - | • •                                               | 34  |

|   | AS5140H Differences to AS5040                     | 34  |

|   | 7.00 (170)   Dillicitation to A00070              | J-1 |

# AS5140H

Data Sheet - Applications

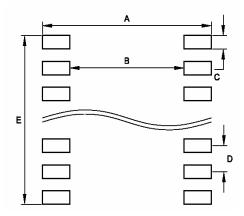

| 9  | Package Drawings and Markings | 35 |

|----|-------------------------------|----|

|    | Recommended PCB Footprint     | 36 |

| 10 | Ordering Information          | 37 |

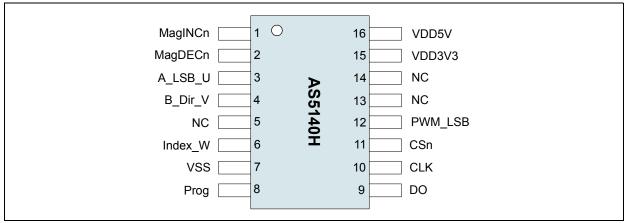

# 4 Pin Assignments

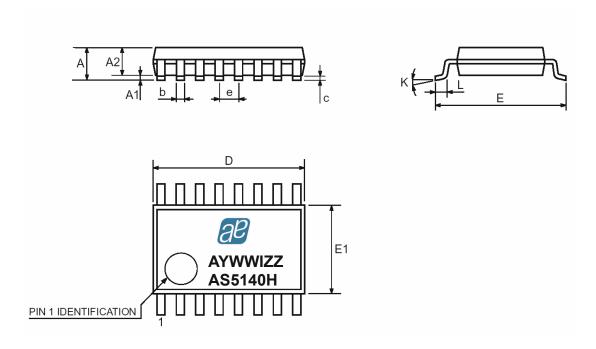

Figure 2. Pin Assignments (Top View)

# **Pin Descriptions**

The following table shows the description of each pin of the standard SSOP16 package (Shrink Small Outline Package, 16 leads, body size: 5.3mm x 6.2mmm; See Figure 2).

Table 1. Pin Descriptions

| Pin Name | Pin Number | Description                                                                                                                                                                        |

|----------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MagINCn  | 1          | Magnet Field Magnitude Increase. Active low. Indicates a distance reduction between the magnet and the device surface.                                                             |

| MagDECn  | 2          | Magnet Field Magnitude Decrease. Active low. Indicates a distance increase between the device and the magnet.                                                                      |

| A_LSB_U  | 3          | Mode1.x: Quadrature A channel Mode2.x: Least Significant Bit Mode3.x: U signal (phase1)                                                                                            |

| B_Dir_V  | 4          | Mode1.x: Quadrature B channel quarter period shift to channel A Mode2.x: Direction of Rotation Mode3.x: V signal (phase2)                                                          |

| NC       | 5          | For internal use. Must be left unconnected.                                                                                                                                        |

| Index_W  | 6          | Mode1.x and Mode2.x: Index signal indicates the absolute zero position Mode3.x: W signal (phase3)                                                                                  |

| VSS      | 7          | Negative Supply Voltage (GND).                                                                                                                                                     |

| Prog     | 8          | OTP Programming Input and Data Input for Daisy Chain mode. Internal pull-down resistor ( $\sim$ 74k $\Omega$ ). May be connected to VSS if programming is not used.                |

| DO       | 9          | Data Output of Synchronous Serial Interface.                                                                                                                                       |

| CLK      | 10         | SSI Clock Input. Schmitt-Trigger input.                                                                                                                                            |

| CSn      | 11         | Chip Select. Active low; Schmitt-Trigger input, internal pull-up resistor $(\sim 50 k\Omega)$ connect to VSS in incremental mode (see Incremental Power-up Lock Option on page 16) |

| PWM_LSB  | 12         | Pulse Width Modulation of approx. 1kHz; LSB in Mode3.x                                                                                                                             |

| NC       | 13         | For internal use. Must be left unconnected.                                                                                                                                        |

| NC       | 14         | For internal use. Must be left unconnected.                                                                                                                                        |

Table 1. Pin Descriptions

| Pin Name | Pin Number | Description                         |

|----------|------------|-------------------------------------|

| VDD3V3   | 15         | 3V-Regulator Output (see Figure 17) |

| VDD5V    | 16         | Positive Supply Voltage 5V          |

Pins 1 and 2 are the magnetic field change indicators, MagINCn and MagDECn (magnetic field strength increase or decrease through variation of the distance between the magnet and the device). These outputs can be used to detect the valid magnetic field range. Furthermore those indicators can also be used for contact-less push-button functionality. Pins 3, 4 and 6 are the incremental pulse output pins. The functionality of these pins can be configured through programming the one-time programmable (OTP) register:

Table 2. Pin Assignment for Different Incremental Output Modes

| Output Mode         | Pin 3 | Pin 4     | Pin 6 | Pin 12 |

|---------------------|-------|-----------|-------|--------|

| 1.x: Quadrature     | А     | В         | Index | PWM    |

| 2.x: Step/direction | LSB   | Direction | Index | PWM    |

| 3.x: Commutation    | U     | V         | W     | LSB    |

#### Mode 1.x: Quadrature A/B Output

Represents the default quadrature A/B signal mode.

# Mode 2.x: Step / Direction Output

Configures pin 3 to deliver up to 512 pulses (up to 1024 state changes) per revolution. It is equivalent to the LSB (least significant bit) of the absolute position value. Pin 4 provides the information of the rotational direction.

**Note:** Both modes (mode 1.x and mode 2.x) provide an index signal (1 pulse/revolution) with an adjustable width of one LSB or three LSB's.

#### Mode 3.x: Brushless DC Motor Commutation Mode

In addition to the absolute encoder output over the SSI interface, this mode provides commutation signals for brushless DC motors with either one pole pair or two pole pair rotors. The commutation signals are usually provided by 3 discrete Hall switches, which are no longer required, as the AS5140H can fulfill two tasks in parallel: absolute encoder + BLDC motor commutation. In this mode,

- Pin 12 provides the LSB output instead of the PWM (Pulse-Width-Modulation) signal.

- Pin 8 (Prog) is also used to program the different incremental interface modes, the incremental resolution and the zero position into the OTP (see page 22). This pin is also used as digital input to shift serial data through the device in Daisy Chain configuration, (see page 15).

- Pin 11 Chip Select (CSn; active low) selects a device within a network of AS5140H encoders and initiates serial data transfer. A logic high at CSn puts the data output pin (DO) to tri-state and terminates serial data transfer. This pin is also used for alignment mode (see page 24) and programming mode (see page 20).

- Pin 12 allows a single wire output of the 10-bit absolute position value. The value is encoded into a pulse width modulated signal with 1µs pulse width per step (1µs to 1024µs over a full turn). By using an external low pass filter, the digital PWM signal is converted into an analog voltage, allowing a direct replacement of potentiometers.

# **5 Absolute Maximum Ratings**

Stresses beyond those listed in Table 3 may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in Electrical Characteristics on page 7 is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 3. Absolute Maximum Ratings

| Parameter                            | Min  | Max  | Units | Comments                                                                   |

|--------------------------------------|------|------|-------|----------------------------------------------------------------------------|

| DC supply voltage at pin VDD5V       | -0.3 | 7    | V     |                                                                            |

| DC supply voltage at pin VDD3V3      | -0.3 | 5    | V     |                                                                            |

| Input pin voltage                    | -0.3 | 7    | V     | Pins Prog, MagINCn, MagDECn, CLK, CSn                                      |

| Input current (latchup immunity)     | -100 | 100  | mA    | Norm: JEDEC 78                                                             |

| Electrostatic discharge              |      | ±2   | kV    | Norm: MIL 883 E method 3015                                                |

| Storage temperature                  | -55  | +150 | °C    |                                                                            |

| Body temperature (Lead-free package) |      | 260  | °C    | t=20 to 40s, Norm: IPC/JEDEC J-Std-020C<br>Lead finish 100% Sn "matte tin" |

| Humidity non-condensing              | 5    | 85   | %     |                                                                            |

| Ambient temperature                  | -40  | 150  | °C    |                                                                            |

# **6 Electrical Characteristics**

$\mathsf{TAMB} = -40 \text{ to } 150^{\circ}\mathsf{C}, \ \mathsf{VDD5V} = 3.0 - 3.6 \mathsf{V} \ (3 \mathsf{V} \ \mathsf{operation}) \ \mathsf{VDD5V} = 4.5 - 5.5 \mathsf{V} \ (5 \mathsf{V} \ \mathsf{operation}), \ \mathsf{unless} \ \mathsf{otherwise} \ \mathsf{noted}.$

| Table 4   | <b>Flectrical</b> | Characteristics   |

|-----------|-------------------|-------------------|

| I abic T. | Liccincai         | Orial actoristics |

| Symbol               | Parameter                                                         | Conditions                                                                                                                                                                    | Min  | Тур   | Max    | Units      |

|----------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------|------------|

| RES                  | Resolution <sup>1</sup>                                           | 0.352 deg                                                                                                                                                                     |      |       | 10     | bit        |

|                      | 7 bit                                                             |                                                                                                                                                                               |      | 2.813 |        |            |

| LSB                  | 8 bit                                                             | Adjustable resolution only available for incremental output modes;                                                                                                            |      | 1.406 |        | dog        |

| LOB                  | 9 bit                                                             | Least significant bit, minimum step                                                                                                                                           |      | 0.703 |        | deg        |

|                      | 10 bit                                                            |                                                                                                                                                                               |      | 0.352 |        |            |

| INL <sub>opt</sub>   | Integral non-linearity (optimum) <sup>2</sup>                     | Maximum error with respect to the best line fit.  Verified at optimum magnet placement, TAMB =25°C                                                                            |      |       | ±0.5   | deg        |

| INL <sub>temp</sub>  | Integral non-linearity (optimum)                                  | Maximum error with respect to the best line fit.  Verified at optimum magnet placement, TAMB = -40 to +150°C                                                                  |      |       | ±0.9   | deg        |

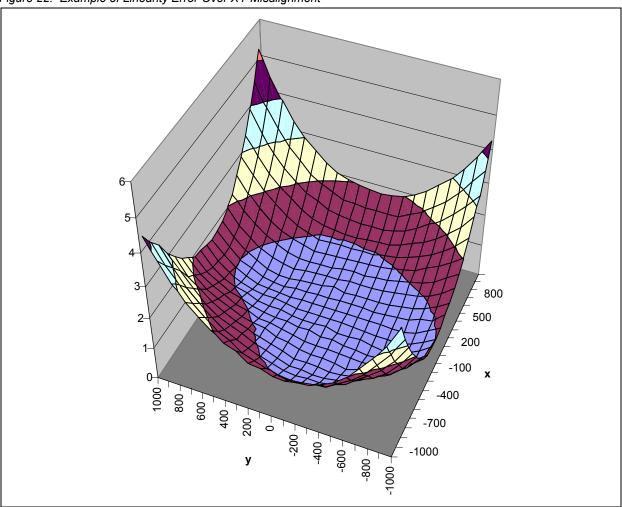

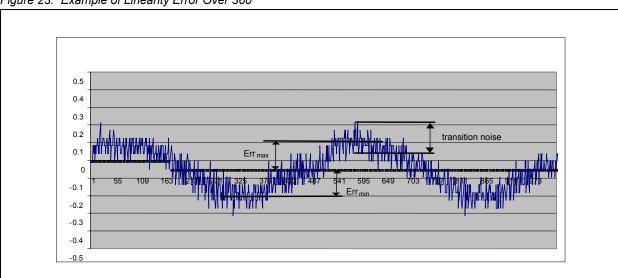

| INL                  | Integral non-linearity                                            | Best line fit = (Err <sub>max</sub> – Err <sub>min</sub> ) / 2<br>Over displacement tolerance with<br>6mm diameter magnet, T <sub>AMB</sub> = -40<br>to +150°C (see Figure 3) |      |       | ±1.4   | deg        |

| DNL                  | Differential non-linearity <sup>3</sup>                           | 10bit, no missing codes                                                                                                                                                       |      |       | ±0.176 | deg        |

| TN                   | Transition noise <sup>4</sup>                                     | RMS equivalent to 1 sigma                                                                                                                                                     |      |       | 0.12   | Deg<br>RMS |

| Hyst                 | Hysteresis                                                        | Incremental modes only                                                                                                                                                        |      | 0.704 |        | deg        |

| V <sub>on</sub>      | Power-on reset thresholds<br>On voltage; 300mV typ.<br>hysteresis | DC auanty voltage 2 21/ (1/DD21/2)                                                                                                                                            | 1,37 | 2.2   | 2.9    | V          |

| V <sub>off</sub>     | Power-on reset thresholds Off voltage; 300mV typ. hysteresis      | DC supply voltage 3.3V (VDD3V3)                                                                                                                                               | 1.08 | 1.9   | 2.6    | V          |

| t <sub>PwrUp</sub>   | Power-up time                                                     | Until offset compensation finished                                                                                                                                            |      |       | 50     | ms         |

| t <sub>delay</sub>   | System propagation delay absolute output                          | Includes delay of ADC and DSP                                                                                                                                                 |      |       | 48     | μs         |

|                      | System propagation delay incremental output                       | Calculation over two samples                                                                                                                                                  |      |       | 192    | μs         |

|                      | Sampling rate for absolute                                        | Internal sampling rate, TAMB = 25°C                                                                                                                                           | 9.90 | 10.42 | 10.94  |            |

| f <sub>S</sub>       | output                                                            | Internal sampling rate, TAMB = -40 to +150°C                                                                                                                                  | 9.38 | 10.42 | 11.46  | kHz        |

| CLK                  | Read-out frequency                                                | Max. clock frequency to read out serial data                                                                                                                                  |      |       | 1      | MHz        |

| Operating Conditions |                                                                   |                                                                                                                                                                               |      |       |        |            |

| I <sub>supp</sub>    | Supply current                                                    |                                                                                                                                                                               |      | 16    | 21     | mA         |

| VDD5V                | External supply voltage at pin VDD5V                              | 5V operation                                                                                                                                                                  | 4.5  | 5.0   | 5.5    | V          |

| VDD3V3               | Internal regulator output voltage at pin VDD3V3                   | - 1 5p 31 duo.                                                                                                                                                                | 3.0  | 3.3   | 3.6    | V          |

Table 4. Electrical Characteristics (Continued)

| Symbol                               | Parameter                                            | Conditions                                                   | Min            | Тур                  | Max            | Units |

|--------------------------------------|------------------------------------------------------|--------------------------------------------------------------|----------------|----------------------|----------------|-------|

| VDD5V                                | External supply voltage at pin                       | 3.3V operation                                               | 3.0            | 3.3                  | 3.6            | V     |

| VDD3V3                               | VDD5V,VDD3V3                                         | (pins VDD5V and VDD3V3 connected)                            | 3.0            | 3.3                  | 3.6            | V     |

| t <sub>pwrup3</sub>                  | External VDD3V3 supply voltage rise time at power-up | 10%-90% level in 3.3V mode (pins VDD5V and VDD3V3 connected) | 1              |                      | 150            | μs    |

| DC Charac                            | teristics for Digital Inputs and                     | Outputs                                                      | •              |                      |                |       |

|                                      | CMOS Schmitt-Tri                                     | gger Inputs: CLK, CSn (CSn = interna                         | l Pull-up)     |                      |                |       |

| VIH                                  | High level input voltage                             | Normal operation                                             | 0.7 *<br>VDD5V |                      |                | V     |

| VIL                                  | Low level input voltage                              |                                                              |                |                      | 0.3 *<br>VDD5V | V     |

| $V_{\text{lon}}$ - $V_{\text{loff}}$ | Schmitt Trigger hysteresis                           |                                                              | 1              |                      |                | V     |

| ILEAK                                | Input leakage current                                | CLK only                                                     | -1             |                      | 1              |       |

| l <sub>iL</sub>                      | Pull-up low level input current                      | CSn only, VDD5V:5.0V                                         | -30            |                      | -100           | μA    |

|                                      | (                                                    | CMOS / Program Input: Prog                                   | 1              |                      | •              |       |

| VIH                                  | High level input voltage                             |                                                              | 0.7 *<br>VDD5V |                      | 5              | V     |

| V <sub>PROG</sub>                    | High level input voltage                             | During programming                                           | Refer          | to Progr<br>Conditio | ramming<br>ns  | >     |

| VIL                                  | Low level input voltage                              |                                                              |                |                      | 0.3 *<br>VDD5V | ٧     |

| l <sub>iL</sub>                      | Pull-down high level input current                   | VDD5V:5.5V                                                   |                |                      | 100            | μΑ    |

|                                      | CMOS Ou                                              | tput Open Drain: MagINCn, MagDEC                             | n              |                      |                |       |

| V <sub>OL</sub>                      | Low level output voltage                             |                                                              |                |                      | Vss+0.4        | V     |

| 1-                                   | Outrout accoment                                     | VDD5V:4.5V                                                   |                |                      | 4              | Л     |

| lo                                   | Output current                                       | VDD5V:3V                                                     |                |                      | 2              | mA    |

| loz                                  | Open drain leakage current                           |                                                              |                |                      | 1              | μA    |

|                                      | CN                                                   | MOS Output: A, B, Index, PWM                                 |                |                      |                |       |

| Vон                                  | High level output voltage                            |                                                              | VDD5V<br>-0.5  |                      |                | V     |

| V <sub>OL</sub>                      | Low level output voltage                             |                                                              |                |                      | Vss+0.4        | V     |

|                                      | 0.10.10.0001                                         | VDD5V:4.5V                                                   |                |                      | 4              |       |

| lo                                   | Output current                                       | VDD5V:3V                                                     |                |                      | 2              | mA    |

|                                      | ı                                                    | Tristate CMOS Output: DO                                     |                |                      | 1              |       |

| Vон                                  | High level output voltage                            |                                                              | VDD5V<br>-0.5  |                      |                | V     |

| V <sub>OL</sub>                      | Low level output voltage                             |                                                              |                |                      | Vss+0.4        | V     |

|                                      |                                                      | VDD5V:4.5V                                                   |                |                      | 4              | _     |

| I <sub>O</sub>                       | Output current                                       | VDD5V:3V                                                     |                |                      | 2              | mA    |

| I <sub>OZ</sub>                      | Tri-state leakage current                            |                                                              |                |                      | 1              | μΑ    |

| Magnetic Ir                          | nput Specification (Two-pole cyl                     | lindrical diametrically magnetized sou                       | rce)           |                      |                |       |

| d <sub>mag</sub>                     | Diameter                                             | Recommended magnet: Ø 6mm x                                  | 4              | 6                    |                | mm    |

|                                      | Thickness                                            | 2.5mm for cylindrical magnets                                | 2.5            |                      |                | mm    |

Table 4. Electrical Characteristics (Continued)

| Symbol                        | Parameter                            | Conditions                                                                                                                                 | Min  | Тур    | Max    | Units |

|-------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------|--------|--------|-------|

| B <sub>pk</sub>               | Magnetic input field amplitude       | Required vertical component of the magnetic field strength on the die's surface, measured along a concentric circle with a radius of 1.1mm | 45   |        | 75     | mT    |

| B <sub>off</sub>              | Magnetic offset                      | Constant magnetic stray field                                                                                                              |      |        | ±10    | mT    |

|                               | Field non-linearity                  | Including offset gradient                                                                                                                  |      |        | 5      | %     |

| f <sub>mag_abs</sub>          | Input frequency (rotational          | Absolute mode: 600 rpm @ readout of 1024 positions (see Table 9)                                                                           |      |        | 10     | Hz    |

| f <sub>mag_inc</sub>          | speed of magnet)                     | Incremental mode: no missing pulses at rotational speeds of up to 10,000 rpm (see Table 9)                                                 |      |        | 166    | Hz    |

| Disp                          | Displacement Radius                  | Max. X-Y offset between defined IC package center and magnet axis (see Figure 19)                                                          |      |        | 0.25   | mm    |

|                               |                                      | Max. X-Y offset between chip center and magnet axis                                                                                        |      |        | 0.485  |       |

|                               | Chip placement tolerance             | Placement tolerance of chip within IC package (see Figure 21)                                                                              |      |        | ±0.235 | mm    |

|                               | Recommended magnet                   | NdFeB (Neodymium Iron Boron)                                                                                                               |      | -0.12  |        | %/K   |

|                               | material and temperature drift       | SmCo (Samarium Cobalt)                                                                                                                     |      | -0.035 |        | /0/1  |

| Programmi                     | ing Conditions                       |                                                                                                                                            |      |        |        |       |

| $V_{PROG}$                    | Programming voltage                  | Voltage applied during programming                                                                                                         | 3.0  | 3.3    | 3.6    | V     |

| $V_{ProgOff}$                 | Programming voltage off level        | Line must be discharged to this level                                                                                                      | 0    |        | 1      | V     |

| I <sub>PROG</sub>             | Programming current                  | Current during programming                                                                                                                 |      |        | 100    | mA    |

| R <sub>programme</sub>        | Programmed fuse resistance (log 1)   | 10μA max. current @ 100mV                                                                                                                  | 100k |        | ∞      | Ω     |

| R <sub>unprogram</sub><br>med | Unprogrammed fuse resistance (log 0) | 2mA max. current @ 100mV                                                                                                                   | 50   |        | 100    | Ω     |

| t <sub>PROG</sub>             | Programming time per bit             | Time to prog. a singe fuse bit                                                                                                             | 10   |        | 20     | μs    |

| t <sub>CHARGE</sub>           | Refresh time per bit                 | Time to charge the cap after t <sub>PROG</sub>                                                                                             | 1    |        |        | μs    |

| f <sub>LOAD</sub>             | LOAD frequency                       | Data can be loaded at n*2µs                                                                                                                |      |        | 500    | kHz   |

| f <sub>READ</sub>             | READ frequency                       | Read the data from the latch                                                                                                               |      |        | 2.5    | MHz   |

| f <sub>WRITE</sub>            | WRITE frequency                      | Write the data to the latch                                                                                                                |      |        | 2.5    | MHz   |

- 1. Digital Interface

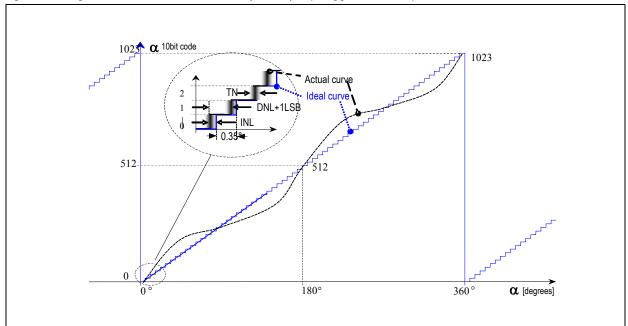

- 2. Integral Non-Linearity (INL) is the maximum deviation between actual position and indicated position.

- 3. Differential Non-Linearity (DNL) is the maximum deviation of the step length from one position to the next.

- 4. Transition Noise (TN) is the repeatability of an indicated position.

# **Timing Characteristics**

TAMB = -40 to +150 °C, VDD5V = 3.0-3.6V (3V operation) VDD5V = 4.5-5.5V (5V operation), unless otherwise noted.

Table 5. Timing Characteristics

| Symbol                                        | Parameter                                | Conditions                                                                          | Min   | Тур   | Max   | Units |

|-----------------------------------------------|------------------------------------------|-------------------------------------------------------------------------------------|-------|-------|-------|-------|

| Synchron                                      | ous Serial Interface (SSI)               |                                                                                     |       |       |       |       |

| t <sub>DO active</sub>                        | Data output activated (logic high)       | Time between falling edge of CSn and data output activated                          |       |       | 100   | ns    |

| t <sub>CLK FE</sub>                           | First data shifted to output register    | Time between falling edge of CSn and first falling edge of CLK                      | 500   |       |       | ns    |

| T <sub>CLK/2</sub>                            | Start of data output                     | Rising edge of CLK shifts out one bit at a time                                     | 500   |       |       | ns    |

| t <sub>DO valid</sub>                         | Data output valid                        | Time between rising edge of CLK and data output valid                               | 357   | 375   | 394   | ns    |

| t <sub>DO tristate</sub>                      | Data output tristate                     | After the last bit DO changes back to "tristate"                                    |       |       | 100   | ns    |

| t <sub>CSn</sub>                              | Pulse width of CSn                       | CSn =high; To initiate read-out of next angular position                            | 500   |       |       | ns    |

| f <sub>CLK</sub>                              | Read-out frequency                       | Clock frequency to read out serial data                                             | >0    |       | 1     | MHz   |

| Pulse Wid                                     | th Modulation Output                     |                                                                                     |       |       |       |       |

| f <sub>PWM</sub>                              | PWM frequency                            | Signal period = 1025µs ±5% at T <sub>amb</sub> = 25°C                               | 0.927 | 0.976 | 1.024 | kHz   |

|                                               |                                          | Signal period =1025µs ±10% at T <sub>amb</sub> = -40 to +150°C                      | 0.878 | 0.976 | 1.074 | KMZ   |

| $PW_{MIN}$                                    | Minimum pulse width                      | Position 0d; angle 0 degree                                                         | 0.95  | 1     | 1.05  | μs    |

| PW <sub>MAX</sub>                             | Maximum pulse width                      | Position 1023d; angle 359.65 degree                                                 | 973   | 1024  |       | μs    |

| Increment                                     | al Outputs                               |                                                                                     |       | •     |       |       |

| t <sub>Incrementa</sub><br>I outputs<br>valid | Incremental outputs valid after power-up | Time between first falling edge of CSn after power-up and valid incremental outputs |       |       | 500   | ns    |

| t <sub>Dir valid</sub>                        | Directional indication valid             | Time between rising or falling edge of LSB output and valid directional indication  |       |       | 500   | ns    |

Figure 3. Integral and Differential Non-Linearity Example (exaggerated curve)

# 7 Detailed Description

The AS5140H is manufactured in a CMOS standard process and uses a spinning current Hall technology for sensing the magnetic field distribution across the surface of the chip. The integrated Hall elements are placed around the center of the device, and deliver a voltage representation of the magnetic field at the surface of the IC. Through Sigma-Delta Analog / Digital Conversion and Digital Signal-Processing (DSP) algorithms, the AS5140H provides accurate high-resolution absolute angular position information. For this purpose, a Coordinate Rotation Digital Computer (CORDIC) calculates the angle and the magnitude of the Hall array signals. The DSP is also used to provide digital information at the outputs MagINCn and MagDECn that indicate movements of the used magnet towards or away from the device's surface. A small low cost diametrically magnetized (two-pole) standard magnet provides the angular position information (see Figure 18).

The AS5140H senses the orientation of the magnetic field and calculates a 10-bit binary code. This code can be accessed via a Synchronous Serial Interface (SSI). In addition, an absolute angular representation is given by a Pulse Width Modulated signal at pin 12 (PWM). Simultaneously, the device also provides incremental output signals. The various incremental output modes can be selected by programming the OTP mode register bits (see Table 10). As long as no programming voltage is applied to pin Prog, the new setting may be overwritten at any time and will be reset to default when power is turned off. To make the setting permanent, the OTP register must be programmed. The default setting is a quadrature A/B mode including the Index signal with a pulse width of 1 LSB. The Index signal is logic high at the user programmable zero position.

The AS5140H is tolerant to magnet misalignment and magnetic stray fields due to differential measurement technique and Hall sensor conditioning circuitry.

Figure 4. Typical Arrangement of AS5140H and Magnet

# 10-bit Absolute Angular Position Output

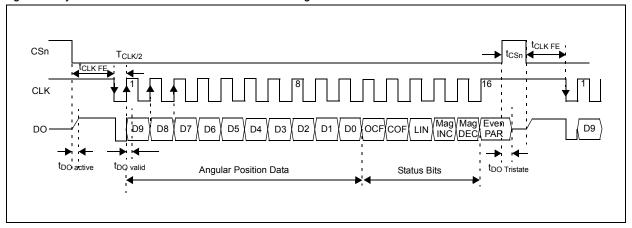

#### Synchronous Serial Interface (SSI)

If CSn changes to logic low, Data Out (DO) will change from high impedance (tri-state) to logic high and the read-out will be initiated.

- After a minimum time t<sub>CLK</sub> FE, data is latched into the output shift register with the first falling edge of CLK.

- Each subsequent rising CLK edge shifts out one bit of data.

- The serial word contains 16 bits; the first 10 bits are the angular information D[9:0], the subsequent 6 bits contain system information about the validity of data such as OCF, COF, LIN, Parity and Magnetic Field status (increase/decrease).

- A subsequent measurement is initiated by a log "high" pulse at CSn with a minimum duration of t<sub>CSn</sub>.

Figure 5. Synchronous Serial Interface with Absolute Angular Position Data

#### Data Content

**D9:D0** – Absolute angular position data (MSB is clocked out first).

**OCF** – (Offset Compensation Finished). Logic high indicates the finished Offset Compensation Algorithm. For fast startup, this bit may be polled by the external microcontroller. As soon as this bit is set, the AS5140H has completed the startup and the data is valid (see Table 7).

**COF** – (Cordic Overflow). Logic high indicates an out of range error in the CORDIC part. When this bit is set, the data at D9:D0 is invalid. The absolute output maintains the last valid angular value. This alarm may be resolved by bringing the magnet within the X-Y-Z tolerance limits.

**LIN** – (Linearity Alarm). Logic high indicates that the input field generates a critical output linearity. When this bit is set, the data at D9:D0 may still be used, but can contain invalid data. This warning may be resolved by bringing the magnet within the X-Y-Z tolerance limits.

**MagINCn** – (Magnitude Increase) becomes HIGH, when the magnet is pushed towards the IC, thus increasing the magnetic field strength.

**MagDECn** – (Magnitude Decrease) becomes HIGH, when the magnet is pulled away from the IC, thus decreasing the magnetic field strength.

Signal "HIGH" for both MagINCn and MagDECn indicate a magnetic field that is out of the allowed range (see Table 6).

Table 6. Magnetic Magnitude Variation Indicator

| MagINCn | MagDECn | Description                                                                                                                         |

|---------|---------|-------------------------------------------------------------------------------------------------------------------------------------|

| 0       | 0       | No distance change<br>Magnetic Input Field OK (in range)                                                                            |

| 0       | 1       | Distance increase: Pull-function. This state is dynamic, it is only active while the magnet is moving away from the chip in Z-axis. |

| 1       | 0       | Distance decrease: Push- function. This state is dynamic, it is only active while the magnet is moving towards the chip in Zaxis.   |

| 1       | 1       | Magnetic Input Field invalid – out of range: Too large, Too small (missing magnet).                                                 |

**Note:** Pins 1 and 2 (MagINCn, MagDECn) are open drain outputs and require external pull-up resistors. If the magnetic field is in range, both outputs are turned off.

The two pins may also be combined with a single pull-up resistor. In this case, the signal is high when the magnetic field is in range. It is low in all other cases (see Table 6).

Even Parity – A bit for transmission error detection of bits 1to 15 (D9 to D0, OCF, COF, LIN, MagINCn, MagDECn).

The absolute angular output is always set to a resolution of 10 bit. Placing the magnet above the chip, angular values increase in clockwise direction by default. Data D9:D0 is valid, when the status bits have the following configurations:

Table 7. Status Bit Outputs

| OCF | COF | LIN | MagINCn | MagDECn | Parity                     |

|-----|-----|-----|---------|---------|----------------------------|

|     |     |     | 0       | 0       |                            |

| 1   | 0   | 0   | 0       | 1       | even checksum of bits 1:15 |

|     |     |     | 1       | 0       |                            |

The absolute angular position is sampled at a rate of 10kHz (0.1ms). This allows reading of all 1024 positions per 360 degrees within 0.1 seconds = 9.76Hz (~10Hz) without skipping any position. Multiplying 10Hz by 60, results the corresponding maximum rotational speed of 600 rpm. Readout of every second angular position allows for rotational speeds of up to 1200 rpm.

Consequently, increasing the rotational speed reduces the number of absolute angular positions per revolution (see Table 11). Regardless of the rotational speed or the number of positions to be read out, the absolute angular value is always given at the highest resolution of 10 bit.

The incremental outputs are not affected by rotational speed restrictions due to the implemented interpolator. The incremental output signals may be used for high-speed applications with rotational speeds of up to 10,000 rpm without missing pulses.

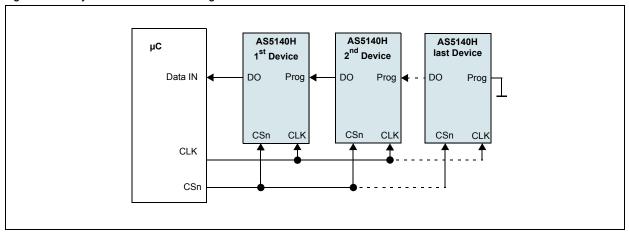

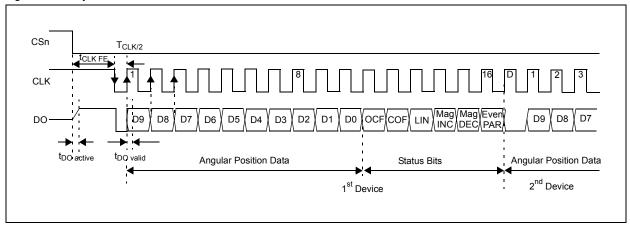

# **Daisy Chain Mode**

The Daisy Chain mode allows connection of several AS5140H's in series, while still keeping just one digital input for data transfer (see "Data IN" in Figure 6 below). This mode is accomplished by connecting the data output (DO; pin 9) to the data input (Prog; pin 8) of the subsequent device. The serial data of all connected devices is read from the DO pin of the first device in the chain. The Prog pin of the last device in the chain should be connected to VSS. The length of the serial bit stream increases with every connected device. It is,

For example, 34 bit for two devices, 51 bit for three devices, etc.

The last data bit of the first device (Parity) is followed by a logic low bit and the first data bit of the second device (D9), etc. (see Figure 7).

Figure 6. Daisy Chain Hardware Configuration

Figure 7. Daisy Chain Mode Data Transfer

# Programming Daisy Chained Devices

In Daisy Chain mode, the Prog pin is connected directly to the DO pin of the subsequent device in the chain (see Figure 6). During programming (see Programming the AS5140H on page 20), a programming voltage of 7.5V must be applied to pin Prog. This voltage level exceeds the limits for pin DO, so one of the following precautions must be made during programming:

- Open the connection DO → Prog during programming, (or)

- Add a Schottky diode between DO and Prog (Anode = DO, Cathode = Prog)

Due to the parallel connection of CLK and CSn, all connected devices may be programmed simultaneously.

# **Incremental Outputs**

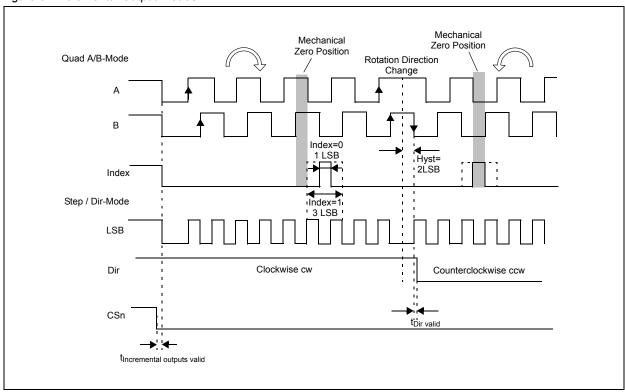

Three different incremental output modes are possible with quadrature A/B being the default mode. Figure 8 shows the two-channel quadrature as well as the step / direction incremental signal (LSB) and the direction bit in clockwise (CW) and counter-clockwise (CCW) direction.

# Quadrature A/B Output (Quad A/B Mode)

The phase shift between channel A and B indicates the direction of the magnet movement. Channel A leads channel B at a clockwise rotation of the magnet (top view) by 90 electrical degrees. Channel B leads channel A at a counter-clockwise rotation.

Figure 8. Incremental Output Modes

# LSB Output (Step/Direction Mode)

Output LSB reflects the LSB (least significant bit) of the programmed incremental resolution (OTP Register Bit Div0, Div1). Output Dir provides information about the rotational direction of the magnet, which may be placed above or below the device (1=clockwise; 0=counter clockwise; top view). Dir is updated with every LSB change. In both modes (quad A/B, step/direction), the resolution and the index output are user programmable. The index pulse indicates the zero position and is by default one angular step (1LSB) wide. However, it can be set to three LSBs by programming the Index-bit of the OTP register accordingly (see Table 10).

# Incremental Power-up Lock Option

After power-up, the incremental outputs can optionally be locked or unlocked, depending on the status of the CSn pin:

■ CSn = low at power-up: CSn has an internal pull-up resistor and must be externally pulled low ( $R_{ext} \le 5k\Omega$ ). If Csn is low at power-up, the incremental outputs (A, B, Index) will be high until the internal offset compensation is finished. This unique state (A=B=Index = high) may be used as an indicator for the external controller to shorten

the waiting time at power-up. Instead of waiting for the specified maximum power up-time (0), the controller can start requesting data from the AS5140H as soon as the state (A=B=Index = high) is cleared.

■ CSn = high or open at power-up: In this mode, the incremental outputs (A, B, Index) will remain at logic high state, until CSn goes low or a low pulse is applied at CSn. This mode allows intentional disabling of the incremental outputs until, for example the system microcontroller is ready to receive data.

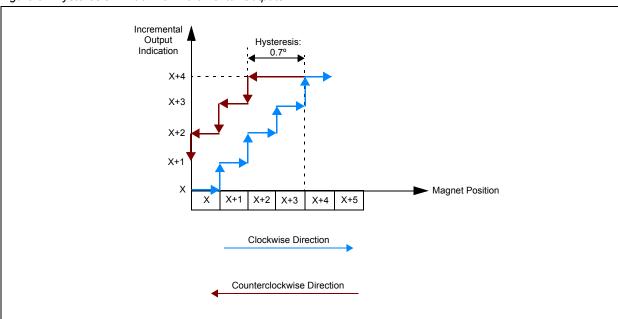

#### **Incremental Output Hysteresis**

To avoid flickering incremental outputs at a stationary magnet position, a hysteresis is introduced. In case of a rotational direction change, the incremental outputs have a hysteresis of 2 LSB. Regardless of the programmed incremental resolution, the hysteresis of 2 LSB always corresponds to the highest resolution of 10 bit. In absolute terms, the hysteresis is set to 0.704 degrees for all resolutions. For constant rotational directions, every magnet position change is indicated at the incremental outputs (see Figure 9). For example, if the magnet turns clockwise from position "x+3" to "x+4", the incremental output would also indicate this position accordingly. A change of the magnet's rotational direction back to position "x+3" means that the incremental output still remains unchanged for the duration of 2 LSB, until position "x+2" is reached. Following this direction, the incremental outputs will again be updated with every change of the magnet position.

Figure 9. Hysteresis Window for Incremental Outputs

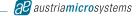

# **Pulse Width Modulation (PWM) Output**

The AS5140H provides a pulse width modulated output (PWM), whose duty cycle is proportional to the measured angle:

$$Position = \frac{t_{on} \cdot 1025}{(t_{on} + t_{off})} - 1$$

(EQ 2)

The PWM frequency is internally trimmed to an accuracy of  $\pm 5\%$  ( $\pm 10\%$  over full temperature range). This tolerance can be cancelled by measuring the complete duty cycle as shown above.

Figure 10. PWM Output Signal

Table 8. PWM Signal Parameters

| Symbol            | Parameter       | Тур    | Unit | Note                                   |

|-------------------|-----------------|--------|------|----------------------------------------|

| f <sub>PWM</sub>  | PWM frequency   | 0.9756 | kHz  | Signal period: 1025µs                  |

| PW <sub>MIN</sub> | MIN pulse width | 1      | μs   | - Position 0d<br>- Angle 0 deg         |

| PW <sub>MAX</sub> | MAX pulse width | 1024   | μs   | - Position 1023d<br>- Angle 359,65 deg |

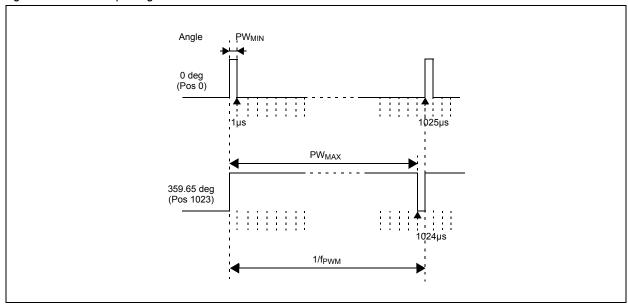

# **Analog Output**

An analog output may be generated by averaging the PWM signal, using an external active or passive lowpass filter. The analog output voltage is proportional to the angle:  $0^{\circ} = 0V$ ;  $360^{\circ} = VDD5V$ . Using this method, the AS5140H can be used as direct replacement of potentiometers.

Figure 11. Simple Passive 2<sup>nd</sup> Order Lowpass Filter

$$R1,R2 \ge 4k7$$

$C1,C2 \ge 1\mu F / 6V$  (EQ 3)

R1 should be  $\ge$ 4k7 to avoid loading of the PWM output. Larger values of Rx and Cx will provide better filtering and less ripple, but will also slow down the response time.

# **Brushless DC Motor Commutation Mode**

Brushless DC motors require angular information for stator commutation. The AS5140H provides U-V-W commutation signals for one and two pole pair motors. In addition to the three-phase output signals, the step (LSB) output at pin 12 allows high accuracy speed measurement. Two resolutions (9 or 10 bit) can be selected by programming Div0 according to Table 10.

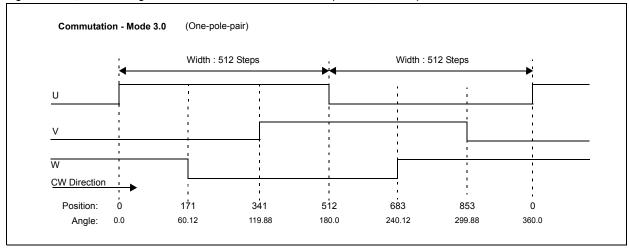

Mode 3.0 (3.1) is used for brush-less DC motors with one-pole pair rotors. The three phases (U, V, W) are 120 degrees apart, each phase is 180 degrees on and 180 degrees off.

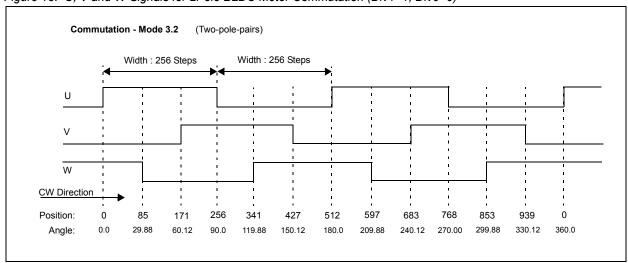

Mode 3.2 (3.3) is used for motors with two pole pairs requiring a higher pulse count to ensure a proper current commutation. In this case the pulse width is 256 positions, equal to 90 degrees. The precise physical angle at which the U, V and W signals change state ("Angle" in Figure 12 and Figure 13) is calculated by multiplying each transition position by the angular value of 1 count:

Angle [deg] = Position x (360 degree / 1024) (EQ 4)

Figure 12. U, V and V-Signals for BLDC Motor Commutation (Div1=0, Div0=0)

Figure 13. U, V and W-Signals for 2Pole BLDC Motor Commutation (Div1=1, Div0=0)

# **Programming the AS5140H**

**Note:** A detailed description of the austriamicrosystems low voltage polyfuse OTP programming method is given in Application Note AN5000-30, which can be downloaded from the austriamicrosystems website. The OTP programming description in this datasheet is for general information only.

After power-on, programming the AS5140H is enabled with the rising edge of CSn with Prog = high and CLK = low. The AS5140H programming is a one-time-programming (OTP) method, based on polysilicon fuses. The advantage of this method is that a programming voltage of only 3.3V is required for programming. The OTP consists of 52 bits, of which 21 bits are available for user programming. The remaining 31 bits contain factory settings and a unique chip identifier (Chip-ID).

A single OTP cell can be programmed only once. Per default, the cell is "0"; a programmed cell will contain a "1". While it is not possible to reset a programmed bit from "1" to "0", multiple OTP writes are possible, as long as only unprogrammed "0"-bits are programmed to "1". Independent of the OTP programming, it is possible to overwrite the OTP register temporarily with an OTP write command at any time. This setting will be cleared and overwritten with the hard programmed OTP settings at each power-up sequence or by a LOAD operation.

The OTP memory can be accessed in several ways:

- Load Operation: The Load operation reads the OTP fuses and loads the contents into the OTP register. Note that the Load operation is automatically executed after each power-on-reset.

- Write Operation: The Write operation allows a temporary modification of the OTP register. It does not program the OTP. This operation can be invoked multiple times, and will remain set while the chip is supplied with power and while the OTP register is not modified with another Write or Load operation.

- **Read Operation**: The Read operation reads the contents of the OTP register, for example to verify a Write command or to read the OTP memory after a Load command.

- **Program Operation**: The Program operation writes the contents of the OTP register permanently into the OTP ROM.

- Analog Readback Operation: The Analog Readback operation allows a quantifiable verification of the programming. For each programmed or unprogrammed bit, there is a representative analog value (in essence, a resistor value) that is read to verify whether a bit has been successfully programmed or not.

# **OTP Memory Assignment**

Table 9. OTP Bit Assignment

| Bit | Symbol     | Function                          |                  |  |

|-----|------------|-----------------------------------|------------------|--|

|     | mbit1      | Factory Bit                       |                  |  |

| 51  | Md0        |                                   |                  |  |

| 50  | Md1        |                                   |                  |  |

| 49  | Div0       | Incremental Output Mode Selection |                  |  |

| 48  | Div1       |                                   | c                |  |

| 47  | Index      |                                   | ctio             |  |

| 46  | Z0         |                                   | Customer Section |  |

| :   | :          | 10 bit Zero Position              | ome              |  |

| 37  | <b>Z</b> 9 |                                   | Cust             |  |

| 36  | CCW        | Direction                         | O                |  |

| 35  | RA0        |                                   |                  |  |

| :   | :          | Redundancy Address                |                  |  |

| 31  | RA4        |                                   |                  |  |

| 30  | FS 0       | Factory Bit                       | tion             |  |

| :   | FS 1       | Factory Bit                       | Seci             |  |

| 18  | FS 12      | Factory Bit                       | Factory Section  |  |

| 17  | ChipID0    |                                   | <b>C</b>         |  |

| 16  | ChipID1    | 18 bit Chip ID                    | ID Section       |  |

| :   | :          | 16 bit Only 10                    | Š                |  |

| 0   | ChipID17   |                                   | =                |  |

|     | mbit0      | Factory Bit                       |                  |  |

# **User Selectable Settings**

The AS5140H allows programming of the following user selectable options:

- Md1, Md0: Incremental Output Mode Selection.

- Div1, Div0: Divider Setting of Incremental Output.

- Index: Index Pulse Width Selection 1LSB / 3LSB.

- **Z [9:0]:** Programmable Zero / Index Position.

- CCW: Counter Clockwise Bit.

- ccw=0 angular value increases in clockwise direction.

- ccw=1 angular value increases in counterclockwise direction.

- RA [4:0]: Redundant Address. An OTP bit location addressed by this address is always set to "1" independent of the corresponding original OTP bit setting.

# **OTP Default Setting**

The AS5140H can also be operated without programming. The default, un-programmed setting is as listed below.

- Md0, MD1:00 = Incremental mode = quadrature.

- **Div0**, **Div1**:00 = Incremental resolution = 10bit.

- Index:0 = Index bit width = 1LSB.

- **Z9 to Z0**:00 = No programmed zero position.

- **CCW**:0 = Clockwise operation.

- RA4 to RA0:0 = No OTP bit is selected.

# **Redundant Programming Option**

In addition to the regular programming, a redundant programming option is available. This option allows that one selectable OTP bit can be set to "1" (programmed state) by writing the location of that bit into a 5-bit address decoder. This address can be stored in bits RA5..0 in the OTP user settings.

Example: Setting RA5...0 to "00001" will select bit 51 = MD0, "00010" selects bit 50 = MD1, "10000" selects bit 36 = CCW, etc.

# **OTP Register Entry and Exit Condition**

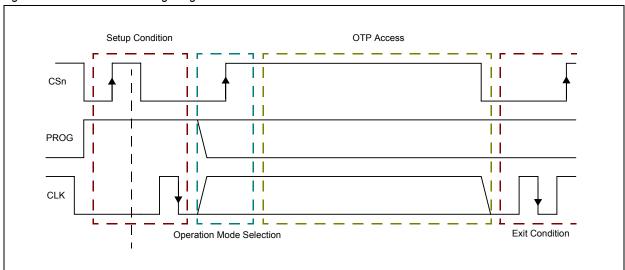

To avoid accidental modification of the OTP during normal operation, each OTP access (Load, Write, Read, Program) requires a defined entry and exit procedure, using the CSn, PROG and CLK signals as shown in Figure 14.

Figure 14. OTP Access Timing Diagram

# **Incremental Mode Programming**

The following three different incremental output modes are available:

- Mode: Md1=0 / Md0=1 sets the AS5140H in quadrature mode.

- Mode: Md1=1 / Md0=0 sets the AS5140H in step / direction mode (see Table 2).

In both modes listed above, the incremental resolution may be reduced from 10 bit down to 9, 8 or 7 bit using the divider OTP bits Div1 and Div0 (see Table 10 below).

■ Mode: Md1=1 / Md0=1 sets the AS5140H in brushless DC motor commutation mode with an additional LSB incremental signal at pin 12 (PWM\_LSB).

To allow programming of all bits, the default factory setting is all bits = 0. This mode is equal to mode 1:0 (quadrature A/B, 1LSB index width, 256ppr). The absolute angular output value, by default, increases with clockwise rotation of the magnet (top view). Setting the CCW-bit (see Table 9) allows for reversing the indicated direction, e.g. when the magnet is placed underneath the IC:

- CCW = 0 angular value increases clockwise;

- CCW = 1 angular value increases counterclockwise.

By default, the zero / index position pulse is one LSB wide. It can be increased to a three LSB wide pulse by setting the Index-bit of the OTP register. Further programming options (commutation modes) are available for brushless DC motor-control.

Md1 = Md0 = 1 changes the incremental output pins 3, 4 and 6 to a 3-phase commutation signal. Div1 defines the number of pulses per revolution for either a two-pole (Div1=0) or four-pole (Div1=1) rotor.

In addition, the LSB is available at pin 12 (the LSB signal replaces the PWM-signal), which allows for high rotational speed measurement of up to 10,000 rpm.

Table 10. One Time Programmable (OTP) Register Options

| Mode                           | 01  | ГР-Мо | de-Re | gister | -Bit  |               | P              | Pin#             |               | Pulses per<br>Revolution | Incremental Resolution |

|--------------------------------|-----|-------|-------|--------|-------|---------------|----------------|------------------|---------------|--------------------------|------------------------|

|                                | Md1 | Md0   | Div1  | Div0   | Index | 3             | 4              | 6                | 12            | ppr                      | bit                    |

| Default (Mode0.0) <sup>1</sup> | 0   | 0     | 0     | 0      | 0     |               |                | 1LSB             |               |                          |                        |

| quadAB-Mode1.0                 | 0   | 1     | 0     | 0      | 0     |               |                | 1LSB             |               | 2 x 256                  | 10                     |

| quadAB-Mode1.1                 | 0   | 1     | 0     | 0      | 1     |               |                | 3LSBs            |               |                          |                        |

| quadAB-Mode1.2                 | 0   | 1     | 0     | 1      | 0     |               |                | 1LSB             | D\A/\ 4       | 2 x 128                  | 9                      |

| quadAB-Mode1.3                 | 0   | 1     | 0     | 1      | 1     | Α             | В              | 3LSBs            | PWM<br>10 bit | 2 X 120                  | 9                      |

| quadAB-Mode1.4                 | 0   | 1     | 1     | 0      | 0     |               |                | 1LSB             |               | 2 x 64                   | 8                      |

| quadAB-Mode1.5                 | 0   | 1     | 1     | 0      | 1     |               |                | 3LSBs            | -             | 2 X 64                   | 8                      |

| quadAB-Mode1.6                 | 0   | 1     | 1     | 1      | 0     |               |                | 1LSB             |               | 2 x 32                   | 7                      |

| quadAB-Mode1.7                 | 0   | 1     | 1     | 1      | 1     |               |                | 3LSBs            |               | 2 X 32                   | ,                      |

| Step/Dir-Mode2.0               | 1   | 0     | 0     | 0      | 0     |               |                | 1LSB             |               | 512                      | 10                     |

| Step/Dir-Mode2.1               | 1   | 0     | 0     | 0      | 1     |               |                | 3LSBs            |               | 512                      | 10                     |

| Step/Dir -Mode2.2              | 1   | 0     | 0     | 1      | 0     |               |                | 1LSB             |               | 256                      | 9                      |

| Step/Dir -Mode2.3              | 1   | 0     | 0     | 1      | 1     | LSB           | Dir            | 3LSBs            | PWM           | 250                      | 9                      |

| Step/Dir -Mode2.4              | 1   | 0     | 1     | 0      | 0     | LOD           | Dii            | 1LSB 10<br>3LSBs | 10 bit        | 128                      | 8                      |

| Step/Dir -Mode2.5              | 1   | 0     | 1     | 0      | 1     |               |                |                  |               | 120                      | O                      |

| Step/Dir -Mode2.6              | 1   | 0     | 1     | 1      | 0     |               |                | 1LSB             |               | 64                       | 7                      |

| Step/Dir -Mode2.7              | 1   | 0     | 1     | 1      | 1     |               |                | 3LSBs            |               | 04                       | ,                      |

| Commutation-Mode3.0            | 1   | 1     | 0     | 0      | 0     | U(0°)         | V(120°)        | W(240°)          | LSB           | 3 x 1                    | 10                     |

| Commutation-Mode3.1            | 1   | 1     | 0     | 1      | 0     | U(U')         | V(120°)        | VV(240°)         | LOB           | 3 % 1                    | 9                      |

| Commutation-Mode3.2            | 1   | 1     | 1     | 0      | 0     | U'            | V'             | W'               | 1.00          | 0 4 0                    | 10                     |

| Commutation-Mode3.3            | 1   | 1     | 1     | 1      | 0     | (0°,1<br>80°) | (60°,24<br>0°) | (120°,30<br>0°)  | LSB           | 2 x 3                    | 9                      |

<sup>1.</sup> Div1, Div0 and Index cannot be programmed in Mode 0:0

# **Zero Position Programming**

Zero position programming is an OTP option that simplifies assembly of a system, as the magnet does not need to be manually adjusted to the mechanical zero position. Once the assembly is completed, the mechanical and electrical zero positions can be matched by software. Any position within a full turn can be defined as the permanent new zero/index position. For zero position programming, the magnet is turned to the mechanical zero position (e.g. the "off"-position of a rotary switch) and the actual angular value is read.

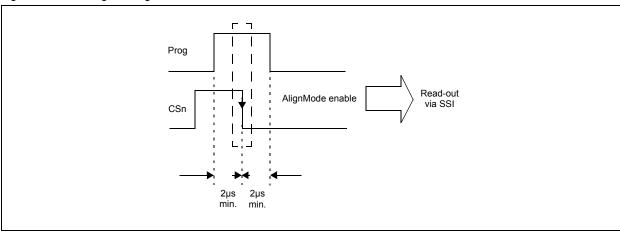

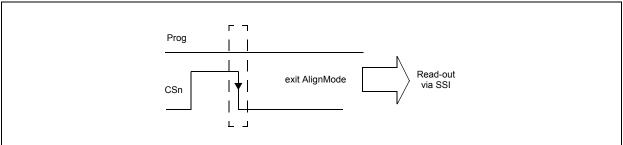

# **Alignment Mode**

The alignment mode simplifies centering the magnet over the center of the chip to gain maximum accuracy. Alignment mode can be enabled with the falling edge of CSn while Prog = logic high (see Figure 16). The Data bits D9-D0 of the SSI change to a 10-bit displacement amplitude output. A high value indicates large X or Y displacement, but also higher absolute magnetic field strength. The magnet is properly aligned, when the difference between highest and lowest value over one full turn is at a minimum. Under normal conditions, a properly aligned magnet will result in a reading of less than 128 over a full turn. The MagINCn and MagDECn indicators will be = 1 when the alignment mode reading is < 128. At the same time, both hardware pins MagINCn (#1) and MagDECn (#2) will be pulled to VSS. A properly aligned magnet will therefore produce a MagINCn = MagDECn = 1 signal throughout a full 360° turn of the magnet. Stronger magnets or short gaps between magnet and IC may show values larger than 128. These magnets are still properly aligned as long as the difference between highest and lowest value over one full turn is at a minimum. The Alignment mode can be reset to normal operation by a power-on-reset (disconnect / re-connect power supply) or by a falling edge on CSn with Prog = low.

Figure 15. Enabling the Alignment Mode

Figure 16. Exiting Alignment Mode

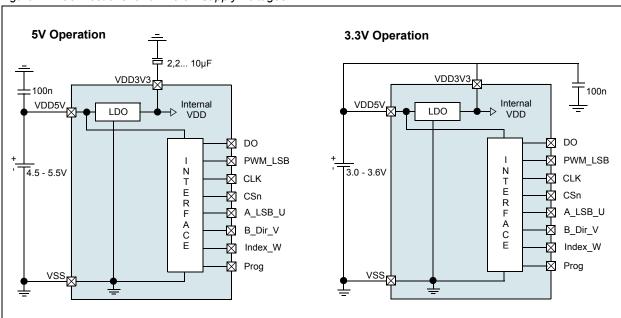

# 3.3V / 5V Operation

The AS5140H operates either at  $3.3V \pm 10\%$  or at  $5V \pm 10\%$ . This is made possible by an internal 3.3V Low-Dropout (LDO) voltage regulator. The internal supply voltage is always taken from the output of the LDO, meaning that the internal blocks are always operating at 3.3V. For 3.3V operation, the LDO must be bypassed by connecting VDD3V3 with VDD5V (see Figure 17).

For 5V operation, the 5V supply is connected to pin VDD5V, while VDD3V3 (LDO output) must be buffered by a 2,2..10µF capacitor, which is supposed to be placed close to the supply pin (see Figure 17). The VDD3V3 output is intended for internal use only. It must not be loaded with an external load.

The output voltage of the digital interface I/O's corresponds to the voltage at pin VDD5V, as the I/O buffers are supplied from this pin (see Figure 17). A buffer capacitor of 100nF is recommended in both cases close to pin VDD5V.

Note that pin VDD3V3 must always be buffered by a capacitor. It must not be left floating, as this may cause an instable internal 3.3V supply voltage, which may lead to larger than normal jitter of the measured angle.

Figure 17. Connections for 5V / 3.3V Supply Voltages

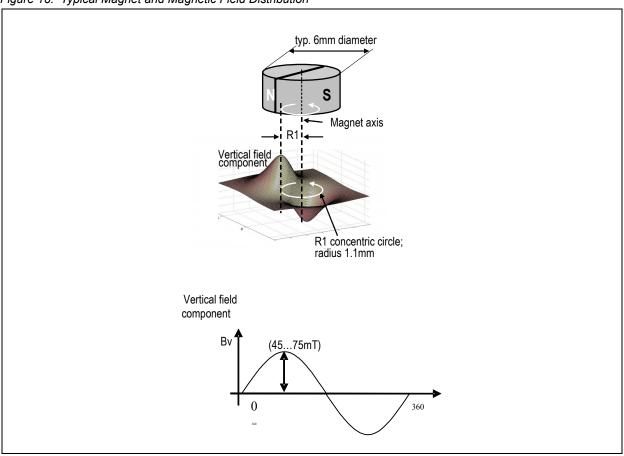

# **Choosing the Proper Magnet**

Typically the magnet should be 6mm in diameter and  $\geq$ 2.5mm in height. Magnetic materials such as rare earth AlNiCo, SmCo5 or NdFeB are recommended. The magnet's field strength perpendicular to the die surface should be verified using a gaussmeter. The magnetic field  $B_v$  at a given distance, along a concentric circle with a radius of 1.1mm (R1), should be in the range of  $\pm$ 45mT... $\pm$ 75mT. (see Figure 18).

Figure 18. Typical Magnet and Magnetic Field Distribution

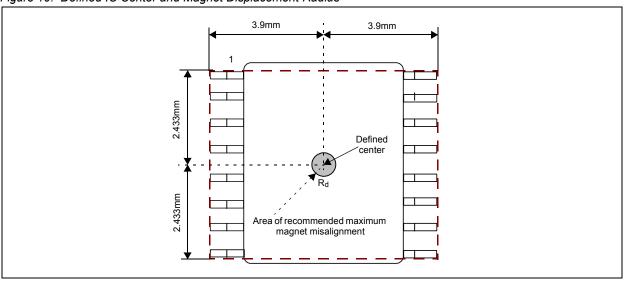

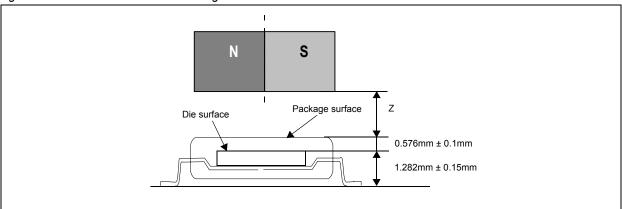

# **Physical Placement of the Magnet**

The best linearity can be achieved by placing the center of the magnet exactly over the defined center of the IC package as shown in Figure 19.

Figure 19. Defined IC Center and Magnet Displacement Radius

Magnet Placement

The magnet's center axis should be aligned within a displacement radius  $R_d$  of 0.25mm from the defined center of the IC with reference to the edge of pin #1 (see Figure 19). This radius includes the placement tolerance of the chip within the SSOP-16 package (+/- 0.235mm). The displacement radius  $R_d$  is 0.485mm with reference to the center of the chip (see Alignment Mode on page 24).

The vertical distance should be chosen such that the magnetic field on the die surface is within the specified limits (see Figure 18). The typical distance "z" between the magnet and the package surface is 0.5mm to 1.8mm with the recommended magnet (6mm x 2.5mm). Larger gaps are possible, as long as the required magnetic field strength stays within the defined limits. A magnetic field outside the specified range may still produce usable results, but the out-of-range condition will be indicated by MagINCn (pin 1) and MagDECn (pin 2), (see Table 6).

Figure 20. Vertical Placement of the Magnet

# Simulation Modeling

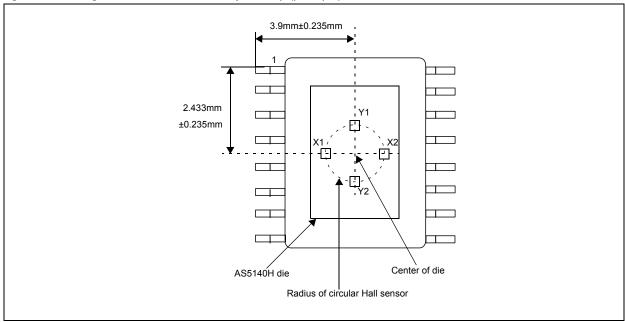

With reference to Figure 21, a diametrically magnetized permanent magnet is placed above or below the surface of the AS5140H. The chip uses an array of Hall sensors to sample the vertical vector of a magnetic field distributed across the device package surface. The area of magnetic sensitivity is a circular locus of 1.1mm radius with respect to the center of the die. The Hall sensors in the area of magnetic sensitivity are grouped and configured such that orthogonally related components of the magnetic fields are sampled differentially. The differential signal Y1-Y2 will give a sine vector of the magnetic field. The differential signal X1-X2 will give an orthogonally related cosine vector of the magnetic field.

Figure 21. Arrangement of Hall Sensor Array on Chip (principle)

The angular displacement ( $\Theta$ ) of the magnetic source with reference to the Hall sensor array may then be modelled by:

$$\Theta = \arctan \frac{(Y1 - Y2)}{(X1 - X2)} \pm 0.5^{\circ}$$

(EQ 5)

The ±0.5° angular error assumes a magnet optimally aligned over the center of the die and is a result of gain mismatch errors of the AS5140H. Placement tolerances of the die within the package are ±0.235mm in X and Y direction, using a reference point of the edge of pin #1 (Figure 21). In order to neglect the influence of external disturbing magnetic fields, a robust differential sampling and ratiometric calculation algorithm has been implemented. The differential sampling of the sine and cosine vectors removes any common mode error due to DC components introduced by the magnetic source itself or external disturbing magnetic fields. A ratiometric division of the sine and cosine vectors removes the need for an accurate absolute magnitude of the magnetic field and thus accurate Z-axis alignment of the magnetic source.

The recommended differential input range of the magnetic field strength  $(B_{(X1-X2)},B_{(Y1-Y2)})$  is  $\pm 75\text{mT}$  at the surface of the die. In addition to this range, an additional offset of  $\pm 5\text{mT}$ , caused by unwanted external stray fields is allowed. The chip will continue to operate, but with degraded output linearity, if the signal field strength is outside the recommended range. Too strong magnetic fields will introduce errors due to saturation effects in the internal preamplifiers. Too weak magnetic fields will introduce errors due to noise becoming more dominant.

# **Failure Diagnostics**

The AS5140H also offers several diagnostic and failure detection features, which are discussed in detail further in the document.

# **Magnetic Field Strength Diagnosis**

By Software: The MagINCn and MagDECn status bits will both be high when the magnetic field is out of range.

**By Hardware:** Pins #1 (MagINCn) and #2 (MagDECn) are open-drain outputs and will both be turned on (= low with external pull-up resistor) when the magnetic field is out of range. If only one of the outputs is low, the magnet is either moving towards the chip (MagINCn) or away from the chip (MagDECn).

# **Power Supply Failure Detection**

By Software: If the power supply to the AS5140H is interrupted, the digital data read by the SSI will be all "0"s. Data is only valid, when bit OCF is high, hence a data stream with all "0"s is invalid. To ensure adequate low levels in the failure case, a pull-down resistor ( $\sim$ 10k $\Omega$ ) should be added between pin DO and VSS at the receiving side.

By Hardware: The MagINCn and MagDECn pins are open drain outputs and require external pull-up resistors. In normal operation, these pins are high ohmic and the outputs are high (see Table 6). In a failure case, either when the magnetic field is out of range or the power supply is missing, these outputs will become low. To ensure adequate low levels in case of a broken power supply to the AS5140H, the pull-up resistors (>10k $\Omega$ ) from each pin must be connected to the positive supply at pin 16 (VDD5V).

By Hardware - PWM Output: The PWM output is a constant stream of pulses with 1kHz repetition frequency. In case of power loss, these pulses are missing.