## 4-/8-Channel Wideband Video Multiplexers

#### **FEATURES**

- Wide Bandwidth: 500 MHz

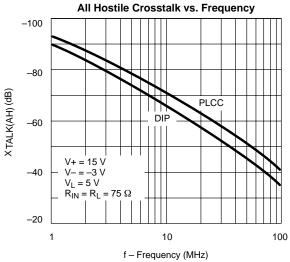

- Very Low Crosstalk: –97 dB @ 5 MHz

- On-Board TTL-Compatible Latches with Readback

- Optional Negative Supply

- Low r<sub>DS(on)</sub>: 45 Ω

- Single-Ended or Differential Operation

- Latch-up Proof

#### **BENEFITS**

- Improved System Bandwidth

- Improved Channel Off-Isolation

- Simplified Logic Interfacing

- High-Speed Readback

- Allows Bipolar Signal Swings

- Reduced Insertion Loss

- Allows Differential Signal Switching

#### **APPLICATIONS**

- Wideband Signal Routing and Multiplexing

- Video Switchers

- ATE Systems

- Infrared Imaging

- Ultrasound Imaging

#### **DESCRIPTION**

The DG534A is a digitally selectable 4-channel or dual 2-channel multiplexer. The DG538A is an 8-channel or dual 4-channel multiplexer. On-chip TTL-compatible address decoding logic and latches with data readback are included to simplify the interface to a microprocessor data bus. The low on-resistance and low capacitance of the these devices make them ideal for wideband data multiplexing and video and audio signal routing in channel selectors and crosspoint arrays. An optional negative supply pin allows the handling of bipolar signals without dc biasing.

The DG534A/DG538A are built on a D/CMOS process that combines n-channel DMOS switching FETs with low-power CMOS control logic, drivers and latches. The low-capacitance DMOS FETs are connected in a "T" configuration to achieve extremely high levels of off isolation. Crosstalk is reduced to –97 dB at 5 MHz by including a ground line between adjacent signal paths. An epitaxial layer prevents latch-up.

For more information refer to Vishay Siliconix applications note AN502.

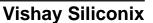

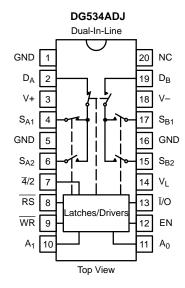

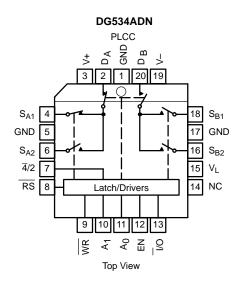

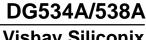

#### **FUNCTIONAL BLOCK DIAGRAM AND PIN CONFIGURATION**

#### **FUNCTIONAL BLOCK DIAGRAM AND PIN CONFIGURATION**

|     | TRUTH TABLE — DG534A |                |    |    |    |                          |                                     |                                          |                     |  |  |

|-----|----------------------|----------------|----|----|----|--------------------------|-------------------------------------|------------------------------------------|---------------------|--|--|

| Ī/O | A <sub>1</sub>       | A <sub>0</sub> | EN | WR | RS | <u>4</u> /2 <sup>a</sup> | On Switch                           |                                          |                     |  |  |

| Х   | Х                    | Х              | Х  | 7  | 1  | 1                        | Maintains previous state            |                                          |                     |  |  |

| Х   | Х                    | Х              | Х  | Х  | 0  | Х                        | None (latches cleared)              |                                          |                     |  |  |

| Х   | Х                    | Х              | 0  | 0  | 1  | X                        | None                                |                                          |                     |  |  |

| 0   | 0                    | 0              | 1  | 0  | 1  | 0                        | S <sub>A1</sub>                     |                                          |                     |  |  |

| 0   | 0                    | 1              | 1  | 0  | 1  | 0                        | S <sub>A2</sub>                     | D <sub>A</sub> and D <sub>B</sub> may be |                     |  |  |

| 0   | 1                    | 0              | 1  | 0  | 1  | 0                        | S <sub>B1</sub>                     | connected externally                     | Latches Transparent |  |  |

| 0   | 1                    | 1              | 1  | 0  | 1  | 0                        | S <sub>B2</sub>                     | 7                                        |                     |  |  |

| 0   | Х                    | 0              | 1  | 0  | 1  | 1                        | S <sub>A1</sub> and S <sub>B</sub>  | S <sub>A1</sub> and S <sub>B1</sub>      |                     |  |  |

| 0   | Х                    | 1              | 1  | 0  | 1  | 1                        | S <sub>A2</sub> and S <sub>B2</sub> |                                          | 7                   |  |  |

| 1   |                      | Note b         |    | 1  | 1  | Note c                   |                                     |                                          | •                   |  |  |

$\begin{array}{l} \text{Logic "0"} = \text{ V}_{AL} \leq 0.8 \text{ V} \\ \text{Logic "1"} = \text{V}_{AH} \geq 2.4 \text{ V} \\ \text{X} = \text{Don't Care} \end{array}$

|     | TRUTH TABLE — DG538A |                |                |    |    |    |                  |                          |                                             |                     |  |  |  |  |

|-----|----------------------|----------------|----------------|----|----|----|------------------|--------------------------|---------------------------------------------|---------------------|--|--|--|--|

| Ī/O | A <sub>2</sub>       | A <sub>1</sub> | A <sub>0</sub> | EN | WR | RS | 8/4 <sup>a</sup> | On Switch                |                                             |                     |  |  |  |  |

| Х   | Х                    | Х              | Х              | Х  |    | 1  | 1                | Maintains previous state |                                             |                     |  |  |  |  |

| Х   | Х                    | Х              | Х              | Х  | Х  | 0  | Х                | None (lat                | None (latches cleared)                      |                     |  |  |  |  |

| Х   | Х                    | Х              | Х              | 0  | 0  | 1  | Х                | None                     |                                             |                     |  |  |  |  |

| 0   | 0                    | 0              | 0              | 1  | 0  | 1  | 0                | S <sub>A1</sub>          |                                             | 1                   |  |  |  |  |

| 0   | 0                    | 0              | 1              | 1  | 0  | 1  | 0                | S <sub>A2</sub>          |                                             | Latches Transparent |  |  |  |  |

| 0   | 0                    | 1              | 0              | 1  | 0  | 1  | 0                | S <sub>A3</sub>          |                                             |                     |  |  |  |  |

| 0   | 0                    | 1              | 1              | 1  | 0  | 1  | 0                | S <sub>A4</sub>          | D <sub>A</sub> and D <sub>B</sub> should be |                     |  |  |  |  |

| 0   | 1                    | 0              | 0              | 1  | 0  | 1  | 0                | S <sub>B1</sub>          | connected externally                        |                     |  |  |  |  |

| 0   | 1                    | 0              | 1              | 1  | 0  | 1  | 0                | S <sub>B2</sub>          |                                             |                     |  |  |  |  |

| 0   | 1                    | 1              | 0              | 1  | 0  | 1  | 0                | S <sub>B3</sub>          |                                             |                     |  |  |  |  |

| 0   | 1                    | 1              | 1              | 1  | 0  | 1  | 0                | S <sub>B4</sub>          |                                             |                     |  |  |  |  |

| 0   | Х                    | 0              | 0              | 1  | 0  | 1  | 1                | S <sub>A1</sub> and      | S <sub>B1</sub>                             | 1                   |  |  |  |  |

| 0   | Х                    | 0              | 1              | 1  | 0  | 1  | 1                | S <sub>A2</sub> and      | S <sub>B2</sub>                             |                     |  |  |  |  |

| 0   | Х                    | 1              | 0              | 1  | 0  | 1  | 1                | S <sub>A3</sub> and      | S <sub>A3</sub> and S <sub>B3</sub>         |                     |  |  |  |  |

| 0   | Х                    | 1              | 1              | 1  | 0  | 1  | 1                | S <sub>A4</sub> and      | S <sub>A4</sub> and S <sub>B4</sub>         |                     |  |  |  |  |

| 1   |                      | Not            | e b            | -  | 1  | 1  | Note c           |                          |                                             | -                   |  |  |  |  |

Logic "0" =  $V_{AL} \le 0.8 \text{ V}$ Logic "1" =  $V_{AH} \ge 2 \text{ V}$  X = Don't Care

#### Notes:

a. Connect D<sub>A</sub> and D<sub>B</sub> together externally for single-ended operation.

b. With Ī/O high, A<sub>n</sub> and EN pins become outputs and reflect latch contents. See timing diagrams for more detail.

c. 8/4 can be either "1" or "0" but should not change during these operations.

| ORDERING INFORMATION |                    |                               |  |  |  |  |  |  |  |

|----------------------|--------------------|-------------------------------|--|--|--|--|--|--|--|

| Temperature Range    | Package            | Part Number                   |  |  |  |  |  |  |  |

| DG534A               |                    |                               |  |  |  |  |  |  |  |

| −40 to 85°C          | 20-Pin Plastic DIP | DG534ADJ                      |  |  |  |  |  |  |  |

| -40 to 65 C          | 20-Pin PLCC        | DG534ADN                      |  |  |  |  |  |  |  |

| −55 to 125°C         | 20-Pin Sidebraze   | DG534AAP/883, 5962-906021MRC  |  |  |  |  |  |  |  |

| DG538A               |                    |                               |  |  |  |  |  |  |  |

| −40 to 85°C          | 28-Pin Plastic DIP | DG538ADJ                      |  |  |  |  |  |  |  |

| -40 to 60 C          | 28-Pin PLCC        | DG538ADN                      |  |  |  |  |  |  |  |

| –55 to 125°C         | 28-Pin Sidebraze   | DG538AAP/883, 5962-8976001MXA |  |  |  |  |  |  |  |

# DG534A/538A

# Vishay Siliconix

## **ABSOLUTE MAXIMUM RATINGS**

| V+ to GND0.3 V to +21 V                                 |

|---------------------------------------------------------|

| V+ to V0.3 V to +21 V                                   |

| V- to GND10 V to +0.3 V                                 |

| $V_L$                                                   |

| Digital Inputs (V–) –0.3 V to (V <sub>L</sub> ) + 0.3 V |

| or 20 mA, whichever occurs first                        |

| $V_S$ , $V_D$ (V–) –0.3 V to (V–) + 14 V                |

| or 20 mA, whichever occurs first                        |

| Current (any terminal) Continuous 20 mA                 |

| Current(S or D) Pulsed I ms 10% Duty                    |

| Storage Temperature | (A Suffix) -65 to 150°C<br>(D Suffix) -65 to 125°C |

|---------------------|----------------------------------------------------|

| PLCC <sup>c</sup>   |                                                    |

| SPECIFICATION                        | Sa                  |                                                                                     |           |              |                          |              |                                |             |                  |       |

|--------------------------------------|---------------------|-------------------------------------------------------------------------------------|-----------|--------------|--------------------------|--------------|--------------------------------|-------------|------------------|-------|

|                                      |                     | Test Condition Unless Otherwise S                                                   |           |              | A Suffix<br>-55 to 125°C |              | <b>D Suffix</b><br>-40 to 85°C |             |                  |       |

| Parameter                            | Symbol              | <b>Symbol</b> V+ = 15 V, V- = -3 V, V <sub>L</sub> = 5 V<br>WR = 0.8 V, RS, EN= 2 V |           | Tempb        | Typ <sup>c</sup>         | Mind         | Max <sup>d</sup>               | Mind        | Max <sup>d</sup> | Unit  |

| Analog Switch                        | L                   | 1                                                                                   |           | l .          | I.                       |              |                                |             |                  |       |

| Analog Signal Range <sup>g</sup>     | V <sub>ANALOG</sub> | V- = -5 V                                                                           |           | Full         |                          | -5           | 8                              | -5          | 8                | V     |

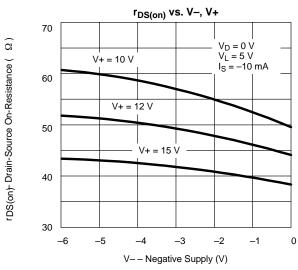

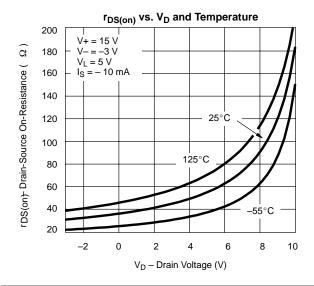

| Drain-Source<br>On-Resistance        | r <sub>DS(on)</sub> | $I_S = -10 \text{ mA}, V_S = V_{AIL} = 0.8 \text{ V}, V_{AIH} = 0.8 \text{ V}$      | 0 V       | Room<br>Full | 45                       |              | 90<br>120                      |             | 90<br>120        | Ω     |

| Resistance Match<br>Between Channels | $\Delta r_{DS(on)}$ | Sequence Each Swit                                                                  | tch On    | Room         |                          |              | 9                              |             | 9                | Ω     |

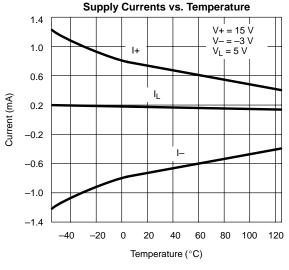

| Source Off<br>Leakage Current        | I <sub>S(off)</sub> | V <sub>S</sub> = 8 V, V <sub>D</sub> = 0 V, EN                                      | I = 0.8 V | Room<br>Full | 0.05                     | -5<br>-50    | 5<br>50                        | -5<br>-50   | 5<br>50          |       |

| Drain Off<br>Leakage Current         | I <sub>D(off)</sub> | V <sub>S</sub> = 0 V, V <sub>D</sub> = 8 V, EN = 0.8 V                              |           | Room<br>Full | 0.1                      | -20<br>-500  | 20<br>500                      | -20<br>-100 | 20<br>100        | nA    |

| Drain On<br>Leakage Current          | I <sub>D(on)</sub>  | V <sub>S</sub> = V <sub>D</sub> = 8 V                                               |           | Room<br>Full | 0.1                      | -20<br>-1000 | 20<br>1000                     | -20<br>-200 | 20<br>200        |       |

| Digital Control                      |                     |                                                                                     |           |              |                          |              |                                |             |                  |       |

| Input Voltage High                   | $V_{AIH}$           |                                                                                     |           | Full         |                          | 2            |                                | 2           |                  | V     |

| Input Voltage Low                    | $V_{AIL}$           | 1                                                                                   |           | Full         |                          |              | 0.8                            |             | 0.8              | ľ     |

| Address Input Current                | I <sub>AI</sub>     | V <sub>AI</sub> = 0 V, or 2 V or                                                    | r 5 V     | Room<br>Full | -0.1                     | −1<br>−10    | 1<br>10                        | −1<br>−10   | 1<br>10          | μА    |

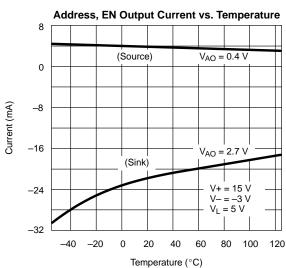

| Address Output Current               | I <sub>AO</sub>     | V <sub>AO</sub> = 2.7 V                                                             |           | Room         | -21                      |              | -2.5                           |             | -2.5             | mA    |

| Address Odiput Odirent               | 'AO                 | V <sub>AO</sub> = 0.4 V                                                             |           | Room         | 3.5                      | 2.5          |                                | 2.5         |                  | 11171 |

| Dynamic Characteris                  | stics               |                                                                                     |           |              |                          |              |                                |             |                  |       |

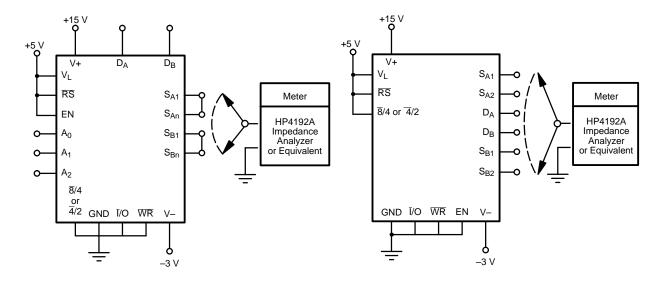

| On State Input                       |                     | Coo Figure 44                                                                       | PLCC      | Room         | 28                       |              | 40                             |             | 40               |       |

| Capacitance <sup>g</sup>             | C <sub>S(on)</sub>  | See Figure 11                                                                       | DIP       | Room         | 31                       |              | 45                             |             | 45               |       |

| Off State Input                      | C                   |                                                                                     | PLCC      | Room         | 3                        |              | 5                              |             | 4                | nE    |

| Capacitance <sup>9</sup>             | C <sub>S(off)</sub> | See Figure 12                                                                       | DIP       | Room         | 4                        |              |                                |             | 5                | pF    |

| Off State Output                     | C                   | See rigule 12                                                                       | PLCC      | Room         | 6                        |              | 10                             |             | 8                |       |

| Capacitance <sup>g</sup>             | $C_{D(off)}$        |                                                                                     | DIP       | Room         | 8                        |              |                                |             | 10               |       |

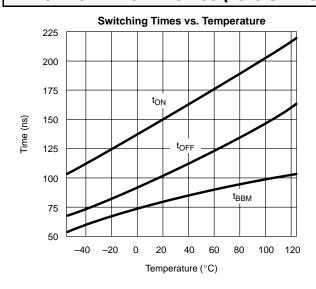

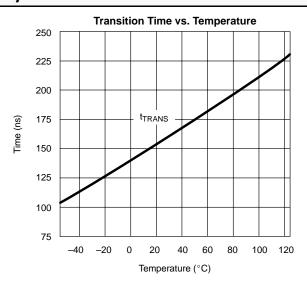

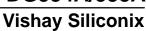

| Transition Time                      | t <sub>TRANS</sub>  | Can Figure 4                                                                        |           |              | 160                      |              | 300<br>500                     |             | 300<br>500       |       |

| Break-Before-Make<br>Interval        | t <sub>OPEN</sub>   | See Figure 4                                                                        |           | Room<br>Full | 80                       | 50<br>25     |                                | 50<br>25    |                  | ns    |

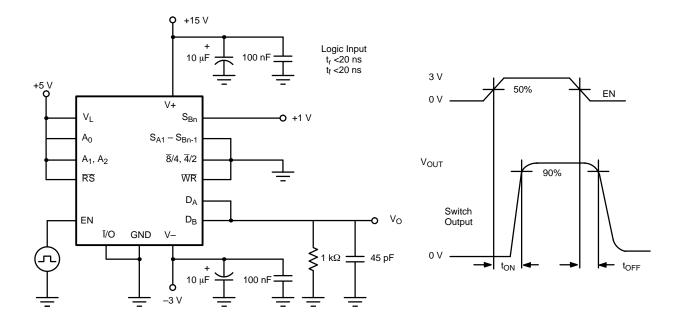

| EN, WR Turn On Time                  | t <sub>ON</sub>     | See Figure 2 and                                                                    | 13        | Room<br>Full | 150                      |              | 300<br>500                     |             | 300<br>500       | ns    |

| EN, Turn Off Time                    | t <sub>OFF</sub>    | See Figure 2                                                                        |           | Room<br>Full | 105                      |              | 175<br>300                     |             | 175<br>300       |       |

| Charge Injection                     | Qi                  | See Figure 5                                                                        |           | Room         | -70                      |              |                                |             |                  | рC    |

|                                                                 |                          | Test Condition<br>Unless Otherwise Sp                                                                                        |                                  |              | A Suffix<br>-55 to 125°C |            | D Suffix<br>-40 to 85°C |                  |                  |      |

|-----------------------------------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--------------|--------------------------|------------|-------------------------|------------------|------------------|------|

| Parameter                                                       | Symbol                   | $V+ = 15 \text{ V}, V- = -3 \text{ V}, V_L = 5 \text{ V}$<br>$\overline{WR} = 0.8 \text{ V}, \overline{RS}, EN= 2 \text{ V}$ |                                  | Tempb        | Тур <sup>с</sup>         | Mind       | Max <sup>d</sup>        | Min <sup>d</sup> | Max <sup>d</sup> | Unit |

| Dynamic Characteris                                             | tics (Cont'd)            |                                                                                                                              |                                  |              |                          |            |                         |                  |                  |      |

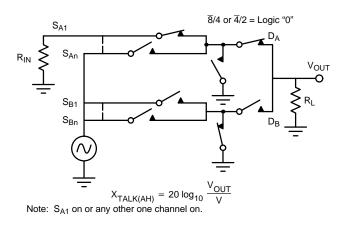

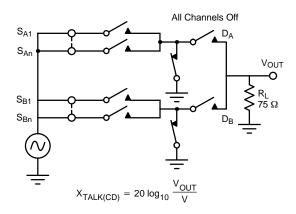

| Ohio Disabled Ossestallif                                       | V                        | $R_L = 75 \Omega, f = 5 MHz$<br>EN = 0.8 V                                                                                   | PLCC                             | Room         | -75                      |            |                         |                  |                  |      |

| Chip Disabled Crosstalk <sup>f</sup>                            | X <sub>TALK(CD)</sub>    | See Figure 8                                                                                                                 | DIP                              | Room         | -65                      |            |                         |                  |                  |      |

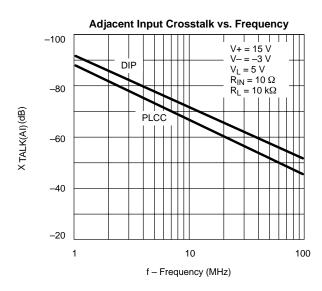

|                                                                 |                          | $R_{IN} = 10 \Omega$<br>$R_{L} = 10 k\Omega$                                                                                 | PLCC                             | Room         | -97                      |            |                         |                  |                  |      |

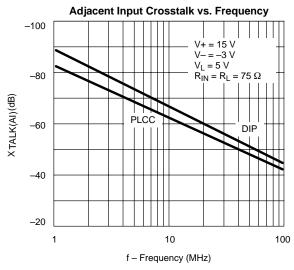

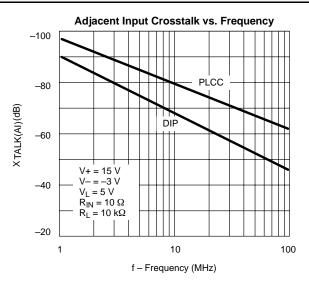

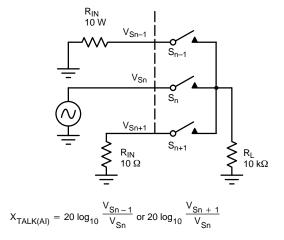

| Adjacent Input Crosstalkf                                       | X <sub>TALK(AI)</sub>    | f = 5 MHz<br>SeeFigure 9                                                                                                     | DIP                              | Room         | -87                      |            |                         |                  |                  |      |

| ,,                                                              | IALIX(AI)                | $R_{IN} = 75 \Omega, R_{L} = 75 \Omega$                                                                                      | PLCC                             | Room         | -80                      |            |                         |                  |                  |      |

|                                                                 |                          | f = 5 MHz<br>See Figure 7                                                                                                    | DIP                              | Room         | -70                      |            |                         |                  |                  |      |

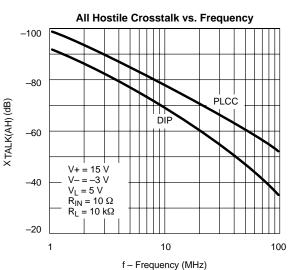

|                                                                 |                          | $R_{IN} = 10 \Omega$<br>$R_{L} = 10 k\Omega$                                                                                 | PLCC                             | Room         | -77                      |            |                         |                  |                  | dB   |

| All Hostile Crosstalk                                           | X <sub>TALK(AH)</sub>    | f = 5 MHz<br>See Figure 7                                                                                                    | DIP                              | Room         | -72                      |            |                         |                  |                  |      |

| All HUSLIE CIUSSIAIK                                            |                          | $R_{\text{IN}}$ = 75 $\Omega$ , $R_{\text{L}}$ = 75 $\Omega$<br>f = 5 MHz<br>See Figure 7                                    | PLCC                             | Room         | -77                      |            |                         |                  |                  |      |

|                                                                 |                          |                                                                                                                              | DIP                              | Room         | -72                      |            |                         |                  |                  |      |

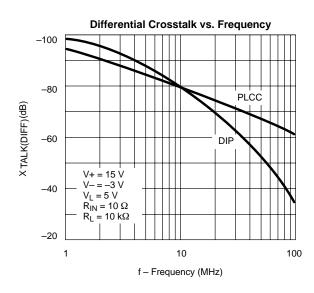

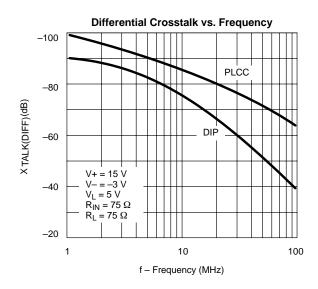

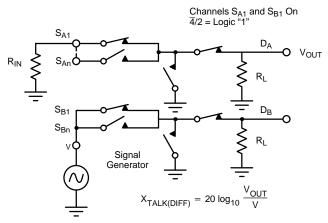

| Differential Crosstalk                                          | · ·                      | $R_{IN} = 10 \Omega$ , $R_{L} = 10 k\Omega$<br>f = 5 MHz, See Figure 10                                                      |                                  | Room         | -84                      |            |                         |                  |                  |      |

|                                                                 | X <sub>TALK</sub> (DIFF) | $R_{IN} = R_L = 75 \Omega$<br>f = 5 MHz, See Figure 10                                                                       |                                  | Room         | -84                      |            |                         |                  |                  |      |

| Bandwidth                                                       | BW                       | $R_L = 50 \Omega$ , See Figur                                                                                                |                                  | Room         | 500                      |            |                         |                  |                  | MHz  |

| Power Supplies                                                  |                          | •                                                                                                                            |                                  |              |                          | 1          |                         |                  |                  |      |

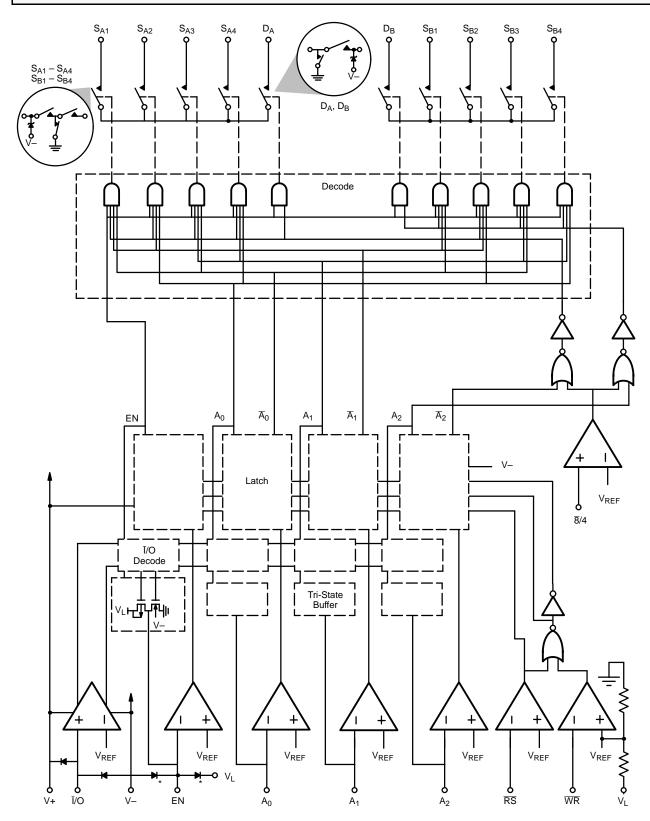

| Positive Supply Current                                         | I+                       | Any One Channel Selected                                                                                                     | Any One Channel Selected with Ad |              | 0.6                      |            | 2<br>5                  |                  | 2<br>5           |      |

| Negative Supply Current                                         | I–                       | dress Inputs at GND o                                                                                                        |                                  | Room<br>Full | 0.6                      | -1.8<br>-2 |                         | -1.8<br>-2       |                  | mA   |

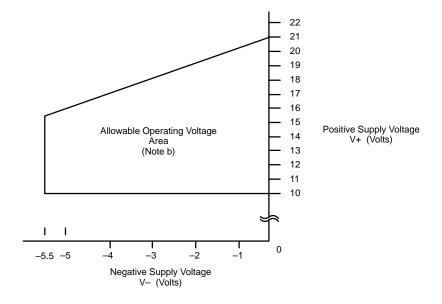

| Functional Check of                                             | V+ to V-                 |                                                                                                                              |                                  | Full         |                          | 10         | 21                      | 10               | 21               |      |

| Maximum Operating                                               | V- to GND                | Functional Test Only                                                                                                         |                                  | Full         |                          | -5.5       | 0                       | -5.5             | 0                | V    |

| Supply Voltage Range                                            | V+ to GND                |                                                                                                                              |                                  | Full         |                          | 10         | 21                      | 10               | 21               |      |

| Logic Supply Current                                            | ال                       |                                                                                                                              |                                  | Full         | 150                      |            | 500                     |                  | 500              | μΑ   |

| Timing                                                          |                          |                                                                                                                              |                                  |              |                          |            |                         |                  |                  |      |

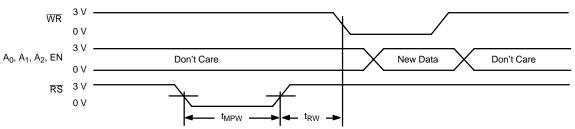

| Reset to Write                                                  | t <sub>RW</sub>          |                                                                                                                              |                                  | Room<br>Full | -22                      | 50         |                         | 50               |                  |      |

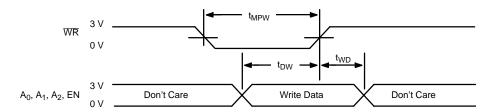

| WR, RS<br>Minimum Pulse Width                                   | t <sub>MPW</sub>         | See Figure 1                                                                                                                 |                                  | Room<br>Full | 60                       | 200        |                         | 200              |                  | ns   |

| A <sub>0</sub> , A <sub>1</sub> , EN<br>Data Valid to Strobe    | t <sub>DW</sub>          |                                                                                                                              |                                  | Room<br>Full | 20                       | 100        |                         | 100              |                  |      |

| A <sub>0</sub> , A <sub>1</sub> , EN<br>Data Valid after Strobe | t <sub>WD</sub>          | Jee rigule r                                                                                                                 |                                  | Room<br>Full | -20                      | 50         |                         | 50               |                  | 115  |

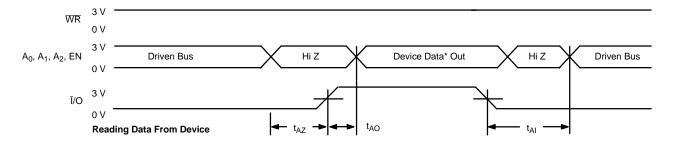

| Address Bus Tri-State <sup>e</sup>                              | $t_{AZ}$                 | 1                                                                                                                            |                                  | Room         | 25                       |            |                         |                  |                  |      |

| Address Bus Output                                              | t <sub>AO</sub>          |                                                                                                                              |                                  | Room         | 95                       |            |                         |                  |                  |      |

| Address Bus Input                                               | t <sub>Al</sub>          |                                                                                                                              |                                  | Room         | 110                      |            |                         |                  |                  | 1    |

#### Notes:

- tes:

Refer to PROCESS OPTION FLOWCHART.

Room = 25°C, Full = as determined by the operating temperature suffix.

Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

The algebraic convention whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet.

Defined by system bus requirements.

Each individual pin shown as GND must be grounded.

Guaranteed by design, not subject to production test.

## CONTROL CIRCUITRY

<sup>\*</sup>Typical all Readback (A<sub>X</sub>, EN) pins

### TYPICAL CHARACTERISTICS (25°C UNLESS NOTED)

#### TYPICAL CHARACTERISTICS (25°C UNLESS NOTED)

## TYPICAL CHARACTERISTICS (25°C UNLESS NOTED)

#### **OUTPUT TIMING REQUIREMENTS**

#### Writing Data to Device

**Delay Time Required after Reset before Write**

FIGURE 1.

#### **TEST CIRCUITS**

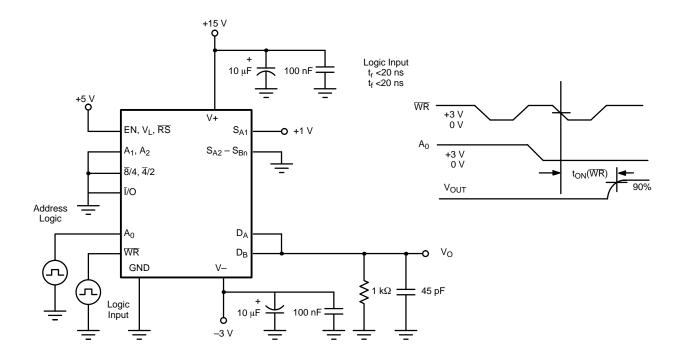

FIGURE 2. EN, CS, CS, Turn On/Off Time

FIGURE 3. WR, Turn On Time

#### **TEST CIRCUITS**

FIGURE 4. Transition Time and Break-Before-Make Interval

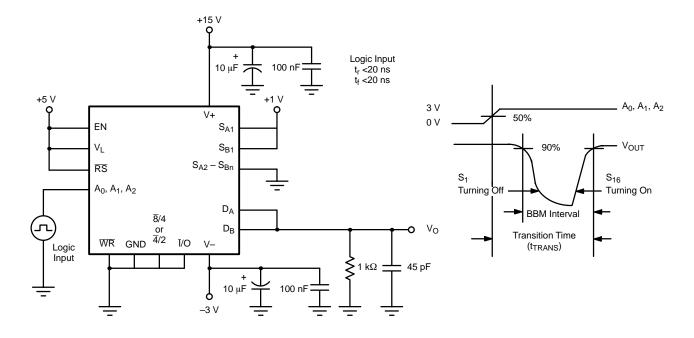

$\Delta V_{OUT}$  is the measured voltage error due to charge injection. The charge injection in Coulombs is Q = C<sub>L</sub> x  $\Delta V_{OUT}$

FIGURE 5. Charge Injection

#### **TEST CIRCUITS**

FIGURE 6. Bandwidth

FIGURE 7. All Hostile Crosstalk

FIGURE 8. Chip Disabled Crosstalk

FIGURE 9. Adjacent Input Crosstalk

FIGURE 10. Differential Crosstalk

#### **TEST CIRCUITS**

FIGURE 11. On State Input Capacitance

FIGURE 12. Off State Input/Output Capacitance

## **OPERATING VOLTAGE RANGE**

#### Notes:

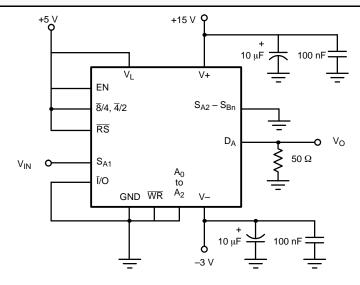

- a. Both V+ and V- must have decoupling capacitors mounted as close as possible to the device pins. Typical decoupling capacitors would be 10-μF tantalum bead in parallel with 100-nF ceramic disc.

- b. Production tested with V+ = 15 V and V- = -3 V.

- a. For  $V_L$  = 5 V  $\pm$  10%, 0.8- or 2-V TTL compatibility is maintained over the entire operating voltage range.

#### FIGURE 13.

|                 | Pin N     | lumber                 |                                                                                                       |  |  |  |  |

|-----------------|-----------|------------------------|-------------------------------------------------------------------------------------------------------|--|--|--|--|

| Symbol          | DG534ADJ  | DG538A                 | Description                                                                                           |  |  |  |  |

| D <sub>A</sub>  | 2         | 2                      | Analog Output/Input                                                                                   |  |  |  |  |

| V+              | 3         | 3                      | Positive Supply Voltage                                                                               |  |  |  |  |

| S <sub>A1</sub> | 4         | 4                      | Analog Input/Output                                                                                   |  |  |  |  |

| S <sub>A2</sub> | 6         | 6                      | Analog Input/Output                                                                                   |  |  |  |  |

| S <sub>A3</sub> | -         | 8                      | Analog Input/Output                                                                                   |  |  |  |  |

| S <sub>A4</sub> | -         | 10                     | Analog Input/Output                                                                                   |  |  |  |  |

| 4/2             | 7         | -                      | 4 x 1 or 2 x 2 Select                                                                                 |  |  |  |  |

| 8/4             | -         | 11                     | 8 x 1 or 4 x 2 Select                                                                                 |  |  |  |  |

| RS              | 8         | 12                     | Reset                                                                                                 |  |  |  |  |

| WR              | 9         | 13                     | Write command that latches A, EN                                                                      |  |  |  |  |

| $A_0, A_1, A_2$ | 11, 10, – | 16, 15, 14             | Binary address inputs that determine which channel(s) is/are connected to the output(s)               |  |  |  |  |

| EN              | 12        | 17                     | Enable. Input/Output, if EN = 0, all channels are open                                                |  |  |  |  |

| Ī/O             | 13        | 18                     | Input/Output control. Used to write to or read from the address latches                               |  |  |  |  |

| $V_{L}$         | 14        | 19                     | Logic Supply Voltage, usually +5 V                                                                    |  |  |  |  |

| S <sub>B4</sub> | -         | 20                     | Analog Input/Output                                                                                   |  |  |  |  |

| S <sub>B3</sub> | -         | 22                     | Analog Input/Output                                                                                   |  |  |  |  |

| S <sub>B2</sub> | 15        | 24                     | Analog Input/Output                                                                                   |  |  |  |  |

| S <sub>B1</sub> | 17        | 26                     | Analog Input/Output                                                                                   |  |  |  |  |

| V-              | 18        | 27                     | Negative Supply Voltage                                                                               |  |  |  |  |

| $D_B$           | 19        | 28                     | Analog Output/Input                                                                                   |  |  |  |  |

| GND             | 1, 5, 16  | 1, 5, 7, 9, 21, 23, 25 | Analog and Digital Grounds. All grounds should be connected externally to optimic dynamic performance |  |  |  |  |

#### **APPLICATIONS**

#### **Device Description**

The DG534A/538A D/CMOS wideband multiplexers offer single-ended or differential functions. A  $\overline{8}/4$  or  $\overline{4}/2$  logic input pin selects the single-ended or differential mode.

To meet the high dynamic performance demands of video, high definition TV, digital data routing (in excess of 100 Mbps), etc., the DG534A/538A are fabricated with DMOS transistors configured in 'T' arrangements with second level 'L' configurations (see Functional Block Diagram).

Use of DMOS technology yields devices with very low capacitance and low  $r_{DS(on)}$ . This directly relates to improved high frequency signal handling and higher switching speeds, while maintaining low insertion loss figures. The 'T' and 'L' switch configurations further improve dynamic performance by greatly reducing crosstalk and output node capacitances.

The DG534A/DG538A are improved pin-compatible replacements for the non-A versions. Improvements include: higher current readback drivers, readback of the EN bit, latchup protection

#### **Frequency Response**

A single multiplexer on-channel exhibits both resistance  $[r_{DS(on)}]$  and capacitance  $[C_{S(on)}].$  This RC combination causes a frequency dependent attenuation of the analog signal. The –3-dB bandwidth of the DG534A/538A is typically 500 MHz (into 50  $\Omega).$  This figure of 500 MHz illustrates that the switch-channel cannot be represented by a simple RC combination. The on capacitance of the channel is distributed along the on-resistance, and hence becomes a more complex multi-stage network of R's and C's making up the total  $r_{DS(on)}$  and  $C_{S(on)}.$

#### **APPLICATIONS (CONT'D)**

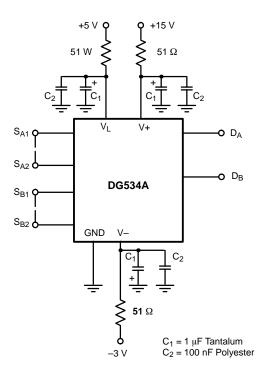

#### **Power Supplies and Decoupling**

A useful feature of the DG534A/538A is its power supply flexibility. It can be operated from unipolar supplies (V-connected to 0 V) if required. Allowable operating voltage ranges are shown in Figure 13.

Note that the analog signal must not go below V– by more than 0.3 V (see absolute maximum ratings). However, the addition of a V– pin has a number of advantages:

- a. It allows flexibility in analog signal handling, i.e. with V-=-5 V and V+=15 V, up to  $\pm 5$  V ac signals can be accepted.

- b. The value of on capacitance  $(C_{S(on)})$  may be reduced by increasing the reverse bias across the internal FET body to source junction. V+ has no effect on  $C_{S(on)}$ .

- It is useful to note that tests indicate that optimum video differential phase and gain occur when V- is -3 V.

- V- eliminates the need to bias an ac analog signal using potential dividers and large decoupling capacitors.

It is established rf design practice to incorporate sufficient bypass capacitors in the circuit to decouple the power supplies to all active devices in the circuit. The dynamic performance of the DG534/538 is adversely affected by poor decoupling of power supply pins. Also, since the substrate of the device is connected to the negative supply, proper decoupling of this pin is essential.

#### Rules:

- Decoupling capacitors should be incorporated on all power supply pins (V+, V-, V<sub>I</sub>).

- They should be mounted as close as possible to the device pins.

- c. Capacitors should have good frequency characteristics tantalum bead and/or ceramic disc types are suitable. Recommended decoupling capacitors are 1- to  $10-\mu F$  tantalum bead, in parallel with 100-nF ceramic or polyester.

- d. Additional high frequency protection may be provided by  $51-\Omega$  carbon film resistors connected in series with the power supply pins (see Figure 14).

#### **Board Layout**

PCB layout rules for good high frequency performance must also be observed to achieve the performance boasted by the DG534A/538A. Some tips for minimizing stray effects are:

- Use extensive ground planes on double sided PCB separating adjacent signal paths. Multilayer PCB is even better.

- Keep signal paths as short as practically possible with all channel paths of near equal length.

- c. Use strip-line layout techniques.

Improvements in performance can be obtained by using PLCC parts instead of DIPs. The stray effects of the quad PLCC package are lower than those of the dual-in-line packages. Sockets for the PLCC packages usually increase crosstalk.

FIGURE 14. DG534A Power Supply Decoupling

#### Interfacing

Logic interfacing is easily accomplished. Comprehensive addressing and control functions are incorporated in the design.

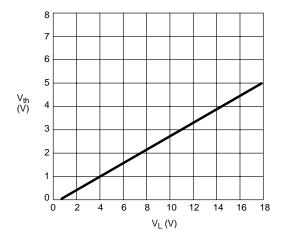

The  $V_L$  pin permits interface to various logic types. The device is primarily designed to be TTL or CMOS logic compatible with +5 V applied to  $V_L$ . The actual logic threshold can be raised simply by increasing  $V_L$ .

# VISHAY

#### **APPLICATIONS (CONT'D)**

A typical switching threshold versus V<sub>L</sub> is shown in Figure 15.

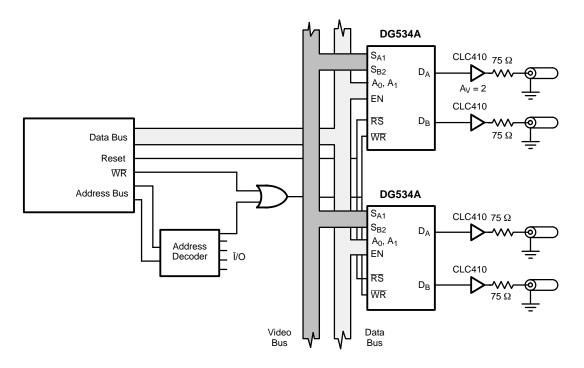

These devices feature an address readback (Tally) facility, whereby the last address written to the device may be output to the system. This allows improved status monitoring and hand shaking without additional external components.

This function is controlled by the  $\overline{I}/O$  pin, which directly addresses the tri-state buffers connected to the EN and address pins. EN and address pins can be assigned to accept data (when  $\overline{I}/O = 0$ ;  $\overline{WR} = 0$ ;  $\overline{RS} = 1$ ), or output data (when  $\overline{I}/O = 1$ ;  $\overline{WR} = 1$ ;  $\overline{RS} = 1$ ), or to reflect a high impedance and latched state (when  $\overline{I}/O = 0$ ;  $\overline{WR} = 1$ ;  $\overline{RS} = 1$ ).

When  $\overline{I}/O$  is high, the address output can sink or source current. Note that  $V_L$  is the logic high output condition. This point must be respected if  $V_L$  is varied for input logic threshold shifting.

Further control pins facilitate easy microprocessor interface. On chip address, data latches are activated by WR, which serves as a strobe type function eliminating the need for peripheral latch or memory I/O port devices. Also, for ease of interface, a direct reset function (RS) allows all latches to be cleared and switches opened. Reset should be used during power up, etc., to avoid spurious switch action. See Figure 16.

Channel address data can only be entered during  $\overline{WR}$  low, when the address latches are transparent and  $\overline{I}/O$  is low. Similarly, address readback is only operational when  $\overline{WR}$  and  $\overline{I}/O$  are high.

The Siliconix CLC410 Video amplifier is recommended as an output buffer to reduce insertion loss and to drive coaxial cables. For low power video routing applications or for unity gain input buffers CLC111/CLC114 are recommended.

FIGURE 15. Switching Threshold Voltage vs. V<sub>L</sub>

FIGURE 16. DG534A in a Video Matrix

## **Legal Disclaimer Notice**

Vishay

## **Notice**

Specifications of the products displayed herein are subject to change without notice. Vishay Intertechnology, Inc., or anyone on its behalf, assumes no responsibility or liability for any errors or inaccuracies.

Information contained herein is intended to provide a product description only. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Vishay's terms and conditions of sale for such products, Vishay assumes no liability whatsoever, and disclaims any express or implied warranty, relating to sale and/or use of Vishay products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright, or other intellectual property right.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications. Customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Vishay for any damages resulting from such improper use or sale.

Document Number: 91000 www.vishay.com

Revision: 08-Apr-05 1