THAT 1280, 1283, 1286

#### **FEATURES**

• High CMRR: typ. 90 dB at 60Hz

Self-contained

• Excellent audio performance

Wide bandwidth: typ. >7.6 MHz

- High slew rate: typ. 15  $V/\mu s$

- Low distortion: typ. 0.0006% THD

- Low noise: typ. -104.5 dBu

• Low current: typ. 3 mA (per amplifier)

• Several gains: 0 dB, ±3 dB, ±6 dB

• Industry Standard Pinout

## **APPLICATIONS**

- Balanced Audio Line Receivers

- Instrumentation Amplifiers

- Differential Amplifiers

- Precision Summers

- Current Shunt Monitors

## Description

The THAT 1280 series of precision differential amplifiers was designed primarily for use as balanced line receivers for audio applications. Gains of 0 dB,  $\pm 3$  dB, and  $\pm 6$  dB are available to suit various applications requirements.

These devices are laser-trimmed in wafer form to obtain the precision resistor matching needed for high CMR performance and precise gain. Manufactured in THAT Corporation's proprietary complementary dielectric isolation (DI) process, the 1280 series provides the sonic benefits of discrete designs with the simplicity,

reliability, matching, and small size of a fully integrated solution.

All three versions of the part typically exhibit 90 dB of common-mode rejection. With 15 V/ $\mu$ s slew rate, 7.6 MHz or higher bandwidth, and 0.0006% THD, these devices are sonically transparent. Moreover, current consumption is typically a low 6 mA (3 mA per amplifier).

The 1280 series is available in a 14-pin SOIC package. The 1280 is pin-compatible with the TI INA2134, and the 1286 is pin-compatible with the TI INA2137 and the ADI AD8273.

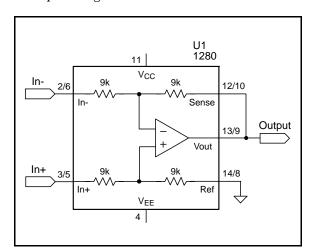

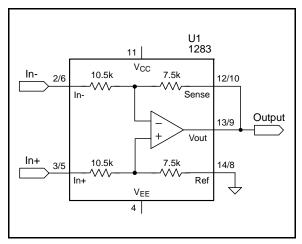

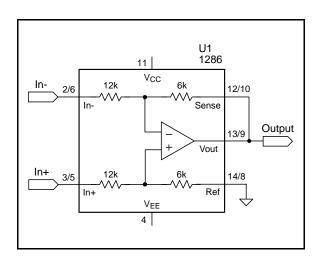

| Part No. | Gain  | R <sub>1</sub> & R <sub>3</sub> | R <sub>2</sub> & R <sub>4</sub> |

|----------|-------|---------------------------------|---------------------------------|

| THAT1280 | 0 dB  | 9 kΩ                            | 9 kΩ                            |

| THAT1283 | -3 dB | 10.5 k $\Omega$                 | <b>7.5 k</b> Ω                  |

| THAT1286 | -6 dB | <b>12 k</b> Ω                   | 6 kΩ                            |

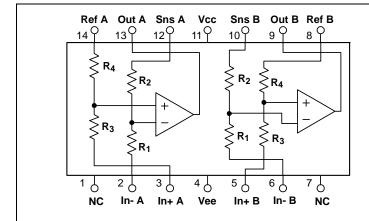

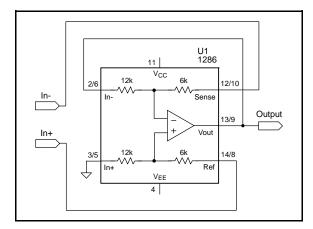

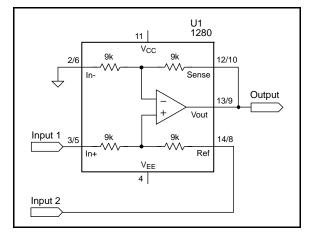

Figure 1. Equivalent circuit

| Pin Name        | Pin Number |

|-----------------|------------|

| N/C             | 1          |

| IN- A           | 2          |

| IN+ A           | 3          |

| V <sub>EE</sub> | 4          |

| IN+ B           | 5          |

| IN- B           | 6          |

| N/C             | 7          |

| REF B           | 8          |

| OUT B           | 9          |

| SENSE B         | 10         |

| V <sub>cc</sub> | 11         |

| SENSE A         | 12         |

| OUT A           | 13         |

| REF A           | 14         |

Table 1. Pin assignments

# SPECIFICATIONS<sup>1</sup>

| Absolute Maximum Ratings <sup>2,3</sup>              |                                                |                                                  |                |  |

|------------------------------------------------------|------------------------------------------------|--------------------------------------------------|----------------|--|

| Supply Voltages (V <sub>CC</sub> - V <sub>EE</sub> ) | 40V                                            | Storage Temperature Range (T <sub>ST</sub> )     | -40 to +125 °C |  |

| Maximum In₋ or In₊ Voltage                           | $-50V + V_{CC}, 50V + V_{EE}$                  | Operating Temperature Range (T <sub>OP</sub> )   | -40 to +85 °C  |  |

| Max/Min Ref or Sense Voltage                         | $V_{CC}$ + 0.5V, $V_{EE}$ - 0.5V               | Output Short-Circuit Duration (t <sub>SH</sub> ) | Continuous     |  |

| Maximum Output Voltage (V <sub>OM</sub> )            | $V_{\text{CC}}$ + 0.5V, $V_{\text{EE}}$ - 0.5V | Junction Temperature (T <sub>J</sub> )           | +125 °C        |  |

| Parameter                                 | Symbol                             | Conditions                                              | Min    | Тур          | Max | Units      |

|-------------------------------------------|------------------------------------|---------------------------------------------------------|--------|--------------|-----|------------|

|                                           |                                    |                                                         | IVIIII |              |     |            |

| Supply Current                            | I <sub>CC</sub> ; -I <sub>EE</sub> | No signal                                               | _      | 6            | 8   | mA         |

| Supply Voltage                            | $V_{\text{CC}}$ - $V_{\text{EE}}$  |                                                         | 6      | _            | 36  | V          |

| Input Voltage Range                       | $V_{\text{IN-DIFF}}$               | Differential (equal and opposite swing)                 |        |              |     |            |

|                                           |                                    | 1280 (0dB gain)                                         | _      | 21.5         | _   | dBu        |

|                                           |                                    | 1283 (-3dB gain)<br>1286 (-6dB gain)                    | _      | 24.5<br>27.5 | _   | dBu<br>dBu |

|                                           | $V_{\text{IN-CM}}$                 | Common Mode                                             |        | 27.0         |     | аВа        |

|                                           |                                    | 1280 (0dB gain)                                         | _      | 27.5         | _   | dBu        |

|                                           |                                    | 1283 (-3dB gain)                                        | _      | 29.1         | _   | dBu        |

|                                           |                                    | 1286 (-6dB gain)                                        |        | 31           |     | dBu        |

| Input Impedance <sup>5</sup>              | $Z_{\text{IN-DIFF}}$               | Differential                                            |        |              |     |            |

|                                           |                                    | 1280 (0dB gain)                                         | _      | 18           | _   | $k\Omega$  |

|                                           |                                    | 1283 (-3dB gain)                                        | _      | 21           | _   | kΩ         |

|                                           | -                                  | 1286 (-6dB gain)                                        | _      | 24           | _   | kΩ         |

|                                           | $Z_{\text{IN-CM}}$                 | Common Mode                                             |        |              |     |            |

|                                           |                                    | All versions                                            |        | 18           | _   | kΩ         |

| Common Mode Rejection Ratio               | CMRR                               | Matched source impedances; $V_{CM} = \pm 10$            | V      |              |     |            |

|                                           |                                    | DC                                                      | 70     | 90           | _   | dB         |

|                                           |                                    | 60Hz                                                    | 70     | 90           | _   | dB         |

|                                           |                                    | 20kHz                                                   | _      | 85           | _   | dB         |

| Power Supply Rejection Ratio <sup>6</sup> | PSRR                               | $\pm 3V$ to $\pm 18V$ ; $V_{CC} = -V_{EE}$ ; all gains  | _      | 90           | _   | dB         |

| Total Harmonic Distortion                 | THD                                | $V_{out} = 5Vrms$ , $f = 1kHz$ , $BW = 22kHz$ , $R_L =$ | 2 kΩ   |              |     |            |

|                                           |                                    |                                                         | _      | 0.0006       | _   | %          |

| Output Noise                              | e <sub>out</sub>                   | 22 Hz to 22kHz bandwidth                                |        |              |     |            |

|                                           |                                    | 1280 (0dB gain)                                         | _      | -104.5       | _   | dBu        |

|                                           |                                    | 1283 (-3dB gain)                                        | _      | -105.9       | _   | dBu        |

|                                           |                                    | 1286 (-6dB gain)                                        |        | -107.3       | _   | dBu        |

| Slew Rate                                 | SR                                 | $R_L = 2k\Omega$ ; $C_L = 300$ pF, all gains            | 10.5   | 15           | _   | V/μs       |

|                                           |                                    |                                                         |        |              |     |            |

<sup>1.</sup> All specifications are subject to change without notice.

2. Unless otherwise noted, T<sub>A</sub>=25°C, V<sub>CC</sub>=+15V, V<sub>EE</sub>=-15V.

3. Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only; the functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

4. 0 dBu = 0.775 Vrms.

5. While specific resisters ratios are your closely tripped, absolute resistance values can your closely tripped absolute resistance values can your closely tripped absolute resistance is

<sup>4.</sup> Ubu = 0.773 Villis.

5. While specific resistor ratios are very closely trimmed, absolute resistance values can vary ±25% from the typical values shown. Input impedance is monitored by lot sampling.

6. Defined with respect to differential gain.

7. Parameter guaranteed over the entire range of power supply and temperature.

|                              | Electrical                         | Characteristics                                                                                        | (con't)2,4           |                                          |                           |                   |

|------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------|------------------------------------------|---------------------------|-------------------|

| Parameter                    | Symbol                             | Conditions                                                                                             | Min                  | Тур                                      | Max                       | Units             |

| Small signal bandwidth       | BW <sub>-3dB</sub>                 | $R_L = 2k\Omega$ ; $C_L = 10 pF$<br>1280 (0dB gain)<br>1283 (-3dB gain)<br>1286 (-6dB gain)            | _<br>_<br>_          | 7.6<br>9.6<br>11.6                       |                           | MHz<br>MHz<br>MHz |

| Output Gain Error            | G <sub>ER-OUT</sub>                |                                                                                                        | -0.05                | _                                        | 0.05                      | dB                |

| Output Voltage Swing         | V <sub>O+</sub><br>V <sub>O-</sub> | $\begin{aligned} R_L &= 2k\Omega; \ C_L = 200 \ pF \\ R_L &= 2k\Omega; \ C_L = 200 \ pF \end{aligned}$ | V <sub>cc</sub> -2.5 | V <sub>CC</sub> -2<br>V <sub>EE</sub> +2 | —<br>V <sub>EE</sub> +2.5 | V<br>V            |

| Output Offset Voltage        | $V_{OFF}$                          | No signal                                                                                              | -1                   | _                                        | 1                         | mV                |

| Output Short Circuit Current | I <sub>sc</sub>                    | $R_L = 0 \Omega$                                                                                       | _                    | ±42                                      | _                         | mA                |

| Capacitive Load <sup>7</sup> | CL                                 |                                                                                                        | _                    | _                                        | 300                       | pF                |

| Channel Separation           |                                    | f = 1kHz                                                                                               |                      | 120                                      | _                         | dB                |

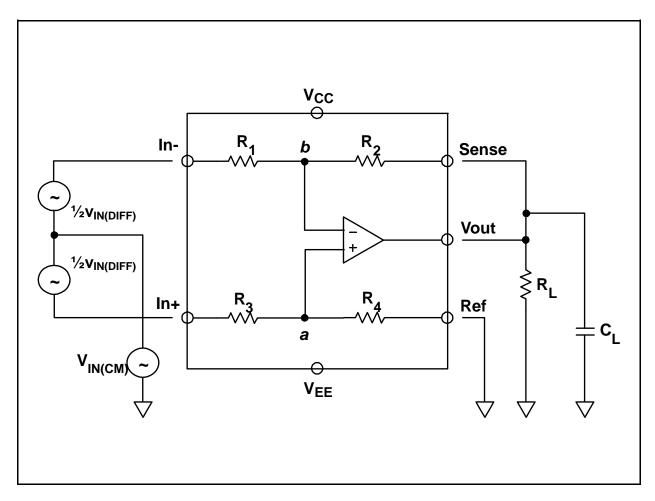

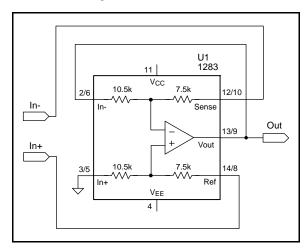

Figure 2. Simplified test circuit (1/2 of 128x shown)

## Theory of Operation

The THAT 1280 series ICs consist of two high performance opamps with integrated, laser-trimmed resistors. These designs take advantage of THAT's fully complementary dielectric isolation (DI) process to deliver excellent performance with low current consumption. The devices are simple to apply in a wide range of applications.

### Resistor Trimming, Values, and CMRR

The 1280-series devices rely upon proprietary, laser-trimmed, silicon-chromium (Si-Cr), thin-film, integrated resistors to deliver the precise matching required to achieve a 90 dB common mode rejection ratio. Trimming is performed in two cycles, both using dc inputs. First, gain is set by trimming the  $R_1/R_2$  pair. Then, CMRR is set by trimming the other pair ( $R_3/R_4$ ). Generally, only one resistor of each pair is trimmed (whichever needs to increase to meet the required specification).

To achieve 90 dB CMRR, the  $R_3/R_4$  ratio is trimmed to within  $\pm 0.005$ % of the  $R_1/R_2$  ratio. Since the resistors themselves are on the order of 10 k $\Omega$  (see Figure 1 for actual values, which change with the specific part), an increase of as little as 0.6  $\Omega$  can reduce the CMRR from over 90 dB to 84 dB. The better the starting CMRR, the more impact (in dB) a given added resistance will have.

Therefore, to achieve this high CMRR in practice, take care to ensure that all source impedances remain balanced. To accomplish this, PCB traces carrying signals should be balanced in length, connector resistance should be minimized, and any input capacitance (including strays) should be balanced between the + and - legs of the input circuitry. Note that the additional contact resistance of some sockets is sufficient to undo the effects of precision trimming. Therefore, socketing the parts is not recommended. THAT's 1200-series InGenius® input stages address many of these difficulties through a patented method of increasing commonmode input impedance, and should be considered for any critical applications.

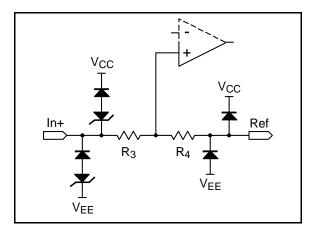

Figure 3. Representative input protection circuit

A further consideration is that after trimming, the two resistor divider ratios are tightly controlled, but the actual value of any individual resistor is not. The initial tolerance of the resistors is quite wide, so it is possible for any given resistor to vary over a surprisingly wide range. Lot-to-lot variations of up to  $\pm 30$  % are to be expected.

## Input Considerations

The 1280-series devices are internally protected against input overload via an unusual arrangement of diodes connecting the + and - input pins to the power supply pins. The circuit of Figure 3 shows the arrangement used for the  $R_{\rm 3}/R_{\rm 4}$  side; a similar one applies to the other side. The zener diodes prevent the protection network from conducting until an input pin is raised at least 50 V above  $V_{\rm CC}$  or lowered 50V below  $V_{\rm EE}$ . Thus, the protection networks protect the devices without constraining the allowable signal swing at the input pins. The reference (and sense) pins are protected via more conventional reverse-biased diodes which will conduct if these pins are raised above  $V_{\rm CC}$  or below  $V_{\rm EE}$ .

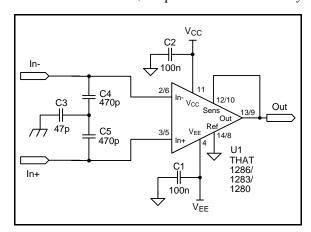

To reduce risk of damage from ESD, and to prevent RF from reaching the devices, THAT recommends the circuit of Figure 4. C<sub>3</sub> through C<sub>5</sub> should be located close to the point where the input signal comes into the chassis, preferably directly on the connector. The unusual circuit design is intended to minimize the unbalancing impact of differences in the values of C4 and C5 by forcing the capacitance from each input to chassis ground to depend primarily on the value of C3. The circuit shown is approximately ten times less sensitive to mismatches between  $C_4$  and  $C_5$  than the more conventional approach in which the junction of C4 and C5 is grounded directly. An excellent discussion of input stage grounding can be found in the June 1995 issue of the Journal of the Audio Engineering Society, Vol. 43, No. 6, in articles by Stephen Macatee, Whitlock, and others.

Note that because of the tight matching of the internal resistor ratios, coupled with the uncertainty

Figure 4. RFI and supply bypassing

in absolute value of any individual resistor, RF bypassing through the addition of R-C networks at the inputs (series resistor followed by a capacitor to ground at each input) is not recommended. The added resistors can interact with the internal ones in unexpected ways. If some impedance for the RF-bypass capacitor to work against is deemed necessary, THAT recommends the use of a ferrite bead or balun instead.

If it is necessary to ac-couple the inputs of the 1280-series parts, the coupling capacitors should be sized to present negligible impedance at any frequencies of interest for common mode rejection. Regardless of the type of coupling capacitor chosen, variations in the values of the two capacitors, working against the 1280-series input impedance (itself subject to potential imbalances in absolute value, even when trimmed for perfect ratio match), can unbalance common mode input signals. This can convert common-mode to balanced signals which will not be rejected by the CMRR of the devices. For this reason, THAT recommends dc-coupling the inputs of the 1280-series devices.

### Input Voltage Limitations

When configured, respectively, for -3 dB and -6 dB gain, the 1283 and 1286 devices are capable of accepting input signals above the power supply rails. This is because the internal opamp's inputs connect to the outside world only through the on-chip resistors  $R_1$  through  $R_4$  at nodes a and b as shown in Figure 2. Consider the following analysis.

#### Differential Input Signals

For differential signals ( $v_{\rm IN(DIFF)}$ ), the limitation to signal handling will be output clipping. The outputs of all the devices typically clip at within 2V of the supply rails. Therefore, maximum differential input signal levels are directly related to the gain and supply rails and can be calculated in dBu as follows:

$$V_{in(diff)} = 20 \log \frac{\frac{V_{CC^{-}V_{EE}} - 2V}{2}}{\frac{\sqrt{2}}{0.775}} - Gain$$

$$V_{in(diff)} = 20 \log(V_{CC} - V_{EE} - 4V) - Gain - 6.8dB$$

For example, If  $V_{\text{CC}} = 15\text{V}$ ,  $V_{\text{EE}} = -15\text{V}$ , and Gain = -3 dB, then

$$V_{in(diff)} = 20\log[15V - (-15V) - 4V] - (-3dB) - 6.8dB$$

= 24.5 dBu

#### Common-Mode Input Signals

For common-mode input signals, there is essentially no output signal. The limitation on common-mode handling is the point at which the inputs are overloaded. So, we must consider the inputs of the opamp.

For common-mode signals ( $V_{\text{IN(CM)}}$ ), the common-mode input current splits to flow through both  $R_1/R_2$  and through

$R_{\text{3}}/\!R_{\text{4}}.$  Because  $v_{\text{b}}$  is constrained to follow  $V_{\text{a}},$  we will consider only the voltage at node a.

The voltage at a can be calculated as:

$$V_a = V_{IN(CM)} \left[ \frac{R_4}{R_3 + R_4} \right]$$

Solving for v<sub>IN(CM)</sub>

$$V_{IN(CM)} = V_a \left[ \frac{R_3 + R_4}{R_4} \right]$$

For the 1280,  $(R_3+R_4)/R_4=2$ . For the 1283,  $(R_3+R_4)/R_4=2.4$ . For the 1286,  $(R_3+R_4)/R_4=3$ . Furthermore, the same constraints apply to  $v_a$  as in the differential analysis.

Following the same reasoning as above, the maximum common-mode input signal for the 1280 is  $(2V_{\rm CC}$  - 4) V, and the minimum is  $(2V_{\rm EE}+4)$  V. For the 1283, these figures are  $(2.4V_{\rm CC}$  - 4.8) V, and  $(2.4V_{\rm EE}+4.8)$  V. For the 1286, these figures are  $(3V_{\rm CC}$  - 6) V, and  $(3V_{\rm EE}+6)$  V.

Therefore, for common-mode signals and  $\pm 15~V$  rails, the 1280 will accept up to  $\sim\!26~V$  in either direction. As an ac signal, this is 52 V peak-peak, 18.4 V rms, or +27.5~dBu. With the same supply rails, the 1283 will accept up to  $\sim\!31~V$  in either direction. As an ac signal, this is 62 V peak-peak, 21.9 V rms, or +29~dBu. With the same supply rails, the 1286 will accept up to  $\sim\!39~V$  in either direction. As an ac signal, this is 78 V peak-peak, 27.6 V rms, or +31~dBu.

Of course, in the real world, differential and common-mode signals combine. The maximum signal that can be accommodated will depend on the superposition of both differential and common-mode limitations.

### **Output Considerations**

The 1280-series devices are typically capable of supplying 42 mA into a short circuit. While they will survive a short, power dissipation will rise dramatically if the output is shorted. Junction temperature must be kept under 125  $^{\circ}$ C to maintain the devices' specifications.

These devices are stable with up to 300 pF of load capacitance over the entire rated temperature range, and even more at room temperature.

#### **Power Supply Considerations**

The 1280-series parts are not particularly sensitive to the power supply, but they *do* contain wide bandwidth opamps. Accordingly, small local bypass capacitors should be located within a few inches of the supply pins on these parts, as shown in Figure 4.

## Selecting a Gain Variation

The three different parts offer different gain structures to suit different applications. The 1286 is customarily configured for -6 dB gain, but by reversing the resistor connections, it can also be configured for +6 dB. The 1283 is most often configured for -3 dB gain, but can also be configured for +3 dB. The choice of input gain is determined by the input

voltage range to be accommodated, and the power supply voltages used within the circuit.

To minimize noise and maximize signal-to-noise ratio, the input stage should be selected and configured for the highest possible gain that will ensure that maximum-level input signals will not clip the input stage or succeeding stages. For example, with  $\pm 18$  V supply rails, the 1280-series parts have a maximum output signal swing of  $\pm 23$  dBu. In order to accommodate  $\pm 24$  dBu input signals, the maximum gain for the stage is  $\pm 1$  dB. With  $\pm 15$  V supply rails, the maximum output signal swing is  $\pm 10$  dBu; here,  $\pm 3$  dB is the maximum gain. In

each case, a 1283 configured for -3 dB gain is the ideal choice. The 1280 (0 dB gain only) will not provide enough headroom at its output to support a +24 dBu input signal. The 1286 (configured for -6 dB gain) will increase noise, thus reducing dynamic range, by attenuating the input signal more than necessary to support a +24 dBu input.

In fact, for most professional audio applications, THAT recommends the -3 dB input configuration possible only with the 1283 in order to preserve dynamic range within a reasonable range of power supply voltages and external headroom limits.

## **Applications**

The THAT 1280, 1283, and 1286 are usually thought of as precision differential amplifiers with gains of zero, -3 and -6 dB respectively. These devices are primarily intended as balanced line receivers for audio applications. However, their topology lends itself to other applications as well.

#### **Basic Balanced Receiver Applications**

Figures 5, 6, and 7, respectively, show the 1280, 1286 and 1286 configured as zero, -3 dB, and -6 dB line receivers. Figures 8 and 9, respectively, show the 1283 and 1286 configured as +3 dB and +6 dB line receivers. The higher gains are achieved by swapping the positions of the resistors within each pair in regard to signal input vs. Output.

#### **Precision Summing Application**

Figure 10 shows a 1280 configured as a precision summing amplifier. This circuit uses both the In+ and Ref pins as inputs. Because of the excellent matching between the laser-trimmed resistor pairs, the output voltage is precisely equal to the sum of the two input voltages.

Figure 5. Zero dB line receiver

Figure 6. -3 dB line receiver

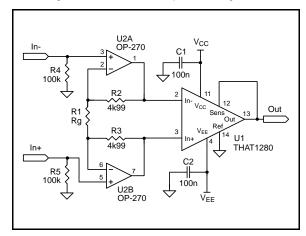

#### Instrumentation Amplifier Application

Figure 11 shows one half of a 1280 configured as an instrumentation amplifier. The two opamps preceding the 1280 buffer the input signal before passing it on to the 1280. The OP270 shown was chosen for its combination of good ac and dc performance. In this configuration, the opamps provide gain equal to  $1+(9.98 \text{ k}\Omega/\text{R}_s)$  for differential signals, but unity gain for common-mode signals. The 1280 then rejects the common mode signal while passing on the differential portion. As well, the opamps buffer the input of the 1280, raising the circuit's input impedance to both differential and common-mode signals. This makes the circuit's common-mode rejection less sensitive to variations in the source impedance driving the stage.

As noted in the Theory of Operation section, THAT's InGenius® input stages use patented circuitry to increase common-mode input impedance. This even further inproves common-mode rejection in real-world applications. See the THAT 1200-series datasheet for more information.

Figure 7. -6 dB line receiver

Figure 8. +3 dB line receiver

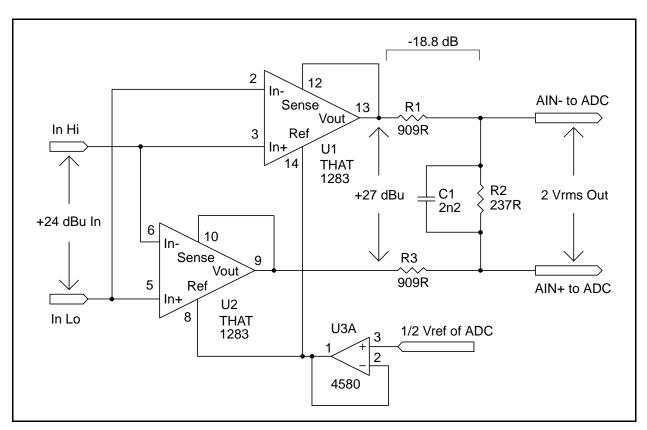

### **Driving Analog-to-Digital Converters**

Figure 12 shows a convenient method of driving a typical audio ADC with balanced inputs. This circuit accepts +24 dBu in. By using both halves of a single 1283 IC connected in anti-phase, the maximum signal level between their respective outputs is +27 dBu. An attenuator network brings

Figure 9. +6 dB line receiver

Figure 10. Precision two-input summing circuit

Figure 11. Instrumentation amplifier

this signal down by  $18.8~\mathrm{dB}$  while attenuating the noise of the line receivers as well.

In ADC applications such as this, noise is usually a significant consideration. The output noise of one channel of a THAT1283 is -105.9 dBu in a 22 kHz bandwidth, or 26.6 nV//Hz. Since both channels are used, and since noise adds in random fashion (square-root of the sum of the squares), the total noise level at the input of the resistive pad ( $R_{\rm l} \sim R_{\rm 3}$ ) will be -102.9 dBu or 37.5 nV//Hz. The pad reduces this noise level to -121.7 dBu or 4.3 nV//Hz at the input to the ADC, while  $C_{\rm l}$  provides low-pass filtering typically required by ADCs.

The thermal noise of the resistive attenuator is 1.87 nV//Hz or the equivalent noise of a 210  $\Omega$  resistor. Therefore, the total noise density going into the input of the ADC will be

$$e_{n\,ADC\,input} = \sqrt{(1.87 \frac{nV}{\sqrt{Hz}})^2 + (4.3 \frac{nV}{\sqrt{Hz}})^2} \ = 4.7 \frac{nV}{\sqrt{Hz}} \ .$$

The noise floor can then be calculated to be

Noise<sub>(dBu)</sub> = 20 log

$$\frac{4.7 \frac{nV}{\sqrt{Hz}} \times \sqrt{22kHz}}{0.775}$$

= -121 dBu.

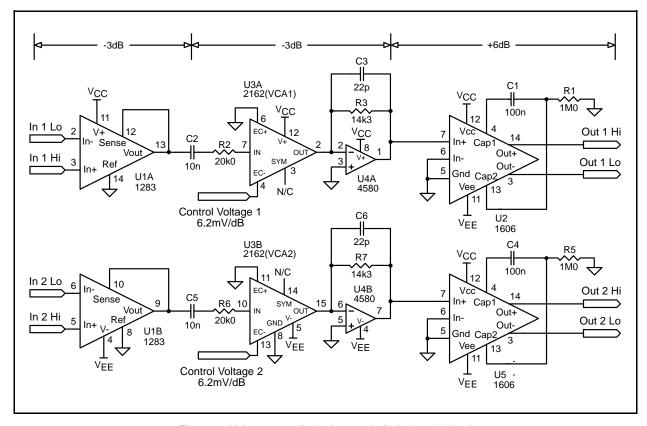

### Controlling Gain in Balanced Systems

When it becomes necessary to control gain in a balanced system, designers are often tempted to keep the signal balanced and use two Voltage Controlled Amplifiers (VCAs) to control the gain on each half of the balanced signal. Unfortunately, this can result in common-mode to differential-mode conversion (degrading CMRR) when there are even slight differences in gain between the VCAs. A better approach is to convert the signal to single-ended, alter the gain, and then convert back to balanced.

Figure 13 shows a stereo gain control for a balanced system. First, we use a 1283 -3 dB line receiver to perform the balanced to single-ended conversion. A THAT 1606, with +6dB gain, is used to rebalance the signal before the circuit's output. A THAT 2162 dual VCA is used to alter gain based on a dc voltage applied at  $E_{\rm C}$ , the "Control Voltage" node. (This point is intended to be driven from a low-impedance, low-noise voltage source. See the THAT 2162-series data sheet for details.)

As shown, the VCA section is configured for "static" gain of -3 dB (gain with 0 Vdc applied to the  $E_{\rm C}$ .) due to the choice of ratio of  $R_3$  to  $R_2$  and  $R_7$  to  $R_6$ . Additionally, the 1283 has a gain of -3 dB for a total attenuation of 6 dB before the output driver. The 1606 has a gain of 6 dB, therefore the circuit has a gain of 0 dB with 0 V at the control voltage node.

This circuit accepts and delivers over  $+24~\mathrm{dBu}$  before clipping, and has a noise floor of  $-91.5~\mathrm{dBu}$  (22 kHz bandwidth). By varying the Control Voltage, gains from  $-70~\mathrm{dB}$  to  $+40~\mathrm{dB}$  may easily be achieved. The VCA's "deci-linear" relationship between Control Voltage and gain makes the gain setting precise, predictable, and repeatable.

Figure 12. Circuit for audio ADCs with balanced inputs

Figure 13. Voltage-controlled gain control of a balanced signal

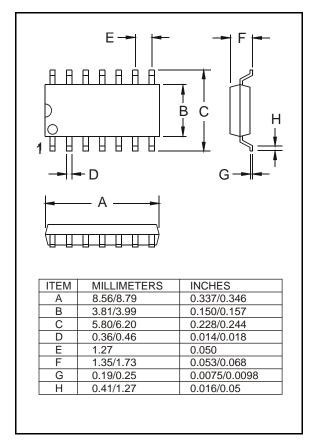

# **Package Information**

The THAT1280 series is available in a 14-pin surface mount (SOIC) package. Package dimensions are shown in Figure 14 below; Pinouts are given in Table 1 on page 1. Ordering information is provided in Table 2 below.

The 1280 series package is entirely lead-free. The lead-frame is copper, plated with successive layers of nickel, palladium, and gold. This approach makes it possible to solder these devices using lead-free and lead-bearing solders.

Neither the lead-frame nor the the plastic mold compound used in the 1280-series contains any hazardous substances as specified in the European Union's Directive on the Restriction of the Use of Certain Hazardous Substances in Electrical and Electronic Equipment 2002/95/EG of January 27, 2003.

The surface-mount package is suitable for use in a 100% tin solder process.

|                             | ]             | Package Characteristics                 | <u> </u> |              |            |            |

|-----------------------------|---------------|-----------------------------------------|----------|--------------|------------|------------|

| Parameter                   | Symbol        | Conditions                              | Min      | Тур          | Max        | Units      |

| Package Style               |               | See Fig. 14 for dimensions              |          | 14 Pin SO    |            |            |

| Thermal Resistance          | $\theta_{JA}$ | SO package soldered to board            |          | 100          |            | °C/W       |

| Environmental Regulation Co | mpliance      | Complies w                              | ith Janu | ary 27, 2003 | RoHS re    | quirements |

| Soldering Reflow Profile    |               | JE                                      | DEC JE   | SD22-A113-   | ·D (250 º0 | C)         |

| Moisture Sensitivity Level  | MSL           | Above-referenced JEDEC soldering profil | е        | 1            |            |            |

Figure 14. SO package outline drawing

| Gain  | Order Number |

|-------|--------------|

| 0 dB  | 1280S14-U    |

| -3 dB | 1283S14-U    |

| -6 dB | 1286S14-U    |

Table 2. Ordering information