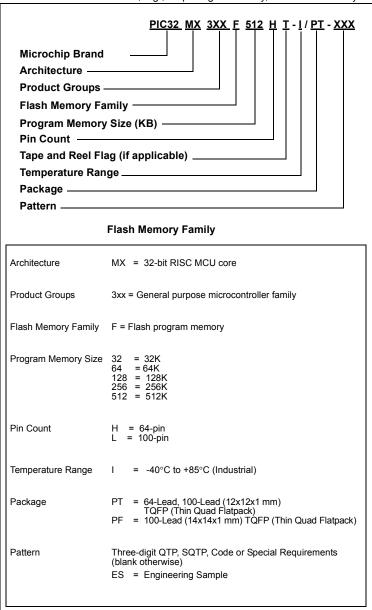

# PIC32MX Family Data Sheet

64/100-Pin General Purpose, 32-Bit Flash Microcontrollers

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, KEELOQ logo, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, rfPIC and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Linear Active Thermistor, Migratable Memory, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, Select Mode, Smart Serial, SmartTel, Total Endurance, UNI/O, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2007, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

QUALITY MANAGEMENT SYSTEM

CERTIFIED BY DNV

ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

### 64/100-Pin General Purpose, 32-Bit Flash Microcontrollers

#### **High-Performance RISC CPU:**

- MIPS32<sup>®</sup> M4K<sup>™</sup> 32-Bit Core with 5-Stage Pipeline

- Single-Cycle Multiply and High-Performance Divide Unit

- MIPS16e<sup>™</sup> Mode for Up to 40% Smaller Code Size

- User and Kernel Modes to Enable Robust Embedded System

- Two 32-Bit Core Register Files to Reduce Interrupt Latency

- Prefetch Cache Module to Speed Execution from Flash

#### **Special Microcontroller Features:**

- · Operating Voltage Range of 2.5V to 3.6V

- · 32-512K Flash and 8-32K Data Memory

- · Additional 12 KB of Boot Flash Memory

- Pin-Compatible with most PIC24/dsPIC<sup>®</sup> Devices

- · Multiple Power Management Modes

- Multiple Interrupt Vectors with Individually Programmable Priority

- · Fail-Safe Clock Monitor Mode

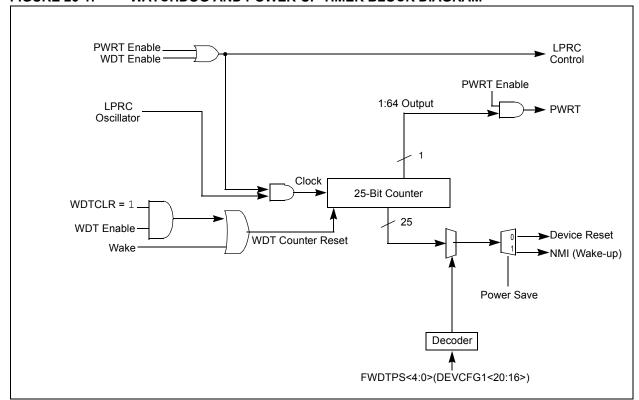

- Configurable Watchdog Timer with On-Chip, Low-Power RC Oscillator for Reliable Operation

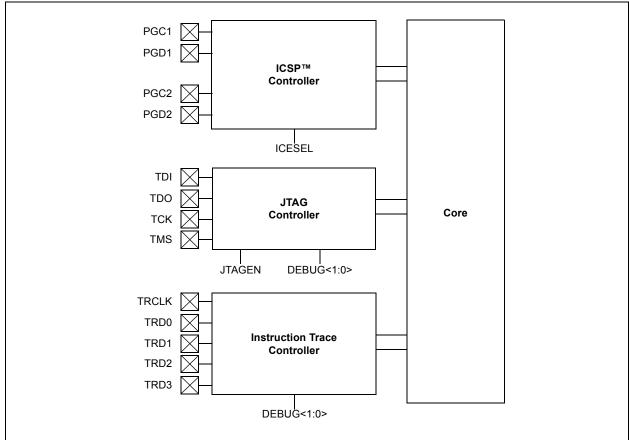

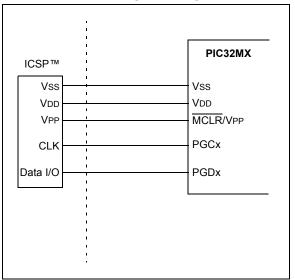

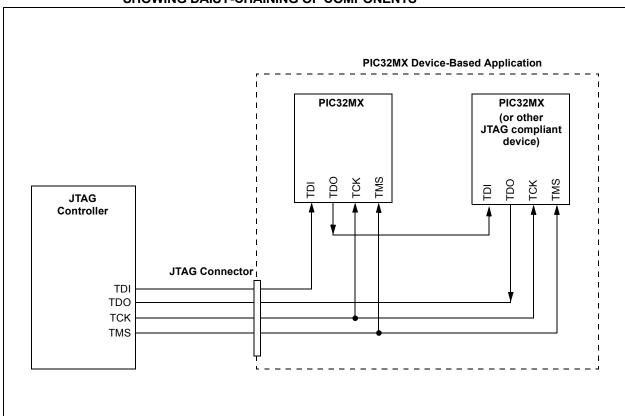

- Two Programming and Debugging Interfaces:

- 2-wire interface with unintrusive access and real-time data exchange with application

- 4-wire MIPS standard enhanced JTAG interface

- · Unintrusive Hardware-Based Instruction Trace

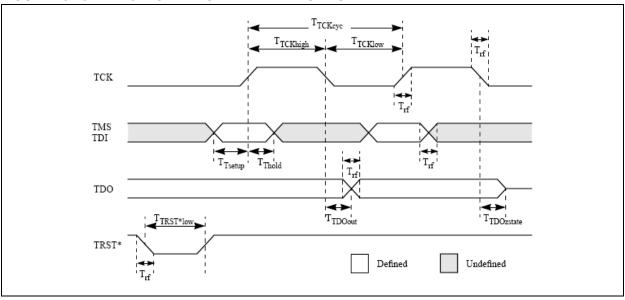

- IEEE Std 1149.2 Compatible (JTAG) Boundary Scan

#### **Analog Features:**

- Up to 16-Channel 10-Bit Analog-to-Digital Converter:

- 400 ksps conversion rate

- Conversion available during Sleep, Idle

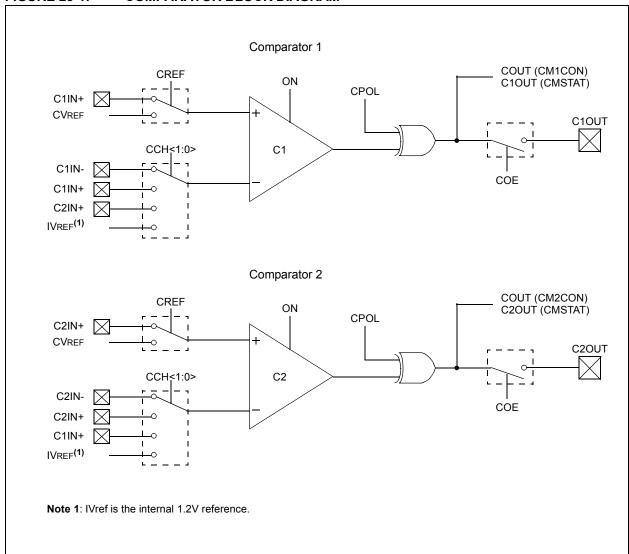

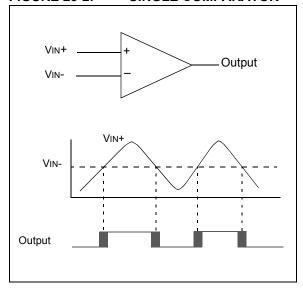

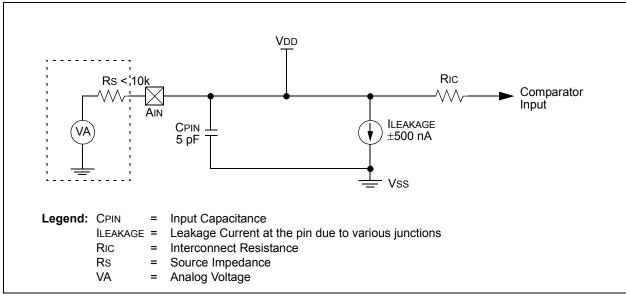

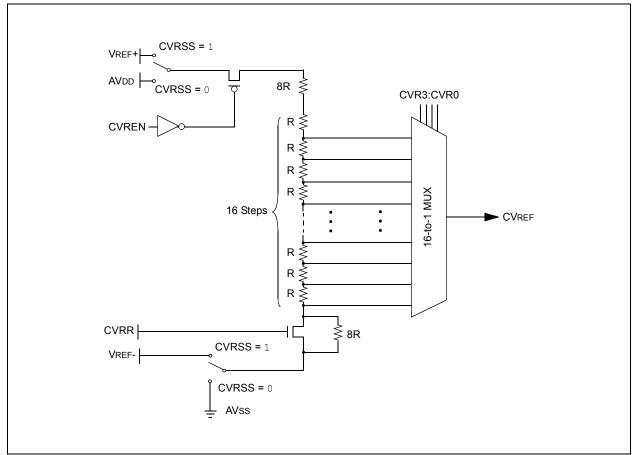

- Two Analog Comparators

#### **Peripheral Features:**

- Atomic SET, CLEAR and INVERT Operation on Select Peripheral Registers

- Up to 4-Channel Hardware DMA Controller with Automatic Data Size Detection

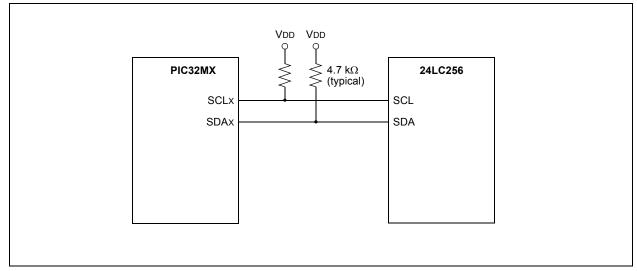

- Two I<sup>2</sup>C™ Modules

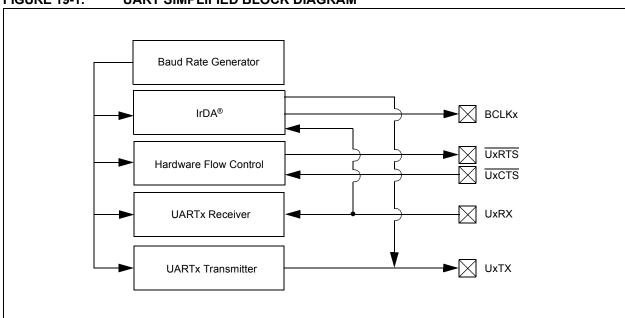

- · Two UART Modules with:

- RS-232, RS-485 and LIN 1.2 support

- IrDA<sup>®</sup> with on-chip hardware encoder and decoder

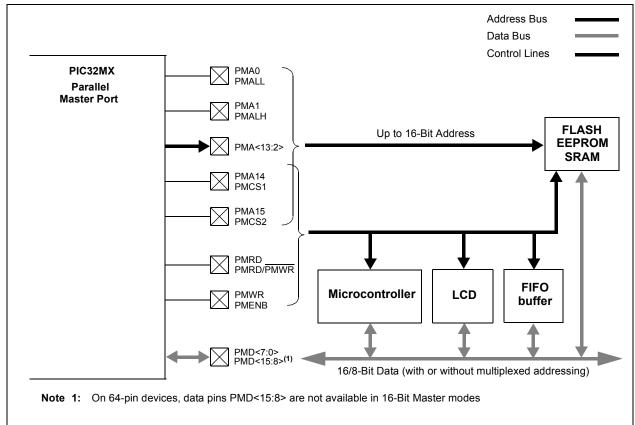

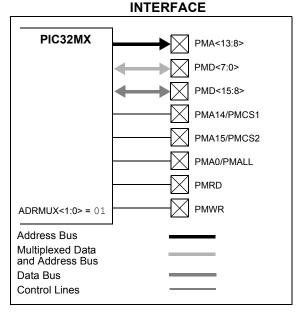

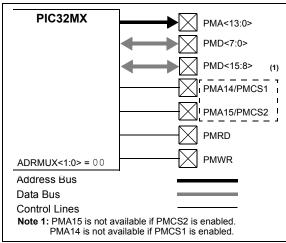

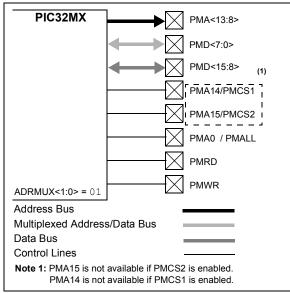

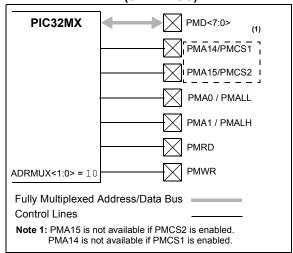

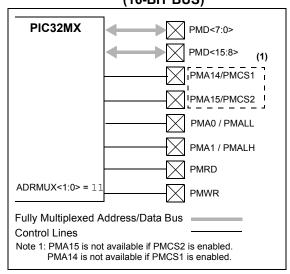

- Parallel Master and Slave Port (PMP/PSP) with 8-Bit and 16-Bit Data and Up to 16 Address Lines

- Hardware Real-Time Clock/Calendar (RTCC)

- Five 16-Bit Timers/Counters (two 16-bit pairs combine to create two 32-bit timers)

- · Five Capture Inputs

- · Five Compare/PWM Outputs

- · Five External Interrupt pins

- · 5V Tolerant Input Pins

- · 8 mA Sink/Source on Select I/O Pins

- Configurable Open-Drain Output on Digital I/O Pins

|                 | General Purpose |                                    |                                |                 |      |                   |       |                                     |                    |             |         |      |

|-----------------|-----------------|------------------------------------|--------------------------------|-----------------|------|-------------------|-------|-------------------------------------|--------------------|-------------|---------|------|

| Device          | Pins            | Program/<br>Data<br>Memory<br>(KB) | Timers/<br>Capture/<br>Compare | DMA<br>Channels | VREG | Prefetch<br>Cache | Trace | EUART/<br>SPI/<br>I <sup>2</sup> C™ | 10-Bit<br>A/D (ch) | Comparators | PMP/PSP | JTAG |

| PIC32MX300F032H | 64              | 32/8                               | 5/5/5                          | 0               | Yes  | No                | No    | 2/2/2                               | 16                 | 2           | Yes     | Yes  |

| PIC32MX320F064H | 64              | 64/16                              | 5/5/5                          | 0               | Yes  | Yes               | No    | 2/2/2                               | 16                 | 2           | Yes     | Yes  |

| PIC32MX320F128H | 64              | 128/16                             | 5/5/5                          | 0               | Yes  | Yes               | No    | 2/2/2                               | 16                 | 2           | Yes     | Yes  |

| PIC32MX340F256H | 64              | 256/32                             | 5/5/5                          | 4               | Yes  | Yes               | No    | 2/2/2                               | 16                 | 2           | Yes     | Yes  |

| PIC32MX320F128L | 100             | 128/16                             | 5/5/5                          | 0               | Yes  | Yes               | No    | 2/2/2                               | 16                 | 2           | Yes     | Yes  |

| PIC32MX360F256L | 100             | 256/32                             | 5/5/5                          | 4               | Yes  | Yes               | Yes   | 2/2/2                               | 16                 | 2           | Yes     | Yes  |

| PIC32MX360F512L | 100             | 512/32                             | 5/5/5                          | 4               | Yes  | Yes               | Yes   | 2/2/2                               | 16                 | 2           | Yes     | Yes  |

#### **Table of Contents**

| 1.0  | Device Overview                                            | 7   |

|------|------------------------------------------------------------|-----|

| 2.0  | PIC32MX MCU                                                | 19  |

| 3.0  | Instruction Set                                            | 33  |

| 4.0  | Prefetch                                                   | 39  |

| 5.0  | Direct Memory Access (DMA) Controller                      | 59  |

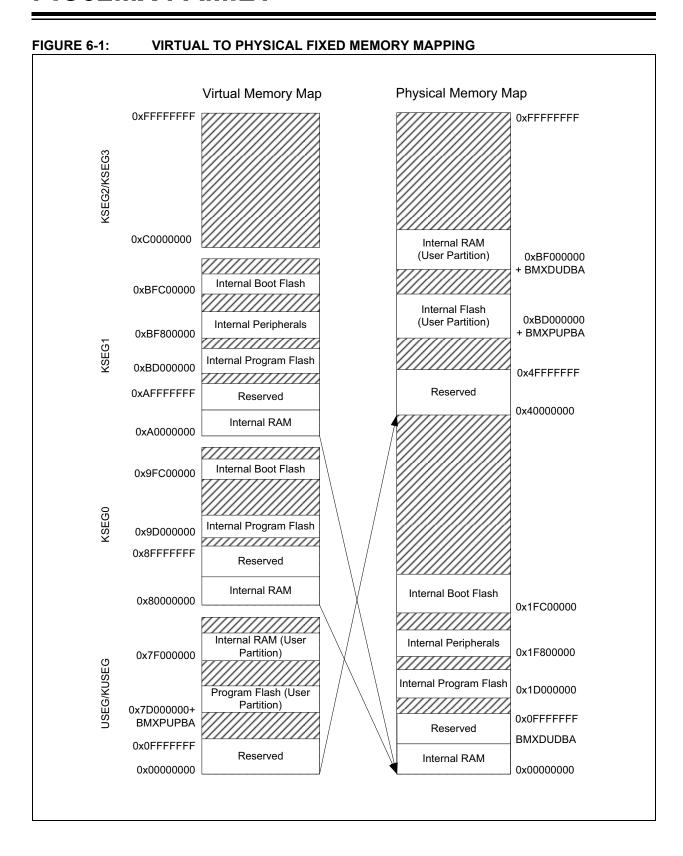

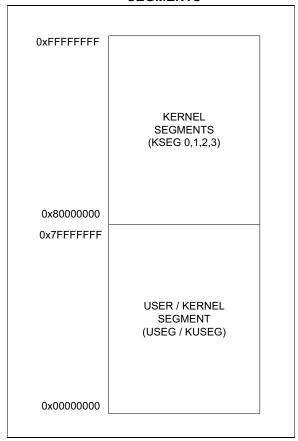

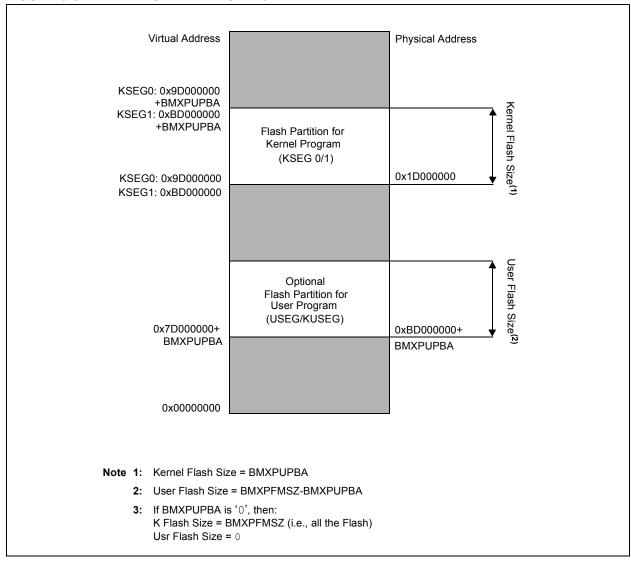

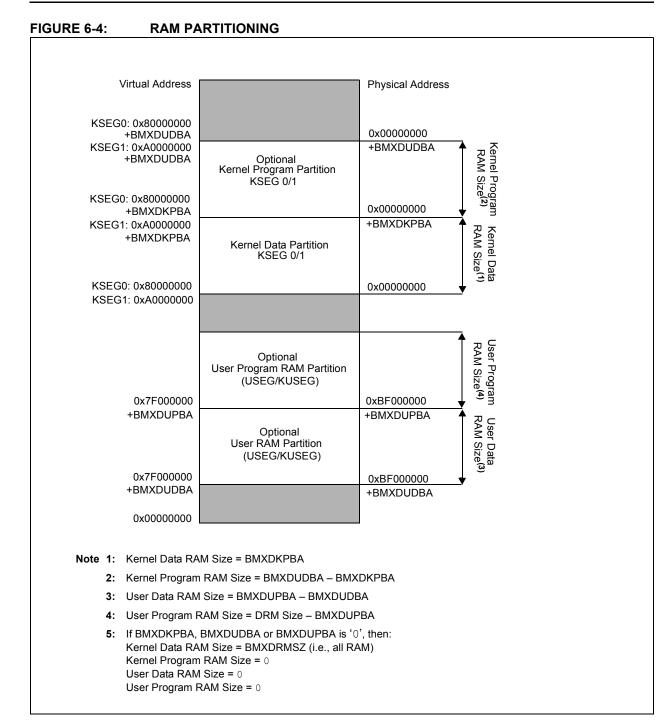

| 6.0  | Memory Organization                                        | 105 |

| 7.0  | Flash Program Memory                                       | 127 |

| 8.0  | Resets                                                     | 137 |

| 9.0  | Interrupts                                                 | 147 |

| 10.0 | Oscillators                                                | 201 |

| 11.0 | Power Saving                                               | 227 |

| 12.0 | I/O Ports                                                  | 243 |

| 13.0 | Timer1                                                     | 265 |

| 14.0 | Timers 2,3,4,5                                             | 277 |

| 15.0 | Input Capture                                              | 293 |

| 16.0 | Output Compare                                             | 301 |

| 17.0 | Serial Peripheral Interface (SPI)                          | 317 |

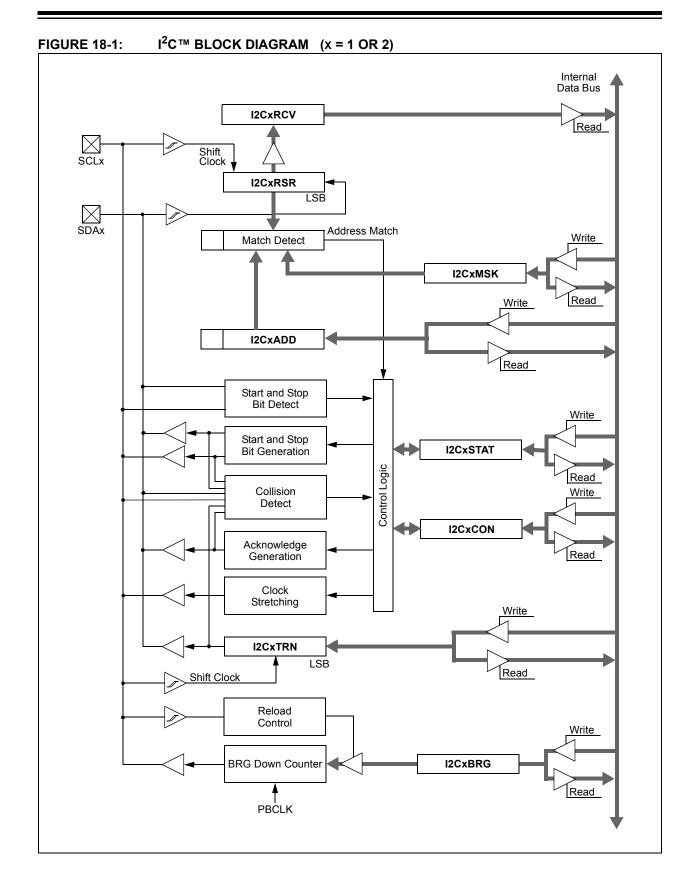

| 18.0 | Inter-Integrated Circuit (I <sup>2</sup> C <sup>TM</sup> ) | 343 |

|      | Universal Asynchronous Receiver Transmitter (UART)         |     |

| 20.0 | Parallel master port                                       | 371 |

| 21.0 | Real-Time Clock and Calendar (RTCC)                        | 399 |

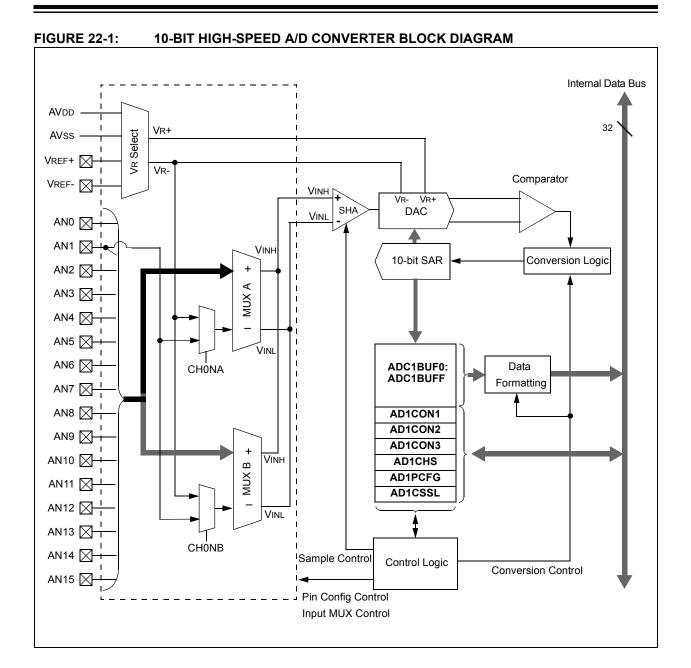

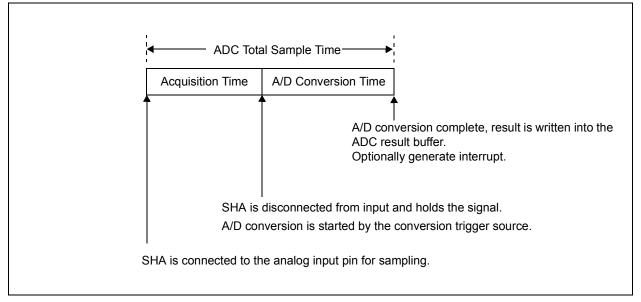

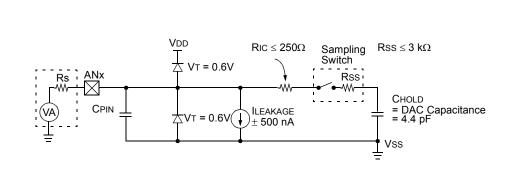

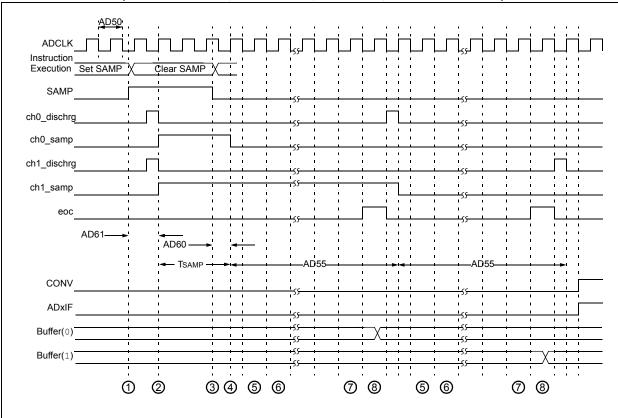

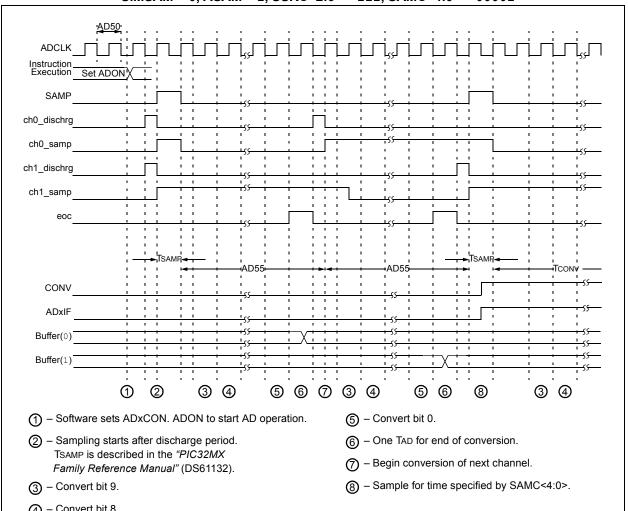

| 22.0 | Analog-Digital Converter                                   | 419 |

| 23.0 | Comparator                                                 | 447 |

| 24.0 | Comparator Reference                                       | 459 |

| 25.0 | Special Features                                           | 465 |

| 26.0 | Watchdog Timer                                             | 477 |

| 27.0 | Programming and diagnostics                                | 487 |

|      | Development Support                                        |     |

| 29.0 | Electrical Characteristics                                 | 503 |

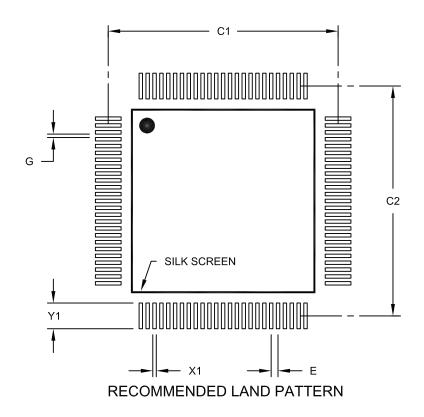

| 30 0 | Packaging Information                                      | 535 |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### **Frrata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- · Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

NOTES:

### 64/100-Pin General Purpose, 32-Bit Flash Microcontrollers

#### 1.0 DEVICE OVERVIEW

This document contains device specific information for the following devices:

- PIC32MX300F032H

- PIC32MX320F064H

- PIC32MX320F128H

- PIC32MX320F128L

- PIC32MX340F256H

- PIC32MX360F256L

- PIC32MX360F512L

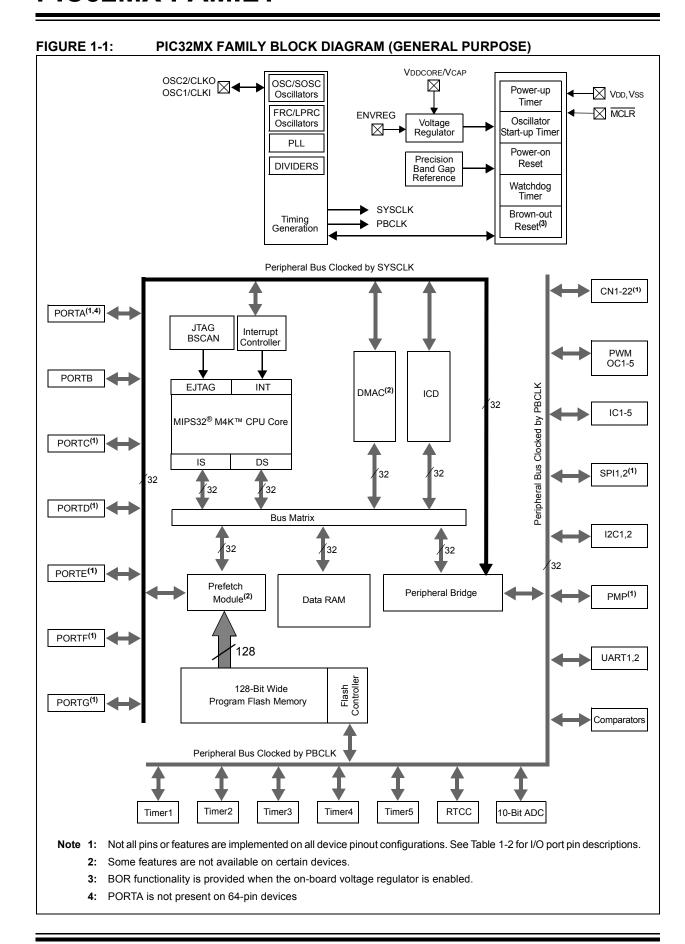

This family introduces a new line of Microchip devices: a 32-bit RISC microcontroller family with a broad peripheral feature set and enhanced computational performance. The PIC32MX Family offers a new migration option for those high-performance applications which may be outgrowing their 16-bit platforms.

#### 1.1 Easy Migration

The PIC32MX Family was designed to provide an easy migration path as the application needs change.

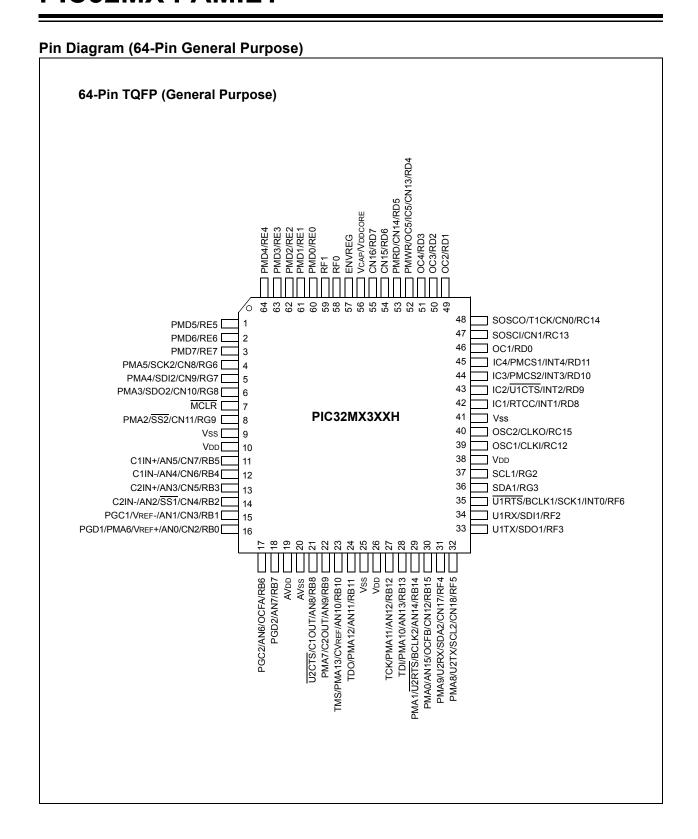

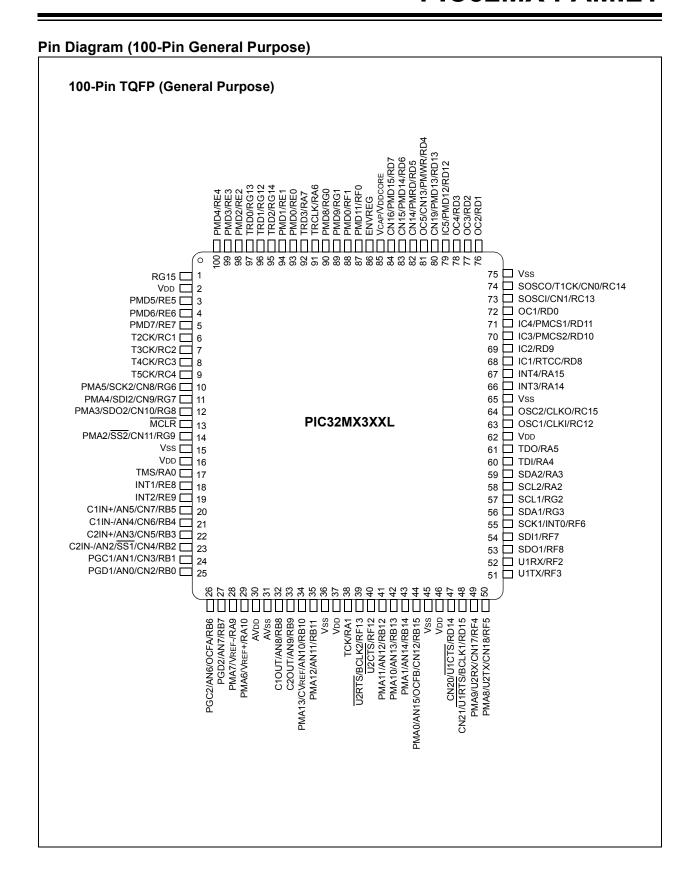

The consistent pinout scheme used throughout the entire family aids in migrating to the next larger device. This is true when moving between devices with the same pin count, or even jumping from 64-pin to 100-pin devices.

The PIC32MX Family is pin compatible with Microchip PIC24FJ128GA010 devices.

#### 1.2 Core Features

#### 1.2.1 32-BIT RISC ARCHITECTURE

Central to all PIC32MX Family devices is the 32-bit MIPS32 M4K CPU core, offering a wide range of features, such as:

- Up to 1.5 DMIPS/MHz

- · 32-bit Address and Data paths

- · 32-bit Linear (program space) addressing

- (2) thirty-two element 32-bit core register files

- Single-cycle multiply and high-performance divide unit for 32-bit integer math

- 16 and 32-bit instructions, optimized for high-level languages, such as 'C'

#### 1.3 Power-Saving Technology

All of the devices in the PIC32MX Family incorporate a range of features that can significantly reduce power consumption during operation. Key features include:

- On-the-Fly Clock Switching: The device clock can be changed under software control to any of the four clock sources during operation.

- Instruction-Based Power-Saving Modes: The microcontroller can suspend all operations, or selectively shut down its core while leaving its peripherals active, with a single instruction in software.

#### 1.4 Communications

The PIC32MX Family incorporates a range of serial communication peripherals to handle a range of application requirements. All devices are equipped with two independent UARTs with built-in IrDA encoder/decoders. There are also two independent SPI modules, and two independent I<sup>2</sup>C modules that support both Master and Slave modes of operation.

#### 1.5 10-Bit A/D Converter

The A/D Converter features 400+ ksps maximum sample rate. This configurable module incorporates a user-selectable scan list and auto-convert functions to allow acquisitions without processor intervention. Multiple A/D trigger sources are user-selectable: timer event, external pin, manual and auto-convert.

#### 1.6 External Interface

A Parallel Master Port Parallel Slave Port enables 8/16bit parallel data communications in Master mode with up to 16 address lines; 8-bit Slave modes are also supported.

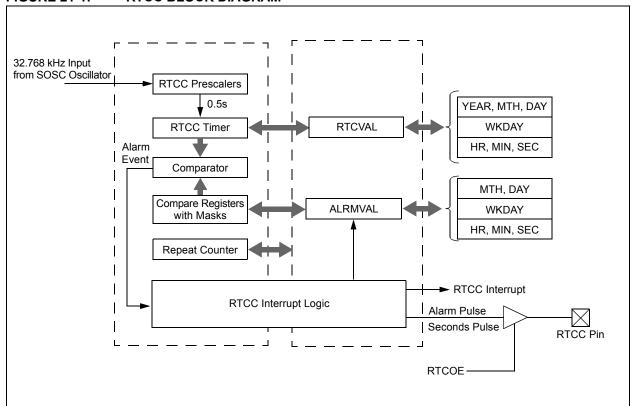

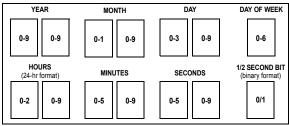

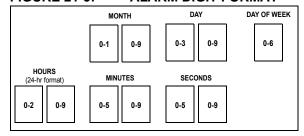

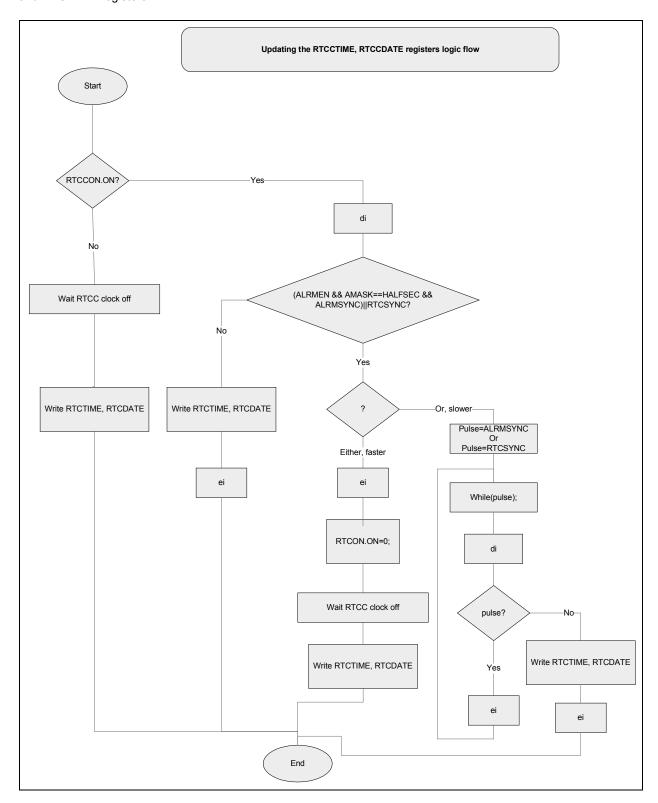

#### 1.7 Real-Time Clock/Calendar

This module implements a full-featured clock and calendar with alarm functions in hardware, freeing up timer resources and program memory space for use of the core application.

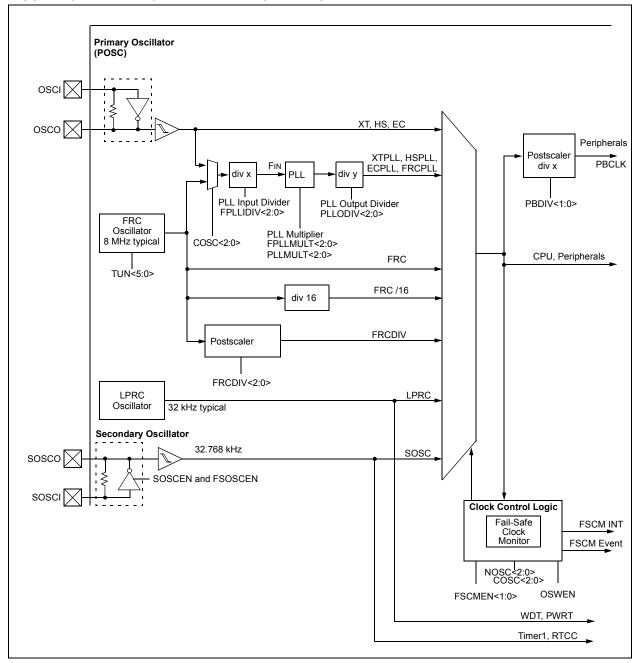

#### 1.8 Oscillator Options and Features

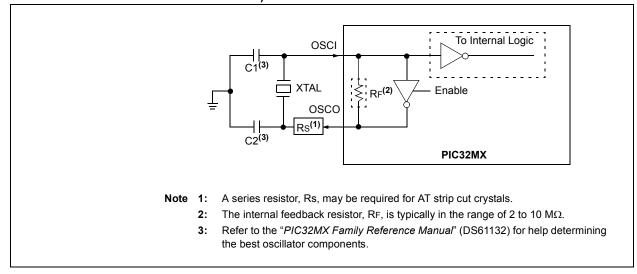

All of the devices in the PIC32MX Family offer four different oscillator options, allowing users a range of choices in developing application hardware. These include:

- A Primary Oscillator (POSC) with two External Crystal modes using crystals or ceramic resonators.

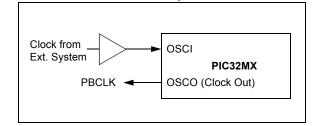

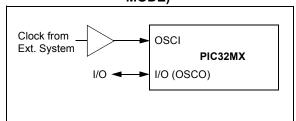

- Two External Clock modes with selectable peripheral bus clock output.

- A Fast Internal Oscillator (FRC) with a nominal 8 MHz output.

- On-board postscalers and/or PLL to provide clock speeds ranging from 31 kHz to maximum specified frequency.

- A Secondary Oscillator (SOSC) designed to operate with an external 32.768 kHz crystal. This oscillator can also be used with Timer1 and the integrated RTCC.

- An Internal Low-Power RC oscillator (LPRC)

having a fixed 31 kHz output, which provides a

low-power option for timing-insensitive

applications.

The oscillator block also provides a stable reference source for the user-controlled Fail-Safe Clock Monitor. This option constantly monitors the main clock source against a reference signal provided by the internal oscillator and enables the controller to switch to the internal oscillator, allowing for continued low-speed operation or a safe application shutdown.

# 1.9 Device Features, Block Diagrams and Pinout Tables

TABLE 1-1: DEVICE FEATURES FOR THE PIC32MX3XXFXXX GENERAL PURPOSE FAMILY

| TABLE 1-1. DEVICE                                   | FEATURES                                                                                          | . •             |                         | ,,                    |                 | KFU3E FA        |                 |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------|-------------------------|-----------------------|-----------------|-----------------|-----------------|

| Features                                            | PIC32MX300F032H                                                                                   | PIC32MX320F064H | PIC32MX320F128H         | PIC32MX340F256H       | PIC32MX320F128L | PIC32MX360F256L | PIC32MX360F512L |

| Operating Frequency                                 | DC – 20 MHz                                                                                       |                 |                         | DC - 7                | 2 MHz           |                 |                 |

| Program Memory (Bytes)                              | 32K                                                                                               | 64K             | 128K                    | 256K                  | 128K            | 256K            | 512K            |

| Data Memory (Bytes)                                 | 8K                                                                                                | 16K             | 16K                     | 32K                   | 16K             | 32K             | 32K             |

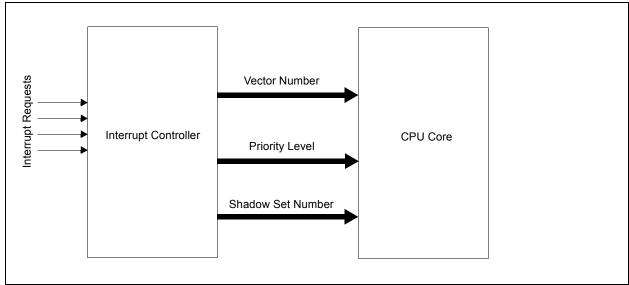

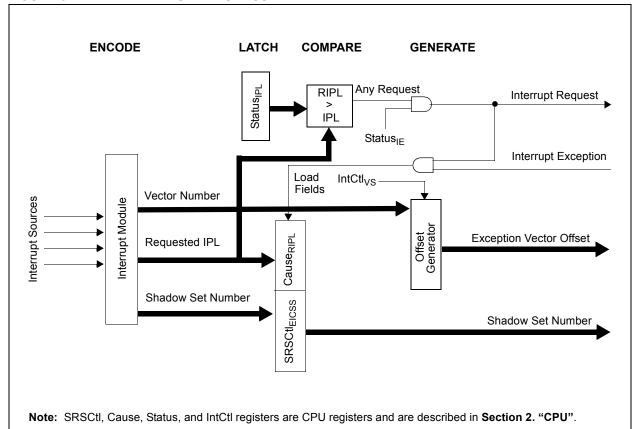

| Interrupt Sources/Vectors                           |                                                                                                   |                 |                         | 95 / 63               |                 |                 |                 |

| I/O Ports                                           |                                                                                                   | Ports B, C,     | D, E, F, G              |                       | Ports           | A, B, C, D, E   | , F, G          |

| Total I/O Pins                                      |                                                                                                   | 53              |                         |                       |                 | 85              |                 |

| DMA Channels                                        |                                                                                                   | 0               |                         | 4                     | 0               | 4               | 1               |

| Timers:                                             |                                                                                                   |                 |                         |                       |                 |                 |                 |

| Total number (16-bit)                               |                                                                                                   |                 |                         | 5                     |                 |                 |                 |

| 32-bit (paired 16-bit)                              |                                                                                                   |                 |                         | 2                     |                 |                 |                 |

| 32-bit core timer                                   |                                                                                                   |                 |                         | 1                     |                 |                 |                 |

| Input Capture Channels                              |                                                                                                   |                 |                         | 5                     |                 |                 |                 |

| Output Compare/PWM Channels                         |                                                                                                   |                 |                         | 5                     |                 |                 |                 |

| Input Change Interrupt Notification                 |                                                                                                   | 19              |                         |                       |                 | 22              |                 |

| Serial Communications:                              |                                                                                                   |                 |                         |                       |                 |                 |                 |

| Enhanced UART                                       |                                                                                                   |                 |                         | 2                     |                 |                 |                 |

| SPI (3-wire/4-wire)                                 |                                                                                                   |                 |                         | 2                     |                 |                 |                 |

| I <sup>2</sup> C™                                   |                                                                                                   |                 |                         | 2                     |                 |                 |                 |

| Parallel Communications (PMP/PSP)                   |                                                                                                   |                 |                         | Yes                   |                 |                 |                 |

| JTAG Boundary Scan                                  |                                                                                                   |                 |                         | Yes                   |                 |                 |                 |

| JTAG Debug and Program                              |                                                                                                   |                 |                         | Yes                   |                 |                 |                 |

| ICSP™ 2-Wire Debug and Program                      |                                                                                                   |                 |                         | Yes                   |                 |                 |                 |

| Instruction Trace                                   |                                                                                                   |                 | No                      |                       |                 | Ye              | es              |

| Hardware Break Points                               |                                                                                                   |                 | 6 Ins                   | truction, 2 Da        | ata             | •               |                 |

| 10-Bit Analog-to-Digital<br>Module (input channels) |                                                                                                   |                 |                         | 16                    |                 |                 |                 |

| Analog Comparators                                  |                                                                                                   |                 |                         | 2                     |                 |                 |                 |

| Internal LDO                                        |                                                                                                   |                 |                         | Yes                   |                 |                 |                 |

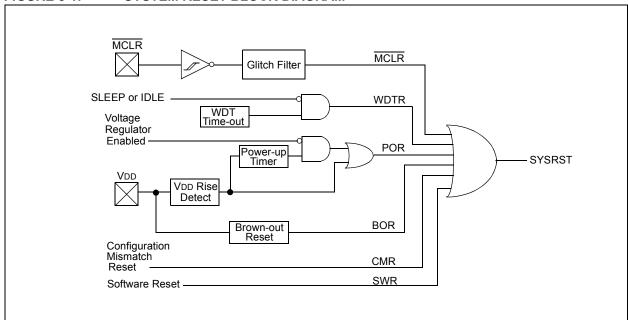

| Resets (and delays)                                 | POR, BOR, MCLR, WDT, SWR (Software Reset), CM (Configuration Bit Mismatch)  (PWRT, OST, PLL Lock) |                 |                         |                       |                 |                 |                 |

| Instruction Support                                 |                                                                                                   | MIPS            | S32 <sup>®</sup> Enhanc | ed Architectu         | ıre (Release    | 2)              |                 |

|                                                     |                                                                                                   |                 | MIPS16e™                | <sup>™</sup> Code Com | oression        |                 |                 |

| Packages                                            |                                                                                                   | 64-pin∃         | ΓQFP                    |                       |                 | 100-pin TQFF    | )               |

| · · · · · · · · · · · · · · · · · · ·               |                                                                                                   |                 |                         |                       |                 |                 |                 |

TABLE 1-2: PIC32MX FAMILY PINOUT DESCRIPTIONS – GENERAL PURPOSE

| TABLE 1-2.  | Pin Number |          |          |                 |                                      |  |

|-------------|------------|----------|----------|-----------------|--------------------------------------|--|

| Function    | 64-pin     | 100-pin  | I/O      | Input<br>Buffer | Description                          |  |

| ANO         | 16         | 25       | 1        | A N I A         | A/D Apolog Inputs                    |  |

| AN0<br>AN1  | 15         | 25       |          | ANA<br>ANA      | A/D Analog Inputs.                   |  |

| AN1<br>AN2  | 14         | 23       |          | ANA             | -                                    |  |

| AN3         | 13         | 22       | <u>'</u> | ANA             | -                                    |  |

| AN4         | 12         | 21       | '<br>    | ANA             | -                                    |  |

|             |            |          | '        |                 |                                      |  |

| AN5         | 11<br>17   | 20<br>26 | 1        | ANA             |                                      |  |

| AN6         |            |          | - 1      | ANA<br>ANA      |                                      |  |

| AN7         | 18         | 27       | 1        |                 |                                      |  |

| AN8         | 21         | 32       | I        | ANA             |                                      |  |

| AN9         | 22         | 33       | I        | ANA             |                                      |  |

| AN10        | 23         | 34       | - 1      | ANA             |                                      |  |

| AN11        | 24         | 35       | l .      | ANA             |                                      |  |

| AN12        | 27         | 41       | 1        | ANA             |                                      |  |

| AN13        | 28         | 42       | ı        | ANA             |                                      |  |

| AN14        | 29         | 43       | <u> </u> | ANA             | -                                    |  |

| AN15        | 30         | 44       | <u> </u> | ANA             |                                      |  |

| AVDD        | 19         | 30       | P        |                 | Positive Supply for Analog Modules.  |  |

| AVss        | 20         | 31       | Р        | _               | Ground Reference for Analog Modules. |  |

| BCLK1       | 35         | 48       | 0        | _               | UART1 IrDA® Baud Clock.              |  |

| BCLK2       | 29         | 39       | 0        | _               | UART2 IrDA Baud Clock.               |  |

| C1IN-       | 12         | 21       | I        | ANA             | Comparator 1 Negative Input.         |  |

| C1IN+       | 11         | 20       | I        | ANA             | Comparator 1 Positive Input.         |  |

| C1OUT       | 21         | 32       | 0        | _               | Comparator 1 Output.                 |  |

| C2IN-       | 14         | 23       | I        | ANA             | Comparator 2 Negative Input.         |  |

| C2IN+       | 13         | 22       | I        | ANA             | Comparator 2 Positive Input.         |  |

| C2OUT       | 22         | 33       | 0        | _               | Comparator 2 Output.                 |  |

| CLKI        | 39         | 63       | I        | ANA             | Main Clock Input Connection.         |  |

| CLKO        | 40         | 64       | 0        |                 | System Clock Output.                 |  |

| CN0         | 48         | 74       | I        | ST              | Interrupt-on-Change Inputs.          |  |

| CN1         | 47         | 73       | I        | ST              |                                      |  |

| CN2         | 16         | 25       | I        | ST              |                                      |  |

| CN3         | 15         | 24       | I        | ST              |                                      |  |

| CN4         | 14         | 23       | I        | ST              |                                      |  |

| CN5         | 13         | 22       | I        | ST              |                                      |  |

| CN6         | 12         | 21       | I        | ST              |                                      |  |

| CN7         | 11         | 20       | I        | ST              |                                      |  |

| CN8         | 4          | 10       | I        | ST              |                                      |  |

| CN9         | 5          | 11       | ı        | ST              |                                      |  |

| CN10        | 6          | 12       | I        | ST              |                                      |  |

| CN11        | 8          | 14       | I        | ST              |                                      |  |

| CN12        | 30         | 44       | I        | ST              |                                      |  |

| CN13        | 52         | 81       | I        | ST              |                                      |  |

| CN14        | 53         | 82       | ı        | ST              |                                      |  |

| CN15        | 54         | 83       | I        | ST              |                                      |  |

| CN16        | 55         | 84       | I        | ST              |                                      |  |

| CN17        | 31         | 49       | I        | ST              |                                      |  |

| Legend: TTL | _ TTI :    | buffor   | ·        |                 | ST = Schmitt Trigger input buffer    |  |

**Legend:** TTL = TTL input buffer

ANA = Analog level input/output

ST = Schmitt Trigger input buffer  $I^2C^{TM} = I^2C/SMBus$  input buffer

TABLE 1-2: PIC32MX FAMILY PINOUT DESCRIPTIONS – GENERAL PURPOSE (CONTINUED)

| Eunetien       | Pin N  | umber   | I/O | Input  | Degovintion                                                                                                                                                                |

|----------------|--------|---------|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Function       | 64-pin | 100-pin | 1/0 | Buffer | Description                                                                                                                                                                |

| CN18           | 32     | 50      | I   | ST     | Interrupt-on-Change Inputs.                                                                                                                                                |

| CN19           | _      | 80      | I   | ST     |                                                                                                                                                                            |

| CN20           | _      | 47      | I   | ST     |                                                                                                                                                                            |

| CN21           | _      | 48      | I   | ST     |                                                                                                                                                                            |

| CVREF          | 23     | 34      | 0   | ANA    | Comparator Voltage Reference Output.                                                                                                                                       |

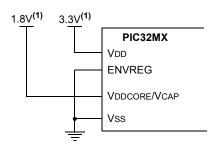

| ENVREG         | 57     | 86      | I   | ST     | Enable for On-Chip Voltage Regulator.                                                                                                                                      |

| IC1            | 42     | 68      | I   | ST     | Input Capture Inputs.                                                                                                                                                      |

| IC2            | 43     | 69      | I   | ST     |                                                                                                                                                                            |

| IC3            | 44     | 70      | I   | ST     |                                                                                                                                                                            |

| IC4            | 45     | 71      | I   | ST     |                                                                                                                                                                            |

| IC5            | 52     | 79      | I   | ST     |                                                                                                                                                                            |

| INT0           | 35     | 55      | I   | ST     | External Interrupt Inputs.                                                                                                                                                 |

| INT1           | 42     | 18      | I   | ST     |                                                                                                                                                                            |

| INT2           | 43     | 19      | I   | ST     |                                                                                                                                                                            |

| INT3           | 44     | 66      | I   | ST     |                                                                                                                                                                            |

| INT4           | 45     | 67      | I   | ST     |                                                                                                                                                                            |

| MCLR           | 7      | 13      | I   | ST     | Master Clear (Device Reset) Input. Bring this line low to cause a Reset.                                                                                                   |

| OC1            | 46     | 72      | 0   | _      | Output Compare/PWM Outputs.                                                                                                                                                |

| OC2            | 49     | 76      | 0   | _      |                                                                                                                                                                            |

| OC3            | 50     | 77      | 0   | _      |                                                                                                                                                                            |

| OC4            | 51     | 78      | 0   | _      |                                                                                                                                                                            |

| OC5            | 52     | 81      | 0   | _      |                                                                                                                                                                            |

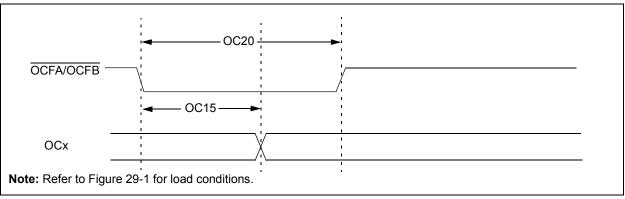

| OCFA           | 17     | 26      | I   | ST     | Output Compare Fault A Input.                                                                                                                                              |

| OCFB           | 30     | 44      | I   | ST     | Output Compare Fault B Input.                                                                                                                                              |

| OSC1           | 39     | 63      | I   | ANA    | Main Oscillator Input Connection.                                                                                                                                          |

| OSC2           | 40     | 64      | 0   | ANA    | Main Oscillator Output Connection.                                                                                                                                         |

| PGC1           | 15     | 24      | I/O | ST     | In-Circuit Debugger and ICSP™ Programming Clock                                                                                                                            |

| PGD1           | 16     | 25      | I/O | ST     | In-Circuit Debugger and ICSP Programming Data.                                                                                                                             |

| PGC2           | 17     | 26      | I/O | ST     | In-Circuit Debugger and ICSP™ Programming Clock.                                                                                                                           |

| PGD2           | 18     | 27      | I/O | ST     | In-Circuit Debugger and ICSP Programming Data.                                                                                                                             |

| PMA0/<br>PMALL | 30     | 44      | I/O | ST     | Parallel Master Port Address Bit 0 Input (Buffered Slave modes) and Output (Master modes). Parallel Master Port Address Latch Enable low-byte (Multiplexed Master modes).  |

| PMA1/<br>PMALH | 29     | 43      | I/O | ST     | Parallel Master Port Address Bit 1 Input (Buffered Slave modes) and Output (Master modes). Parallel Master Port Address Latch Enable high-byte (Multiplexed Master modes). |

**Legend:** TTL = TTL input buffer

ANA = Analog level input/output

ST = Schmitt Trigger input buffer

$I^2C^{TM} = I^2C/SMBus$  input buffer

**TABLE 1-2:** PIC32MX FAMILY PINOUT DESCRIPTIONS – GENERAL PURPOSE (CONTINUED)

|                    | Pin N  | umber   |     | Input  |                                                                                                          |

|--------------------|--------|---------|-----|--------|----------------------------------------------------------------------------------------------------------|

| Function           | 64-pin | 100-pin | I/O | Buffer | Description                                                                                              |

| PMA2               | 8      | 14      | 0   | _      | Parallel Master Port Address (Demultiplexed Master modes).                                               |

| PMA3               | 6      | 12      | 0   | _      |                                                                                                          |

| PMA4               | 5      | 11      | 0   | _      |                                                                                                          |

| PMA5               | 4      | 10      | 0   | _      |                                                                                                          |

| PMA6               | 16     | 29      | 0   | _      |                                                                                                          |

| PMA7               | 22     | 28      | 0   | _      |                                                                                                          |

| PMA8               | 32     | 50      | 0   | _      |                                                                                                          |

| PMA9               | 31     | 49      | 0   | _      |                                                                                                          |

| PMA10              | 28     | 42      | 0   | _      |                                                                                                          |

| PMA11              | 27     | 41      | 0   | _      |                                                                                                          |

| PMA12              | 24     | 35      | 0   | _      |                                                                                                          |

| PMA13              | 23     | 34      | 0   | _      |                                                                                                          |

| PMCS1/<br>PMA14    | 45     | 71      | 0   | _      | Parallel Master Port Chip Select 1 Strobe/Address bit 14.                                                |

| PMCS2/<br>PMA15    | 44     | 70      | 0   | _      | Parallel Master Port Chip Select 2 Strobe/Address bit 15.                                                |

| PMD0               | 60     | 93      | I/O | ST/TTL | Parallel Master Port Data (Demultiplexed Master mode) or Address/                                        |

| PMD1               | 61     | 94      | I/O | ST/TTL | Data (Multiplexed Master modes).                                                                         |

| PMD2               | 62     | 98      | I/O | ST/TTL |                                                                                                          |

| PMD3               | 63     | 99      | I/O | ST/TTL |                                                                                                          |

| PMD4               | 64     | 100     | I/O | ST/TTL |                                                                                                          |

| PMD5               | 1      | 3       | I/O | ST/TTL |                                                                                                          |

| PMD6               | 2      | 4       | I/O | ST/TTL |                                                                                                          |

| PMD7               | 3      | 5       | I/O | ST/TTL |                                                                                                          |

| PMD8               | _      | 90      | I/O | ST/TTL |                                                                                                          |

| PMD9               | _      | 89      | I/O | ST/TTL |                                                                                                          |

| PMD10              | _      | 88      | I/O | ST/TTL |                                                                                                          |

| PMD11              | _      | 87      | I/O | ST/TTL |                                                                                                          |

| PMD12              | _      | 79      | I/O | ST/TTL |                                                                                                          |

| PMD13              | _      | 80      | I/O | ST/TTL |                                                                                                          |

| PMD14              | _      | 83      | I/O | ST/TTL |                                                                                                          |

| PMD15              | _      | 84      | I/O | ST/TTL |                                                                                                          |

| PMRD/<br>PMRD/PMWR | 53     | 82      | 0   | _      | Parallel Master Port Read Strobe (Master Mode 2) Parallel Master Port Read/Write Strobe (Master Mode 1). |

| PMWR/<br>PMENB     | 52     | 81      | 0   | _      | Parallel Master Port Write Strobe (Master Mode 2) Parallel Master Port Enable Strobe (Master Mode 1).    |

Legend:

TTL = TTL input buffer

ANA = Analog level input/output

ST = Schmitt Trigger input buffer

$I^2C^{TM} = I^2C/SMBus$  input buffer

TABLE 1-2: PIC32MX FAMILY PINOUT DESCRIPTIONS – GENERAL PURPOSE (CONTINUED)

| TABLE 1-2. FIGSZMA FAMILT FINOUT DESCRIPTIONS - GENERAL FORFOSE (CONTINUED) |                     |         |     |        |                    |  |

|-----------------------------------------------------------------------------|---------------------|---------|-----|--------|--------------------|--|

| Function                                                                    | Function Pin Number |         | I/O | Input  | Description        |  |

| Function                                                                    | 64-pin              | 100-pin | 1/0 | Buffer | Description        |  |

| RA0                                                                         | _                   | 17      | I/O | ST     | PORTA Digital I/O. |  |

| RA1                                                                         | _                   | 38      | I/O | ST     |                    |  |

| RA2                                                                         | _                   | 58      | I/O | ST     |                    |  |

| RA3                                                                         | _                   | 59      | I/O | ST     |                    |  |

| RA4                                                                         | _                   | 60      | I/O | ST     |                    |  |

| RA5                                                                         | _                   | 61      | I/O | ST     |                    |  |

| RA6                                                                         | _                   | 91      | I/O | ST     |                    |  |

| RA7                                                                         | _                   | 92      | I/O | ST     |                    |  |

| RA9                                                                         | _                   | 28      | I/O | ST     |                    |  |

| RA10                                                                        | _                   | 29      | I/O | ST     |                    |  |

| RA14                                                                        | _                   | 66      | I/O | ST     |                    |  |

| RA15                                                                        | _                   | 67      | I/O | ST     |                    |  |

| RB0                                                                         | 16                  | 25      | I/O | ST     | PORTB Digital I/O. |  |

| RB1                                                                         | 15                  | 24      | I/O | ST     |                    |  |

| RB2                                                                         | 14                  | 23      | I/O | ST     |                    |  |

| RB3                                                                         | 13                  | 22      | I/O | ST     |                    |  |

| RB4                                                                         | 12                  | 21      | I/O | ST     |                    |  |

| RB5                                                                         | 11                  | 20      | I/O | ST     |                    |  |

| RB6                                                                         | 17                  | 26      | I/O | ST     |                    |  |

| RB7                                                                         | 18                  | 27      | I/O | ST     |                    |  |

| RB8                                                                         | 21                  | 32      | I/O | ST     |                    |  |

| RB9                                                                         | 22                  | 33      | I/O | ST     |                    |  |

| RB10                                                                        | 23                  | 34      | I/O | ST     |                    |  |

| RB11                                                                        | 24                  | 35      | I/O | ST     |                    |  |

| RB12                                                                        | 27                  | 41      | I/O | ST     |                    |  |

| RB13                                                                        | 28                  | 42      | I/O | ST     |                    |  |

| RB14                                                                        | 29                  | 43      | I/O | ST     |                    |  |

| RB15                                                                        | 30                  | 44      | I/O | ST     |                    |  |

| RC1                                                                         |                     | 6       | I/O | ST     | PORTC Digital I/O. |  |

| RC2                                                                         | _                   | 7       | I/O | ST     |                    |  |

| RC3                                                                         | _                   | 8       | I/O | ST     |                    |  |

| RC4                                                                         | _                   | 9       | I/O | ST     |                    |  |

| RC12                                                                        | 39                  | 63      | I/O | ST     |                    |  |

| RC13                                                                        | 47                  | 73      | I/O | ST     |                    |  |

| RC14                                                                        | 48                  | 74      | I/O | ST     |                    |  |

| RC15                                                                        | 40                  | 64      | I/O | ST     |                    |  |

Legend: TTL = TTL input buffer

ANA = Analog level input/output

ST = Schmitt Trigger input buffer  $I^2C^{TM} = I^2C/SMBus$  input buffer

TABLE 1-2: PIC32MX FAMILY PINOUT DESCRIPTIONS – GENERAL PURPOSE (CONTINUED)

| Fation   | Pin N  | umber   | I/O | Input  | Description.       |

|----------|--------|---------|-----|--------|--------------------|

| Function | 64-pin | 100-pin | 1/0 | Buffer | Description        |

| RD0      | 46     | 72      | I/O | ST     | PORTD Digital I/O. |

| RD1      | 49     | 76      | I/O | ST     |                    |

| RD2      | 50     | 77      | I/O | ST     |                    |

| RD3      | 51     | 78      | I/O | ST     |                    |

| RD4      | 52     | 81      | I/O | ST     |                    |

| RD5      | 53     | 82      | I/O | ST     |                    |

| RD6      | 54     | 83      | I/O | ST     |                    |

| RD7      | 55     | 84      | I/O | ST     |                    |

| RD8      | 42     | 68      | I/O | ST     |                    |

| RD9      | 43     | 69      | I/O | ST     |                    |

| RD10     | 44     | 70      | I/O | ST     |                    |

| RD11     | 45     | 71      | I/O | ST     |                    |

| RD12     | _      | 79      | I/O | ST     |                    |

| RD13     | _      | 80      | I/O | ST     |                    |

| RD14     | _      | 47      | I/O | ST     |                    |

| RD15     | _      | 48      | I/O | ST     |                    |

| RE0      | 60     | 93      | I/O | ST     | PORTE Digital I/O. |

| RE1      | 61     | 94      | I/O | ST     |                    |

| RE2      | 62     | 98      | I/O | ST     |                    |

| RE3      | 63     | 99      | I/O | ST     |                    |

| RE4      | 64     | 100     | I/O | ST     |                    |

| RE5      | 1      | 3       | I/O | ST     |                    |

| RE6      | 2      | 4       | I/O | ST     |                    |

| RE7      | 3      | 5       | I/O | ST     |                    |

| RE8      | _      | 18      | I/O | ST     |                    |

| RE9      | _      | 19      | I/O | ST     |                    |

| RF0      | 58     | 87      | I/O | ST     | PORTF Digital I/O. |

| RF1      | 59     | 88      | I/O | ST     |                    |

| RF2      | 34     | 52      | I/O | ST     |                    |

| RF3      | 33     | 51      | I/O | ST     |                    |

| RF4      | 31     | 49      | I/O | ST     |                    |

| RF5      | 32     | 50      | I/O | ST     |                    |

| RF6      | 35     | 55      | I/O | ST     |                    |

| RF7      | _      | 54      | I/O | ST     |                    |

| RF8      | _      | 53      | I/O | ST     |                    |

| RF12     | _      | 40      | I/O | ST     |                    |

| RF13     | _      | 39      | I/O | ST     |                    |

**Legend:** TTL = TTL input buffer

ANA = Analog level input/output

ST = Schmitt Trigger input buffer  $I^2C^{TM} = I^2C/SMBus$  input buffer

TABLE 1-2: PIC32MX FAMILY PINOUT DESCRIPTIONS – GENERAL PURPOSE (CONTINUED)

| F        | Pin Nu | umber   |     | Input            | Book and all the                               |

|----------|--------|---------|-----|------------------|------------------------------------------------|

| Function | 64-pin | 100-pin | I/O | Buffer           | Description                                    |

| RG0      |        | 90      | I/O | ST               | PORTG Digital I/O.                             |

| RG1      |        | 89      | I/O | ST               |                                                |

| RG2      | 37     | 57      | I/O | ST               |                                                |

| RG3      | 36     | 56      | I/O | ST               |                                                |

| RG6      | 4      | 10      | I/O | ST               |                                                |

| RG7      | 5      | 11      | I/O | ST               |                                                |

| RG8      | 6      | 12      | I/O | ST               |                                                |

| RG9      | 8      | 14      | I/O | ST               |                                                |

| RG12     | 1      | 96      | I/O | ST               |                                                |

| RG13     | -      | 97      | I/O | ST               |                                                |

| RG14     | -      | 95      | I/O | ST               |                                                |

| RG15     | -      | 1       | I/O | ST               |                                                |

| RTCC     | 42     | 68      | 0   | _                | Real-Time Clock Alarm Output.                  |

| SCK1     | 35     | 55      | 0   | _                | SPI1 Serial Clock Output.                      |

| SCK2     | 4      | 10      | I/O | ST               | SPI2 Serial Clock Output.                      |

| SCL1     | 37     | 57      | I/O | I <sup>2</sup> C | I2C1 Synchronous Serial Clock Input/Output.    |

| SCL2     | 32     | 58      | I/O | I <sup>2</sup> C | I2C2 Synchronous Serial Clock Input/Output.    |

| SDA1     | 36     | 56      | I/O | I <sup>2</sup> C | I2C1 Data Input/Output.                        |

| SDA2     | 31     | 59      | I/O | I <sup>2</sup> C | I2C2 Data Input/Output.                        |

| SDI1     | 34     | 54      | I   | ST               | SPI1 Serial Data Input.                        |

| SDI2     | 5      | 11      | I   | ST               | SPI2 Serial Data Input.                        |

| SDO1     | 33     | 53      | 0   | _                | SPI1 Serial Data Output.                       |

| SDO2     | 6      | 12      | 0   | _                | SPI2 Serial Data Output.                       |

| SOSCI    | 47     | 73      | 1   | ANA              | Secondary Oscillator/Timer1 Clock Input.       |

| SOSCO    | 48     | 74      | 0   | ANA              | Secondary Oscillator/Timer1 Clock Output.      |

| SS1      | 14     | 23      | I/O | ST               | Slave Select Input/Frame Select Output (SPI1). |

| SS2      | 8      | 14      | I/O | ST               | Slave Select Input/Frame Select Output (SPI2). |

| T1CK     | 48     | 74      | I   | ST               | Timer1 Clock.                                  |

| T2CK     |        | 6       | I   | ST               | Timer2 External Clock Input.                   |

| T3CK     |        | 7       | I   | ST               | Timer3 External Clock Input.                   |

| T4CK     | _      | 8       | I   | ST               | Timer4 External Clock Input.                   |

| T5CK     |        | 9       | I   | ST               | Timer5 External Clock Input.                   |

| TCK      | 27     | 38      | I   | ST               | JTAG Test Clock/Programming Clock Input.       |

| TDI      | 28     | 60      | I   | ST               | JTAG Test Data/Programming Data Input.         |

| TDO      | 24     | 61      | 0   | _                | JTAG Test Data Output.                         |

| TMS      | 23     | 17      | I   | ST               | JTAG Test Mode Select Input.                   |

| TRCLK    | _      | 91      | 0   | _                | Trace Clock.                                   |

| TRD0     |        | 97      | 0   | -                | Trace Data Bit 0.                              |

| TRD1     | _      | 96      | 0   | _                | Trace Data Bit 1.                              |

| TRD2     | _      | 95      | 0   | _                | Trace Data Bit 2.                              |

| TRD3     | _      | 92      | 0   | _                | Trace Data Bit 3.                              |

Legend: TT

TTL = TTL input buffer

ANA = Analog level input/output

ST = Schmitt Trigger input buffer

$I^2C^{TM} = I^2C/SMBus$  input buffer

TABLE 1-2: PIC32MX FAMILY PINOUT DESCRIPTIONS – GENERAL PURPOSE (CONTINUED)

| Function | Pin Nu     | umber                 | 1/0 | Input                         | Description                                                          |  |

|----------|------------|-----------------------|-----|-------------------------------|----------------------------------------------------------------------|--|

| Function | 64-pin     | 100-pin               | 1/0 | Buffer                        | Description                                                          |  |

| U1CTS    | 43         | 47                    | I   | ST UART1 Clear to Send Input. |                                                                      |  |

| U1RTS    | 35         | 48                    | 0   | _                             | UART1 Request to Send Output.                                        |  |

| U1RX     | 34         | 52                    | I   | ST                            | UART1 Receive.                                                       |  |

| U1TX     | 33         | 51                    | 0   | DIG                           | UART1 Transmit Output.                                               |  |

| U2CTS    | 21         | 40                    | 1   | ST                            | UART2 Clear to Send Input.                                           |  |

| U2RTS    | 29         | 39                    | 0   | _                             | UART2 Request to Send Output.                                        |  |

| U2RX     | 31         | 49                    | - 1 | ST                            | UART 2 Receive Input.                                                |  |

| U2TX     | 32         | 50                    | 0   | _                             | UART2 Transmit Output.                                               |  |

| VDD      | 10, 26, 38 | 2, 16, 37,<br>46, 62  | Р   | _                             | Positive Supply for Peripheral Digital Logic and I/O pins.           |  |

| VDDCAP   | 56         | 85                    | Р   | _                             | External Filter Capacitor Connection (regulator enabled).            |  |

| VDDCORE  | 56         | 85                    | Р   | _                             | Positive Supply for Microcontroller Core Logic (regulator disabled). |  |

| VREF-    | 15         | 28                    | _   | ANA                           | A/D and Comparator Reference Voltage (Low) Input.                    |  |

| VREF+    | 16         | 29                    | I   | ANA                           | A/D and Comparator Reference Voltage (High) Input.                   |  |

| Vss      | 9, 25, 41  | 15, 36,<br>45, 65, 75 | Р   | _                             | Ground Reference for Logic and I/O pins.                             |  |

**Legend:** TTL = TTL input buffer ANA = Analog level input/output

ST = Schmitt Trigger input buffer $I^2C^{TM} = I^2C/SMBus input buffer$

NOTES:

#### 2.0 PIC32MX MCU

Note:

This data sheet summarizes the features of the PIC32MX of devices. It is not intended to be a comprehensive reference source. Refer to the "PIC32MX Family Reference Manual" (DS61132) for a detailed description of this peripheral.

The MCU module is the heart of the PIC32MX processor. The MCU fetches instructions, decodes each instruction, fetches source operands, executes each instruction, and writes the results of instruction execution to the proper destinations.

#### 2.1 Features

- · 5-stage pipeline

- · 32-bit Address and Data Paths

- MIPS32 Enhanced Architecture (Release 2)

- Multiply-Accumulate and Multiply-Subtract Instructions

- Targeted Multiply Instruction

- Zero/One Detect Instructions

- Wait Instruction

- Conditional Move Instructions (MOVN, MOVZ)

- Vectored interrupts

- Programmable exception vector base

- Atomic interrupt enable/disable

- GPR shadow registers to minimize latency for interrupt handlers

- Bit field manipulation instructions

- MIPS16e<sup>™</sup> Code Compression

- 16 bit encodings of 32 bit instructions to improve code density

- Special PC-relative instructions for efficient loading of addresses and constants

- SAVE & RESTORE macro instructions for setting up and tearing down stack frames within subroutines

- Improved support for handling 8 and 16 bit data types

- Simple Fixed Mapping Translation (FMT) mechanism

- · Simple Dual Bus Interface

- Independent 32-bit address and data busses

- Transactions can be aborted to improve interrupt latency

- · Autonomous Multiply/Divide Unit

- Maximum issue rate of one 32x16 multiply per clock

- Maximum issue rate of one 32x32 multiply every other clock

- Early-in iterative divide. Minimum 11 and maximum 34 clock latency (dividend (rs) sign extension-dependent)

- · Power Control

- Minimum frequency: 0 MHz

- Low-Power mode (triggered by WAIT instruction)

- Extensive use of local gated clocks

- · EJTAG Debug and Instruction Trace

- Support for single stepping

- Virtual instruction and data address/value breakpoints

- PC tracing w/ trace compression

#### 2.2 Architecture Overview

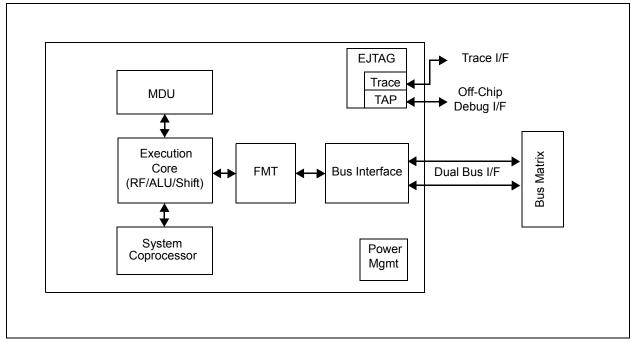

The PIC32MX core contains several logic blocks working together in parallel, providing an efficient high performance computing engine. The blocks included with the PIC32MX core are as follows:

- · Execution Unit

- Multiply/Divide Unit (MDU)

- System Control Coprocessor (CP0)

- · Fixed Mapping Translation (FMT)

- Dual Internal Bus interfaces

- · Power Management

- · MIPS16e support

- Enhanced JTAG (EJTAG) Controller

FIGURE 2-1: MCU BLOCK DIAGRAM

#### 2.2.1 EXECUTION UNIT

The PIC32MX core execution unit implements a load/ store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous multiply/divide unit. The PIC32MX core contains thirty-two 32-bit general-purpose registers used for integer operations and address calculation. One additional register file shadow set (containing thirty-two registers) is added to minimize context switching overhead during interrupt/exception processing. The register file consists of two read ports and one write port and is fully bypassed to minimize operation latency in the pipeline.

The execution unit includes:

- · 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction address

- Logic for branch determination and branch target address calculation

- Load aligner

- Bypass multiplexers used to avoid stalls when executing instructions streams where data producing instructions are followed closely by consumers of their results

- Leading Zero/One detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing bitwise logical operations

- Shifter & Store Aligner

#### 2.2.2 MULTIPLY/DIVIDE UNIT (MDU)

The PIC32MX core includes a multiply/divide unit (MDU) that contains a separate pipeline for multiply and divide operations. This pipeline operates in parallel with the integer unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows MDU operations to be partially masked by system stalls and/ or other integer unit instructions.

The high-performance MDU consists of a 32x16 booth recoded multiplier, result/accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic. The first number shown ('32' of 32x16) represents the *rs* operand. The second number ('16' of 32x16) represents the *rt* operand. The PIC32MX core only checks the value of the latter (*rt*) operand to determine how many times the operation must pass through the multiplier. The 16x16 and 32x16 operations pass through the multiplier once. A 32x32 operation passes through the multiplier twice.

The MDU supports execution of one 16x16 or 32x16 multiply operation every clock cycle; 32x32 multiply operations can be issued every other clock cycle. Appropriate interlocks are implemented to stall the issuance of back-to-back 32x32 multiply operations. The multiply operand size is automatically determined by logic built into the MDU.

Divide operations are implemented with a simple 1 bit per clock iterative algorithm. An early-in detection checks the sign extension of the dividend (*rs*) operand. If rs is 8 bits wide, 23 iterations are skipped. For a 16-bit-wide rs, 15 iterations are skipped, and for a 24-bit-wide rs, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline stall until the divide operation is completed.

Table 2-1 lists the repeat rate (peak issue rate of cycles until the operation can be reissued) and latency (number of cycles until a result is available) for the PIC32MX core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks.

### PIC32MX

TABLE 2-1: PIC32MX CORE HIGH-PERFORMANCE INTEGER MULTIPLY/DIVIDE UNIT LATENCIES AND REPEAT RATES

| Opcode                  | Operand Size (mul rt) (div rs) | Latency | Repeat Rate |

|-------------------------|--------------------------------|---------|-------------|

| MULT/MULTU, MADD/MADDU, | 16 bits                        | 1       | 1           |

| MSUB/MSUBU              | 32 bits                        | 2       | 2           |

| MUL                     | 16 bits                        | 2       | 1           |

|                         | 32 bits                        | 3       | 2           |

| DIV/DIVU                | 8 bits                         | 12      | 11          |

|                         | 16 bits                        | 19      | 18          |

|                         | 24 bits                        | 26      | 25          |

|                         | 32 bits                        | 33      | 32          |

The MIPS architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the general-purpose register file.

In addition to the HI/LO targeted operations, the MIPS32 architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction, required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, multiply-add (MADD) and multiply-subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

# 2.2.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation, the exception control system, the processor's diagnostics capability, the operating modes (kernel, user, and debug), and whether interrupts are enabled or disabled. Configuration information, such as presence of options like MIPS16e, is also available by accessing the CP0 registers, listed in Table 2-2.

TABLE 2-2: COPROCESSOR 0 REGISTERS

| Register<br>Number | Register<br>Name        | Function                                                                |

|--------------------|-------------------------|-------------------------------------------------------------------------|

| 0-6                | Reserved                | Reserved in the PIC32MX core                                            |

| 7                  | HWREna                  | Enables access via the RDHWR instruction to selected hardware registers |

| 8                  | BadVAddr <sup>(1)</sup> | Reports the address for the most recent address-related exception       |

| 9                  | Count <sup>(1)</sup>    | Processor cycle count                                                   |

| 10                 | Reserved                | Reserved in the PIC32MX core                                            |

| 11                 | Compare <sup>(1)</sup>  | Timer interrupt control                                                 |

| 12                 | Status <sup>(1)</sup>   | Processor status and control                                            |

| 12                 | IntCtl <sup>(1)</sup>   | Interrupt system status and control                                     |

| 12                 | SRSCtl <sup>(1)</sup>   | Shadow register set status and control                                  |

| 12                 | SRSMap <sup>(1)</sup>   | Provides mapping from vectored interrupt to a shadow set                |

| 13                 | Cause <sup>(1)</sup>    | Cause of last general exception                                         |

| 14                 | EPC <sup>(1)</sup>      | Program counter at last exception                                       |

| 15                 | PRId                    | Processor identification and revision                                   |

| 15                 | EBASE                   | Exception vector base register                                          |

| 16                 | Config                  | Configuration register                                                  |

| 16                 | Config1                 | Configuration register 1                                                |

| 16                 | Config2                 | Configuration register 2                                                |

| 16                 | Config3                 | Configuration register 3                                                |

| 17-22              | Reserved                | Reserved in the PIC32MX core                                            |

| 23                 | Debug <sup>(2)</sup>    | Debug control and exception status                                      |

| 24                 | DEPC <sup>(2)</sup>     | Program counter at last debug exception.                                |

| 25-29              | Reserved                | Reserved in the PIC32MX core.                                           |

| 30                 | ErrorEPC <sup>(1)</sup> | Program counter at last error.                                          |

| 31                 | DESAVE <sup>(2)</sup>   | Debug handler scratchpad register.                                      |

Note 1: Registers used in exception processing.

2: Registers used during debug.

### PIC32MX

Coprocessor 0 also contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including alignment errors in data, external events, or program errors. Table 2-3 shows the exception types in order of priority.

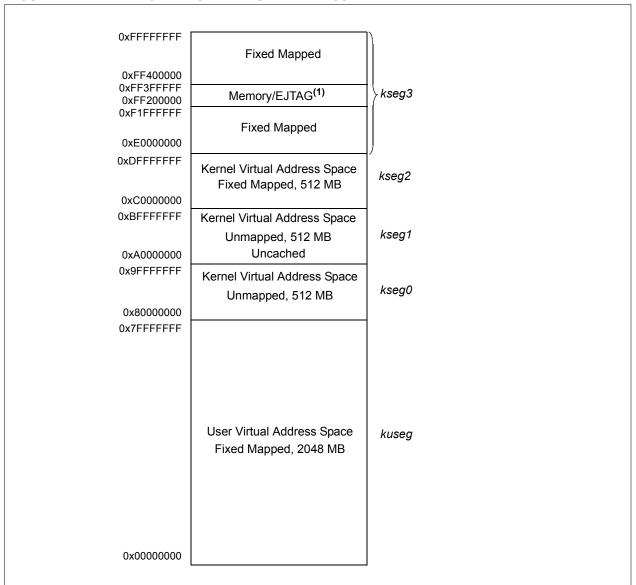

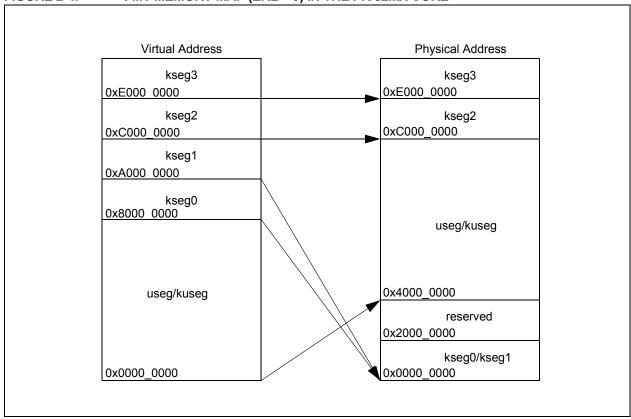

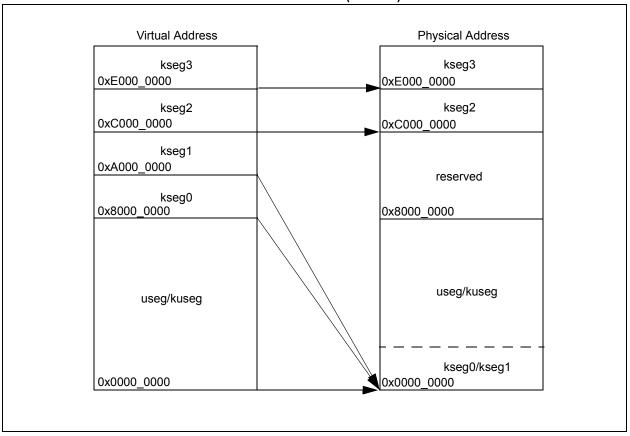

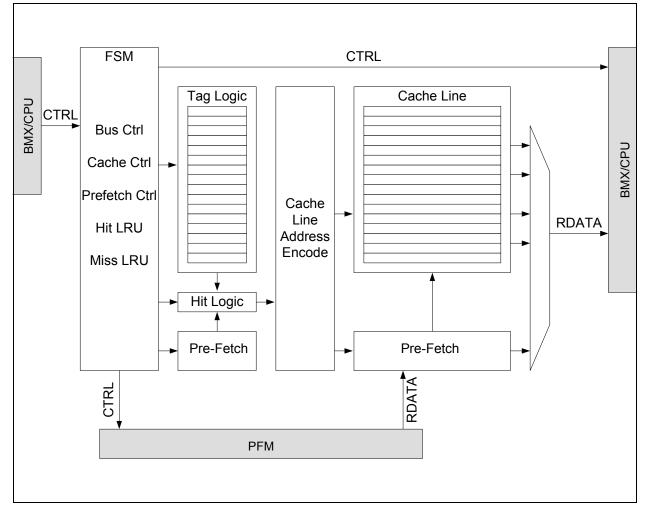

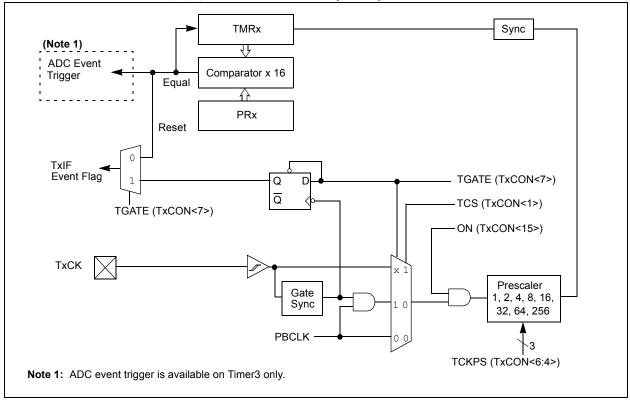

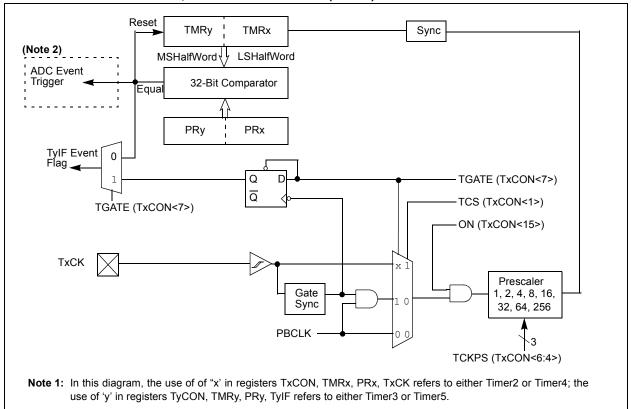

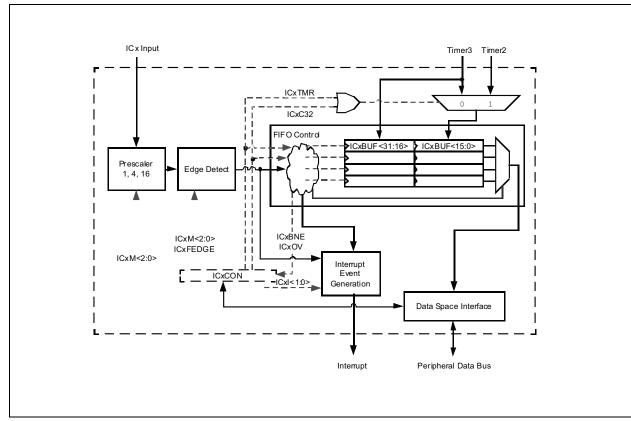

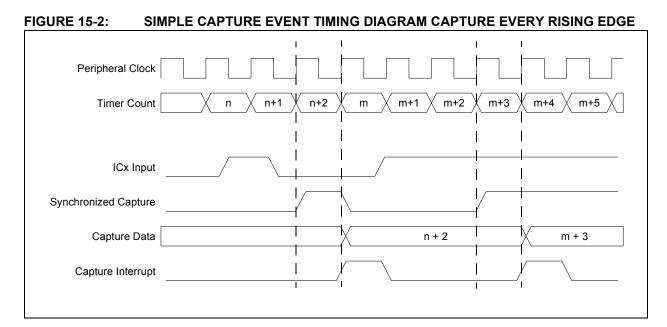

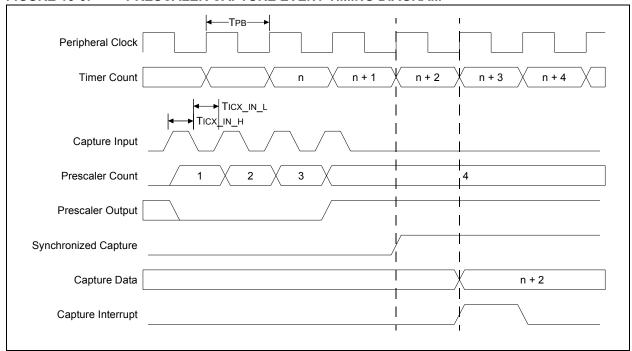

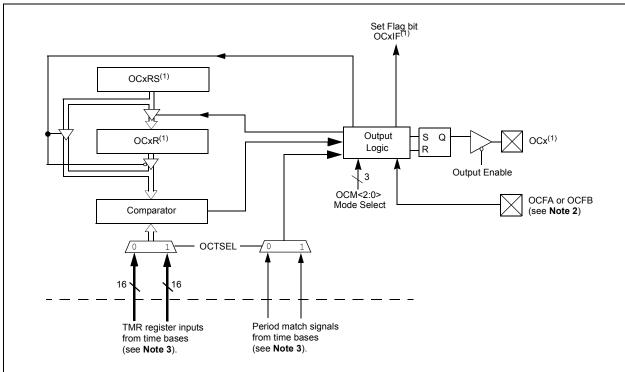

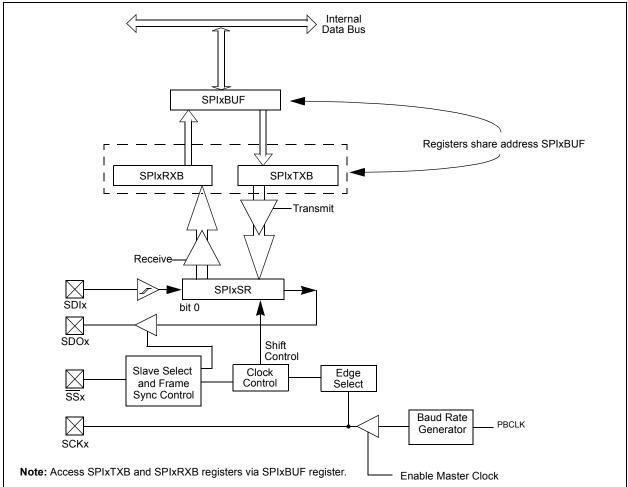

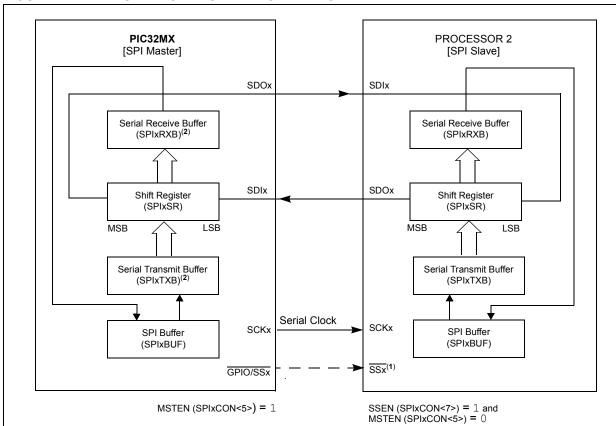

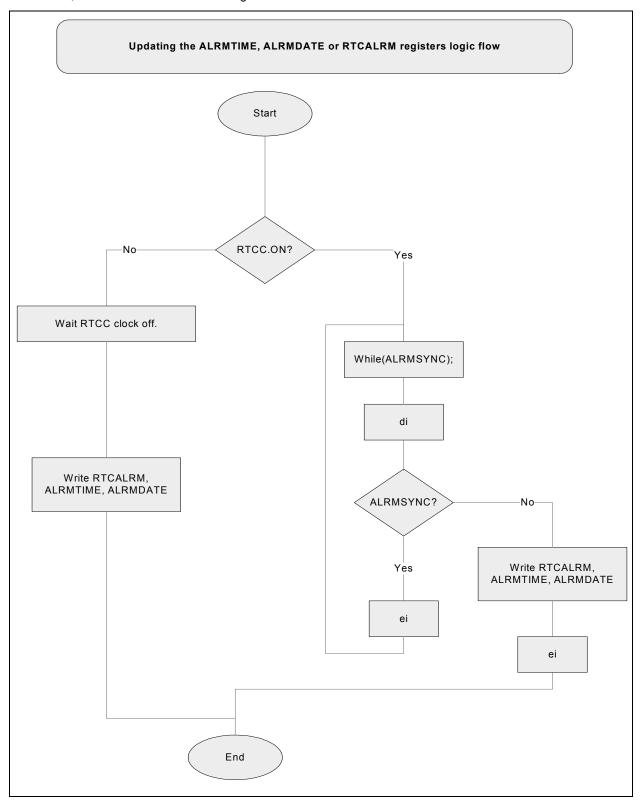

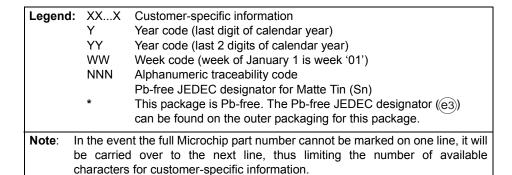

TABLE 2-3: PIC32MX CORE EXCEPTION TYPES