#### **INTEGRATED CIRCUITS**

# DATA SHEET

### **TZA1038HW**

High speed advanced analog DVD signal processor and laser supply

Product specification

2003 Sep 03

# High speed advanced analog DVD signal processor and laser supply

#### **TZA1038HW**

| CONTEN       | TS                                                                   | 7.4                        | Internal digital control, serial bus and external digital input signal relationships |

|--------------|----------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------|

| 1            | FEATURES                                                             | 7.4.1                      | STANDBY mode                                                                         |

| 2            | GENERAL DESCRIPTION                                                  | 7.4.2                      | RF only mode                                                                         |

| 3            | ORDERING INFORMATION                                                 | 7.5                        | Signal descriptions                                                                  |

|              |                                                                      | 7.5.1                      | Data path signals through pins A to D                                                |

| 4            | QUICK REFERENCE DATA                                                 | 7.5.2                      | Data signal path through input pins RFSUMP                                           |

| 5            | BLOCK DIAGRAM                                                        |                            | and RFSUMN                                                                           |

| 6            | PINNING                                                              | 7.5.3                      | HF filtering                                                                         |

| 7            | FUNCTIONAL DESCRIPTION                                               | 7.5.4                      | Focus signals                                                                        |

|              |                                                                      | 7.5.5                      | Radial signals                                                                       |

| 7.1          | RF data processing                                                   | 7.5.5.1                    | DPD signals (DVD-ROM mode) with no                                                   |

| 7.2<br>7.2.1 | Servo signal processing<br>Servo signal path set-up                  | 7550                       | drop-out concealment                                                                 |

| 7.2.1        | Focus servo                                                          | 7.5.5.2                    | DPD signals (DVD-ROM mode) with                                                      |

| 7.2.2        | Radial servo                                                         | 7550                       | drop-out concealment                                                                 |

| 7.2.4        | Differential phase detection                                         | 7.5.5.3<br>7.5.5.4         | Three-beam push-pull (CD mode) Enhanced push-pull                                    |

| 7.2.4.1      | Drop-out concealment                                                 |                            |                                                                                      |

| 7.2.4.2      | Push-pull and three-beam push-pull                                   | 8                          | LIMITING VALUES                                                                      |

| 7.2.4.3      | Enhanced push-pull (dynamic offset                                   | 9                          | THERMAL CHARACTERISTICS                                                              |

|              | compensation for beam landing)                                       | 10                         | CHARACTERISTICS                                                                      |

| 7.2.4.4      | Offset compensation                                                  | 11                         | APPLICATION INFORMATION                                                              |

| 7.2.5        | Automatic dual laser supply                                          |                            |                                                                                      |

| 7.2.6        | Power-on reset and general power on                                  | 11.1                       | Signal relationships                                                                 |

| 7.2.7        | Compatibility with TZA1033HL/V1                                      | 11.1.1                     | Data path                                                                            |

| 7.2.7.1      | Software compatibility                                               | 11.1.2                     | Servo path                                                                           |

| 7.2.7.2      | Hardware compatibility                                               | 11.2                       | Programming examples                                                                 |

| 7.2.8        | Interface to the system controller                                   | 11.3<br>11.4               | Energy saving                                                                        |

| 7.3          | Control registers                                                    | 11. <del>4</del><br>11.4.1 | Initial DC and gain setting strategy Electrical offset from pick-up                  |

| 7.3.1        | Register 0: power control                                            | 11.4.1                     | Gain setting servo                                                                   |

| 7.3.2        | Register 1: servo and RF modes                                       | 11.4.2                     | DC level in RF path                                                                  |

| 7.3.3        | Register 2: focus offset DAC                                         | 11.4.4                     | Gain setting RF path                                                                 |

| 7.3.4        | Register 3: RF path gain                                             |                            | * *                                                                                  |

| 7.3.5        | Register 4: RF left and right, or sum offset                         | 12                         | PACKAGE OUTLINE                                                                      |

| 700          | compensation                                                         | 13                         | SOLDERING                                                                            |

| 7.3.6        | Register 5: RF sum offset compensation                               | 13.1                       | Introduction to soldering surface mount                                              |

| 7.3.7        | Register 6: servo gain and dynamic radial offset compensation factor |                            | packages                                                                             |

| 7.3.8        | Register 7: servo path gain and bandwidth and                        | 13.2                       | Reflow soldering                                                                     |

| 7.5.0        | RF path bandwidth and pre-emphasis                                   | 13.3                       | Wave soldering                                                                       |

| 7.3.9        | Register 8: RF channel selection                                     | 13.4                       | Manual soldering                                                                     |

| 7.3.10       | Register 11: radial servo offset cancellation                        | 13.5                       | Suitability of surface mount IC packages for                                         |

| 7.3.11       | Register 12: central servo offset cancellation                       |                            | wave and reflow soldering methods                                                    |

|              | inputs A and B                                                       | 14                         | DATA SHEET STATUS                                                                    |

| 7.3.12       | Register 13: central servo offset cancellation                       | 15                         | DEFINITIONS                                                                          |

|              | inputs C and D                                                       | 16                         | DISCLAIMERS                                                                          |

| 7.3.13       | Register 14: RF filter settings                                      | 10                         | DIGGLATIVIENG                                                                        |

| 7.3.14       | Register 15: DPD filter settings                                     |                            |                                                                                      |

### High speed advanced analog DVD signal processor and laser supply

**TZA1038HW**

#### 1 FEATURES

- Operates with DVD-ROM, DVD+RW, DVD-RW, CD-ROM and CD-RW

- Operates up to  $64 \times \text{CD-ROM}$  and  $12 \times \text{DVD-ROM}$

- RF data amplifier with wide, fine pitch programmable noise filter and equalizer equivalent to 64 × CD or 12 × DVD

- Programmable RF gain for DVD-ROM, CD-RW and CD-ROM applications (approximately 50 dB range to cover a large range of disc-reflectivity and OPUs)

- Additional RF sum input

- · Balanced RF data signal transfer

- Universal photodiode IC interface using internal conversion resistors and offset cancellation

- · Input buffers and amplifiers with low-pass filtering

- · Three different tracking servo strategies:

- Conventional three-beam tracking for CD

- Differential Phase Detection (DPD) for DVD-ROM, including option to emulate traditional drop-out detection: Drop-Out Concealment (DOC)

- Advanced push-pull with dynamic offset compensation.

- Enhanced signal conditioning in DPD circuit for optimal tracking performance under noisy conditions

- Radial error signal for Fast Track Counting (FTC)

- RF only mode: servo outputs can be set to 3-state, while RF data path remains active

- · Radial servo polarity switch

- · Flexible adaption to different light pen configurations

- Two fully automatic laser controls for red and infrared lasers, including stabilization and an on/off switch

- Automatic selection of monitor diode polarity

- · Digital interface with 3 and 5 V compatibility.

#### 2 GENERAL DESCRIPTION

The TZA1038HW is an analog preprocessor and laser supply circuit for DVD and CD read-only players. The device contains data amplifiers, several options for radial tracking and focus control. The preamplifier forms a versatile, programmable interface between single light path voltage output CD or DVD mechanisms to Philips digital signal processor family for CD and DVD (for example, Gecko, HDR65 or Iguana). A separate high-speed RFSUM input is available.

The device contains several options for radial tracking:

- · Conventional three-beam tracking for CD

- · Differential phase detector for DVD

- Push-pull with flexible left and right weighting to compensate dynamic offsets e.g. beam landing offset

- A radial error signal to allow Fast Track Count (FTC) during track jumps.

The dynamic range of this preamplifier and processor combination can be optimized for LF servo and RF data paths. The gain in both channels can be programmed separately and so guarantees optimal playability for all disc types.

The RF path is fully DC coupled. The DC content compensation techniques provide fast settling after disc errors.

The device can accommodate astigmatic, single foucault and double foucault detectors and can be used with P-type lasers with N-sub or P-sub monitor diodes. After an initial adjustment, the circuit will maintain control over the laser diode current. With an on-chip reference voltage generator, a constant stabilized output power is ensured and is independent of ageing.

An internal Power-on reset circuit ensures a safe start-up condition.

2003 Sep 03

3

# High speed advanced analog DVD signal processor and laser supply

TZA1038HW

#### 3 ORDERING INFORMATION

| TYPE NUMBER                  |         | PACKAGE                                                                                                   |          |  |  |  |  |

|------------------------------|---------|-----------------------------------------------------------------------------------------------------------|----------|--|--|--|--|

| TYPE NUMBER NAME DESCRIPTION |         | DESCRIPTION                                                                                               | VERSION  |  |  |  |  |

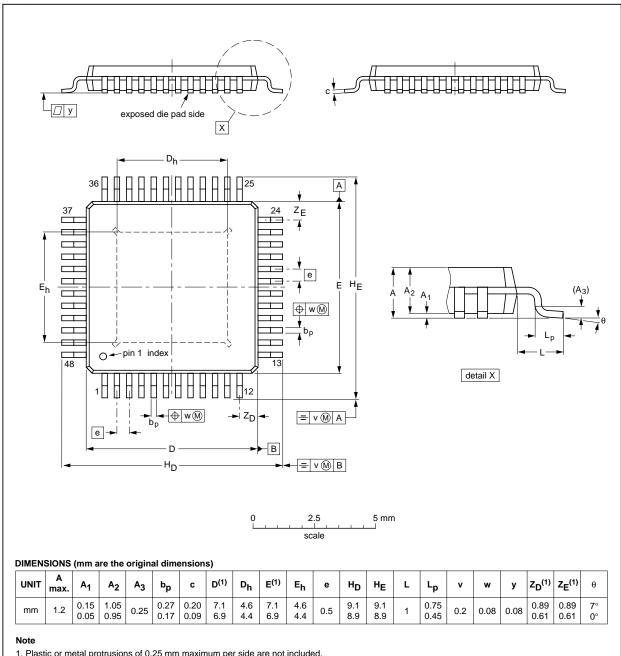

| TZA1038HW                    | HTQFP48 | plastic thermal enhanced thin quad flat package; 48 leads; body $7 \times 7 \times 1$ mm; exposed die pad | SOT545-2 |  |  |  |  |

#### 4 QUICK REFERENCE DATA

| SYMBOL                                                                           | PARAMETER                                  | CONDITIONS                                             | MIN.           | TYP. | MAX. | UNIT |

|----------------------------------------------------------------------------------|--------------------------------------------|--------------------------------------------------------|----------------|------|------|------|

| T <sub>amb</sub>                                                                 | ambient temperature                        |                                                        | -40            | _    | +85  | °C   |

| Supplies                                                                         | •                                          | •                                                      |                | •    | •    |      |

| V <sub>DDA1</sub> , V <sub>DDA2</sub> ,<br>V <sub>DDA3</sub> , V <sub>DDA4</sub> | analog supply voltage                      |                                                        | 4.5            | 5.0  | 5.5  | V    |

| V <sub>DDD3</sub>                                                                | 3 V digital supply voltage                 |                                                        | 2.7            | 3.3  | 5.5  | V    |

| V <sub>DDD5</sub>                                                                | 5 V digital supply voltage                 |                                                        | 4.5            | 5.0  | 5.5  | V    |

| I <sub>DD</sub>                                                                  | supply current                             | without laser supply                                   | _              | 98   | 120  | mA   |

|                                                                                  |                                            | STANDBY mode                                           | _              | _    | 1    | mA   |

| V <sub>I(logic)</sub>                                                            | logic input compatibility                  | note 1                                                 | 2.7            | 3.3  | 5.5  | V    |

| Servo signal p                                                                   | rocessing                                  |                                                        |                |      |      |      |

| B <sub>LF(-3dB)</sub>                                                            | -3 dB bandwidth of LF path                 |                                                        | 60             | 75   | 100  | kHz  |

| I <sub>O(LF)</sub>                                                               | output current                             | focus servo output                                     | 0              | _    | 12   | μΑ   |

|                                                                                  |                                            | radial servo output                                    | 0              | _    | 12   | μΑ   |

| V <sub>O(FTC)(p-p)</sub>                                                         | FTC output voltage (peak-to-peak value)    |                                                        | 2.0            | -    | _    | V    |

| B <sub>FTC</sub>                                                                 | FTC bandwidth                              | FTCHBW = 0                                             | _              | 600  | _    | kHz  |

|                                                                                  |                                            | FTCHBW = 1; note 2                                     | _              | 1200 | _    | kHz  |

| V <sub>I(FTCREF)</sub>                                                           | FTC reference input voltage                |                                                        | 1.25           | -    | 2.75 | V    |

| RF data proces                                                                   | ssing                                      |                                                        |                | •    |      | •    |

| A <sub>RF</sub>                                                                  | linear current gain                        | programmable gain RF channels                          | 6              | _    | 49   | dB   |

|                                                                                  |                                            | RFSUM channels                                         | <del>-</del> 6 |      | +31  | dB   |

| B <sub>RF(-3dB)</sub>                                                            | -3 dB bandwidth of RFP and RFN signal path | RFEQEN = 0;<br>RFNFEN = 0                              | 200            | 300  | -    | MHz  |

| f <sub>0(RF)</sub>                                                               | noise filter and equalizer                 | BWRF = 0                                               | 8              | 12.0 | 14.5 | MHz  |

| - (· ·· /                                                                        | corner frequency                           | BWRF = 127                                             | 100            | 145  | 182  | MHz  |

| t <sub>d(RF)</sub>                                                               | flatness delay in RF data path             | equalizer on; flat from<br>0 to 100 MHz;<br>BWRF = 127 | -              | _    | 0.5  | ns   |

| Z <sub>i</sub>                                                                   | input impedance of pins A to D             |                                                        | 100            | _    | _    | kΩ   |

# High speed advanced analog DVD signal processor and laser supply

TZA1038HW

| SYMBOL                     | PARAMETER                                                                  | CONDITIONS                      | MIN. | TYP.                      | MAX.                   | UNIT |

|----------------------------|----------------------------------------------------------------------------|---------------------------------|------|---------------------------|------------------------|------|

| V <sub>i(RF)(FS)</sub>     | input voltage on                                                           | at the appropriate signal       |      |                           |                        |      |

|                            | pins A to D for full-scale at                                              | path gain setting               |      |                           |                        |      |

|                            | output                                                                     | RF signal path                  | -    | _                         | 600                    | mV   |

|                            |                                                                            | LF signal path                  | _    | _                         | 700                    | mV   |

| $V_{i(SUM)(dif)}$          | differential input voltage on pins RFSUMP and RFSUMN                       | G <sub>RFSUM</sub> = -6 dB      | _    | _                         | 1800                   | mV   |

| V <sub>I(DC)</sub>         | DC input voltage range on pins RFSUMP and RFSUMN                           | with respect to V <sub>SS</sub> | 1.3  | _                         | V <sub>DDA</sub> – 1.0 | V    |

| $V_{o(RF)(dif)(p-p)}$      | differential output voltage<br>on pins RFP and RFN<br>(peak-to-peak value) |                                 | _    | _                         | 1.4                    | V    |

| $V_{O(RF)(DC)}$            | DC output voltage on pins RFP and RFN                                      |                                 | 0.35 | _                         | V <sub>DDA</sub> – 1.9 | V    |

| V <sub>i(RFREF)(CM)</sub>  | input reference voltage on<br>pin RFREF for common<br>mode output          |                                 | 0.8  | 1.2                       | 2.1                    | V    |

| Laser supply               |                                                                            |                                 |      |                           |                        |      |

| I <sub>o(laser)(max)</sub> | maximum current output to laser                                            |                                 | -120 | _                         | -                      | mA   |

| V <sub>i(mon)</sub>        | input voltage from laser                                                   | P-type monitor diode            |      |                           |                        |      |

| ,                          | monitor diode                                                              | LOW level voltage               | _    | V <sub>DDA4</sub> – 0.155 | _                      | V    |

|                            |                                                                            | HIGH level voltage              | _    | V <sub>DDA4</sub> – 0.190 | _                      | V    |

|                            |                                                                            | N-type monitor diode            |      |                           |                        |      |

|                            |                                                                            | LOW level voltage               | _    | 0.155                     | _                      | V    |

|                            |                                                                            | HIGH level voltage              | _    | 0.185                     | _                      | V    |

#### Notes

1. Input logic voltage level follows the supply voltage applied at pin  $V_{\mbox{\scriptsize DDD3}}$ .

2. High FTC bandwidth is achieved when  $I_{S1}$  and  $I_{S2}$  > 1.5  $\mu A.$

## High speed advanced analog DVD signal processor and laser supply

**TZA1038HW**

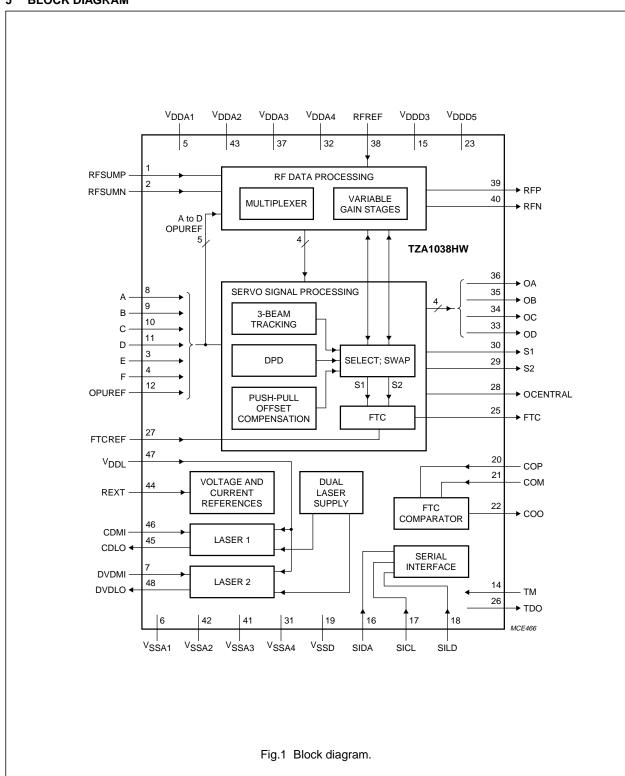

#### 5 BLOCK DIAGRAM

6

2003 Sep 03

# High speed advanced analog DVD signal processor and laser supply

TZA1038HW

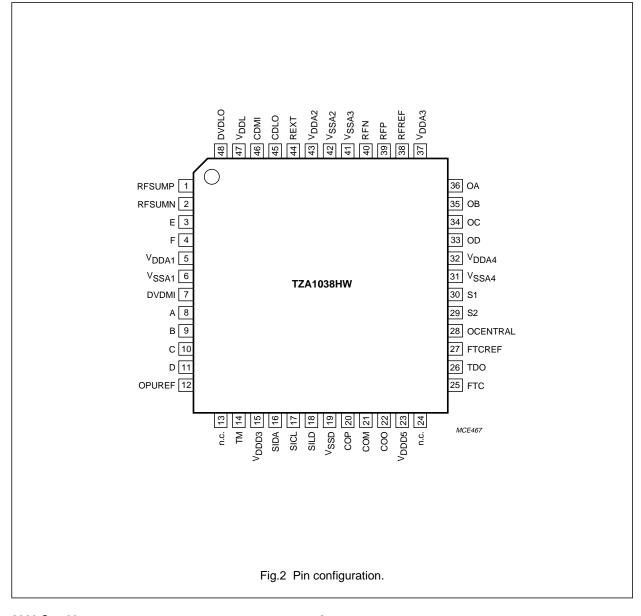

#### 6 PINNING

| SYMBOL            | PIN | DESCRIPTION                                                               |

|-------------------|-----|---------------------------------------------------------------------------|

| RFSUMP            | 1   | positive RF sum input                                                     |

| RFSUMN            | 2   | negative RF sum input                                                     |

| Е                 | 3   | input E                                                                   |

| F                 | 4   | input F                                                                   |

| $V_{DDA1}$        | 5   | analog supply voltage 1 (RF input stage)                                  |

| V <sub>SSA1</sub> | 6   | analog ground 1                                                           |

| DVDMI             | 7   | input signal from DVD laser monitor diode                                 |

| Α                 | 8   | input A                                                                   |

| В                 | 9   | input B                                                                   |

| С                 | 10  | input C                                                                   |

| D                 | 11  | input D                                                                   |

| OPUREF            | 12  | reference input from Optical Pick-Up (OPU)                                |

| n.c.              | 13  | not connected                                                             |

| TM                | 14  | test mode input (factory test only)                                       |

| $V_{DDD3}$        | 15  | digital supply voltage (serial interface 3 V I/O pads and FTC comparator) |

| SIDA              | 16  | serial host interface data input                                          |

| SICL              | 17  | serial host interface clock input                                         |

| SILD              | 18  | serial host interface load                                                |

| V <sub>SSD</sub>  | 19  | digital ground                                                            |

| COP               | 20  | positive FTC comparator input                                             |

| COM               | 21  | inverting FTC comparator input                                            |

| COO               | 22  | FTC comparator output                                                     |

| $V_{DDD5}$        | 23  | digital supply voltage (5 V digital core)                                 |

| n.c.              | 24  | not connected                                                             |

| FTC               | 25  | fast track count output                                                   |

| TDO               | 26  | test data output (factory test only)                                      |

| FTCREF            | 27  | FTC reference input                                                       |

| OCENTRAL          | 28  | test pin for offset cancellation                                          |

| S2                | 29  | servo current output 2 for radial tracking                                |

| S1                | 30  | servo current output 1 for radial tracking                                |

| V <sub>SSA4</sub> | 31  | analog ground 4                                                           |

| $V_{DDA4}$        | 32  | analog supply voltage 4 (servo signal processing)                         |

| OD                | 33  | servo current output for focus D                                          |

| OC                | 34  | servo current output for focus C                                          |

| ОВ                | 35  | servo current output for focus B                                          |

| OA                | 36  | servo current output for focus A                                          |

| $V_{DDA3}$        | 37  | analog supply voltage 3 (RF output stage)                                 |

| RFREF             | 38  | DC reference input for RF channel common mode output voltage              |

| RFP               | 39  | positive RF output                                                        |

| RFN               | 40  | negative RF output                                                        |

2003 Sep 03

## High speed advanced analog DVD signal processor and laser supply

#### TZA1038HW

| SYMBOL            | PIN | DESCRIPTION                                                         |  |  |  |

|-------------------|-----|---------------------------------------------------------------------|--|--|--|

| V <sub>SSA3</sub> | 41  | analog ground 3                                                     |  |  |  |

| V <sub>SSA2</sub> | 42  | analog ground 2                                                     |  |  |  |

| V <sub>DDA2</sub> | 43  | analog supply voltage 2 (internal RF data processing)               |  |  |  |

| REXT              | 44  | reference current input (connect via 12.1 kΩ to V <sub>SSA4</sub> ) |  |  |  |

| CDLO              | 45  | CD laser output                                                     |  |  |  |

| CDMI              | 46  | input signal from CD laser monitor diode                            |  |  |  |

| V <sub>DDL</sub>  | 47  | laser supply voltage                                                |  |  |  |

| DVDLO             | 48  | DVD laser output                                                    |  |  |  |

### High speed advanced analog DVD signal processor and laser supply

TZA1038HW

#### 7 FUNCTIONAL DESCRIPTION

#### 7.1 RF data processing

The RF data path is a fully DC-coupled, multi-stage amplifier (see Fig.3). The input signal for data can be selected from RF inputs A to D or from the summed RF inputs RFSUMP and RFSUMN. Switching between the two sets of signals is performed by an internal multiplexer. The signals are fully balanced internally to improve signal quality and reduce power supply interference.

RF outputs RFP and RFN can be DC coupled to the Analog-to-Digital Converter (ADC) of the decoder.

The RF input signals are from photodiodes and have a large DC content by nature. This DC component must be removed from the signals for good system performance. Built-in DACs, located after the input stages G<sub>1</sub> and RFSUM, have the ability to do this. The DAC range and resolution is scaled with the gain setting of the first amplifier stage. When the DC content is removed, the RF signal can be DC coupled to the decoder. The main advantage of DC coupling is fast recovery from signal swings due to disc defects since there is no AC coupling capacitance to slow the recovery. When using DC coupling, both AC and DC content in the data signal is known. The Philips Iguana decoders have on-chip control loops to support Automatic Gain Control (AGC) and DC cancellation.

Two separate DACs are available for cases where the left and right side DC conditions can be different.

When it is not possible to have a DC connection between the TZA1038HW and the decoder, the signals on servo outputs OA to OD can be used as they contain the same LP-filtered and DC coupled information.

Summing of the photodiode signals A to D is performed in the second amplifier stage  $G_2$ . Each individual diode channel can be switched on, off or inverted with switches SW-A to SW-D.

Switching between photodiode signals and RFSUM input is performed immediately before the third amplifier stage G<sub>3</sub>. This stage has a variable gain with fine resolution to allow automatic gain adjustment to be controlled by the decoder.

The filter stage limits the bandwidth according to the maximum playback speed of the disc. This is to optimize the noise performance. The filter stage consists of an equalizer and a noise filter, both of which can be bypassed, also the boost factor of the equalizer can be set. The corner frequencies of the equalizer and noise filter are equal and can be programmed to a 7-bit resolution.

The RF output signals RFP and RFN can be DC coupled to a decoder with a differential input pair (as with Philips Iguana decoders). The common mode output voltage can be set externally at pin RFREF.

The signals for differential phase detection are tapped from the inputs A to D at the RF amplifier  $G_1$  stages. DC cancellation for the A to D and RFSUM signal paths can be set independently or simultaneously.

Product specification

Downloaded from **Elcodis.com** electronic components distributor

### High speed advanced analog DVD signal processor and laser supply

**TZA1038HW**

#### 7.2 Servo signal processing

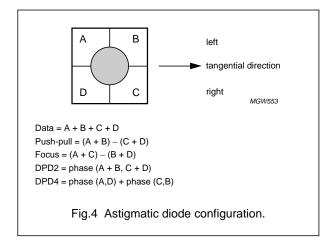

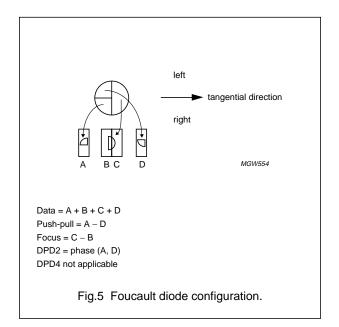

The photodiode configurations and naming conventions are shown in Figs 4 and 5.

#### 7.2.1 SERVO SIGNAL PATH SET-UP

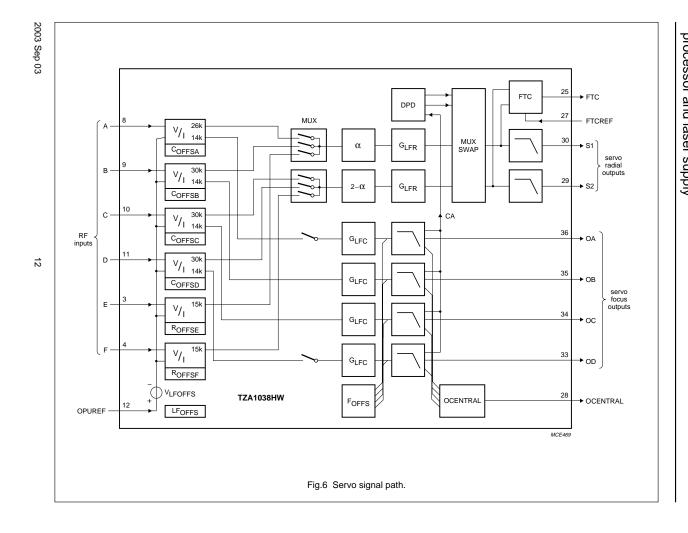

A block diagram of the servo signal path is shown in Fig.6. In general, the servo signal path comprises:

- A voltage-to-current converter with programmable offset voltage source V<sub>LFOFFS</sub> that is common to all inputs

- A 4-bit DAC for each of the six channels to compensate for offset per channel

- A variable gain stage to adapt the signal level to the specific pick-up and disc properties

- Low-pass filtering and output stage for the photodiode current signals

- Error output stage in the radial data path for fast track counting.

Servo output signals OA to OD, S1 and S2 are unipolar current signals which represent the low-pass filtered photodiode signals. In DPD radial tracking, the S1 and S2 signals are the equivalent of the satellite signals commonly found in traditional CD systems.

The servo output signals OA to OD, S1 and S2 are set to 3-state if bit RFonly = 1 (register 13, bit 11).

#### 7.2.2 FOCUS SERVO

Focus information is reflected in the four outputs OA to OD. Gain and offset can be programmed.

For optical pick-ups where only channels B and C are used for focus, channels A and D can be switched off (bit Focus\_mode = 0).

For initial alignment, a copy of the output currents can be made available on pin OCENTRAL.

#### 7.2.3 RADIAL SERVO

Radial information can be obtained from the two output signals S1 and S2, and the gain and offset can be programmed. The TZA1038HW provides differential phase detection, push-pull and three-beam push-pull for radial tracking. The signal FTC is made available for fast track counting and is primarily the voltage error signal derived from signals S1 or S2.

The polarity of the radial loop can be reversed via the serial control bus (RAD\_pol).

Philips Semiconductors

Product specification

### High speed advanced analog DVD signal processor and laser supply

TZA1038HW

#### 7.2.4 DIFFERENTIAL PHASE DETECTION

The TZA1038HW provides differential phase detection to support DVD in various ways:

- DPD2 with four channels programmed to be active gives DPD as required in the standard specification

- Two of the four channels can be excluded from the DPD for pick-ups with an alternative photodiode arrangement

- An increase in performance, dedicated for DVD+RW, can be obtained by using the DPD4 method. Then two truly separated phase detectors are active. After the phase detection of the two input pairs the result is summed.

Input signals for DPD are taken from input pins A to D after the first gain stage  $G_1$  (see Fig.3). Pre-emphasis is applied by means of a programmable lead/lag filter. Additionally, a programmable low-pass filter is available to improve the signal quality under noisy signal conditions at lower speeds. For further signal improvements the DPD pulse stretcher can be programmed to higher values at lower speeds.

The DPD signal is low-pass filtered by two internal capacitors. The signal is then fed to pins S1 and S2, or directed via the drop-out concealment circuit to the outputs (see Section 7.5).

#### 7.2.4.1 Drop-out concealment

A special function is built in for compatibility with drop-out detection strategies, based on level detection in the S1 and S2 signals. When using DPD in a fundamental way, there is no representation of mirror level information from the light pen.

When the drop-out concealment function is enabled (bit DOCEN = 1), a portion of the Central Aperture (CA) signal is added to S1 and S2. Also, when the CA signal drops below the DOC threshold, the DPD signal is gradually attenuated.

The DPD detection cannot work properly when the input signal becomes very small. The output of the DPD may then show a significant offset. The DOC may not conceal this offset completely because:

- DOC is gradually controlled from the CA signal

- The CA signal may not become 0 during disc-defect.

For details see Section 7.5.5.2

#### 7.2.4.2 Push-pull and three-beam push-pull

The TZA1038HW can also provide radial information by means of push-pull signals (from the photodiode inputs) or

in a three-spot optical system with Three-Beam Push-Pull (TBPP). The built-in multiplexer gives a flexible method of dealing with many detector arrangements. For push-pull, the input signals are taken from channels A to D. There is also a command that switches off channels B and C, leaving channels A and D for push-pull (bits RT\_mode[2:0]).

For TBPP, the input signal is taken from channels E and F, irrespective of bit RFSUM setting.

### 7.2.4.3 Enhanced push-pull (dynamic offset compensation for beam landing)

This option cancels offsets due to beam landing. A factor  $\alpha$  can be programmed to re-balance the signal gain between channels S1 and S2. In a simplified form this can be described as:

S1 =  $A_{LFR} \times \alpha \times \text{input left}$ S2 =  $A_{LFR} \times (2 - \alpha) \times \text{input right.}$

Factor  $\alpha$  can be programmed in a range from 0.6 to 1.35, with 1.0 as the balanced condition (bits  $\alpha[3:0]$ ).

#### 7.2.4.4 Offset compensation

A provision is made to compensate electrical offset from a light pen. The offset voltage from the light pen can be positive or negative. In general, the offset between any two channels is smaller than the absolute offsets. As negative input signals cannot be handled by the TZA1038HW internal servo channels, a two-step approach is adopted:

- A coarse DAC, common to all the input channels, adds an offset that shifts the input signals in positive direction until all inputs are ≥0. The DAC used (LF<sub>OFFS</sub>) has a 2-bit resolution (bits LF<sub>OFF</sub>[1:0]).

- A fine setting per channel is provided to cancel the remainder of the offset between the channels. This is achieved by DACs subtracting the DC component from the signals and bringing the inputs to approximately zero offset (within ≈ 1 mV). The DACs (registers 11 to 13) have a 4-bit resolution.

The range of both DACs can be increased by a factor of three to compensate for higher offset values by means of control parameter bit SERVOOS.

With a switched-off laser, the result of the offset cancellation can be observed at each corresponding output pin, OA to OD, S1 and S2, or via a built-in multiplexer to pin OCENTRAL (central channels only). See registers 11 to 13 for DAC and multiplexer control.

### High speed advanced analog DVD signal processor and laser supply

TZA1038HW

#### 7.2.5 AUTOMATIC DUAL LASER SUPPLY

The TZA1038HW can control the output power of two lasers; it has an Automatic Laser Power Control (ALPC) that stabilizes the laser output power and compensates the effects of temperature and ageing of the laser.

ALPC automatically detects if there is a P-type or N-type monitor diode in use in either of the laser circuits. The regulation loop formed by the ALPC, the laser, the monitor diode and the associated adjustment resistor will settle at the monitor input voltage. The monitor input voltage can be programmed to HIGH ( $\approx$  180 mV) or LOW ( $\approx$  150 mV), according to frequently-used pre-adjustments of the light pen. This set point can be set independently for both ALPCs. Bandwidth limitation and smooth switch-on behaviour is realized using an internal capacitor.

A protection circuit is included to prevent laser damage due to dips in laser supply voltage  $V_{DDL}$ . If a supply voltage dip occurs, the output can saturate and restrict the required laser current. Without the protection circuit, the ALPC would try to maximize the output power with destructive results for the laser when the supply voltage recovers. The protection circuit monitors the supply voltage and shuts off the laser when the voltage drops below a safe value. The ALPC recovers automatically after the dip has passed.

Only one laser can be activated at the same time. An internal break-before-make circuit ensures safe start-up for the laser when a toggle situation between the two lasers is detected. When both lasers are programmed on, neither laser will be activated.

#### 7.2.6 POWER-ON RESET AND GENERAL POWER ON

When the supply voltage is switched on, bit PWRON is reset by the Power-On Reset (POR) signal. This concludes in a STANDBY mode at power up. POR is intended to prevent the lasers being damaged due to random settings. All other functions may be switched when power is on. The TZA1038HW becomes active when bit PWRON = 1.

#### 7.2.7 COMPATIBILITY WITH TZA1033HL/V1

#### 7.2.7.1 Software compatibility

The TZA1038HW is highly software compatible with the TZA1033HL/V1. Provided that some conditions are met, the software of the TZA1038HW can be used as a successor with just minor modifications. This compatibility is achieved with the implementation of the TZA1038HW mode control bit (bit K2\_Mode). When bit K2\_Mode = 0, the TZA1038HW will act as a TZA1033HL/V1. When bit K2\_Mode = 1, the TZA1038HW will act as a TZA1033HL/K2 and the new functions will be available (but require a software update).

Other conditions or restrictions are:

- Register bits of the TZA1038HW which were not defined are programmed to a logic 0. Registers 9, 10, 14 and 15 may be left undefined

- The G<sub>4</sub> stage high gain setting of the TZA1033HL/V1 is not available in the TZA1038HW; if this value was set to logic 0, there will be no difference

- When bit K2\_Mode = 0 the RF bandwidth will be fixed to the minimum value of 10 MHz (typical); bit K2\_Mode = 1 to select a higher bandwidth; the bandwidth is now lower than using a TZA1033HL/V1.

#### 7.2.7.2 Hardware compatibility

The package is changed from LQFP64 for the TZA1033HL to LQFP48 for the TZA1038HW.

The hardware differences are:

- Input pins STB, HEADER and LAND of the TZA1033HL are not present

- Input pins CD of TZA1033HL/V1 are not used; TZA1038HW has RFSUM inputs instead; the RFSUM inputs of TZA1038HW may be connected to ground when not used.

### High speed advanced analog DVD signal processor and laser supply

TZA1038HW

#### 7.2.8 INTERFACE TO THE SYSTEM CONTROLLER

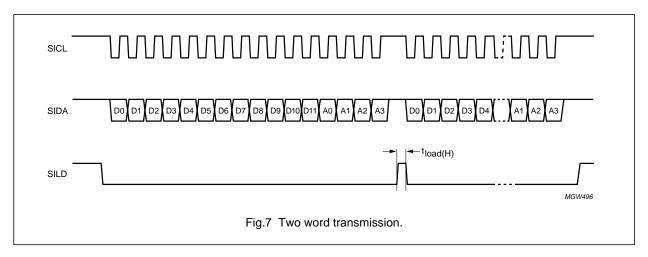

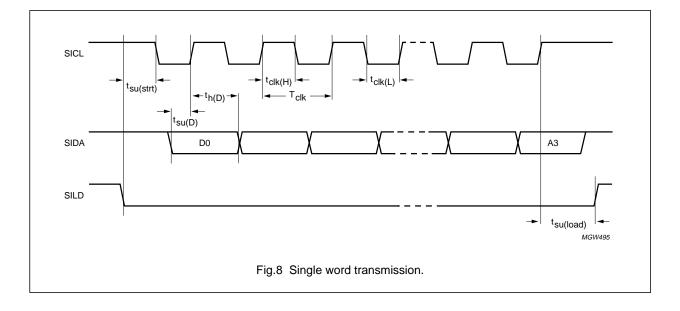

Programming the registers of TZA1038HW is done via a serial bus (see Fig.7). The circuitry is formed by a serial input shift register and a number of registers that store the data. The registers can always be programmed, irrespective of STANDBY mode.

If required, the bus lines can be connected in parallel with an I<sup>2</sup>C-bus. The protocol needs no switching of the data line during SICL = HIGH. This means that other I<sup>2</sup>C-bus devices will not recognise any START or STOP commands. Control words addressed to TZA1038HW

should go uniquely with the SILD signal. When SILD = HIGH, the TZA1038HW will not respond to any signal on SIDA or SICL.

During a transmission, the serial data is first stored in an input shift register. At the rising edge of SILD, the content of the input register is copied into the addressed register. This is also the moment the programmed information becomes effective.

The input pins have CMOS compatible threshold levels for both 3.3 and 5 V supplies.

#### 7.3 Control registers

The TZA1038HW is controlled by serial registers. To keep programming fast and efficient, the control bits are sent in 16-bit words. Four bits of the word are used for the address and for each address there are 12 data bits.

Table 1 Overview of control parameters

| SYMBOL                           | PARAMETER                                                   | VALUES                                              | REGISTER | BITS      |

|----------------------------------|-------------------------------------------------------------|-----------------------------------------------------|----------|-----------|

| Data path                        |                                                             |                                                     |          |           |

| G <sub>1</sub> (A <sub>1</sub> ) | gain of first RF amplifier stage (or linear amplification)  | 0, 6 and 12 dB (1×, 2× and 4×)                      | 3        | 11 and 10 |

| G <sub>2</sub> (A <sub>2</sub> ) | gain of second RF amplifier stage (or linear amplification) | 6, 12, 18 and 24 dB (2×, 4×, 8× and 16×)            | 3        | 9 and 8   |

| G <sub>3</sub> (A <sub>3</sub> ) | gain of third RF amplifier stage (or linear amplification)  | 0 to 13 dB in steps of 0.8 dB (1× to 4×)            | 3        | 7 to 4    |

| GRFSUM<br>(A <sub>RFSUM</sub> )  | gain of RFSUM input stage (or linear amplification)         | -6, 0, 6, 12 and 18 dB<br>(0.5×, 1×, 2×, 4× and 8×) | 0        | 7 to 5    |

| BWRF                             | bandwidth limitation in RF path                             | f <sub>0(RF)</sub> = 12 to 145 MHz                  | 14       | 6 to 0    |

# High speed advanced analog DVD signal processor and laser supply

TZA1038HW

| SYMBOL                  | PARAMETER                                                               | VALUES                                                                        | REGISTER | BITS      |

|-------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------|-----------|

| RF <sub>OFFSL</sub>     | DC offset compensation in left                                          | RFSUM = 0; full range depends on                                              | 4        | 11 to 6   |

|                         | RF input path                                                           | G <sub>1</sub> setting:                                                       |          |           |

|                         |                                                                         | $G_1 = 0$ dB: 0 to 450 mV in 7.1 mV steps                                     |          |           |

|                         |                                                                         | $G_1 = 6 \text{ dB: } 0 \text{ to } 225 \text{ mV in } 3.6 \text{ mV steps}$  |          |           |

|                         |                                                                         | G <sub>1</sub> = 12 dB: 0 to 120 mV in 1.9 mV steps                           |          |           |

| RF <sub>OFFSR</sub>     | DC offset compensation in right RF input path                           | RFSUM = 0; full range depends on G <sub>1</sub> setting:                      | 4        | 5 to 0    |

|                         |                                                                         | $G_1 = 0$ dB: 0 to 450 mV in 7.1 mV steps                                     |          |           |

|                         |                                                                         | G <sub>1</sub> = 6 dB: 0 to 225 mV in 3.6 mV steps                            |          |           |

|                         |                                                                         | $G_1 = 12 \text{ dB: } 0 \text{ to } 120 \text{ mV in } 1.9 \text{ mV steps}$ |          |           |

| RF <sub>OFFSS</sub>     | DC offset compensation in RFSUM path                                    | RFSUM = 1; full range depends on GRFSUM setting:                              | 4 or 5   | 5 to 0    |

|                         |                                                                         | GRFSUM = -6 dB; 0 to 1700 mV                                                  |          |           |

|                         |                                                                         | GRFSUM = 0 dB; 0 to 850 mV                                                    |          |           |

|                         |                                                                         | GRFSUM = 6 dB; 0 to 425 mV                                                    |          |           |

|                         |                                                                         | GRFSUM = 12 dB; 0 to 210 mV                                                   |          |           |

|                         |                                                                         | GRFSUM = 18 dB; 0 to 105 mV                                                   |          |           |

| Servo radial pat        | th                                                                      | ,                                                                             |          |           |

| LF <sub>OFFS</sub>      | DC offset compensation for                                              | SERVOOS = 0:                                                                  | 11       | 11 and 10 |

| 0110                    | LF path (common for all servo                                           | V <sub>LFOFFS</sub> = 0, 5, 10 or 15 mV                                       |          |           |

|                         | inputs)                                                                 | SERVOOS = 1:                                                                  |          |           |

|                         |                                                                         | V <sub>LFOFFS</sub> = 0, 15, 30 or 45 mV                                      |          |           |

| R <sub>LFR</sub>        | CD satellite path input transresistance                                 | 15 kΩ fixed                                                                   | _        | _         |

| R <sub>LFPP</sub>       | DVD push-pull signal transresistance                                    | 30 kΩ fixed                                                                   | _        | _         |

| R <sub>OFFSE</sub>      | DC offset compensation for                                              | SERVOOS = 0: V <sub>ROFFSE</sub> = 0 to 20 mV                                 | 11       | 7 to 4    |

|                         | radial servo path (input E)                                             | SERVOOS = 1: V <sub>ROFFSE</sub> = 0 to 60 mV                                 |          |           |

| R <sub>OFFSF</sub>      | DC offset compensation for                                              | SERVOOS = 0: V <sub>ROFFSF</sub> = 0 to 20 mV                                 | 11       | 3 to 0    |

|                         | radial servo path (input F)                                             | SERVOOS = 1: V <sub>ROFFSF</sub> = 0 to 60 mV                                 |          |           |

| α                       | dynamic radial offset compensation factor                               | $\alpha$ = 0.6 to 1.35 in 15 steps of 0.05                                    | 6        | 3 to 0    |

| I <sub>(FS)(DPD),</sub> | full scale DPD current, fixed                                           | DOCEN = 0: fixed value = 20 μA                                                | 1        | 5         |

| I(FS)(DPD)(DOC)         | value based on bandgap<br>voltage across external<br>resistor           | DOCEN = 1: fixed value = 6.6 μA                                               |          |           |

| I <sub>REFRAD(CM)</sub> | internally generated common<br>mode DC reference current in<br>DPD mode | 3.5 μA fixed                                                                  | _        | _         |

| f <sub>start_DPD</sub>  | start frequency lead/lag filter of DPD block                            | f <sub>start_DPD</sub> = 1, 5 or 10 MHz<br>(TZA1033HL/V1 compatible)          | 7        | 1 and 0   |

|                         |                                                                         | f <sub>start_DPD</sub> = 1, 5, 10, 18 or 24 MHz                               | 15       | 5 to 3    |

# High speed advanced analog DVD signal processor and laser supply

TZA1038HW

| SYMBOL                               | PARAMETER                                                              | VALUES                                           | REGISTER | BITS    |

|--------------------------------------|------------------------------------------------------------------------|--------------------------------------------------|----------|---------|

| G <sub>LFR</sub> (A <sub>LFR</sub> ) | low frequency gain, radial path output stage (or linear amplification) | -15 to +9 dB in steps of 3 dB (0.18× to 2.8×)    | 6        | 11 to 8 |

| R <sub>FTC</sub>                     | gain of fast track count output                                        | 680 kΩ ±20% fixed for ±2 V (p-p)                 | _        | _       |

| Servo focus pa                       | th                                                                     |                                                  |          |         |

| R <sub>LFC</sub>                     | LF path input transresistance                                          | 14 kΩ fixed                                      | _        | _       |

| C <sub>OFFSA</sub>                   | DC offset compensation for                                             | SERVOOS = 0: 0 to 20 mV                          | 12       | 7 to 4  |

|                                      | central servo path A                                                   | SERVOOS = 1: 0 to 60 mV                          |          |         |

| C <sub>OFFSB</sub>                   | DC offset compensation for                                             | SERVOOS = 0: 0 to 20 mV                          | 12       | 3 to 0  |

|                                      | central servo path B                                                   | SERVOOS = 1: 0 to 60 mV                          |          |         |

| C <sub>OFFSC</sub>                   | DC offset compensation for                                             | SERVOOS = 0: 0 to 20 mV                          | 13       | 7 to 4  |

|                                      | central servo path C                                                   | SERVOOS = 1: 0 to 60 mV                          |          |         |

| C <sub>OFFSD</sub>                   | DC offset compensation for                                             | SERVOOS = 0: 0 to 20 mV                          | 13       | 3 to 0  |

|                                      | central servo path D                                                   | SERVOOS = 1: 0 to 60 mV                          |          |         |

| G <sub>LFC</sub> (A <sub>LFC</sub> ) | low frequency gain, central                                            | -15 to +9 dB in steps of 3 dB                    | 6        | 7 to 4  |

|                                      | path output stage (or linear amplification)                            | (0.18× to 2.8×)                                  |          |         |

| β                                    | focus offset compensation                                              | $\beta = 0 \text{ to } ^{31}/_{32}$              | 2        | 4 to 0  |

| F <sub>OFFSEN</sub>                  | full range offset compensation                                         | DAC enabled: I <sub>FOFFS</sub> = 400 nA (fixed) | 2        | 10      |

|                                      | for focus                                                              | DAC disabled: I <sub>FOFFS</sub> = 0 nA          |          |         |

#### 7.3.1 REGISTER 0: POWER CONTROL

#### Table 2 Register address 0H

| BIT    | 15  | 14  | 13  | 12  | 11 | 10 | 9 | 8 |

|--------|-----|-----|-----|-----|----|----|---|---|

| SYMBOL | AD3 | AD2 | AD1 | AD0 | ı  | _  | ı | _ |

| BIT    | 7           | 6           | 5           | 4          | 3        | 2         | 1       | 0     |

|--------|-------------|-------------|-------------|------------|----------|-----------|---------|-------|

| SYMBOL | GRF<br>SUM2 | GRF<br>SUM1 | GRF<br>SUM0 | DVD_ MILVL | CD_MILVL | DVD_ LDON | CD_LDON | PWRON |

#### Table 3 Description of register bits (address 0H)

| BIT      | SYMBOL      | FUNCTION                                         |

|----------|-------------|--------------------------------------------------|

| 15 to 12 | AD[3:0]     | 0000 = address 0H                                |

| 11 to 8  | -           | not used                                         |

| 7 to 5   | GRFSUM[2:0] | Gain of RFSUM input stage.                       |

|          |             | 000 = -6  dB                                     |

|          |             | 001 = 0 dB                                       |

|          |             | 010 = 6 dB                                       |

|          |             | 011 = 12 dB                                      |

|          |             | 100 = 18 dB                                      |

| 4        | DVD_MILVL   | DVD monitor input level. 0 = 150 mV; 1 = 180 mV. |

# High speed advanced analog DVD signal processor and laser supply

#### TZA1038HW

| BIT | SYMBOL   | FUNCTION                                          |

|-----|----------|---------------------------------------------------|

| 3   | CD_MILVL | CD monitor input level. 0 = 150 mV; 1 = 180 mV.   |

| 2   | DVD_LDON | <b>DVD laser on.</b> 0 = laser off; 1 = laser on. |

| 1   | CD_LDON  | CD laser on. 0 = laser off; 1 = laser on.         |

| 0   | PWRON    | Power on. 0 = STANDBY mode; 1 = power on.         |

#### 7.3.2 REGISTER 1: SERVO AND RF MODES

#### Table 4 Register address 1H

| BIT    | 15  | 14  | 13  | 12  | 11      | 10 | 9 | 8       |

|--------|-----|-----|-----|-----|---------|----|---|---------|

| SYMBOL | AD3 | AD2 | AD1 | AD0 | DPD_DCC | -  | - | RAD_pol |

| BIT    | 7 | 6 | 5     | 4              | 3        | 2        | 1        | 0     |

|--------|---|---|-------|----------------|----------|----------|----------|-------|

| SYMBOL | - | - | DOCEN | Focus_<br>mode | RT_mode2 | RT_mode1 | RT_mode0 | RFSUM |

#### Table 5 Description of register bits (address 1H)

| BIT      | SYMBOL       | FUNCTION                                                                                                                                                                  |

|----------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 to 12 | AD[3:0]      | 0001 = address 1H                                                                                                                                                         |

| 11       | DPD_DCC      | RF offset DAC for DPD signal control. 0 = DAC controlled by register 4, bits RF <sub>OFFSL</sub> [5:0]; 1 = DAC controlled by register 5, bits RF <sub>OFFSS</sub> [5:0]. |

| 10 and 9 | _            | not used                                                                                                                                                                  |

| 8        | RAD_pol      | Radial polarity switch. 0 = inverse; 1 = normal (default).                                                                                                                |

| 7 and 6  | _            | not used                                                                                                                                                                  |

| 5        | DOCEN        | <b>Drop-out concealment enable.</b> 0 = disable; 1 = enable.                                                                                                              |

| 4        | Focus_mode   | <b>Focus mode.</b> 0 = two-channel focus (channels B and C only); 1 = four-channel focus.                                                                                 |

| 3 to 1   | RT_mode[2:0] | Radial tracking mode.                                                                                                                                                     |

|          |              | 000 = DPD2; DPD = phase (A,D)                                                                                                                                             |

|          |              | 001 = push-pull; channels A,D only                                                                                                                                        |

|          |              | 100 = DPD2; DPD = phase (A + C, B + D)                                                                                                                                    |

|          |              | 101 = push-pull; four channels                                                                                                                                            |

|          |              | 110 = DPD4; DPD = phase (A,D) + phase (C,B)                                                                                                                               |

|          |              | X11 = TBPP channels E and F                                                                                                                                               |

| 0        | RFSUM        | RF channel selection. 0 = diode inputs selected; 1 = RFSUM input selected.                                                                                                |

# High speed advanced analog DVD signal processor and laser supply

TZA1038HW

#### 7.3.3 REGISTER 2: FOCUS OFFSET DAC

#### Table 6 Register address 2H

| BIT    | 15  | 14  | 13  | 12  | 11      | 10                  | 9  | 8  |

|--------|-----|-----|-----|-----|---------|---------------------|----|----|

| SYMBOL | AD3 | AD2 | AD1 | AD0 | K2_Mode | F <sub>OFFSEN</sub> | β4 | β3 |

|        |     |     |     |     |         |                     |    |    |

| BIT    | 7  | 6  | 5  | 4 | 3 | 2 | 1 | 0 |

|--------|----|----|----|---|---|---|---|---|

| SYMBOL | β2 | β1 | β0 | _ | _ | _ | _ | _ |

#### Table 7 Description of register bits (address 2H)

| BIT      | SYMBOL              | FUNCTION                                                                            |  |  |  |  |

|----------|---------------------|-------------------------------------------------------------------------------------|--|--|--|--|

| 15 to 12 | AD[3:0]             | 0010 = address 2H                                                                   |  |  |  |  |

| 11       | K2_Mode             | 2 mode. 0 = disable; 1 = enable.                                                    |  |  |  |  |

| 10       | F <sub>OFFSEN</sub> | ocus offset enable. 0 = enable; 1 = disable.                                        |  |  |  |  |

| 9 to 5   | β[4:0]              | Focus offset compensation. 00000 to 11111: $\beta = 0$ to $\beta = \frac{31}{32}$ . |  |  |  |  |

| 4 to 0   | _                   | not used                                                                            |  |  |  |  |

#### 7.3.4 REGISTER 3: RF PATH GAIN

#### Table 8 Register address 3H

| BIT    | 15  | 14  | 13  | 12  | 11               | 10               | 9                | 8                |

|--------|-----|-----|-----|-----|------------------|------------------|------------------|------------------|

| SYMBOL | AD3 | AD2 | AD1 | AD0 | G <sub>1</sub> 1 | G <sub>1</sub> 0 | G <sub>2</sub> 1 | G <sub>2</sub> 0 |

| BIT    | 7                | 6                | 5                | 4                | 3 | 2 | 1 | 0 |

|--------|------------------|------------------|------------------|------------------|---|---|---|---|

| SYMBOL | G <sub>3</sub> 3 | G <sub>3</sub> 2 | G <sub>3</sub> 1 | G <sub>3</sub> 0 | - | - | - | - |

#### Table 9 Description of register bits (address 3H)

| BIT       | SYMBOL               | FUNCTION                                                                 |

|-----------|----------------------|--------------------------------------------------------------------------|

| 15 to 12  | AD[3:0]              | 0011 = address 3H                                                        |

| 11 and 10 | G₁[1:0]              | First RF amplifier stage gain.                                           |

|           |                      | 00 = 0  dB                                                               |

|           |                      | 01 = 6  dB                                                               |

|           |                      | 10 = 12 dB                                                               |

|           |                      | 11 = not used                                                            |

| 9 and 8   | G <sub>2</sub> [1:0] | Second RF amplifier stage gain.                                          |

|           |                      | 00 = 6  dB                                                               |

|           |                      | 01 = 12  dB                                                              |

|           |                      | 10 = 18 dB                                                               |

|           |                      | 11 = 24 dB                                                               |

| 7 to 4    | G <sub>3</sub> [3:0] | Third RF amplifier stage gain. 0000 to 1111: 0 to 13 dB in 0.8 dB steps. |

| 3 to 0    | -                    | not used                                                                 |

# High speed advanced analog DVD signal processor and laser supply

TZA1038HW

#### 7.3.5 REGISTER 4: RF LEFT AND RIGHT, OR SUM OFFSET COMPENSATION

#### Table 10 Register address 4H

| BIT    | 15  | 14  | 13  | 12  | 11                    | 10                    | 9                     | 8                     |

|--------|-----|-----|-----|-----|-----------------------|-----------------------|-----------------------|-----------------------|

| SYMBOL | AD3 | AD2 | AD1 | AD0 | RF <sub>OFFSL</sub> 5 | RF <sub>OFFSL</sub> 4 | RF <sub>OFFSL</sub> 3 | RF <sub>OFFSL</sub> 2 |

| BIT    | 7                     | 6                     | 5                                               | 4                                               | 3                                               | 2                                               | 1                                               | 0                                               |

|--------|-----------------------|-----------------------|-------------------------------------------------|-------------------------------------------------|-------------------------------------------------|-------------------------------------------------|-------------------------------------------------|-------------------------------------------------|

| SYMBOL | RF <sub>OFFSL</sub> 1 | RF <sub>OFFSL</sub> 0 | RF <sub>OFFSR</sub> 5/<br>RF <sub>OFFSS</sub> 5 | RF <sub>OFFSR</sub> 4/<br>RF <sub>OFFSS</sub> 4 | RF <sub>OFFSR</sub> 3/<br>RF <sub>OFFSS</sub> 3 | RF <sub>OFFSR</sub> 2/<br>RF <sub>OFFSS</sub> 2 | RF <sub>OFFSR</sub> 1/<br>RF <sub>OFFSS</sub> 1 | RF <sub>OFFSR</sub> 0/<br>RF <sub>OFFSS</sub> 0 |

#### Table 11 Description of register bits (address 4H)

| BIT      | SYMBOL                    | FUNCTION                                                                                                                                                         |

|----------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 to 12 | AD[3:0]                   | 0100 = address 4H                                                                                                                                                |

| 11 to 6  | RF <sub>OFFSL</sub> [5:0] | Left channel RF offset compensation definition.                                                                                                                  |

|          |                           | bit RFSUM = 0: left RF channel offset compensation value                                                                                                         |

|          |                           | bit RFSUM = 1: not used                                                                                                                                          |

| 5 to 0   | RF <sub>OFFSR</sub> [5:0] | Right channel RF offset compensation definition.                                                                                                                 |

|          |                           | bit RFSUM = 0: right RF channel offset compensation value (symbol is RF <sub>OFFSR</sub> )                                                                       |

|          |                           | bit RFSUM = 1 and bit DPD_DCC = 1: not used                                                                                                                      |

|          |                           | bit RFSUM = 1 and bit DPD_DCC = 0: the decoder controls DPD and RFSUM channels automatically, in parallel and with same values (symbol is RF <sub>OFFSS</sub> ). |

#### 7.3.6 REGISTER 5: RF SUM OFFSET COMPENSATION

#### Table 12 Register address 5H

| BIT    | 15  | 14  | 13  | 12  | 11 | 10 | 9 | 8 |

|--------|-----|-----|-----|-----|----|----|---|---|

| SYMBOL | AD3 | AD2 | AD1 | AD0 | _  | _  | _ | _ |

| BIT    | 7 | 6 | 5                     | 4                     | 3                     | 2                     | 1                     | 0                     |

|--------|---|---|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| SYMBOL | _ | _ | RF <sub>OFFSS</sub> 5 | RF <sub>OFFSS</sub> 4 | RF <sub>OFFSS</sub> 3 | RF <sub>OFFSS</sub> 2 | RF <sub>OFFSS</sub> 1 | RF <sub>OFFSS</sub> 0 |

#### Table 13 Description of register bits (address 5H)

| BIT      | SYMBOL                    | FUNCTION                                                                                                                                   |  |  |  |

|----------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 15 to 12 | AD[3:0]                   | 0101 = address 5H                                                                                                                          |  |  |  |

| 11 to 6  | _                         | not used                                                                                                                                   |  |  |  |

| 5 to 0   | RF <sub>OFFSS</sub> [5:0] | RF offset compensation definition.                                                                                                         |  |  |  |

|          |                           | bit RFSUM = 0: not used                                                                                                                    |  |  |  |

|          |                           | bit RFSUM = 1 and bit DPD_DCC = 0: not used                                                                                                |  |  |  |

|          |                           | bit RFSUM = 1 and bit DPD_DCC = 1: the decoder controls RFSUM channels; the DPD channels can be set independently from the microprocessor. |  |  |  |

## High speed advanced analog DVD signal processor and laser supply

TZA1038HW

#### 7.3.7 REGISTER 6: SERVO GAIN AND DYNAMIC RADIAL OFFSET COMPENSATION FACTOR

#### Table 14 Register address 6H

| BIT    | 15  | 14  | 13  | 12  | 11                 | 10                 | 9                  | 8                  |

|--------|-----|-----|-----|-----|--------------------|--------------------|--------------------|--------------------|

| SYMBOL | AD3 | AD2 | AD1 | AD0 | G <sub>LFR</sub> 3 | G <sub>LFR</sub> 2 | G <sub>LFR</sub> 1 | G <sub>LFR</sub> 0 |

|        |     |     |     |     |                    |                    |                    |                    |

|        | _   | l _ | _   | _   | _                  | _                  | _                  | _                  |

| BIT    | 7                  | 6                  | 5                  | 4                  | 3  | 2  | 1  | 0  |

|--------|--------------------|--------------------|--------------------|--------------------|----|----|----|----|

| SYMBOL | G <sub>LFC</sub> 3 | G <sub>LFC</sub> 2 | G <sub>LFC</sub> 1 | G <sub>LFC</sub> 0 | α3 | α2 | α1 | α0 |

#### **Table 15** Description of register bits (address 6H)

| BIT      | SYMBOL                 | FUNCTION                                                                                                                     |

|----------|------------------------|------------------------------------------------------------------------------------------------------------------------------|

| 15 to 12 | AD[3:0]                | 0110 = address 6H                                                                                                            |

| 11 to 8  | G <sub>LFR</sub> [3:0] | Low frequency gain, radial path output stage. 0000 to 1000: -15 to +9 dB in 3 dB steps.                                      |

| 7 to 4   | G <sub>LFC</sub> [3:0] | Low frequency gain, central path output stage. 0000 to 1000: -15 to +9 dB in 3 dB steps.                                     |

| 3 to 0   | α[3:0]                 | <b>Dynamic radial offset compensation factor.</b> 0000 to 1111: 0.60 to 1.35 in 0.05 steps; 1000 = balanced value (default). |

#### 7.3.8 REGISTER 7: SERVO PATH GAIN AND BANDWIDTH AND RF PATH BANDWIDTH AND PRE-EMPHASIS

Definitions in register 7 are intended mainly for software compatibility with the TZA1033HL/V1. New features that require more bit-space to program are moved to registers 14 and 15. Only DPD stretch remains programmed in register 7. Some parameters are slightly modified.

#### Table 16 Register address 7H

| BIT    | 15  | 14  | 13  | 12  | 11      | 10      | 9                | 8                |

|--------|-----|-----|-----|-----|---------|---------|------------------|------------------|

| SYMBOL | AD3 | AD2 | AD1 | AD0 | DPDLPF1 | DPDLPF0 | DPD_<br>stretch2 | DPD_<br>stretch1 |

| BIT    | 7                | 6                | 5                | 4                  | 3                  | 2                  | 1                        | 0                        |

|--------|------------------|------------------|------------------|--------------------|--------------------|--------------------|--------------------------|--------------------------|

| SYMBOL | DPD_<br>stretch0 | DPD_<br>testmode | DVDALAS_<br>mode | EQ <sub>RF</sub> 2 | EQ <sub>RF</sub> 1 | EQ <sub>RF</sub> 0 | f <sub>start_DPD</sub> 1 | f <sub>start_DPD</sub> 0 |

#### Table 17 Description of register bits (address 7H)

| BIT       | SYMBOL      | FUNCTION                                                 |                   |  |  |  |  |

|-----------|-------------|----------------------------------------------------------|-------------------|--|--|--|--|

| ы         | STWIBOL     | K2_Mode = 0                                              | K2_Mode = 1       |  |  |  |  |

| 15 to 12  | AD[3:0]     | 0111 = address 7H                                        | 0111 = address 7H |  |  |  |  |

| 11 and 10 | DPDLPF[1:0] | DPD low-pass filter.                                     | not applicable    |  |  |  |  |

|           |             | $0X : B_{-3dB} = 50 \text{ MHz (equivalent to TZA1023)}$ |                   |  |  |  |  |

|           |             | 1X : B <sub>-3dB</sub> = 10 MHz                          |                   |  |  |  |  |

# High speed advanced analog DVD signal processor and laser supply

TZA1038HW

| DIT     | OVMDOL                       | FUNCTION                                                                                                                                                                                  |                                        |