# Tsi564A<sup>™</sup> Tsi564A Serial RapidIO Switch

## **Features**

# Serial RapidIO Interfaces

- Bandwidth of up to 40 Gbps

- Low latency with cut-through capability

- Individual port power down

- RapidIO Interconnect Specification (Revision 1.2) compliant

The Tsi564A enhances system scalability through device configuration and provides architects and designers with a solution for both throughput intensive and power sensitive applications.

- Port flexibility for multiple I/O bandwidth requirements:

- Up to four 4x mode ports or eight 1x mode ports

- Each 4x serial port can be configured as two 1x serial ports

- Integrated high-speed, full-duplex SerDes with 8b/10b encoding

- Advanced non-blocking internal switching fabric

- Specifically designed for line rate termination and prevention of head-of-line blocking

- Port SerDes frequency configuration to 1.25, 2.5, and 3.125 Gbits/s

- Look-up tables: Table-based packet routing

#### Other Device Capabilities

- I<sup>2</sup>C Interface: Supports configuration through register initialization

- Hot Swappable ports: Enables use in field replaceable blade applications

# **Device Overview**

The IDT Tsi564A is an industry leading Serial RapidIO switch supporting 40 Gbps aggregate bandwidth. The Tsi564A is part of a family of switches that enable customers to develop systems with robust features and high performance at low cost.

The Tsi564A provides designers and architects with maximum scalability to design the device into a wide range of applications. Flexible port configurations can be selected through multiple port width and frequency options.

Based on the Serial RapidIO Specification, the Tsi564A incorporates SerDes functionality, error recovery, priority-based fabric routing, high payload efficiency, and table-based fabric packet routing. In addition, the Tsi564A supports RapidFabric extensions including data streaming packet switching for interworking and encapsulation.

The device goes beyond standard specification requirements to solve system level issues by optimizing performance, lowering power consumption, and supporting hot swappable I/Os. The extensive buffering and traffic management architecture is specifically designed for line rate termination and the prevention of head-of-line blocking.

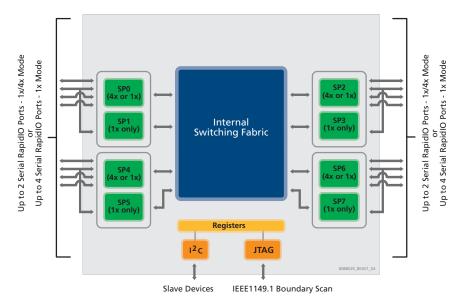

# **Block Diagram**

# **Benefits**

- Scalability: device variations of port width and frequencies

- Performance: low latency and high protocol efficiency

- Power: low power implementation of integrated SerDes functionality

- Time-to-market: leverages open-standard technology

#### **Specifications**

Technology: 0.13uVoltage: 1.2V, 3.3V

- Flexible power consumption

- Highly configuration dependent with SerDes voltage range, baud rate, and port width impacting power consumption

- Package: 399 ball, 21mm x 21mm, 1mm ball pitch FCBGA

## Target Markets

- Wireless Embedded Communications

- Node B, Radio Network Controller, Media Gateway

- Access Embedded Communications

- Multiservice WAN Switches, 1 to 10 Gbit Ethernet Switches, 1 to >10 Gbit Routers, DSLAMs

- Storage

- Storage Area Networks, Network Attached Storage, High-Performance Work Stations

- Video and Imaging

- Signal and image processing, and media processing applications

# **Typical Applications**

The Tsi564A can be used in many embedded communication applications. It provides chip-to-chip interconnect between I/O devices and can replace existing proprietary backplane fabrics for board-to-board interconnect which improves system cost and product time-to-market.

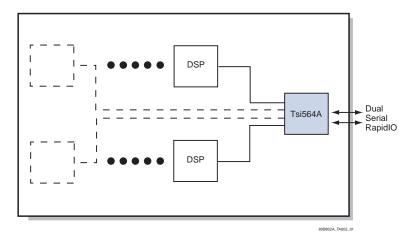

#### **Processor Farm Mezzanine**

The Tsi564A provides traffic aggregation through packet prioritization when it is used with RapidIO-enabled I/O devices. When it is in a system with multiple RapidIO-enabled processors it provides high performance peer-to-peer communication through its non-blocking switch fabric.

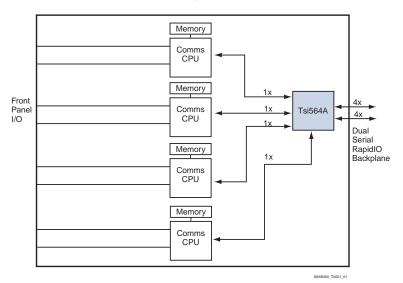

## **Distributed Processing Blade**

DISCLAIMER Integrated Device Technology, Inc. (IDT) and its subsidiaries reserve the right to modify the products and/or specifications described herein at any time and at IDT's sole discretion. All information in this document, including descriptions of product features and performance, is subject to change without notice. Performance specifications and the operating parameters of the described products are determined in the independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT or any third particular.

IDT's products are not intended for use in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using and IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are registered trademarks of IDT. Other trademarks and service marks used herein, including protected names, logos and designs, are the property of IDT or their respective third party owners.

CORPORATE HEADQUARTERS 6024 Silver Creek Valley Road San Jose, CA 95138

for SALES: 800-345-7015 or 408-284-8200 fax: 408-284-2775 www.idt.com for Tech Support: 408-360-1533 sRIO@idt.com Document: 80B802A\_FB001\_03