Preliminary

# 275V 40-Channel Row Driver with SCR Outputs

### **Ordering Information**

|        | Package Options             |                                     |        |  |  |

|--------|-----------------------------|-------------------------------------|--------|--|--|

| Device | 80-Lead<br>Ceramic Gullwing | 64-Lead 3-Sided<br>Plastic Gullwing | Die    |  |  |

| HV506  | HV506DG                     | HV506PG                             | HV506X |  |  |

## Features

- Processed with HVDI<sup>®</sup> technology

- Symmetric row drive

- Output voltage up to 275V

- □ Source/Sink current 300mA (min.)

- Shift Register Speed 3MHz

- □ Pin-programmable shift direction (DIR)

- □ Hi-Rel processing available

# **Absolute Maximum Ratings**

| Logic supply voltage, LV <sub>DD</sub> <sup>1</sup>         |                    | -0.5V to +15V                     |

|-------------------------------------------------------------|--------------------|-----------------------------------|

| Output supply voltage, V <sub>DD</sub> <sup>1</sup>         |                    | -0.5V to +15V                     |

| Substrate bias voltage, $V_{sub}$                           |                    | See Note 3                        |

| Output voltage, HV <sub>OUT</sub>                           |                    | ±300V                             |

| Logic input levels                                          | -0                 | .5V to V <sub>DD</sub> +0.5V      |

| Continuous total power dissipation <sup>2</sup>             | Ceramic<br>Plastic | 1900mW<br>1200mW                  |

| Operating temperature range                                 | Plastic<br>Ceramic | -40°C to +85°C<br>-55°C to +125°C |

| Storage temperature range                                   |                    | -65°C to +150°C                   |

| Lead temperature 1.6mm (1/16 inch) from case for 10 seconds | )                  | 260°C                             |

#### Notes:

1. All voltages are referenced to  $\rm V_{_{\rm SS}}.$

For operation above 25°C ambient derate linearly to maximum operating temperture at 20mW/°C for plasitc and at 19mW/°C for ceramic.

3. V<sub>sub</sub> must be the most positive with respect to V<sub>ss</sub>.

#### 12/13/01

**General Description**

The HV506 is a low-voltage serial to high-voltage parallel converter with push-pull outputs. It is especially suitable for use as a symmetric row driver in AC thin-film electroluminescent (ACTFEL) displays.

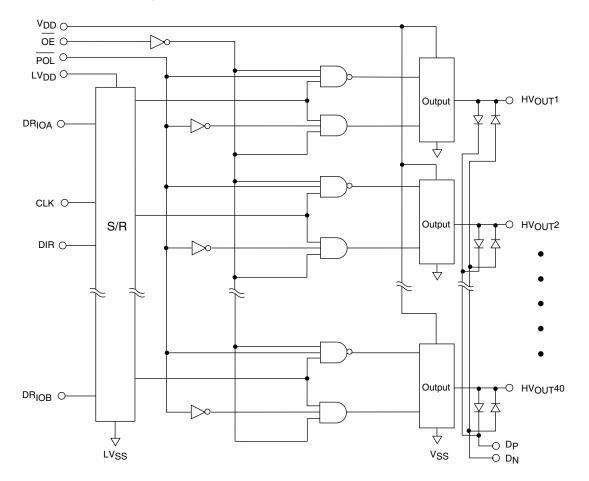

When the data reset pin  $(DR_{10})$  is at logic high, it will reset all the outputs of the internal shift register to zero. At the same time, the output of the shift register will start shifting a logic high from the least significant bit to the most significant bit. The  $DR_{10}$  can be triggered at any time. The DIR pin controls the direction of data through the device. When DIR is at logic high, DR<sub>IDA</sub> is the input and DR<sub>IOB</sub> is the output. When DIR is grounded, DR<sub>IOB</sub> is the input and the DR<sub>IOA</sub> is the output. See the Output Sequence Operation Table for output sequence. The  $\overline{POL}$  and  $\overline{OE}$  pins perform the polarity select and output enable function respectively. Data is clocked through the shift register loaded on the low to high transition of the clock. A logic high in the shift register will cause the other corresponding output to swing to  $V_{DD}$  if  $\overline{POL}$  is high, or to V<sub>ss</sub> if POL is low. All other outputs will be in the High-Z state. If OE is at logic high all outputs will be in the High-Z state. An output in the High-Z state may block up to 275V above  $V_{ss}$  or 275V below  $V_{DD}$ . The  $D_P/D_N$  pins are for the positive/negative discharge of the high voltage output HV<sub>out</sub>. Data output buffers are provided for cascading devices.

$LV_{DD}$  requires low current for the HV506 logic section.  $V_{DD}$  requires high current for the output section . Typically these two pins are at the same potential. The same current and potential conditions apply to the  $LV_{SS}$ , logic, and  $V_{SS}$ , output pins.  $V_{Sub}$  must always be equal or greater than the most positive supply.

Supertex Inc. does not recommend the use of its products in life support applications and will not knowingly sell its products for use in such applications unless it receives an adequate "products liability indemnification insurance agreement." Supertex does not assume responsibility for use of devices described and limits its liability to the replacement of devices determined to be defective due to workmanship. No responsibility is assumed for possible omissions or inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications, refer to the Supertex website: http://www.supertex.com. For complete liability information on all Supertex products, refer to the most current databook or to the Legal/Disclaimer page on the Supertex website.

# **Electrical Characteristics**

(over recommended operating conditions of  $V_{DD} = 12V$ ,  $LV_{DD} = 12V$ , and  $T_A = 25^{\circ}C$  unless noted)

### **DC Characteristics**

| Symbol           | Parameter                           |                   | Min                 | Max                 | Units | Conditions                                                                                |

|------------------|-------------------------------------|-------------------|---------------------|---------------------|-------|-------------------------------------------------------------------------------------------|

| I <sub>DD</sub>  | V <sub>DD</sub> supply current      |                   |                     | 10                  | mA    | f <sub>CLK</sub> = 3MHz                                                                   |

| I <sub>DDQ</sub> | Quiescent V <sub>DD</sub> supply cu | rrent             |                     | 100                 | μΑ    | All $V_{IN} = V_{SS}$ or $V_{DD}$                                                         |

| V <sub>OH</sub>  | High-level output                   | HV <sub>OUT</sub> | V <sub>DD</sub> -10 |                     | V     | I <sub>O</sub> = -300mA                                                                   |

|                  |                                     | Data out          | 10.8                |                     | V     | I <sub>O</sub> = -100μA                                                                   |

| V <sub>OL</sub>  | Low-level output                    | HV <sub>OUT</sub> |                     | V <sub>SS</sub> +10 | V     | I <sub>O</sub> = 300mA                                                                    |

|                  |                                     | Data out          |                     | 1.2                 | V     | I <sub>O</sub> = 100μA                                                                    |

| I <sub>IH</sub>  | High-level logic input curr         | rent              |                     | 1                   | μΑ    | $V_{IH} = V_{DD}$                                                                         |

| I <sub>IL</sub>  | Low-level logic input curre         | ent               |                     | -1                  | μΑ    | $V_{IL} = V_{SS}$                                                                         |

| I <sub>OFF</sub> | Output OFF leakage curr             | ent (High-Z)      |                     | 10                  | μΑ    | $ \begin{array}{l} HV_{OUT} \text{ - } V_{SS} = 275V, \\ V_{sub} = HV_{OUT} \end{array} $ |

|                  |                                     |                   |                     | 10                  | μΑ    | $V_{DD}$ - HV <sub>OUT</sub> = 275V,<br>$V_{sub}$ = $V_{DD}$                              |

Notes:

1. Only one output can be turned on at a time.

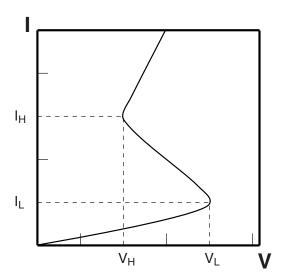

#### **SCR Characteristics**

| Symbol           | Parameter                           | Min                 | Max                 | Units | Conditions                                                                            |

|------------------|-------------------------------------|---------------------|---------------------|-------|---------------------------------------------------------------------------------------|

| V <sub>OH</sub>  | High-level output                   | V <sub>DD</sub> -10 |                     | V     | I <sub>O</sub> = -300mA                                                               |

| V <sub>OL</sub>  | Low-level output                    |                     | V <sub>SS</sub> +10 | V     | I <sub>O</sub> = 300mA                                                                |

| IL I             | Latching Current                    |                     | 15                  | mA    |                                                                                       |

| VL               | Latching Voltage                    |                     | 100                 | V     |                                                                                       |

| I <sub>H</sub>   | Holding Current                     | 10                  |                     | mA    |                                                                                       |

| V <sub>H</sub>   | Holding Voltage                     | 10                  |                     | V     |                                                                                       |

| I <sub>OFF</sub> | Output OFF leakage current (High-Z) |                     | 10                  | μΑ    | $\begin{array}{l} HV_{OUT} \text{-} V_{SS} = 275V, \\ V_{sub} = HV_{OUT} \end{array}$ |

|                  |                                     |                     | 10                  | μΑ    | $V_{DD}$ - $HV_{OUT}$ = 275V,<br>$V_{sub}$ = $V_{DD}$                                 |

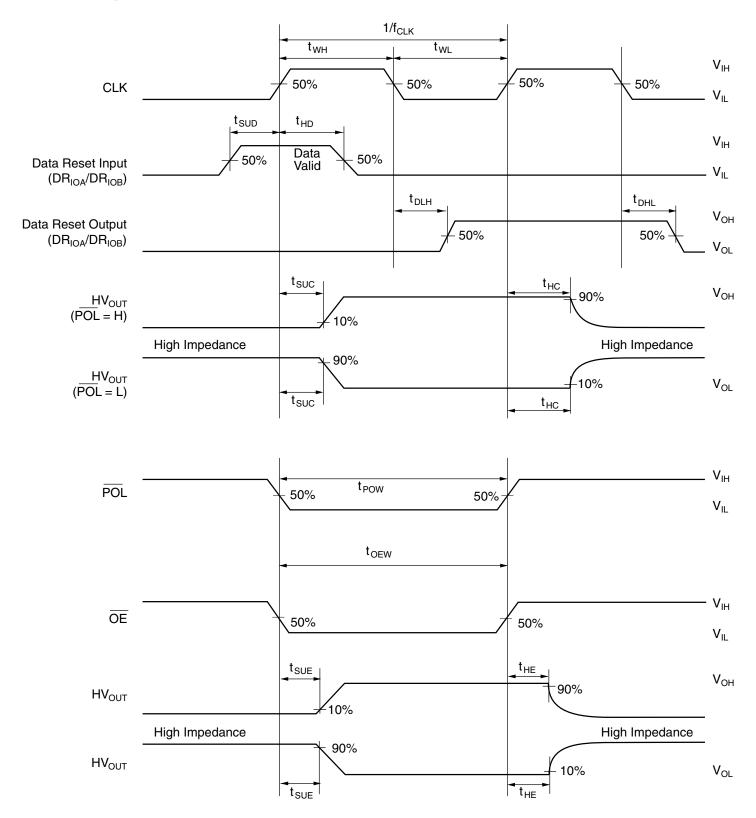

# **AC Characteristics**

| Symbol               | Parameter                                                 | Min | Max | Units | Conditions                                     |

|----------------------|-----------------------------------------------------------|-----|-----|-------|------------------------------------------------|

| f <sub>CLK</sub>     | Clock frequency                                           |     | 3   | MHz   |                                                |

| t <sub>W (H/L)</sub> | Pulse width - clock high or low                           | 150 |     | ns    |                                                |

| t <sub>SUD</sub>     | Data set-up time before clock rises                       | 50  |     | ns    |                                                |

| t <sub>HD</sub>      | Data hold time after clock rises                          | 50  |     | ns    |                                                |

| t <sub>SUC</sub>     | HV <sub>OUT</sub> delay from clock rises (Hi-Z to H or L) |     | 1   | μs    | $C_L = 10nF$                                   |

| t <sub>SUE</sub>     | HV <sub>OUT</sub> delay from Output Enable rises          |     | 600 | ns    | $C_L = 10nF$                                   |

| t <sub>HC</sub>      | HV <sub>OUT</sub> delay from clock rises (H or L to Hi-Z) |     | 2   | μs    | C <sub>L</sub> = 10nF                          |

| t <sub>HE</sub>      | HV <sub>OUT</sub> delay from Output Enable rises          |     | 600 | ns    | $C_L = 10nF$                                   |

| t <sub>DHL</sub> *   | Delay time clock to data output falls                     |     | 250 | ns    | C <sub>L</sub> = 15pF                          |

| t <sub>DLH</sub> *   | Delay time clock to data output rises                     |     | 250 | ns    | C <sub>L</sub> = 15pF                          |

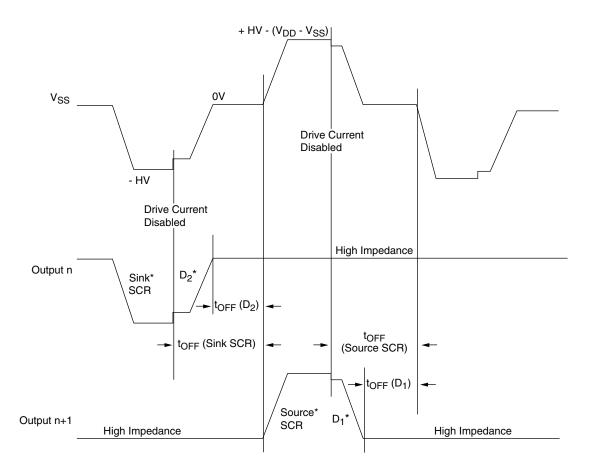

| $t_{OFF(SCR)}$       | Turn off time of output SCR                               |     | 4   | μs    | Time after $I_{OUT} \le 2mA$ ,<br>$C_L = 10nF$ |

| t <sub>OFF(D)</sub>  | Turn off time of output diode                             |     | 2   | μs    | Time after $I_{OUT} \le 2mA$ ,<br>$C_L = 10nF$ |

| t <sub>POW</sub>     | POL pulse width                                           | 3   |     | μs    |                                                |

| t <sub>OEW</sub>     | Output Enable pulse width                                 | 3   |     | μs    |                                                |

| SR                   | Slew rate of HV <sub>OUT</sub>                            |     | 200 | V/µs  |                                                |

\* The delay is measured from the trailing edge of the clock but the data is triggered by the rising edge of the clock. There is an internal delay for the data output which is equal to t<sub>wh</sub>. Therefore the delay is measured from the trailing edge of the clock.

# **Recommended Operating Conditions**

| Symbol           | Parameter                              | Min                         | Max  | Units               |     |

|------------------|----------------------------------------|-----------------------------|------|---------------------|-----|

| LV <sub>DD</sub> | Logic supply voltage                   | 10.8                        | 13.2 | V                   |     |

| V <sub>DD</sub>  | Output supply voltage                  |                             | 10.8 | 13.2                | V   |

| V <sub>IH</sub>  | High-level input voltage               | High-level input voltage    |      | LV <sub>DD</sub>    | V   |

| V <sub>IL</sub>  | Low-level input voltage                |                             | 0    | 0.2LV <sub>DD</sub> | V   |

| f <sub>CLK</sub> | Clock frequency                        | Clock frequency             |      | 3                   | MHz |

| Ι <sub>Ο</sub>   | High voltage output current            | High voltage output current |      | ±300                | mA  |

| T <sub>A</sub>   | Operating free-air temperature         | Plastic                     | -40  | +85                 | °C  |

|                  | Ceramic                                |                             | -55  | +125                | °C  |

| I <sub>OD</sub>  | Allowable pulse current through diodes |                             |      | ±500                | mA  |

#### Notes:

The substrate pin  $V_{sub}$  (pin 39) must be biased for proper output breakdown voltage.  $V_{sub} \ge V_{DD}$  or  $HV_{OUT}$  whichever is higher.

$\rm LV_{DD}/\rm V_{DD}$  are measured with respect to  $\rm LV_{SS}/\rm V_{SS}.$

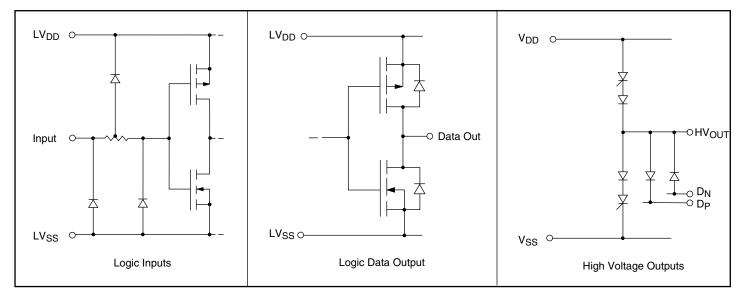

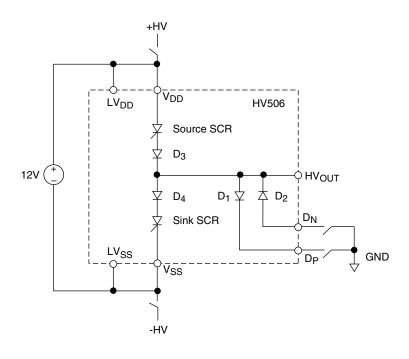

# **Input and Output Equivalent Circuits**

## **SCR Characteristics**

# **Switching Waveforms**

# **Functional Block Diagram**

## **Function Table**

| I/O Relations | Inputs |     |          |     |    |                |

|---------------|--------|-----|----------|-----|----|----------------|

| 1/O Helations | CLK    | DIR | S/R Data | POL | ŌĒ | HV Outputs     |

| O/P HIGH      | Х      | Х   | Н        | Н   | L  | Н              |

| O/P OFF       | Х      | Х   | L        | Х   | L  | HIGH-Z         |

| O/P LOW       | Х      | х   | Н        | L   | L  | L              |

| O/P OFF       | Х      | Х   | Х        | Х   | Н  | All O/P HIGH-Z |

Note:

H = logic high level, L = logic low level, X = irrelevant

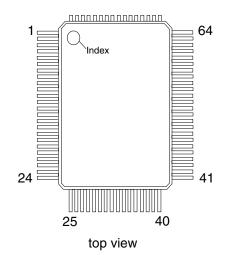

# **Output Sequence Operation Table**

| DIR | Data Reset In     | Data Reset Out                 | HV <sub>OUT</sub> # Sequence | Direction <sup>3</sup>                                                                                                                             |

|-----|-------------------|--------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| L   | DR <sub>IOB</sub> | DR <sub>IOA</sub> 1            | 40 → 1                       |                                                                                                                                                    |

| Н   | DR <sub>IOA</sub> | DR <sub>IOB</sub> <sup>2</sup> | 1 → 40                       | $\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{\mathbf{$ |

Notes:

1. DR<sub>IOA</sub> is DR<sub>IOB</sub> delayed by 40 clock pulses. 2. DR<sub>IOB</sub> is DR<sub>IOA</sub> delayed by 40 clock pulses. 3. Reference to chip layout drawing.

# **Typical Output Circuit Connections**

Note: The voltage potential between  $\text{LV}_{\text{DD}}/\text{V}_{\text{DD}}$  and  $\text{LV}_{\text{SS}}/\text{V}_{\text{SS}}$  must not exceed recommended operating conditions of 10.8V - 13.2V (12V typical)

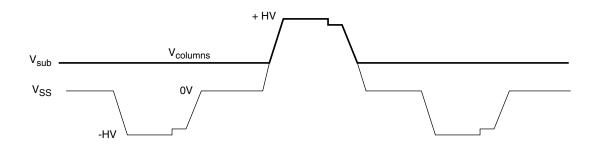

### **Substrate Bias Operation**

In order to achieve the desired output breakdown voltage, the substrate must be biased to the most positive potential of any circuit node. For this condition,  $V_{sub} \ge V_{DD}$  or  $HV_{OUT}$  whichever is

higher. Refer to Typical Output Circuit Connections for wiring. A typical  $\rm V_{sub}$  signal is shown below.

**Note:** In general, when driving the outputs positive,  $V_{SUB} = +HV$ . And when driving outputs negative,  $V_{SUB}$  equals most positive voltage; e.g. GND or >0V.

then discharged through a discharge diode when  $D_2$  is switched to GND. The application of a positive pulse to a row operates in a similar manner using the selected source SCR and  $D_1$ .

\* Notes internal device handling current flow. Refer to Typical Output Circuit Connections for schematic.

# **Pin Configurations**

#### HV506

| Onti     | Option A:            |          |                      |  |  |  |

|----------|----------------------|----------|----------------------|--|--|--|

| Pin      | Function             | Pin      | Function             |  |  |  |

| 1        | HV <sub>out</sub> 1  | 33       | OE                   |  |  |  |

| 2        | HV <sub>OUT</sub> 2  | 34       | POL                  |  |  |  |

| 3        | HV <sub>out</sub> 3  | 35       | LV <sub>DD</sub>     |  |  |  |

| 4        | HV <sub>OUT</sub> 4  | 36       | V <sub>ss</sub>      |  |  |  |

| 5        | HV <sub>OUT</sub> 5  | 37       | V <sub>DD</sub>      |  |  |  |

| 6        | HV <sub>OUT</sub> 6  | 38       | L V                  |  |  |  |

| 7        | HV <sub>OUT</sub> 7  | 39       | V <sub>sub</sub>     |  |  |  |

| 8        | HV <sub>OUT</sub> 8  | 40       | N/C                  |  |  |  |

| 9        | HV <sub>OUT</sub> 9  | 41       | N/C                  |  |  |  |

| 10       | HV <sub>OUT</sub> 10 | 42       | D <sub>N</sub>       |  |  |  |

| 11       | HV <sub>out</sub> 11 | 43       | D <sub>P</sub>       |  |  |  |

| 12       | HV <sub>OUT</sub> 12 | 44       | N/C                  |  |  |  |

| 13       | ΗV <sub>ουτ</sub> 13 | 45       | HV <sub>OUT</sub> 21 |  |  |  |

| 14       | HV <sub>OUT</sub> 14 | 46       | HV <sub>OUT</sub> 22 |  |  |  |

| 15       | HV <sub>OUT</sub> 15 | 47       | $HV_{OUT}^{}23$      |  |  |  |

| 16       | ΗV <sub>ουτ</sub> 16 | 48       | $HV_{OUT}$ 24        |  |  |  |

| 17       | ΗV <sub>ουτ</sub> 17 | 49       | $HV_{OUT}^{}25$      |  |  |  |

| 18       | HV <sub>OUT</sub> 18 | 50       | $HV_{OUT}^{}26$      |  |  |  |

| 19       | HV <sub>OUT</sub> 19 | 51       | HV <sub>OUT</sub> 27 |  |  |  |

| 20       | HV <sub>OUT</sub> 20 | 52       | HV <sub>OUT</sub> 28 |  |  |  |

| 21       | N/C                  | 53       | HV <sub>OUT</sub> 29 |  |  |  |

| 22       | D <sub>P</sub>       | 54       | HV <sub>OUT</sub> 30 |  |  |  |

| 23       | D <sub>N</sub>       | 55       | HV <sub>OUT</sub> 31 |  |  |  |

| 24       | N/C                  | 56       | HV <sub>OUT</sub> 32 |  |  |  |

| 25       | N/C                  | 57       | HV <sub>OUT</sub> 33 |  |  |  |

| 26       | LV <sub>ss</sub>     | 58       | HV <sub>OUT</sub> 34 |  |  |  |

| 27       |                      | 59       | HV <sub>OUT</sub> 35 |  |  |  |

| 28       | DIR                  | 60       | HV <sub>OUT</sub> 36 |  |  |  |

| 29<br>20 |                      | 61<br>62 | HV <sub>OUT</sub> 37 |  |  |  |

| 30<br>31 | CLOCK                | 62<br>63 | HV <sub>OUT</sub> 38 |  |  |  |

| 31       | DR <sub>IOA</sub>    | 63<br>64 | HV <sub>OUT</sub> 39 |  |  |  |

| 32       | DRIOR                | 04       | HV <sub>OUT</sub> 40 |  |  |  |

Note: Pins 65-80 are NC.

# Package Outline

3-sided Plastic 64-pin Gullwing Package

©2001 Supertex Inc. All rights reserved. Unauthorized use or reproduction prohibited. Downloaded from <u>Elcodis.com</u> electronic components distributor 1235 Bordeaux Drive, Sunnyvale, CA 94089 TEL: (408) 744-0100 • FAX: (408) 222-4895 www.supertex.com