## **Advanced Information**

February 1999

#### **DESCRIPTION**

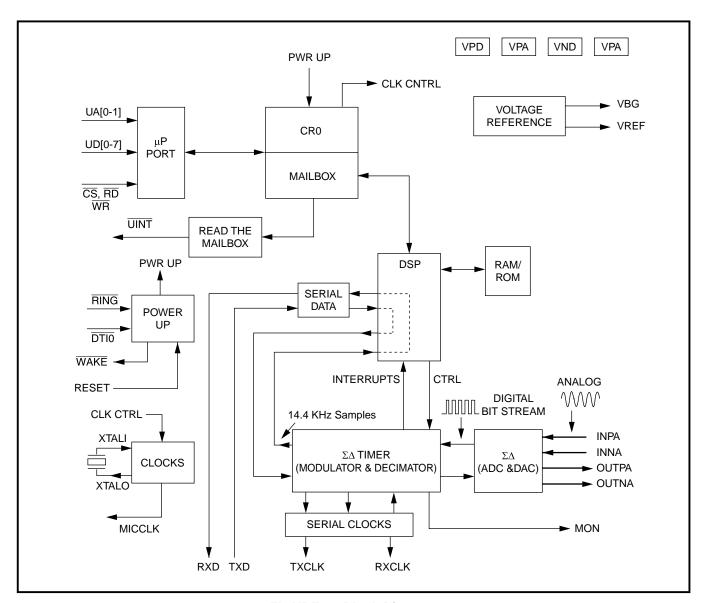

The 73M2921 is a CMOS integrated circuit which provides all the modem "Data Pump" functions required to implement a V.22bis data modem. It consists of a DSP (Digital Signal Processor) core with RAM and ROM data memory, ROM instruction memory, and register mapped input/output functions including timers, interrupts,  $\Sigma\Delta$  ADC and DAC ports and Serial Data I/O.

Once the 73M2921 has been initialized, all call progress and modem handshaking is automatic. The default conditions may be changed as required for country specific or custom applications.

The 73M2921 provides DTMF tone generation and detection, precise call progress detect and ADSI functions such as CAS tone detection.

Other features include a parallel interface control port between the host processor and the 73M2921. A synchronous serial data channel provides synchronizing clocks RXCLK and TXCLK from the modem pump to the controller.

The 73M2921 contains an oscillator and power control features.

The host controller function can be implemented with a 73M2910 communications micro controller or another commercial microcontroller (such as the 68302). The 73M2921 has been optimized to work with the 73M2910 synchronous serial port.

### **FEATURES**

- Automatic handshaking for all data modes

- Data Speeds:

V.22bis - 2400 b/s V.22, Bell 212 - 1200 b/s V.21, Bell 103 - 300 b/s V.23 1200 b/s - 75 b/s Bell 202 1200 b/s

• Facsimile Speeds:

V.29 - 9600, 7200 b/s V.27ter - 4800, 2400 b/s V.21 ch 2 - 300 b/s

- V.8bis applications

- Designed for 3.3 and 5-Volt systems.

- · Low operating power.

- Speaker monitor output

- Provides 2 tone generators for single tone or DTMF generation

- Provides DTMF tone detection

- Provides 4 precise and 1 imprecise call progress filters and corresponding detect bits with programmable thresholds and frequencies

- Provides CAS tone detection for ADSI and CLASS® feature support

- Supports parallel (8 bit) control, and synchronous serial data I/O

- 73M2921 provides a microcontroller interrupt

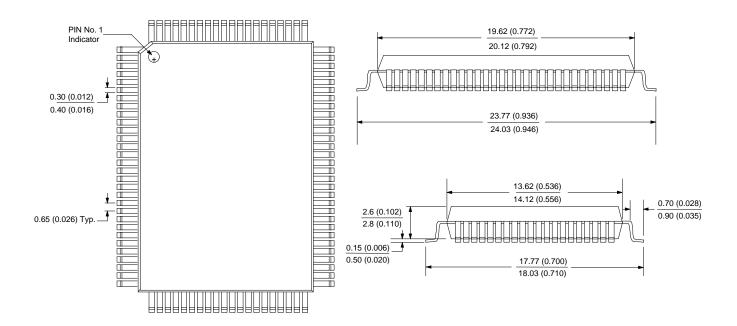

- Packaging: The 73M2921 is available in a QFP production package. A PGA package is available for prototyping

FIGURE 1 - Block Diagram

## **PIN DESCRIPTION**

## **POWER**

| NAME | PIN              | TYPE | DESCRIPTION                                                                                                         |

|------|------------------|------|---------------------------------------------------------------------------------------------------------------------|

| VPD  | 3, 23,<br>51, 82 | I    | DIGITAL POWER: Positive Digital Power.                                                                              |

| VND  | 4, 20,<br>52, 74 | 1    | DIGITAL POWER: Negative Digital Power.                                                                              |

| VPA  | 29, 36           | I    | ANALOG POWER: Positive Analog Power.                                                                                |

| VNA  | 27, 37           |      | ANALOG POWER: Negative Analog Power.                                                                                |

| VREF | 32               | 0    | VREF: Analog voltage reference for biasing of off chip analog function. Maximum output current is +/- 20µA.         |

| VBG  | 33               | 0    | BANDGAP VOLTAGE: Bandgap voltage pin used as a connection point for an external capacitor for noise reduction only. |

### **CLOCKS AND RESETS**

| NAME   | PIN | TYPE | DESCRIPTION                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|--------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| XTALI  | 22  | I    | RYSTAL INPUT: Onboard crystal oscillator input, or the master clock uput to the 73M2921 if the crystal oscillator is not used.                                                                                                                                  |  |  |  |  |  |  |

| XTALO  | 21  | I    | CRYSTAL OUTPUT: Onboard crystal oscillator output should be left unconnected if the crystal oscillator on the 73M2921 is not used. Along with XTALI and proper loading capacitors, these pins include an inverter for use with parallel resonant mode crystals. |  |  |  |  |  |  |

| MICCLK | 19  | 0    | MICROCONTROLLER CLOCK: Programmable clock output for use when the system oscillator is on the 73M2921. May be used to drive the system controller. The output frequency is controlled by CR0 bits D11-D9 (MCLK [2:0]).                                          |  |  |  |  |  |  |

| RESET  | 40  | I    | MASTER CHIP RESET: Active High Input with hysteresis. Resets the 73M2921 and the control registers. If not used as a reset source, this pin must be tied low.                                                                                                   |  |  |  |  |  |  |

## PIN DESCRIPTION (continued)

## **POWER CONTROL**

| NAME | PIN | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                |

|------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DTI0 | 26  | _    | DATA TERMINAL INTERRUPT 0: Active Low Input with hysteresis. Power up signal. The action of this pin can be masked by the PSDIS[1] register bit. This pin would connect to EIA-232 connection DTR in many applications. Requires a $50 \text{K}\Omega$ external pull up.                                                   |

| RING | 24  | I    | RING DETECT: Active Low Input with hysteresis. Power up signal. The action of this pin can be masked by the PSDIS[0] register bit. This pin would connect to the ring detect circuitry or the control microcontroller in many applications. Requires a $50 \text{K}\Omega$ external pull up.                               |

| WAKE | 39  | 0    | WAKE: Active Low Output. Indicates that a power up pin $(\overline{\text{RING}} \text{ or } \overline{\text{DTIO}})$ has been activated when the 73M2921 is in slave mode. The latched signal remains true until a reset of the wake function by a write to CR0 LSByte, or a chip reset. Requires a 50KΩ external pull up. |

### MICROCONTROLLER INTERFACE

| NAME     | PIN   | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|----------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| CS       | 15    | I    | CHIP SELECT: Active Low Input. Enables data transfers on the $\mu P$ parallel interface. Requires a 50K $\!\Omega$ external pull up.                                                                                                                                                                                         |  |  |  |  |  |

| RD       | 17    | I    | EAD: Active Low Input. Read enable signals for the mailbox/control gister interface.                                                                                                                                                                                                                                         |  |  |  |  |  |

| WR       | 16    | I    | WRITE: Active Low Input. Write enable signals for the mailbox/control register interface.                                                                                                                                                                                                                                    |  |  |  |  |  |

| UA[0:1]  | 13-14 | I    | ADDRESS: Address bits that are used by the μP to communicate with he 73M2921 mailbox and CR0.                                                                                                                                                                                                                                |  |  |  |  |  |

| UD [0:7] | 5-12  | I/O  | DATA: Parallel data bus for the mailbox/CR0 interface.                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| UINT     | 18    | 0    | INTERRUPT: $\mu$ C interrupt Active Low Output. Used as an interrupt to the microcontroller indicating that the 73M2921 needs data or has a request for the $\mu$ C. It is activated when the 73M2921 writes to the mailbox and cleared when the $\mu$ C reads the mailbox LSByte. Requires a 50K $\Omega$ external pull up. |  |  |  |  |  |

### PIN DESCRIPTION (continued)

#### **SERIAL DATA INTERFACE**

| NAME  | PIN | TYPE | DESCRIPTION                                                                                                                        |

|-------|-----|------|------------------------------------------------------------------------------------------------------------------------------------|

| RXCLK | 45  | 0    | RECEIVE CLOCK: Receive clock for the serial data interface. Data is transferred from the 73M2921 on the rising edge of the clocks. |

| TXCLK | 42  | 0    | TRANSMIT CLOCK: Transmit clock for the serial data interface. Data is transferred to the 73M2921 on the rising edge of the clocks. |

| RXD   | 44  | 0    | RECEIVE DATA: Receive Digital Data.                                                                                                |

| TXD   | 41  | I    | TRANSMIT DATA: Transmit Digital Data.                                                                                              |

#### **AUXILIARY FUNCTIONS**

| NAME | PIN | TYPE | DESCRIPTION                                                                                              |

|------|-----|------|----------------------------------------------------------------------------------------------------------|

| MON  | 38  | 0    | MONITOR: Speaker driver. PCM output under software control. See app note concerning the use of this pin. |

| PEXT | 50  | I    | EXTERNAL PROGRAM ENABLE: This pin must be tied low for normal operation.                                 |

#### **ANALOG I/O**

| NAME            | PIN       | TYPE | DESCRIPTION                                                           |

|-----------------|-----------|------|-----------------------------------------------------------------------|

| INPA,<br>INNA   | 34,<br>35 | I    | ANALOG INPUT: Differential analog input to a high resolution ADC.     |

| OUTPA,<br>OUTNA | 31,<br>30 | 0    | ANALOG OUTPUT: Differential analog output from a high resolution DAC. |

#### HARDWARE REQUIREMENTS

The 73M2921 chip is designed for a single +3.3 or 5 Volt supply and for minimum power consumption (~100mW @ 3.3V). It supports power down (idle) mode via microcontroller software control. It will also accept a request for power down from the DTE via hardware control. The device operates from internal ROM/RAM, but may be configured for external ROM operation and external RAM access (for custom applications) using either the prototype or the production packages.

### LINE/HYBRID INTERFACE

The 73M2921 chip provides a differential analog input and output. This interface will drive a standard Data Access Arrangement (DAA). The system controller provides additional control such as hook, phone and auxiliary relay, parallel pickup and in-use detect, and ring detect.

The Internal DAC provides a differential output signal with a maximum output swing of 1.2Vpp, capable of driving a  $50K\Omega$  load. One output can be used alone for a single ended output (with possible performance degradation).

The internal ADC has a differential input maximum of 1.2Vpp, and provides a biasing resistor to Vref for AC coupling. One input can be driven while leaving the other floating for a single ended input (with possible performance degradation). The signal passes through a passive anti-aliasing filter.

### **POWER CONTROL**

The power control circuit determines the state of the 73M2921 when powered down, and the means for waking up the chip. The function is related to the chip and DSP reset functions and is controlled by various input pins and register bits. The chip pins are RING, DTIO, and RESET. The CRO register bits that control power circuit function are RSTCHIP, RSTDSPB, ENOSC, ENDSPCK, ENMCLK, and PSDIS (1:0).

#### POWER CONTROL CIRCUIT FUNCTION

Power consumption can be reduced by turning off or slowing down specific circuit functions in register CR0.

- EN DSP=0: stops DSP clock.

- EN MCLK=0: turns off uC clock. MCLK=000: state gives lowest μC clock frequency.

- EN OSC=0: turns off oscillator and analog bias currents.

- DSPCK=000: state gives lowest DSP clock frequency.

The 73M2921 has a power-down mode. Access to this mode is described below.

**Power Down Mode:** To achieve power down first set RSTDSP to 0 in CR0 (bit 0). Second, set ENDSPCK, ENMCLK, and ENOSC to 0 in CR0 (bits 12, 8, and 7 respectively). Writing a one to ENDSPCK, ENMCLK, and ENOSC will bring the 73M2921 back to its previous power mode.

**Powering up:** Toggling the RESET pin,  $\overline{DTI0}$ , or  $\overline{RING}$  will power the 73M2921 up to Normal mode. Similar results can be achieved by writing to the reset pin in CR0 (00b, bit 3).

The following is a functionality chart for the power control circuitry. It shows all inputs and describes the effect on various 73M2921 functions.

| INPUT                | AFFECTED SIGNAL OR FUNCTION                                                    |

|----------------------|--------------------------------------------------------------------------------|

| PIN                  |                                                                                |

| RING                 | These are the two pins used to bring the chip out of a power                   |

| (Pin 24)             | down state. Their function can be masked by the PSDIS bits                     |

| DTI0                 | in register CR0.                                                               |

| (Pin 26)             |                                                                                |

| CR0 bits             |                                                                                |

| ENDSPCK<br>(CR0 D12) | Either of these bits in CR0 set to ONE inhibits the generation of a pulse that |

| ENOSC<br>(CR0 D7)    | will reset the DSP.                                                            |

| PSDIS1<br>(CR0 D2)   | Masks DTI0 input when set.                                                     |

| PSDIS0<br>(CR0 D1)   | Masks RING when set.                                                           |

**Table 4 - Power Control Functions**

#### **POWER CONTROL TIMING**

| DESCRIPTION                     | MIN | TYP | MAX | UNIT |

|---------------------------------|-----|-----|-----|------|

| Powerup input to active state   | 250 |     |     | μs   |

| Powerup input to inactive state | 50  |     |     | μs   |

**Table 5 - Power Control Timing**

#### DCE-DTE INTERFACE

The 73M2921 is designed to interface with a synchronous port such as that found on the TDK 73M2910. It also provides a parallel control interface. This parallel interface appears as an 8 bit memory mapped peripheral to the host controller.

#### **SERIAL DATA INTERFACE**

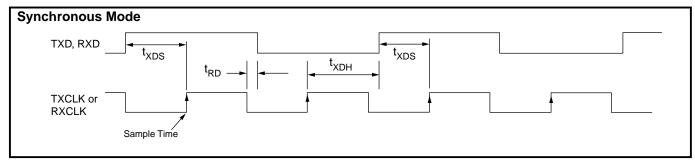

The serial data interface is a four pin bi-directional port. It consists of the TXD and RXD data paths (LSBit shifted in and out first, respectively), the TXCLK and RXCLK serial clock outputs associated with the data pins.

| SYMBOL | DESCRIPTION        | MIN | TYP | MAX | UNIT |

|--------|--------------------|-----|-----|-----|------|

| TXDS   | DATA to TXCLK      |     | Tbd |     | ns   |

| TXDH   | TXCLK to Data Hold |     | Tbd |     | ns   |

| TRD    | RXCLK to RXD Delay |     | Tbd |     | ns   |

**Table 3 - Serial Data Interface Timing**

FIGURE 7 - Serial Data Interface Timing Diagram

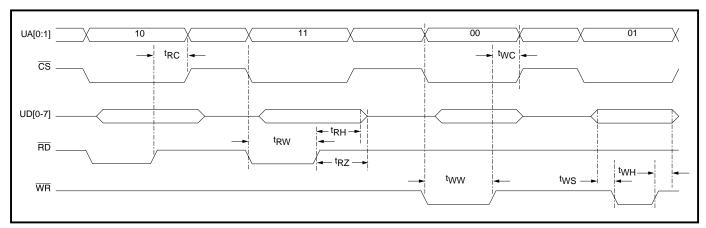

#### MICROCONTROLLER TO 73M2921 PARALLEL INTERFACE

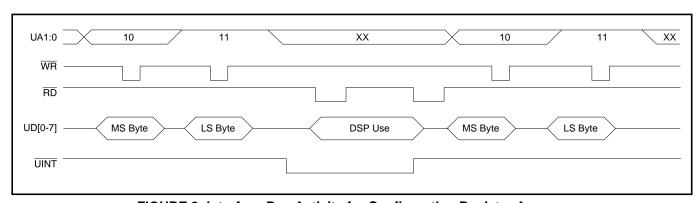

The interface between the microcontroller ( $\mu$ C) and the 73M2921 is accomplished through the 2 bit address UA[1:0] and 8 bit data bus UD[7:0],  $\overline{\text{RD}}$ ,  $\overline{\text{WR}}$ , and  $\overline{\text{CS}}$ . The 73M2921 chip provides an interrupt output to the  $\mu$ C ( $\overline{\text{UINT}}$ ). The 73M2921 and the  $\mu$ C communicate through two 16 bit registers, CR0 and the Mailbox; all  $\mu$ C accesses are 8 bit transfers. All reading and writing functions to and from the 73M2921 internal registers as well

February 99 Rev M TDK Semiconductor Page 7 of 41

as to internal RAM are performed through these four bytes of memory (see Table 1).

There are 5 separate types of register access possible through the microcontroller interface. These are:

- 1. Access to CR0.

- 2. Configuration register access (CR1, CR2), via the Mailbox.

- 3. Access to the 8-bit General register set via the Mailbox.

- 4. Unsolicited Response status, via the Mailbox.

- 5. Memory Block Transfer, via the Mailbox (Not described in this document, please refer to application note "Using the Mailbox on the 73M2921").

The host controller initiates all communications over the data bus by sending a command to either read or write to a location. CR0 is a special case in that it is accessed directly by way of the address bits and does not generate a response from the 73M2921. All other registers are accessed indirectly by way of a "mailbox" register and will generate a response from the 73M2921.

| UA [1:0] | ADDRESS | DESTINATION/SOURCE                        |            |

|----------|---------|-------------------------------------------|------------|

| 0 0      | 0       | Direct hardware control of CR0 (MSB)      | Write Only |

| 0 1      | 1       | Direct hardware control of CR0 (LSB)      | Write Only |

| 1 0      | 2       | Mailbox function - Control Byte/High Byte | Read/Write |

| 1 1      | 3       | Mailbox function - Data Byte/Low Byte     | Read/Write |

Table 1 - Interface Register Address

#### (1) CONTROL REGISTER CR0 DESCRIPTION

Control Register 0 (CR0) is a 16 bit register that defines functions of general importance to the modem system. CR0 can be written to directly from the microcontroller interface, and is read/write accessible by the internal DSP. Control of a number of DSP functions is accomplished by writing two 8 bit bytes to this 16 bit wide register. UA Address 00b accesses bits D15 through D8 and address 01b is for bits D7 through D0. Writing to these locations directly access CR0. Writing to the CR0 Register sets an internal bit notifying the internal DSP firmware that the host microcontroller has issued a command. Access to CR0 does not return a response to the host controller.

Table 2 shows the state of CR0 after various reset conditions. Note that a reset from the register bit D3 (Reset Chip) does not alter the power-up source mask bit D2 and D1 and they remain unchanged from the previous state (U = unchanged).

| CONDITION                | D1<br>5 | D1<br>4 | D1<br>3 | D1<br>2 | D1<br>1 | D1<br>0 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|--------------------------|---------|---------|---------|---------|---------|---------|----|----|----|----|----|----|----|----|----|----|

| Reset from<br>Reset Pin  | 1       | 1       | 1       | 1       | 1       | 1       | 1  | 0  | 1  | 0  | 1  | 1  | 0  | 0  | 0  | 1  |

| Reset from<br>CR0 bit D3 | 1       | 1       | 1       | 1       | 1       | 1       | 1  | 0  | 1  | 0  | 1  | 1  | 0  | U  | U  | 1  |

Table 2 - CR0 State After Reset

State of CR0 after reset from the reset pin and CR0 Reset bit (U = unchanged from previous state)

|                     |                           |                       |                                                                                                                                                                    | ESS: UA00, 01h (WRITE ONLY) |         |                                                                                                                                                                                                                        |                                |                         |                 |                  |                            |               |                |                  |

|---------------------|---------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------------|-----------------|------------------|----------------------------|---------------|----------------|------------------|

| D15 D14             | D13                       | D12                   | D11                                                                                                                                                                | D10                         | D9      | D8                                                                                                                                                                                                                     | D7                             | D6                      | D5              | D4               | D3                         | D2            | D1             | D0               |

| DSPCK               | (2:0)                     | EN<br>DSPCK           | MC                                                                                                                                                                 | LK (2:                      | 0)      | EN<br>MCLK                                                                                                                                                                                                             | EN<br>OSC                      | MA                      | INCK (          | (2:0)            | RESET                      |               | DIS<br>:0)     | RSTDSP           |

| BIT NO.             | N                         | AME                   | CC                                                                                                                                                                 | NDIT                        | ION     | DES                                                                                                                                                                                                                    | CRIPT                          | ION                     |                 |                  |                            |               |                |                  |

| D0                  | RSTD                      | SP                    |                                                                                                                                                                    | 1                           |         | by p                                                                                                                                                                                                                   | owering<br>nust be             | g up th<br>high.        | ne chi          | р. То            | T pin, the enable the      | DSP           | , the F        | RSTDSP           |

|                     |                           |                       |                                                                                                                                                                    | 0                           |         |                                                                                                                                                                                                                        | . While                        |                         |                 |                  | o be conti<br>III remain a |               |                |                  |

| D1, D2              | Power<br>Source<br>Disabl | e .                   |                                                                                                                                                                    |                             |         |                                                                                                                                                                                                                        | <del>G</del> .                 | on                      | PSDIS           | S[1] m           | ower up so                 | _             |                | TIO and          |

| D3                  | Reset                     | Chip                  |                                                                                                                                                                    |                             |         | Resets the state of the 73M2921 putting it into a kno state. The function of this bit is similar to that of the RES pin, except that this bit does NOT change the setting of POWERUP SOURCE DISABLE bits. See Table 2. |                                |                         |                 |                  |                            | RESET         |                |                  |

| D4,<br>D5,<br>D6    | Main 7<br>Clock           | Timer<br>Divisor      | D6                                                                                                                                                                 | D5<br>1                     | D4<br>1 | valu                                                                                                                                                                                                                   |                                | hown                    | sl              | nould            |                            | the t<br>used | imer.<br>with  | Default<br>n the |

| D7                  | Enable<br>Oscilla         |                       |                                                                                                                                                                    | 1<br>0                      |         |                                                                                                                                                                                                                        |                                |                         |                 |                  | . (Must be ops all chip    |               | ,              |                  |

| D8                  | Enable<br>proces<br>Clock | e Micro-<br>ssor      |                                                                                                                                                                    | 1                           |         | MCL<br>osci<br>MIC                                                                                                                                                                                                     | K=0), t<br>llator (E<br>CLK en | he EN<br>N OS0<br>abled | NMCL<br>C) beir | K bit<br>ng disa |                            | urned         | off prid       |                  |

|                     |                           |                       |                                                                                                                                                                    | 0                           |         | MIC                                                                                                                                                                                                                    | CLK dis                        | abled                   | (Set t          | :0 0 if r        | not using M                | 1ICCLI        | <b>&lt;</b> ). |                  |

| D9,<br>D10,<br>D11  |                           | controller<br>Divisor | D1 <sup>2</sup>                                                                                                                                                    | D10                         | D9<br>1 | of the oscillator frequency. Default values shown should be                                                                                                                                                            |                                |                         |                 | nould be         |                            |               |                |                  |

| D12                 | Enable<br>Clock           | e DSP                 |                                                                                                                                                                    |                             |         | Set by the RESET pin, the RESET CHIP to up the chip.  DSP clock enabled. (Must be set to run)                                                                                                                          |                                |                         |                 | or by p          | owering                    |               |                |                  |

|                     |                           |                       |                                                                                                                                                                    | 1<br>0                      |         |                                                                                                                                                                                                                        | clock o                        |                         | •               | ust be           | set to run)                |               |                |                  |

| D13,<br>D14,<br>D15 | D14, 1 1 1                |                       | Controls the internal DSP clock frequency as a function of the oscillator frequency. Default values shown should be used with the 18.432 MHz oscillator frequency. |                             |         |                                                                                                                                                                                                                        |                                |                         |                 |                  |                            |               |                |                  |

For a clean DSPCK transition when stopping the DSP (RSTDSP=0), the RSTDSP bit must be set low prior to the oscillator (ENOSC) being disabled.

For a clean DSPCK transition when starting the DSP ( $\overline{RSTDSP}$ =1), the  $\overline{RSTDSP}$  bit must be set high after the oscillator (ENOSC) is enabled. This happens automatically after reset or power up.

| MCLK  | Divisor | MICCLK Output |

|-------|---------|---------------|

| [2:0] |         |               |

| 0 0 0 | 12      | 1.536         |

| 0 0 1 | 6       | 3.072         |

| 0 1 0 | 3       | 6.144         |

| 0 1 1 | 1.5     | 12.288        |

| 1 0 0 | 8       | 2.304         |

| 1 0 1 | 4       | 4.608         |

| 1 1 0 | 2       | 9.216         |

| 1 1 1 | 1       | 18.432        |

Table 4 - μP clock (MHz) vs. Divisor

### USING THE MAILBOX REGISTER<sup>1</sup>

The mailbox function uses the same data interface as when accessing CR0 but has a different physical addresses (UA1:0 = 10b, 11b). The Mailbox is configured as two 8-bit bytes which are separated into a Control byte at address 10b and the Data byte at address 11b.

The  $\overline{\text{UINT}}$  interrupt is closely coupled to the use of the Mailbox. An interrupt from  $\overline{\text{UINT}}$  (DSP to microcontroller interrupt) indicates that the host controller should read the mailbox. This interrupt can be the result of the host accessing the Mailbox or an "unsolicited interrupt" indicating there has been a change in one of the status registers. The  $\mu$ C reads the MSB first, then the LSB. Reading the LSB sets  $\overline{\text{UINT}}$  high and clears the 73M2921 internal mail full flag bit, allowing the 73M2921 to write new data to the mailbox. Mailbox data is not explicitly formatted. The microcontroller and 73M2921 firmware define the control exchange format.

### (2) CONFIGURATION REGISTER ACCESS (CRA)

The configuration registers, CR1 and CR2 control some of the basic operating conditions. Some of the bits in these registers are for factory use only and should only be set to zero. Others, as noted, must be set to one for normal operation. Descriptions of CR1 and CR2 follow the programming section.

For Configuration Register Access, the Mailbox Control byte must be set up as follows:

### **Mailbox Control Byte for Configuration Register Access**

| D7  | D6    | D5  | D4 | D3 | D2 | D1 | D0 |

|-----|-------|-----|----|----|----|----|----|

| RES | WT/BT | R/W |    |    |    |    |    |

| 0   | 1     | 1/0 | 1  | 0  | 0  | 0  | 1  |

- Res = Reserved for DSP use.

- WT/BT = Word Transfer/Byte Transfer. Should be 1 (word transfer) for CRA.

- R/W = Read/Write. Read = 1, Write = 0

For Configuration Register Access, the Mailbox Data byte specifies CR1 or CR2 as follows:

#### Mailbox Data Byte for CR1 Access

Page 10 of 41 TDK Semiconductor February 99 Rev M

<sup>1</sup> Reading and writing through the Mailbox Register should be limited to once per millisecond while in idle mode and once per ten milliseconds otherwise.

| D7           | D6             | D5       | D4 | D3 | D2 | D1 | D0 |

|--------------|----------------|----------|----|----|----|----|----|

| 1            | 0              | 1        | 1  | 0  | 0  | 0  | 0  |

| Mailbox Data | a Byte for CR2 | 2 Access |    |    |    |    |    |

| D7           | D6             | D5       | D4 | D3 | D2 | D1 | D0 |

| 1            | 1              | 0        | 1  | 0  | 0  | 0  | 0  |

Reading and writing to the Configuration registers is a four step process for the host processor.

- (1) The host processor writes to the Mailbox Control byte:

- (a) When writing data to the configuration registers the control byte 051h should be written to UA address 10b.

- (b) When reading data from the configuration registers the control byte 071h should be written to UA address 10b.

- (2) The Host writes to the Mailbox Data byte (at UA address 11b, write either B0h to access CR1 or D0h to access CR2). Order is important as the writing of the Data byte triggers an internal interrupt in the DSP indicating that new mail is present. The 73M2921 will respond through the mailbox. The contents of the response are not important to the host.

- (3) The host reads/writes the high byte of CR1/CR2 at UA address 10b.

- (4) The host reads/writes the low byte of CR1/CR2 at UA address 11b.

FIGURE 2: Interface Bus Activity for Configuration Register Access

|     |   | Control Byte |    |           |          |     |   |   |                                  |

|-----|---|--------------|----|-----------|----------|-----|---|---|----------------------------------|

| MSB | 0 | 1            | 0  | 1         | 0        | 0   | 0 | 1 | WRITE TO CONFIGURATION REGISTERS |

|     |   |              |    | DA        | ATA      |     |   |   | Data Byte                        |

| LSB | 1 | 0            | 1  | 1         | 0        | 0   | 0 | 0 | CHOOSE<br>CR1                    |

|     |   |              | RE | SPONSE F  | ROM 73M2 | 921 |   |   | _                                |

| MSB | х | Х            | х  | х         | х        | х   | х | х |                                  |

|     |   |              |    | DA        | ATA      |     |   |   | _                                |

| LSB | Х | Х            | х  | х         | х        | х   | х | х |                                  |

|     |   |              |    | CR DATA F | ROM HOST | Г   |   |   | _                                |

| MSB | 1 | 0            | 0  | 1         | 0        | 0   | 0 | 0 | HIGH BYTE OF CR1                 |

|     |   |              |    | DA        | ATA      |     |   |   | _                                |

| LSB | 0 | 0            | 0  | 0         | 0        | 0   | 0 | 0 | LOW BYTE OF CR1                  |

FIGURE 3: Write Command and Response

An example of a Configuration Register write cycle is shown in figures 2 and 3. Figure 2 shows the activity on the interface register data pins and UINT. First there are two command bytes sent by the host processor. The 73M2921 responds (the contents of this response are not important to the host). Then the host writes the high and low byte of the Configuration register to the 73M2921.

An example of the Control and Data bytes for a CRA write is shown in Figure 3. In this example we will write 90 00h to Configuration register one (CR1). This turns on the digital portion of the 73M2921.

The Control byte shows D6 set to indicate that a word size transfer will take place. D5 is zero to indicate a write will occur. D4 is set to specify Configuration Register Access. D0 of the Control byte is always 1h for Configuration Register Access. The data byte shows D7 and D5 set to indicate that CR1 is to be accessed. D4 is always set for configuration register access. D3:0 are always zero for configuration register access.

The response from the 73M2921 will not be defined.

The word size transfer of CR1 data is also shown in figure 3. The MS byte is 90h. This enables the digital portion of the 73M2921. The LS byte is 0h. Refer to the configuration register description on pages 10 and 11 for further information.

**ADDRESS: 05H (101b)**

### REGISTER NAME: CR

## **CR1 Configuration Register 1**

CR1 controls Diagnostic modes, data wait, 5V power supply detect, speaker volume, ADC/DAC sampling rate, slave sync, digital loopback, digital interface loopback, enable digital interface, and enable timer. It also has bits that are reserved for test modes.

| D15         | D1       | 4  | D13                       | D12                    | D11              | D10                                      | D9                                                                                                                                                              | D8                                                                                                   | D7                                   | D6         | D5           | D4    | D3    | D2                          | D1           | D0           |

|-------------|----------|----|---------------------------|------------------------|------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------|------------|--------------|-------|-------|-----------------------------|--------------|--------------|

| EN<br>TIMER | TES<br>3 |    | TEST<br>2                 | EN<br>DIGI             | TDK              | TDK                                      | 0                                                                                                                                                               | 0                                                                                                    | SLAVE<br>SYNC                        | 16<br>KHZ  | SPKR<br>(1:0 |       | 0     | 5V<br>DETECT                | DATA<br>WAIT | DIAG<br>MODE |

| BIT NO      |          |    | NAME                      |                        | CONDI            | TION                                     | D                                                                                                                                                               | ESCI                                                                                                 | RIPTION                              |            |              |       |       |                             |              |              |

| D0          |          |    | Diagnos<br>Mode<br>est Mo |                        | Alway            | /s 0                                     | С                                                                                                                                                               | IAGN                                                                                                 | IOSTIC N                             | MODE:      | Must b       | e zei | о.    |                             |              |              |

| D1          |          | _  | Data Wa<br>est Mo         |                        | Alway            | /s 0                                     | Must be zero.                                                                                                                                                   |                                                                                                      |                                      |            |              |       |       |                             |              |              |

| D2          |          | 5  | 5V Dete<br>(output        |                        |                  |                                          | 5                                                                                                                                                               | V rar                                                                                                |                                      | te, this   | s signa      |       |       | to the 73N<br>only when     |              |              |

| D3          |          |    | 0                         |                        |                  |                                          | ١                                                                                                                                                               | lot Us                                                                                               | ed.                                  |            |              |       |       |                             |              |              |

| D4,D5       |          | Vo | Speake<br>lume (1         | er<br>:0) <sup>2</sup> | 1<br>1<br>0<br>0 | 1<br>0<br>1<br>0                         | N<br>L                                                                                                                                                          | 1ediur                                                                                               | olume<br>n Volume<br>olume<br>er off | Э          |              |       |       |                             |              |              |

| D6          |          |    | 16KHz                     | <u>.</u>               | 1                | 1 The ADC/DAC sampling rates are 16.0KHz |                                                                                                                                                                 |                                                                                                      |                                      |            |              |       |       |                             |              |              |

|             | Ì        |    |                           | Ī                      | 0                |                                          | Т                                                                                                                                                               | he A[                                                                                                | DC/DAC                               | samplii    | ng rate      | s are | 14.4k | KHZ (Defa                   | ult)         |              |

| D7          |          |    | lave Sy<br>nodem t        | test                   | 1                |                                          |                                                                                                                                                                 | The phase error register measures the time between the rising edge of RXC and the rising edge of TXC |                                      |            |              |       |       |                             |              | rising       |

|             |          |    | mode)                     |                        | 0                |                                          |                                                                                                                                                                 |                                                                                                      | ase erro<br>f EXC ar                 |            |              |       |       | ime betwe                   | en the r     | ising        |

| D8,D9       |          |    | 0                         |                        |                  |                                          | N                                                                                                                                                               | lot Us                                                                                               | ed                                   |            |              |       |       |                             |              |              |

| D10         |          |    | TDK                       |                        | Alway            | /s 0                                     | Т                                                                                                                                                               | DK pı                                                                                                | roprietary                           | <b>/</b> . |              |       |       |                             |              |              |

| D11         |          |    | TDK                       |                        | Alway            | /s 0                                     | Т                                                                                                                                                               | DK pı                                                                                                | roprietary                           | <i>/</i> . |              |       |       |                             |              |              |

| D12         |          |    | able Dig<br>Interfac      |                        | 1                |                                          |                                                                                                                                                                 |                                                                                                      |                                      |            |              |       |       | TXCLK, For the for norm     |              |              |

|             |          |    |                           |                        | 0                |                                          | Tri-states pins TXCLK and RXCLK (with a weak pull-down to RXD pin is driven to a 1, TXD is disabled at the input pin, and the timer baud clocks are forced low. |                                                                                                      |                                      |            |              |       |       |                             |              |              |

| D13         |          |    | Test 2                    |                        | 0                |                                          | Λ                                                                                                                                                               | lust b                                                                                               | e zero.                              |            |              |       |       |                             |              |              |

| D14         |          |    | Test 3                    |                        | 0                |                                          | N                                                                                                                                                               | lust b                                                                                               | e zero.                              |            |              |       |       |                             |              |              |

| D15         |          | En | nable Ti                  | mer                    | 1                |                                          |                                                                                                                                                                 |                                                                                                      |                                      |            |              |       |       | or transmit<br>GI is true). | and red      | ceive        |

February 99 Rev M TDK Semiconductor Page 13 of 41

<sup>&</sup>lt;sup>2</sup> Volume PCM output on pin 38, MON, under software control. See application note concerning the use of this pin.

REGISTER NAME: CR2 Configuration Register 2 ADDRESS: 06H (110b)

CR2 controls analog port enable, analog loopback, ADC receive gain, VREF voltage, charge pump, and wide transmit bandwidth. It also has bits that are reserved for test modes.

| D15           | D14 | D13              | D12   | D11      | D1         | 0                                                                                                                                                                                                | D9                         | D8        | D7      | D6     | D5      | D4     | D3      | D2    | D1  | D0 |

|---------------|-----|------------------|-------|----------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------|---------|--------|---------|--------|---------|-------|-----|----|

| WIDE<br>TX BW | N/A | VREF             | N/A   | TDK      | EN<br>ANAL |                                                                                                                                                                                                  | TEST<br>5                  | TEST<br>4 | 0       | 0      | 0       | 0      | 0       | 0     | 0   | 0  |

| BIT NO        |     | NAME             |       | CONDITIO | N          | DESCRIPTION                                                                                                                                                                                      |                            |           |         |        |         |        |         |       |     |    |

| D0 – D7       | 7   | N/A              |       | 0        |            | Not Used.                                                                                                                                                                                        |                            |           |         |        |         |        |         |       |     |    |

| D8            |     | Test 4           |       | 0        |            | Must be zero.                                                                                                                                                                                    |                            |           |         |        |         |        |         |       |     |    |

| D9            |     | Test 5           |       | 0        |            | Must be zero.                                                                                                                                                                                    |                            |           |         |        |         |        |         |       |     |    |

| D10           |     | Enable<br>Analog |       | 1        | NOT        | E: Whe                                                                                                                                                                                           | turned on the are is loope | nalog     | port is | enable | d and t |        | -       |       |     |    |

|               |     |                  |       | 0        |            | Analog port turned off. All analog currents are off, including the bandgap generator. The setting of the ENOSC register bit to the disabled state also forces all analog power to be turned off. |                            |           |         |        |         |        |         |       |     |    |

| D11           |     | TDK              |       |          |            | TDK                                                                                                                                                                                              | propri                     | ietary.   |         |        |         |        |         |       |     |    |

| D12           |     | N/A              |       | 0        |            | Not u                                                                                                                                                                                            | used.                      |           |         |        |         |        |         |       |     |    |

| D13           |     | VREF             |       |          |            | Sele                                                                                                                                                                                             | cts the                    | e voltag  | e refe  | erence | volta   | ge     |         |       |     |    |

|               |     |                  |       | Set to 0 |            | 1.25                                                                                                                                                                                             | V DSF                      | detect    | tors re | equire | this se | etting | on this | versi | on. |    |

| D14           |     | N/A              |       | 1        |            | Not u                                                                                                                                                                                            | used.                      |           |         |        |         |        |         |       |     |    |

| D15           |     | ide Tran         | •     | 1 5      |            | Sets the transmit filter to pass 10KHz                                                                                                                                                           |                            |           |         |        |         |        |         |       |     |    |

|               |     | Bandwid          | dth 0 |          |            | Sets the transmit filter to pass 3KHz (default)                                                                                                                                                  |                            |           |         |        |         |        |         |       |     |    |

### (3) GENERAL REGISTER ACCESS (GRA)

For General Register Access (GRA), the mailbox the Control byte from the host controller is broken down into bit segments as follows:

#### General Register Access Control Byte: Microcontroller to 73M2921

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3  | BIT 2          | BIT 1 | BIT 0 |

|-------|-------|-------|-------|--------|----------------|-------|-------|

| Res   | WT/BT | R/W   |       | Pogis  | etor Addrose B | its   |       |

| 0     | 0     | 1/0   |       | ixegis | ster Address D | 11.5  |       |

Res = Reserved

$WT/\overline{BT}$  = Word Transfer/Byte Transfer. Should be 0 (byte transfer) for GRA.

$R/\overline{W}$  = Read / Write. 1 = Read, 0 = Write

Register Address Bits = 5 bit address for the register being accessed. See General Register descriptions in the following section.

(Register address 00000b is reserved CR0 location)

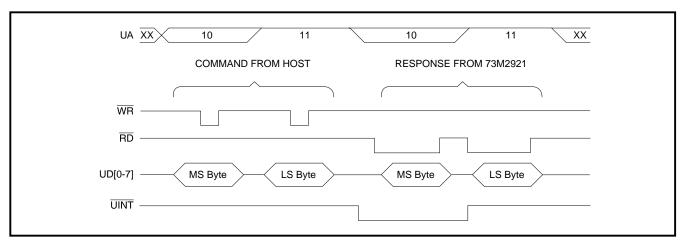

Reading and writing to the General Registers via the Mailbox is a four step process for the µC.

- (1) The  $\mu$ C writes a Control byte (UA1:0 = 10b) to the mailbox with the R/ $\overline{W}$  bit in the appropriate state for a read or a write.

- (2) Then the  $\mu$ C writes a Data byte (UA1:0 = 11b). The Data byte contains the data to be written or null (00h) if a read is performed. Order is important as the Data byte triggers an internal interrupt in the 73M2921 firmware indicating new mail present. The 73M2921 then:

- (a) reads the mailbox

- (b) writes back to the mailbox register the Control Byte.

- (c) writes a response code (if  $R/\overline{W} = 0$ ) or data (if  $R/\overline{W} = 1$ ) to the Data Byte. The response code will be 00h for OK and 01h for ERROR

- (d) Lowers  $\overline{\text{UINT}}$  to interrupt the  $\mu\text{C}$  indicating that data is in the Mailbox from the 73M2921.

The response from the 73M2921 can either be polled by the host controller or interrupt-driven. In the interrupt-driven response, an interrupt is issued by the 73M2921 from UINT when the response data is available, at which time the microcontroller reads two bytes (Control, Data) from the 73M2921. Reading valid Data clears the UINT interrupt for the next command. All reads and writes to the General registers will get an immediate response. In a polled mode of operation, if data is not ready, the Control and Data byte will both be zero. When the Control byte is non-zero, data is available.

- (3) The  $\mu$ C reads the Control byte (UA1:0 = 10b).

- (4) The μC reads the Data byte (UA1:0 = 11b). The data is the response code if the μC had requested a write, or the contents of the General Register in the Control address field if the μC had requested a read. This clears the UINT to a high state. The ERROR indicator byte should never be received when communications between the μC and the 73M2921 are working properly.

The Control byte returned by the 73M2921 is broken down into bit segments as follows:

### Control byte 73M2921 to Microcontroller

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2         | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|---------------|-------|-------|

| UR    | WT/BT | R/W   |       | Reais | ter Address E | lito  |       |

| 1/0   | 0     | 1/0   | _     | Regis | tel Address E | ons   | -     |

UR = Unsolicited Response. Set if data is not response to last command. WT/BT = Word Transfer/Byte Transfer. Should be 0 (byte transfer) for GRA.

$R/\overline{W} = Read = 1$ , Write = 0.

Register Address shadows last operation.

FIGURE 4 - Interface Bus Data Activity

|     |      |   | COMMAN | ND FROM H | IOST CON | TROLLER |   |   |                      |  |  |  |

|-----|------|---|--------|-----------|----------|---------|---|---|----------------------|--|--|--|

| MSB | 0    | 0 | 0      | 0         | 0        | 0       | 0 | 1 | WRITE TO<br>H/S REG. |  |  |  |

|     | DATA |   |        |           |          |         |   |   |                      |  |  |  |

| LSB | 0    | 0 | 0      | 0         | 0        | 1       | 0 | 0 | V.22 bis<br>H/S      |  |  |  |

|     |      |   |        |           |          |         |   |   |                      |  |  |  |

|     |      |   | RE     | SPONSE F  | ROM 73M2 | 921     |   |   | 7                    |  |  |  |

| MSB | 0    | 0 | 0      | 0         | 0        | 0       | 0 | 1 | ECHO<br>OF COMMAND   |  |  |  |

|     |      |   |        |           |          |         |   |   |                      |  |  |  |

|     | DATA |   |        |           |          |         |   |   |                      |  |  |  |

| LSB | 0    | 0 | 0      | 0         | 0        | 0       | 0 | 0 | ок                   |  |  |  |

|     |      |   |        |           |          | •       |   |   | _                    |  |  |  |

FIGURE 5 - Write Command and Response

An example of a write cycle is shown in Figure 4 and 5. Figure 4 shows the activity on the interface data pins and UINT. First there are two command bytes sent by the host controller, then an interrupt is generated in UINT telling the host to read the response data, then the controller reads back the response from the 73M2921. The UINT interrupt is reset when the LS byte is read.

An example of the Control and Data register data in a write command process is shown in Figure 5. In this example we will write data to the Handshake Register telling it to perform a V.22bis handshake. The Control byte shows bit 5 low indicating a write process and the lower 5 address bits are set to address 00001b, the Handshake register. The Data byte contains the new contents for the Handshake register, in this case 04h, indicating a V.22 handshake will be performed. The 73M2921 processes this command and generates an interrupt on UINT. The host then reads the data from the Control register, which echoes the command sent and the Data register which contain all zeros, or a successful operation. UINT is cleared when the Data byte is read.

#### **UNSOLICITED RESPONSE**

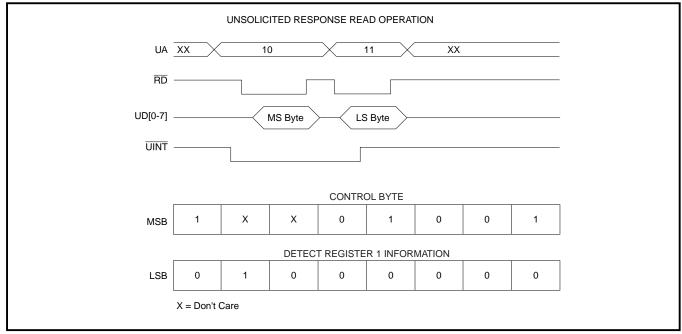

A  $\overline{\text{UINT}}$  (low) interrupt can be the result of the  $\mu\text{C}$  doing a General register access (GRA, previously described), or an Unsolicited Response indicating there has been a change in one of the status registers. An Unsolicited Response is defined as any response or information sent from the 73M2921 to the mailbox, which was the result of an unsolicited interrupt from the internal DSP. The general register set  $\overline{\text{UINT}}$  interrupt service routine must always check bit 7 of the Control byte to determine whether the interrupt was the result of a GRA in progress or an Unsolicited Response from the General register set status registers. An Unsolicited Response must always be serviced first, then the GRA in progress can be resumed. The data received from the 73M2921 is broken into Control and Data fields. Address 10b is the Control byte and Address 11b is the Data byte.

As an example, the user can enable each individual bit in each Detect Register to create an interrupt every time a detect bit has changed state. Once a detect bit is enabled, any change in state for that bit will trigger an Unsolicited Interrupt which sets bit 7 of the control byte to a one and the address bits of the Control byte to the address of the register which contains the bit that changed state. The Data byte will contain the contents of that register. Reading the mailbox clears the interrupt from the 73M2921 and allows further interrupts to occur.

The Control byte is broken down into bit segments as follows:

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3  | BIT 2          | BIT 1 | BIT 0 |

|-------|-------|-------|-------|--------|----------------|-------|-------|

| UR    | WT/BT | R/W   | -     | Genera | l Register Add | ress  | -     |

UR = Unsolicited Response. Set if data is not response to last command.

WT/BT = Word Transfer/Byte Transfer. Will always be zero (byte transfer) during Unsolicited Interrupt.

$R/\overline{W} = Read/W$  rite. Shadows last command. (Don't care).

The General Register Address holds detect register address which triggered the interrupt.

In the example shown in Figure 6, the UR bit 7 will be set informing the microcontroller that this is an unsolicited response. The WT/BT bit is clear as this is a byte transfer. The address bits hold the address of Detect Register 1 (09h), which generated the interrupt. The Data byte contains the Detect register information. In this case an S1 signal is being received.

FIGURE 6 - Unsolicited Interrupt Example

## 2921 GENERAL REGISTER SET SUMMARY

| NAME                   | R/W | FIVE BIT<br>ADDRESS<br>(HEX) | COMMENT                                                                                                                                                               |

|------------------------|-----|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Mode<br>Handshake | R/W | 01h                          | Selects automatic handshake to be performed                                                                                                                           |

| Connection Detect      | R   | 02h                          | Read Only, indicates successful handshake in Data mode                                                                                                                |

| DTMF Dial              | R/W | 03h                          | Sets DTMF digit and twist for transmission                                                                                                                            |

| DTMF Detect            | R   | 04h                          | Read only, indicates DTMF digit received                                                                                                                              |

| Data Mode Control      | R/W | 05h                          | Selects answer/originate and retrain modes allowed                                                                                                                    |

| Test Control           | R/W | 06h                          | Selects test patterns, test mode handshaking, scrambler/descrambler operation.                                                                                        |

| Version                | R   | 07h                          | Read only, revision level of the 73M2921                                                                                                                              |

| Detect 1 Enable        | R/W | 08h                          | Enables interrupts on changes of state from Detect Reg. 1 status bits.                                                                                                |

| Detect Register 1      | R   | 09h                          | Read only, indicates status of detectors used during handshaking for various modes.                                                                                   |

| Detect 2 Enable        | R/W | 0Ah                          | Enables interrupts on changes of state from Detect Reg. 2 status bits.                                                                                                |

| Detect Register 2      | R   | 0Bh                          | Read only, indicates status of detectors used during handshaking for various modes.                                                                                   |

| Transmit Control       | R/W | 0Ch                          | Selects data format or FSK, carrier transmission in DATA mode or DTMF transmit enable in CALL PROGRESS mode.                                                          |

| General Control        | R/W | 0Dh                          | Controls transmit power level, idle mode power consumption, receive gain boost, clock out enable                                                                      |

| Fax Handshake          | R/W | 0Eh                          | Controls Fax speed and transmit or receive mode                                                                                                                       |

| Reserved               | Х   | 0Fh                          | Reserved                                                                                                                                                              |

| Mode Control           | R/W | 010h                         | Controls Call Progress, Data or Idle Mode selection. Also controls method of initialization and modification of default settings. Affects operation of all registers. |

| MSE0                   | R   | 011h                         | Read only, Least Significant Byte of the DSP error signal. Indication of signal quality.                                                                              |

| MSE1                   | R   | 012h                         | Read only, Most Significant Byte of the DSP error signal. Indication of signal quality.                                                                               |

| CPTX                   | R/W | 014h                         | Controls Call Progress transmit functions.                                                                                                                            |

| PCPD Detect<br>Enable  | R/W | 018h                         | Enables interrupts on changes of state from PCPD detect bits.                                                                                                         |

| PCPD Detect            | R   | 019h                         | Read only, indicates detection of precise call progress tones.                                                                                                        |

Note: Reserved bits should never be programmed to a 1 state.

### HANDSHAKE REGISTER ADDRESS: 01H (01d, 00001b) MODE: DATA

| BIT D7  | BIT D6   | BIT D5   | BIT D   | 4                                                   | BIT D3                                              | BIT D2         | BIT D1        | BIT D0 |  |  |  |

|---------|----------|----------|---------|-----------------------------------------------------|-----------------------------------------------------|----------------|---------------|--------|--|--|--|

| V.23    | V.21     | Bell 103 | Bell 21 | 12                                                  | V.22                                                | V.22bis        | Bell 202      | Res.   |  |  |  |

| BIT NO. | NAME     | CONDI    | TION    | DES                                                 | DESCRIPTION                                         |                |               |        |  |  |  |

| D0      | Reserved | 1        | Res     |                                                     | Reserved for future use.                            |                |               |        |  |  |  |

| D1      | Bell 202 | 1        | Ins     |                                                     | Instructs the modem to attempt a Bell 202 handshake |                |               |        |  |  |  |

| D2      | V.22bis  | 1        |         | Insti                                               | ructs the mode                                      | m to attempt a | V.22bis hands | shake  |  |  |  |

| D3      | V.22     | 1        | Inst    |                                                     | ucts the mode                                       | m to attempt a | V.22 handsha  | ke     |  |  |  |

| D4      | Bell 212 | 1        |         | Instructs the modem to attempt a Bell 212 handshake |                                                     |                |               |        |  |  |  |

| D5      | Bell 103 | 1        |         | Instructs the modem to attempt a Bell 103 handshake |                                                     |                |               |        |  |  |  |

| D6      | V.21     | 1        |         | Instructs the modem to attempt a V.21 handshake     |                                                     |                |               |        |  |  |  |

| D7      | V.23     | 1        | Instr   |                                                     | Instructs the modem to attempt a V.23 handshake     |                |               |        |  |  |  |

Note: The Handshake register defines the handshake methods allowed during the connection phase of a communication session. Only one bit can be set at a given time except for automatic V.22bis fallback to V.22 or Bell 212A which requires both BIT D2 and BIT D3 to be set. The master transmit enable, TXEN, BIT D7 of the TRANSMIT CONTROL REGISTER (0CH) must be set for the handshake transmit functions to operate.

### CONNECTION DETECT REGISTER (READ ONLY) ADDRESS: 02h (02d, 00010b) MODE: DATA, FAX

| BIT D7     |                | BIT D6            |          | BIT D5   | BIT D4                                                  | BIT D3           | BIT D2      | BIT D1      | BIT D0 |  |  |  |  |

|------------|----------------|-------------------|----------|----------|---------------------------------------------------------|------------------|-------------|-------------|--------|--|--|--|--|

| V.23 (da   | ata)           | V.21 (            | data)    | Bell 103 | Bell 212                                                | V.22 (data)      | V.22bis     | Bell 202    | Res.   |  |  |  |  |

| V.29 (fa   | ax)            | V.21 CF           | H2 (fax) |          |                                                         | V.27ter (fax)    |             |             |        |  |  |  |  |

| BIT<br>NO. | N              | AME               | CON      | DITION   | DESCRIPTION                                             |                  |             |             |        |  |  |  |  |

| D0         | Res            | served            |          |          | Reserved for future use.                                |                  |             |             |        |  |  |  |  |

| D1         | Ве             | II 202            |          |          | Informs processor Bell 202 was detected.                |                  |             |             |        |  |  |  |  |

| D2         | V.2            | 22bis             |          |          | Informs processor of a successful V.22bis connection.   |                  |             |             |        |  |  |  |  |

| D3         | V              | <sup>7</sup> .22  | Data l   | Mode     | Informs processor of a successful V.22 connection.      |                  |             |             |        |  |  |  |  |

|            | V.:            | 27ter             | Fax N    | Лode     | Informs processor of a successful V.27ter connection.   |                  |             |             |        |  |  |  |  |

| D4         | Ве             | ll 212            |          |          | Informs processor of a successful Bell 212A connection. |                  |             |             |        |  |  |  |  |

| D5         | Be             | II 103            |          |          | Informs pro                                             | cessor of a succ | essful Bell | 103 connect | tion.  |  |  |  |  |

| D6         | V              | <sup>7</sup> .21  | Data I   | Mode     | Informs pro                                             | cessor of a succ | essful V.21 | connection  | •      |  |  |  |  |

|            | V.2            | V.21 CH2 Fax Mode |          |          | Informs processor of a successful V.21 CH2 connection.  |                  |             |             |        |  |  |  |  |