# **High Speed Differential APC Amplifier**

## **FEATURES**

- Dual Wavelength

- Slew Rate of 300V/µs

- Fast Settling Time 7ns

- Gain Control

- 2V Output Swing

- Low Offset Voltage: < 10mV</p>

- Low Offset Drift: < 20μV/°C

- 12dB External Gain Adjust Range

# **APPLICATIONS**

- DVDRW

- DVDRAM

- CDRW

## **DESCRIPTION**

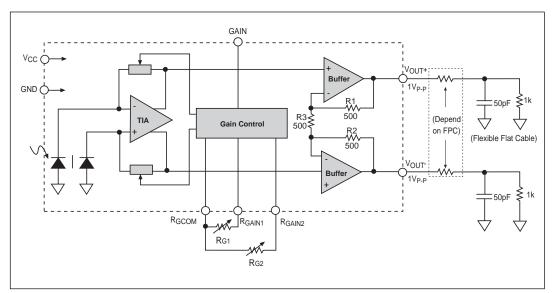

The SP8126B is a high-speed, differential output APC amplifier that integrates the photodiode and adjustable gain block on one chip. Independent gain control allows individual adjustment for 780mn and 650nm wavelength operation, as found in CD/DVD optical storage drives. This allows the user to control the laser power of the system in high-speed DVDRW, DVDRAM and CDRW systems. The wide 2V output swing also allows better system performance, through improved dynamic range.

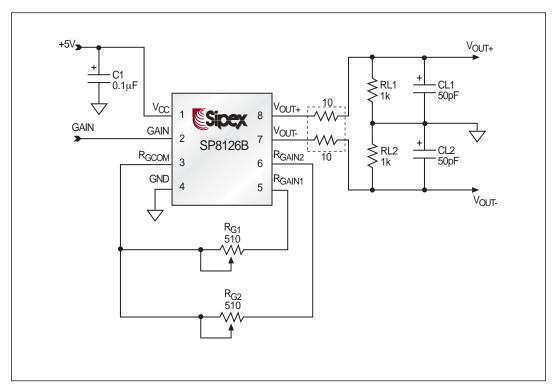

Figure 1. SP8126B Functional Diagram and Typical Application

Rev:B Date: 3/18/04

SP8126B High Speed Differential APC Amplifier

© Copyright 2004 Sipex Corporation

# **ABSOLUTE MAXIMUM RATINGS**

| T <sub>J(MAX)</sub>  | These are     |

|----------------------|---------------|

| V <sub>S(MAX)</sub>  | of the device |

| V <sub>IN(MAX)</sub> | indicated in  |

|                      | holow is no   |

**Power Supply Voltage**

Continuous Power Dissipation (T<sub>AMB</sub> = 70°C) COB (derate 13.3mW/°C above +70°C) ........ 90mW These are stress ratings only and functional operation of the device at these ratings or any other above those indicated in the operation sections of the specifications below is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

# **ELECTRICAL SPECIFICATIONS**

Unless otherwise noted:  $V_{CC}$  = 5.0V,  $C_{LOAD}$  = 50pF to GND,  $R_{LOADP}$  =  $R_{LOADN}$  = 1k $\Omega$  to GND,  $R_{GAIN}$  = 510 $\Omega$  (Nominal Gain), -20°C  $\leq T_A \leq$  +85°C, Output measured differentially.

| PARAMETER                                               | CONDITIONS                                                       | MIN     | TYP   | MAX     | UNITS |

|---------------------------------------------------------|------------------------------------------------------------------|---------|-------|---------|-------|

| Supply Voltage                                          |                                                                  | 4.5     | 5     | 5.5     | V     |

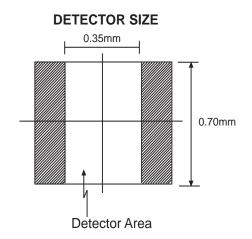

| Output Sensitivity                                      | Laser Beam Diameter = 0.70mm, uniform density                    | 2400    | 3000  | 3600    | V/W   |

| Output Sensitivity vs. Temp                             | R <sub>GAIN</sub> =1230Ω                                         |         |       | 0.1     | %/C   |

| Output Sensitivity vs. Vcc                              | R <sub>GAIN</sub> =1230Ω                                         |         |       | 2       | %/V   |

| Input Optical Power Required to Produce 2V Output Swing |                                                                  | 533     | 666   | 800     | μW    |

| Full Scale Linear Output<br>Voltage Swing               |                                                                  | 2       | 2.8   |         | V     |

| Output Common Mode Voltage                              |                                                                  | 2.3     | 2.5   | 2.7     | V     |

|                                                         | 4.5V < Vcc < 5.5V                                                | Vcc/2.2 | Vcc/2 | Vcc/1.8 | V     |

| Output Offset Voltage                                   |                                                                  | -10     | 0.5   | 10      | mV    |

|                                                         | $R_{GAIN} = 1230\Omega$ (High Gain)                              | -20     | 1.0   | 20      | mV    |

| Output Offset Voltage Drift                             |                                                                  | -25     | -11   | 25      | μV/C  |

|                                                         | $R_{GAIN} = 1230\Omega$ (High Gain)                              | -50     | -13   | 50      | μV/C  |

| Output Noise                                            | BW = 100MHz                                                      |         | 1.6   | 2       | mVrms |

|                                                         | $BW = 100 MHz, \\ R_{GAIN} = 1230 \Omega \text{ (High Gain)}$    |         | 2.4   | 5       | mVrms |

| Bandwidth                                               | -3dB                                                             | 70      | 100   |         | MHz   |

|                                                         | -3dB, R <sub>GAIN</sub> = 1230Ω (High Gain)                      | 50      | 68    |         | MHz   |

| PSRR                                                    | 4.5V < Vcc < 5.5V                                                | 55      | 76    |         | dB    |

|                                                         | 4.5V < Vcc < 5.5V,<br>$R_{GAIN} = 1230\Omega$ (High Gain)        | 50      | 73    |         | dB    |

| Output Settling Time(650nm)                             | 2V <sub>PP</sub> Step                                            |         | 7     | 10      | ns    |

| (1% of Final Value)                                     | $2V_{PP}$ Step,<br>R <sub>GAIN</sub> = 1230 $\Omega$ (High Gain) |         | 12    | 15      | ns    |

Rev:A Date: 3/18/04

SP8126B High Speed Differential APC Amplifier

© Copyright 2004 Sipex Corporation

## ELECTRICAL SPECIFICATIONS: Continued

Unless otherwise noted:  $V_{CC} = 5.0V$ ,  $C_{LOAD} = 50pF$  to GND,  $R_{LOADP} = R_{LOADN} = 1k\Omega$  to GND,  $R_{GAIN} = 510\Omega$  (Nominal Gain),  $-20^{\circ}C \le T_{A} \le +85^{\circ}C$ , Output measured differentially.

| PARAMETER                                    | CONDITIONS                                                       | MIN | TYP | MAX | UNITS |

|----------------------------------------------|------------------------------------------------------------------|-----|-----|-----|-------|

| Output Settling Time (780nm)                 | 2V <sub>PP</sub> Step                                            |     | 10  | 13  | ns    |

| (1% of Final Value)                          | $2V_{PP}$ Step,<br>R <sub>GAIN</sub> = 1230 $\Omega$ (High Gain) |     | 15  | 18  | ns    |

| Output Slew Rate                             |                                                                  | 200 | 300 |     | V/µs  |

| Output Overshoot                             | 2V <sub>PP</sub> Step                                            |     |     | 5   | %     |

| Power Supply Current                         |                                                                  |     | 15  |     | mA    |

|                                              | -20°C < T <sub>A</sub> < +85°C                                   |     |     | 20  | mA    |

| Gain Adjust Range                            | $225\Omega < R_{GAIN} < 1230\Omega$                              | -6  |     | 6   | dB    |

| Gain Select Input Voltage<br>VIL (TTL Level) |                                                                  |     |     | 0.8 | V     |

| Gain Select Input Voltage<br>VIH (TTL Level) |                                                                  | 2.0 |     |     | V     |

#### PIN DESCRIPTION

| PIN NUMBER | NAME               | FUNCTION                                                                |

|------------|--------------------|-------------------------------------------------------------------------|

| 1          | V <sub>CC</sub>    | Supply Voltage                                                          |

| 2          | GAIN               | Gain Select                                                             |

| 3          | R <sub>GCOM</sub>  | Common connection point for R <sub>GAIN</sub> 1 and R <sub>GAIN</sub> 2 |

| 4          | GND                | Power Ground                                                            |

| 5          | R <sub>GAIN1</sub> | Gain Adjust 1 (Gain Select = LOW) or OPEN                               |

| 6          | R <sub>GAIN2</sub> | Gain Adjust 2 (Gain Select = HIGH)                                      |

| 7          | V <sub>OUT</sub> - | Output Voltage -                                                        |

| 8          | V <sub>OUT</sub> + | Output Voltage +                                                        |

#### THEORY OF OPERATION

## **Internal Operation**

The SP8126B APC circuit has an integrated photo detector and is designed with nominal sensitivities of  $3\text{mV}/\mu\text{W}$  for both 650nm and 780nm wavelength laser light. The part's sensitivity can also be adjusted continuously and independently for two different gain modes via two external resistors over a range of  $\pm 6\text{dB}$ . The two gain modes are controlled by a TTL compatible logic input, called GAIN SELECT. This logic pin selects between the two external gain setting resistors to allow independent control and settings for the two gain functions.

The system is a two stage design, consisting of a Trans-Impedance Amplifier (TIA) and an output buffer stage. In dark condition the outputs  $V_{OUT}$ - and  $V_{OUT}$ + are set to a reference voltage

that is defined internally as Vcc/2. With 650nm or 780nm wavelength laser light falling on the photodetector, the output will swing differentially around Vcc/2 proportional with the light power according to the chosen gain.

## **TIA and Gain control**

The first stage is a differential TIA used to convert the photodetector current to a balanced differential voltage. The traditional fixed feedback resistors have been replaced with an active resistor circuit that sets the trans-impedance value.

A Resistor Control Block that senses the value of the external gain setting resistor controls the value of the equivalent feedback resistor.

Rev:B Date: 3/18/04

SP8126B High Speed Differential APC Amplifier

© Copyright 2004 Sipex Corporation

The ±6dB Gain adjustment is therefore done directly in the TIA, by adjusting the active feedback blocks proportional with the gain setting resistor. The external resistor is not directly in the signal path, and therefore any parasitic from the off-chip connections does not affect the signal quality. The value of the active feedback is controlled tightly over supply and temperature changes through a Control Block with active feedback circuitry.

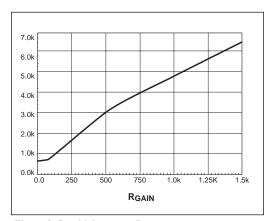

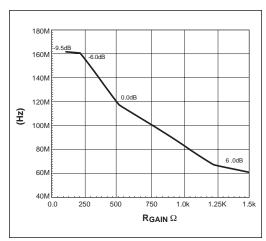

Gain control is proportional with the external resistor, so the lowest value of  $R_{GAIN}$  will produce the -6dB gain adjustment and the highest value will produce the +6dB gain adjustment. Please consult the specification table for the required  $R_{GAIN}$  values.

#### **Buffer**

This stage buffers the differential signal from the TIA to the  $V_{OUT}$  pins and refers the signal to the internal reference voltage. A balanced current feedback amplifier is used for this purpose to achieve high slew rate and fast settling.

The buffer is designed to drive high capacitive loads. The maximum load is 50pF bulk. The actual load is typically a flexible printed circuit (FPC) that acts like a transmission line. This presents a distributed capacitive load plus inductance and resistance. In this case care should be taken to match the characteristic impedance of the line at the far end to avoid standing waves and ringing. The buffer is designed to drive  $1k\Omega$  to ground. However, this resistor can be adjusted in value to accommodate the characteristic impedance of the signal trace. The output buffer amplifier is designed to be stable without load and with loads up to 50pF lumped capacitance.

Figure 2. Sensitivity versus R<sub>GAIN</sub>

Figure 3. Bandwidth versus R<sub>GAIN</sub>

# **TABLE 1: APC SYSTEM TARGET GAIN SET POINTS.**

$V_{OUTP}-V_{OUTN} = 2V_{P-P}, V_{CC} = 5V, T = 27^{\circ}C$

| Gain<br>(dB) | Sensitivity<br>(V/W) | $R_{GAIN}$ ( $\Omega$ ) | Ts 1%<br>(nS) | BW<br>(MHz) | Pin<br>(μW) |

|--------------|----------------------|-------------------------|---------------|-------------|-------------|

| +6           | 6000                 | 1230                    | 12            | 68          | 335         |

| 0            | 3000                 | 510                     | 7             | 119         | 666         |

| -6           | 1500                 | 225                     | 5.5           | 160         | 1331        |

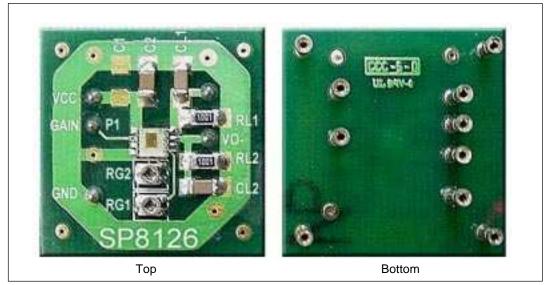

## LAYOUT AND ROUTING CONSIDERATIONS

A major consideration in developing the optical pick-up head system is the extremely small form factor, which is additionally aggravated by the physical locations required by the light path.

Special care must be taken when designing the Flex or PCB for this part. The output peak current requirement is in the order of 12.5mA when driving 50pF of capacitive load with a slew rate of 250V/ $\mu$ s Therefore care must be taken to provide low inductance, low resistance paths for power and ground and output traces.

Supply coupling is also very important. Good supply decoupling is important to ensure the high frequency performance of the system by eliminating supply lead inductance effects. The decoupling capacitor C1, as shown in Figure 5, should be as close to the part as possible. This

capacitor should be  $0.1\mu F$  ceramic. C2 is optional to improve decoupling and is recommended to be  $1\mu F$  tantalum. The layout of the PCB is pictured here. Note the wide and short traces on the supply lines.

The traces for the gain resistors  $R_{\rm GAIN1}$  and  $R_{\rm GAIN2}$  are kept as short as possible to avoid excessive parasitics. Any parasitics on these nodes will limit the performance of the system.  $R_{\rm GAIN1}$  and  $R_{\rm GAIN2}$  are subminiature potentiometers in the application. This is a single layer board using FR4 material.

In order to minimize coupling capacitance into the gain setting resistor nodes, it is also critical that  $V_{OUT}$ + and  $V_{OUT}$ - are routed away from the traces associated with the gain-setting resistors.

Figure 4. Test and Evaluation PCB Layout for COB 8 Lead Package

Figure 5. Test and Evaluation Schematic

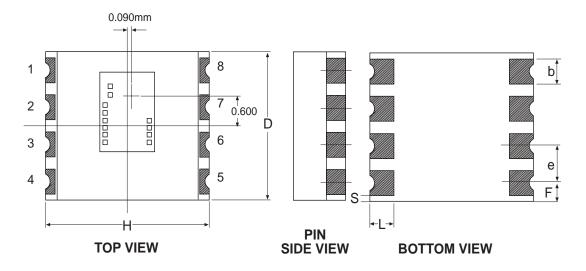

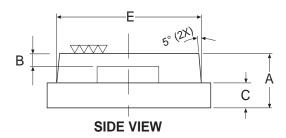

| DIMENSIONS in |             |

|---------------|-------------|

| mm            | 8-PIN       |

| Min/Max       | СОВ         |

| A             |             |

|               | 0.90/1.10   |

| В             | 0.127/0.33  |

| b             | 0.30/0.50   |

| С             | 0.50 nom    |

| D             | 2.90/3.10   |

| E             | 3.00/3.20   |

| e             | 0.75 nom    |

| Н             | 3.40/3.60   |

| L             | 0.40/0.60   |

| F             | 0.28/0.48   |

| S             | 0.075/0.275 |

8 PIN COB (3.0mm X 3.5mm)

| ORDERING INFORMATION |                      |                       |  |

|----------------------|----------------------|-----------------------|--|

| Part Number          | Temperature Range    | Package Type          |  |

| SP8126CB-3           | 20°C to +85°C 8 lead | I COB (3.0mm x 3.5mm) |  |

# ANALOG EXCELLENCE

Sipex Corporation

Headquarters and Sales Office 233 South Hillview Drive Milpitas, CA 95035 TEL: (408) 934-7500 FAX: (408) 935-7600

Sales Office 22 Linnell Circle Billerica, MA 01821 TEL: (978) 667-8700 FAX: (978) 670-9001 e-mail: sales@sipex.com

Sipex Corporation reserves the right to make changes to any products described herein. Sipex does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.