### **DATA SHEET**

**MARCH 2008**

#### **GENERAL DESCRIPTION**

The 71M6515H is a high-accuracy analog front end (AFE) IC that provides measurements for four-quadrant 3-phase metering. The combination of a 21-bit sigma-delta A/D converter with a six-input analog front end, a thermally compensated high precision reference and a compute engine results in high accuracy and wide dynamic range. Patented Single-Converter Technology™ reduces cross talk and cost. This IC also provides RTC and battery backup for time-of-use (TOU) metering.

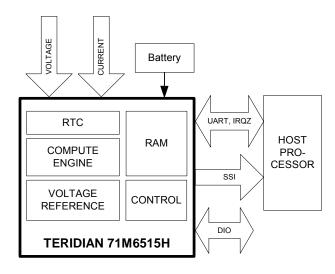

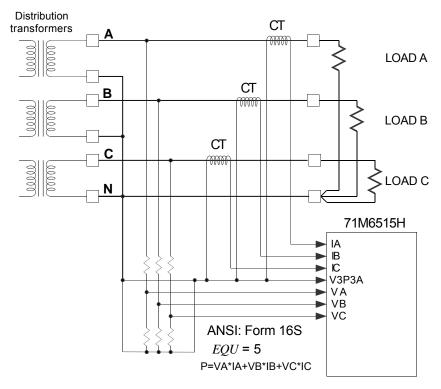

Figure 1: Meter block diagram

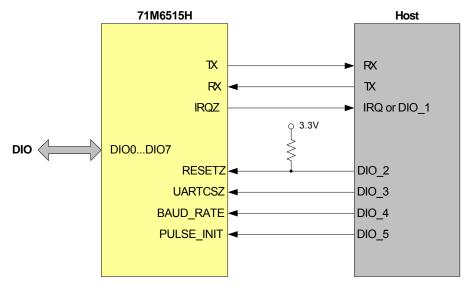

As shown in the block diagram (Figure 1), the host processor communicates with the 71M6515H through a UART interface using the programmable IRQZ interrupt. The 71M6515H calculates and accumulates meter measurements for each accumulation interval. A high-speed synchronous serial port (SSI) is provided to facilitate high-end metering. Integrated rectifying functions on the battery backup circuit enable minimal external component usage and minimum back-up current. Also, eight multi-purpose pins are provided for control of peripherals.

#### **FEATURES**

#### **High Accuracy**

- < 0.1% Wh accuracy over temperature and 2000:1 range

- Exceeds IEC62053/ANSIC12.20 specifications.

- Precision ultra-stable voltage reference (10PPM/°C)

- Single Converter Technology™ reduces cross talk and power consumption

- Six sensor inputs—referenced to V3P3

- Compatible with CTs, resistive shunts and Rogowski Coil sensors

- -90dB THD max.

- Digital temperature compensation

- Sag detection

- Measures Wh, VARh, VAh, Vrms, Irms, V-to-V phase and load angle on each phase

- Four-quadrant metering.

- Four low-jitter pulse outputs from selectable measurements

- Four pulse count registers

- Selectable default status for pulse pins

- Same calibration data for 46Hz to 64Hz line frequency

- Broad CT phase compensation (±7deg)

#### **Battery Backup**

- Protects accumulated data and powers real time clock during power supply outage

- · Compatible with Li-ion, NiCd, or super-capacitor

- Battery backup current 2µA typical at 25°C

#### **External Data Interface**

- UART Control Interface, two selectable data rates

- 8 general-purpose I/O pins with alarm capability

- 5 or 10MHz selectable high speed synchronous serial output for DSP interface

- IRQ output signal for alarms and end of measurement intervals.

- Alarms on voltage sag, over-voltage, over-current

#### **Low System Cost**

- Power Consumption 30mW @ 3.3V typical

- Real-time clock with temperature compensation

- Built-in power fault detection

- Single 32kHz crystal time base

- Single-supply operation (3.3V)

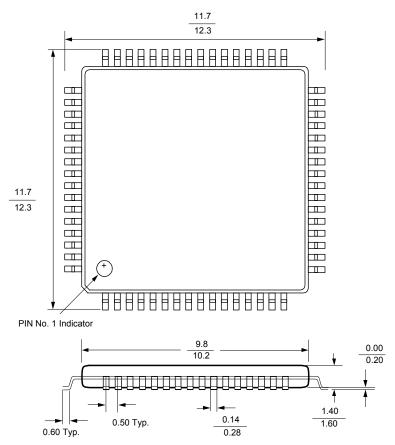

- 64-lead LQFP package

### **DATA SHEET**

**MARCH 2008**

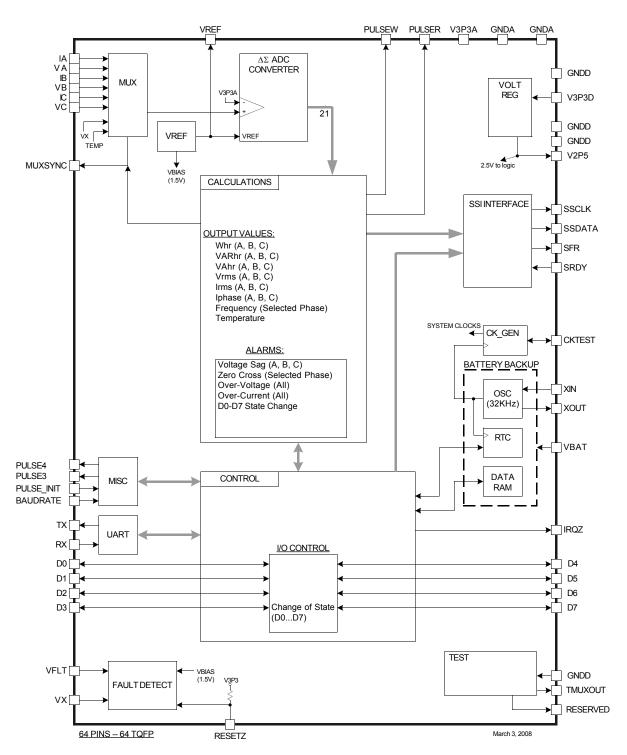

Figure 2: IC Functional Block Diagram

### **DATA SHEET**

**MARCH 2008**

#### **ELECTRICAL SPECIFICATIONS**

#### **ABSOLUTE MAXIMUM RATINGS**

| Supplies and Ground Pins:                    |                                     |

|----------------------------------------------|-------------------------------------|

| V3P3D, V3P3A                                 | −0.5V to 4.6V                       |

| V3P3D – V3P3A                                | 0V to 0.5V                          |

| VBAT                                         | -0.5V to 4.6V                       |

| GNDD                                         | -0.5V to +0.5V                      |

| Analog Output Pins:                          |                                     |

| VREF                                         | -1mA to 1mA,<br>-0.5V to V3P3A+0.5V |

| V2P5                                         | -1mA to 1mA,<br>-0.5 to 3.0V        |

| Analog Input Pins:                           | <u>.</u>                            |

| IA, VA, IB, VB, IC, VC                       | -0.5V to V3P3A+1.0V                 |

| VFLT, VX                                     | -0.5V to V3P3A+0.5V                 |

| XIN, XOUT                                    | -0.5V to 3.0V                       |

| Digital Input Pins:                          |                                     |

| RX                                           | -0.5V to 3.6V                       |

| D0D7                                         | -0.5V to 6V                         |

| All other pins                               | -0.5V to V3P3D+0.5V                 |

| Operating junction temperature (peak, 100ms) | 140 °C                              |

| Operating junction temperature (continuous)  | 125 °C                              |

| Storage temperature                          | −45 °C to 165 °C                    |

| Solder temperature – 10 second duration      | 250 °C                              |

| ESD Stress                                   |                                     |

| Pins IA, VA, IB, VB, IC, VC, RX, TX          | 6kV                                 |

| All other pins                               | 2kV                                 |

Stresses beyond Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. All voltages are with respect to GNDA.

#### **RECOMMENDED OPERATING CONDITIONS**

| PARAMETER                                       | CONDITION        | MIN  | TYP                         | MAX | UNIT |  |

|-------------------------------------------------|------------------|------|-----------------------------|-----|------|--|

| 3.3V Supply Voltage (V3P3A, V3P3D) <sup>+</sup> | Normal Operation | 3.0  | 3.3                         | 3.6 | V    |  |

|                                                 | Battery Backup   | 0    |                             | 3.8 | V    |  |

| VBAT                                            | No Battery       | Exte | Externally Connect to V3P3D |     |      |  |

| VBAT                                            | Battery Backup   | 2.0  |                             | 3.8 | V    |  |

| Operating Temperature                           |                  | -40  |                             | 85  | °C   |  |

V3P3A and V3P3D should be shorted together on the circuit board. GNDD and GNDA should also be shorted on the circuit board.

## **DATA SHEET**

MARCH 2008

#### **LOGIC LEVELS**

| PARAMETER                                                                          | CONDITION                | MIN                  | TYP | MAX                     | UNIT                  |

|------------------------------------------------------------------------------------|--------------------------|----------------------|-----|-------------------------|-----------------------|

| Digital high-level input voltage, V <sub>IH</sub>                                  |                          | 2                    |     | V3P3D                   | V                     |

| Digital low-level input voltage, V <sub>IL</sub>                                   |                          | -0.3                 |     | 0.8                     | V                     |

| District binds level automaturally and M                                           | I <sub>LOAD</sub> = 1mA  | V3P3D<br>-0.4        |     | V3P3D                   | V                     |

| Digital high-level output voltage V <sub>OH</sub>                                  | I <sub>LOAD</sub> = 15mA | V3P3D-<br>0.6        |     |                         | V                     |

| Digital low-level output voltage V <sub>OL</sub>                                   | $I_{LOAD} = 1mA$         | 0                    |     | 0.4                     | V                     |

| Digital low-level output voltage V <sub>OL</sub>                                   | $I_{LOAD} = 15mA$        |                      |     | 0.8                     | V                     |

| Input pull-up current, IIL RESETZ E_RXTX, E_ISYNC/BRKRQ E_RST Other digital inputs | VIN=0V                   | 10<br>10<br>10<br>-1 |     | 100<br>100<br>100<br>+1 | Д<br>Д<br>Д<br>Д<br>Д |

| Input pull down current, Іін<br>TEST<br>Other digital inputs                       | VIN=V3P3D                | 10<br>-1             |     | 100<br>+1               | μΑ<br>μΑ              |

#### **SUPPLY CURRENT**

| PARAMETER     | CONDITION                                               | MIN  | TYP | MAX  | UNIT |

|---------------|---------------------------------------------------------|------|-----|------|------|

| V3P3A + V3P3D | Normal Operation,                                       |      | 8.8 | 11.5 | mA   |

| V3P3A current | V3P3A=V3P3D=3.3V                                        |      | 3.7 | 4.7  | mA   |

| V3P3D current | VBAT=3.6V                                               |      | 5.1 | 6.8  | mA   |

| VBAT current  |                                                         | -300 |     | 300  | nA   |

| VBAT current, | Battery backup, ≤25°C                                   |      | 2   | 4    | μA   |

| VBAT=3.6V     | <b>V3P3A=V3P3D=</b> 0V<br>f <sub>OSC</sub> = 32kHz 85°C |      | 4   | 12   | μΑ   |

#### **VREF**

| PARAMETER                                                                                                                  | CONDITION                      | MIN                                             | TYP   | MAX   | UNIT     |

|----------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------------------------------------|-------|-------|----------|

| VREF output voltage, VNOM(25)                                                                                              | Ta = 25°C                      | 1.193                                           | 1.195 | 1.197 | V        |

| VREF output impedance                                                                                                      | ILOAD = $10\mu A$ , $-10\mu A$ |                                                 |       | 2.5   | kΩ       |

| VNOM definition A                                                                                                          | VNOM(T) = VREF(22)             | $VNOM(T) = VREF(22) + (T-22)TC1 + (T-22)^2T(4)$ |       |       |          |

| $\frac{\textit{VREF(T)} \text{ deviation from VNOM(T)}}{\textit{VREF(T)} - \textit{VNOM(T)}} \frac{10^6}{\max( T-22 ,40)}$ | Ta = -40°C to +85°C            | -10                                             |       | +10   | PPM/°C   |

| VREF aging                                                                                                                 |                                |                                                 | ±25   |       | PPM/year |

## **DATA SHEET**

MARCH 2008

#### 2.5V VOLTAGE REGULATOR

| PARAME    | TER                 | CONDITION                             | MIN | TYP | MAX | UNIT |

|-----------|---------------------|---------------------------------------|-----|-----|-----|------|

| Voltage C | overhead V3P3D-V2P5 | Reduce V3P3 until V2P5<br>drops 200mV |     |     | 440 | mV   |

| PSRR      | ∆V2P5/∆V3P3D        | RESETZ=1, ILOAD=0                     | -3  |     | +3  | mV/V |

#### RTC

| PARAMETER      | CONDITION | MIN  | TYP | MAX  | UNIT |

|----------------|-----------|------|-----|------|------|

| Range for date |           | 2000 |     | 2255 | year |

#### **RESETZ**

| PARAMETER             | CONDITION | MIN | TYP | MAX | UNIT |

|-----------------------|-----------|-----|-----|-----|------|

| Reset pulse width     |           | 5   |     |     | μs   |

| Reset pulse fall time |           |     |     | 1   | μs   |

#### **CRYSTAL OSCILLATOR**

| PARAMETER                                    | CONDITION | MIN | TYP | MAX | UNIT |

|----------------------------------------------|-----------|-----|-----|-----|------|

| Maximum Output Power to Crystal <sup>4</sup> |           |     |     | 1   | μW   |

| Xin to Xout Capacitance                      |           |     |     | 3   | pF   |

| Capacitance to DGND                          |           |     |     |     |      |

| Xin                                          |           |     |     | 5   | pF   |

| Xout                                         |           |     |     | 5   | pF   |

| Watchdog RTC_OK threshold                    |           |     |     | 25  | kHz  |

#### **TEMPERATURE SENSOR**

| PARAMETER                                                       | CONDITION                                 | MIN       | TYP        | MAX | UNIT   |

|-----------------------------------------------------------------|-------------------------------------------|-----------|------------|-----|--------|

| Nominal Sensitivity (S <sub>n</sub> ) <sup>4</sup>              | TA=25°C, TA=75°C                          |           | -900       |     | LSB/°C |

| Nominal Offset (N <sub>n</sub> ) <sup>4</sup>                   | Nominal relationship:<br>$N(T)=S_n*T+N_n$ |           | 40000<br>0 |     | LSB    |

| Temperature Error $ERR = (T - 25) - \frac{(N(T) - N(25))}{S_n}$ | TA = -40°C to +85°C                       | <b></b> 9 |            | +3  | °C     |

#### **PULSE GENERATOR TIMING SPECIFICATIONS**

| PARAMETER                   | CONDITION                                              | MIN | TYP | MAX  | UNIT |

|-----------------------------|--------------------------------------------------------|-----|-----|------|------|

| PULSEW, PULSER maximum rate | APULSE=2 <sup>31</sup> -1,<br>WRATE=2 <sup>15</sup> -1 |     |     | 7.56 | kHz  |

| PULSE3, PULSE4 maximum rate | PULSE3=2 <sup>31</sup> -1,<br>WRATE=2 <sup>15</sup> -1 |     |     | 0.15 | kHz  |

| Pulse count frequency       | all pulse outputs                                      |     |     | 0.15 | kHz  |

### **DATA SHEET**

MARCH 2008

#### THERMAL CHARACTERISTICS

| PARAMETER                                                  | CONDITION                                 | VALUE | UNIT |

|------------------------------------------------------------|-------------------------------------------|-------|------|

| Thermal resistance, junction to ambient (R $\theta_{JA}$ ) | Air velocity 0 m/s. Part soldered to PCB. | 63.7  | °C/W |

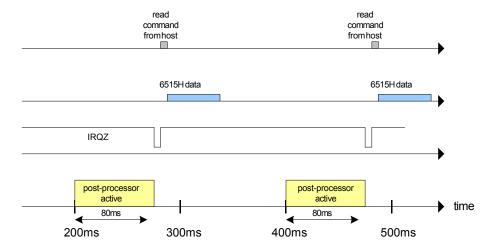

#### **UART HOST INTERFACE**

| PARAMETER                                                           | CONDITION                                    | MIN  | TYP    | MAX  | UNIT  |

|---------------------------------------------------------------------|----------------------------------------------|------|--------|------|-------|

| Baud Rate                                                           |                                              | 19.2 | -      | 38.4 | kBaud |

| Character set                                                       |                                              |      | binary |      |       |

| Data Format                                                         |                                              |      | 8N1    |      |       |

| Byte-to-byte delay (6515H times out after maximum delay)            | Host sending data to 6515H                   | 10   |        | 20   | ms    |

| Byte-to-byte delay                                                  | 6515H sending data to host                   | 0    |        | 0.1  | ms    |

| Response time to read command                                       | 6515H has data ready                         | 0.5  |        | 2    | ms    |

| Response time to read command when 71M6515H is post-processing data | Data not ready  CE_ONLY = 1  CE_ONLY = 0 and |      |        | 40   | ms    |

| · ····································                              | <i>VAH_SELECT</i> = 0 <i>CE_ONLY</i> = 0 and |      |        | 80   | ms    |

|                                                                     | $VAH\_SELECT = 1$                            |      |        | 350  | ms    |

#### ADC CONVERTER, V3P3 REFERENCED

| PARAMETER                                                                                                               | CONDITION                                               | MIN  | TYP     | MAX | UNIT       |

|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------|---------|-----|------------|

| Usable Input Range (Vin-V3P3A)                                                                                          |                                                         | -250 |         | 250 | mV<br>peak |

| Voltage to Current cross talk:                                                                                          | Vin = 200mV peak, 65Hz, on VA, VB, or VC                |      |         |     |            |

| $\frac{10^6 * Vcrosstalk}{Vin} \cos(\angle Vin - \angle Vcrosstalk)$                                                    | Vcrosstalk = largest<br>measurement on IA, IB, or<br>IC | -10  |         | +10 | μV/V       |

| THD (First 10 harmonics)                                                                                                | Vin=65Hz,                                               |      |         |     |            |

| 250mV-pk                                                                                                                | 64kpts FFT, Blackman-                                   |      |         | -75 | dB         |

| 20mV-pk                                                                                                                 | Harris window                                           |      |         | -90 | dB         |

| Input Impedance                                                                                                         | Vin=65Hz                                                | 40   |         | 90  | kΩ         |

| Temperature Coefficient of Input Impedance                                                                              | Vin=65Hz                                                |      | 1.7     |     | Ω/°C       |

| LSB size                                                                                                                |                                                         |      | 355     |     | nV/LSB     |

| Digital Full Scale                                                                                                      |                                                         |      | +884736 |     | LSB        |

| ADC Gain Error vs. %Power Supply Variation $\frac{10^6  \Delta Nout_{PK}  357 nV  / V_{IN}}{100  \Delta V  3P3A / 3.3}$ | Vin=200mV pk, 65Hz<br>V3P3A=3.0V, 3.6V                  |      |         | 50  | PPM/<br>%  |

| Input Offset (Vin-V3P3A)                                                                                                |                                                         | -10  |         | +10 | mV         |

### **DATA SHEET**

**MARCH 2008**

#### RECOMMENDED EXTERNAL COMPONENTS

| NAME | FROM  | TO   | FUNCTION                                                                                                     | VALUE    | UNIT |

|------|-------|------|--------------------------------------------------------------------------------------------------------------|----------|------|

| C1   | V3P3A | AGND | Bypass capacitor for 3.3V supply                                                                             | ≥0.1±20% | μF   |

| C2   | V3P3D | DGND | Bypass capacitor for 3.3V supply                                                                             | ≥0.1±20% | μF   |

| XTAL | XIN   | XOUT | XOUT  32.768kHz crystal – electrically similar to ECS .327-12.5-17X or Vishay XT26T, load capacitance 12.5pF |          | kHz  |

| CXS  | XIN   | AGND | GND Load capacitor for crystal (depends on crystal                                                           |          | pF   |

| CXL  | XOUT  | AGND | specs and board parasitics).                                                                                 | 27±10%   | рF   |

| C2P5 | V2P5  | DGND | Bypass capacitor for V2P5                                                                                    | ≥0.1±20% | μF   |

#### **FOOTNOTES:**

- 1 This spec is guaranteed, has been verified in production samples, but is not measured in production.

- 2 This spec is guaranteed, has been verified in production samples, but is measured in production only at DC.

- 3 This spec is measured in production at the limits of the specified operating temperature.

- 4 This spec defines a nominal relationship rather than a measured parameter. Correct circuit operation is verified with other specs that use this nominal relationship as a reference

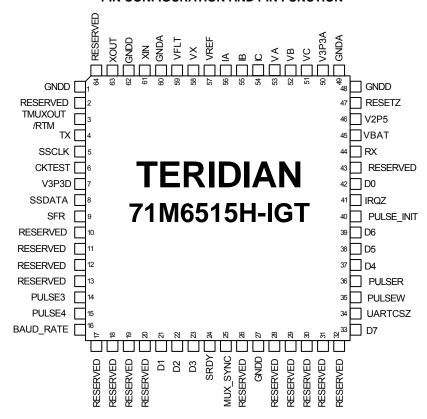

#### PIN CONFIGURATION AND PIN FUNCTION

Pins marked RESERVED should be left unconnected during normal use.

### **DATA SHEET**

MARCH 2008

#### **Analog Pin Description**

| Name             | Pin<br>No.     | Туре | Circuit | Description                                                                                                                                                                                                                |

|------------------|----------------|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IA,<br>IB,<br>IC | 56<br>55<br>54 | I    | 6       | Line Current Sense Inputs: Voltage inputs to the internal A/D converter. Typically, they are connected to the output of a current transformer. The input is referenced to V3P3A. <b>Unused pins must be tied to V3P3A.</b> |

| VA,<br>VB,<br>VC | 53<br>52<br>51 | I    | 6       | Line Voltage Sense Inputs: Voltage inputs to the internal A/D converter. Typically, they are connected to the output of a resistor divider. The input is referenced to V3P3A. Unused pins must be tied to V3P3A.           |

| VFLT             | 59             | ı    | 7       | Power Fault Input. This pin must be tied to V3P3A.                                                                                                                                                                         |

| VX               | 58             | I    | 6       | Auxiliary input (not used). This pin should be tied to VREF.                                                                                                                                                               |

| VREF             | 57             | I/O  | 9       | Voltage Reference for the ADC.                                                                                                                                                                                             |

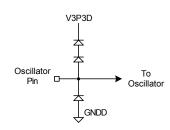

| XIN,<br>XOUT     | 61<br>63       | I    | 8       | Crystal Inputs: A 32768Hz crystal should be connected across these pins. Typically, a 15pF capacitor is also connected from each pin to GNDA. See the datasheet of the crystal manufacturer for details.                   |

Pin types: P = Power, O = Output, I = Input, I/O = Input/Output

The circuit number denotes the equivalent circuit, as specified under "I/O Equivalent Circuits".

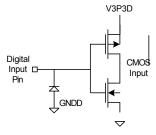

#### **Digital Pin Description**

Unless otherwise indicated, all inputs and outputs are standard CMOS. Inputs do NOT have internal pull-ups or pull-downs.

| Name                                         | Pin<br>No.                                   | Туре | Circuit | Description                                                                                                                                                                                                                                                      |  |

|----------------------------------------------|----------------------------------------------|------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CKTEST                                       | 6                                            | I/O  | 4       | Clock PLL output. Can be enabled and disabled by <i>CKOUT_DSB</i> (see Status Mask).                                                                                                                                                                             |  |

| D0<br>D1<br>D2<br>D3<br>D4<br>D5<br>D6<br>D7 | 42<br>21<br>22<br>23<br>37<br>38<br>39<br>33 | I/O  | 3, 4    | Input/output pins 0 through 7. These pins must be terminated to V3P3D or ground if configured as input pins.  D0 through D7 float after reset or power-up and are configured outputs and driven low 140ms after RESETZ goes high.                                |  |

| PULSE4                                       | 15                                           | 0    | 4       | The fourth pulse generator output                                                                                                                                                                                                                                |  |

| PULSE3                                       | 14                                           | 0    | 4       | The third pulse generator output                                                                                                                                                                                                                                 |  |

| PULSE_INIT                                   | 40                                           | I    | 3       | The pulse output initial power-up voltage (0: 0V, 1: 3.3V), default is 1.  This pin must be terminated to V3P3D or ground.                                                                                                                                       |  |

| BAUD_RATE                                    | 16                                           | I    | 3       | The UART baud rate (1: 38.4kbd, 0: 19.2kbd). This pin must be terminated to V3P3D or ground.                                                                                                                                                                     |  |

| IRQZ                                         | 41                                           | 0    | 4       | Interrupt output, low active. A falling edge indicates the end of a measurement frame, as well as alarms. Rises when status word is read.                                                                                                                        |  |

| MUXSYNC                                      | 25                                           | 0    | 4       | Internal signal. MUXSYNC falls at the beginning of each conversion cycle (multiplexer frame).                                                                                                                                                                    |  |

| RESETZ                                       | 47                                           | I    | 1       | Chip reset: Input pin with internal pull-up resistor, used to reset the into a known state. For normal operation, this pin is set to 1. To res the chip, this pin is driven to 0 for 5 microseconds. No external rese circuitry is necessary for power-up reset. |  |

### **DATA SHEET**

| Name    | Pin<br>No. | Туре | Circuit | Description                                                                                                                                                              |  |  |

|---------|------------|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| UARTCSZ | 34         | I    | 3       | Enables the UART when 0. The UART is disabled when this pin is set to 1. A positive pulse on this pin will reset the UART. <b>This pin must be terminated to ground.</b> |  |  |

|         |            |      |         | High-Speed Synchronous Interface (SSI).                                                                                                                                  |  |  |

| SRDY    | 24         | I    | 3       | The SRDY input should be tied to ground.                                                                                                                                 |  |  |

| SFR     | 9          | 0    | 4       | SSI frame pulse output, one SSCLK wide.                                                                                                                                  |  |  |

| SSCLK   | 5          | 0    | 4       | SSI clock output (5MHz or 10MHz selectable).                                                                                                                             |  |  |

| SSDATA  | 8          | 0    | 4       | SSI data output, changes on the rising edge of SSCLK.                                                                                                                    |  |  |

| RX      | 44         | I    | 3       | UART serial Interface receiver input. The voltage at this pin must not exceed 3.6V. This pin must be terminated to V3P3D or ground.                                      |  |  |

| TX      | 4          | 0    | 4       | UART serial Interface transmitter output.                                                                                                                                |  |  |

| TMUXOUT | 3          | 0    | 4       | Digital output test multiplexer. Controlled by TMUX[2:0].                                                                                                                |  |  |

| PULSER  | 36         | 0    | 4       | Selectable pulse output (default: VARh pulse).                                                                                                                           |  |  |

| PULSEW  | 35         | 0    | 4       | Selectable pulse output (default: Wh pulse).                                                                                                                             |  |  |

#### **Power/Ground Pin Description**

| Name  | Pin No.        | Туре | Description                                                                                                                                       |

|-------|----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| GNDA  | 49,60          | Р    | Analog ground: This pin should be connected directly to the ground plane.                                                                         |

| GNDD  | 1,27,<br>48,62 | Р    | Digital ground: These pins must be connected directly to the ground plane.                                                                        |

| V3P3A | 50             | Р    | Analog power: A 3.3V analog power supply should be connected to this pin.                                                                         |

| V3P3D | 7              | Р    | Digital power supply: A 3.3V digital power supply should be connected to this pin.                                                                |

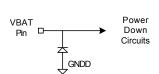

| VBAT  | 45             | Р    | Battery backup power supply. A battery or super-capacitor is to be connected between VBAT and GNDD. If no battery is used, connect VBAT to V3P3D. |

| V2P5  | 46             | 0    | Output of the 2.5V regulator. A 0.1µF capacitor should be connected from this pin to GND.                                                         |

Pin types: P = Power, O = Output, I = Input, I/O = Input/Output The circuit number denotes the equivalent circuit, as specified under "I/O Equivalent Circuits".

#### **Reserved Pins**

Pins labeled RESERVED are not to be connected.

| Name     | Pin No.                                                           | Description                |

|----------|-------------------------------------------------------------------|----------------------------|

| RESERVED | 2,10,11,12,<br>13,17,18,19,<br>20,26,28,29,<br>30,31,32,43,<br>64 | DO NOT CONNECT THESE PINS! |

### **DATA SHEET**

**MARCH 2008**

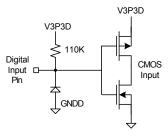

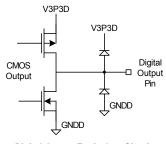

#### **I/O Equivalent Circuits**

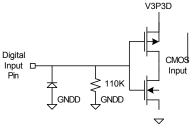

#### **Digital Input Equivalent Circuit** Type 1:

Standard Digital Input or pin configured as DIO Input with Internal Pull-Up

**Analog Input Equivalent Circuit**

Type 6:

V2P5 Equivalent Circuit Type 10:

**Digital Input**

Type 2: Pin configured as DIO Input with Internal Pull-Down

Comparator Input Equivalent Circuit Type 7: Comparator Input

VBAT Equivalent Circuit Type 12:

**Digital Input Type 3:** Standard Digital Input or pin configured as DIO Input

Oscillator Equivalent Circuit Type 8:

**Digital Output Equivalent Circuit** Type 4:

Standard Digital Output or pin configured as DIO Output

**VREF Equivalent Circuit** Type 9: VRFF

**MARCH 2008**

#### TYPICAL PERFORMANCE CHARACTERISTICS

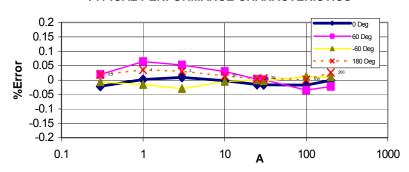

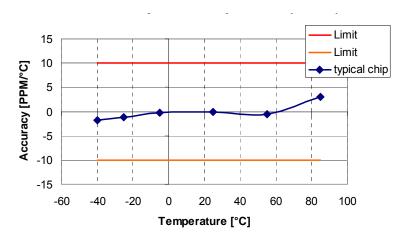

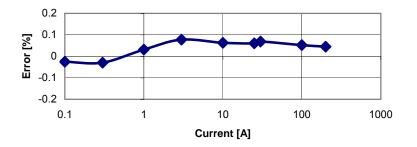

Figure 3: Wh Accuracy, 0.3A - 200A/240V

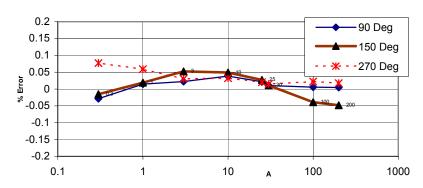

Figure 4: VARh Accuracy for 0.3A to 200A/240V Performance.

Measured at current distortion amplitude of 40% and voltage distortion amplitude of 10%.

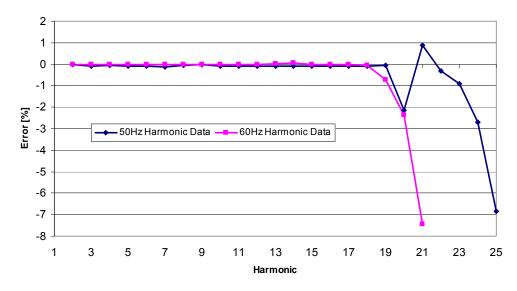

Figure 5: Meter Accuracy over Harmonics at 240V, 30A

**MARCH 2008**

Figure 6: Typical Meter Accuracy over Temperature Relative to 25°C (w/ Temperature Compensation)

Figure 7: Typical VAh Accuracy for VAh Using Vector Method

### **DATA SHEET**

MARCH 2008

#### **FUNCTIONAL DESCRIPTION**

#### THEORY OF OPERATION

The 71M6515H integrates the primary functional blocks required to implement a solid-state electricity meter front end. Included on-chip are an analog front end (AFE), a digital computation engine (CE), a voltage reference, a real time clock, and I/O pins. Various current sensor technologies are supported including Current Transformers (CT), Resistive Shunts, and Rogowski (di/dt) Coils.

In a typical application, the 71M6515H sequentially digitizes the voltage inputs on pins IA, VA, IB, VB, IC, VC and performs calculations to measure active energy (Wh), reactive energy (VARh), and apparent energy (VAh). In addition to these measurement functions, the real time clock function allows the device to record time of use (TOU) metering information for multi-rate applications.

The 71M6515H contains a temperature-trimmed ultra-precise voltage reference, and the on-chip digital temperature compensation mechanism includes a temperature sensor and associated controls for correction of unwanted temperature effects on measurement. RTC accuracy can be greatly improved by supplying correction coefficients derived from crystal characterization. The combination of both features enables designers to produce electricity meters with exceptional accuracy over the industrial temperature range.

#### **Meter Equations**

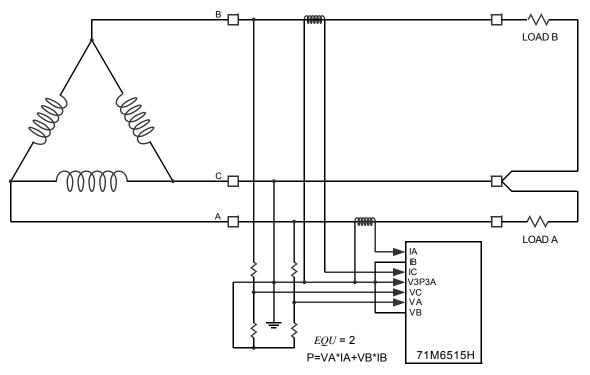

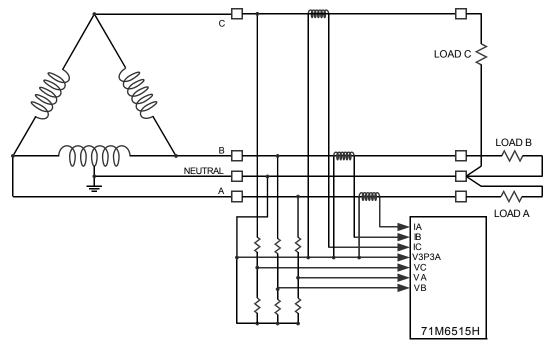

The 71M6515H implements the equations in Table 1. Register *EQU* specifies the equation to be used. In one sample time, each of the six inputs is converted and the selected equation updated. In a typical application, IA, IB, IC are connected to current transformers that sense the current on each phase of the line voltage. VA, VB, and VC are typically connected to voltage sensors (resistor dividers) with respect to NEUTRAL. NEUTRAL is to be connected to V3P3A, the analog supply voltage. **NEUTRAL is the zero reference for all analog measurements.**

| EQU | Watt & VAR Formula         | Application            | Channels used from MUX sequence Mux State: |    |    |    |    |    |

|-----|----------------------------|------------------------|--------------------------------------------|----|----|----|----|----|

|     |                            |                        | 0                                          | 1  | 2  | 3  | 4  | 5  |

| 0   | VA IA                      | 1 element, 2W 1ø       | IA                                         | VA | -  | -  | -  | -  |

| 1*  | VA(IA-IB)/2                | 1 element, 3W 1ø       | IA                                         | VA | IB | -  | -  | -  |

| 2   | VA IA + VB IB              | 2 element, 3W 3 øDelta | IA                                         | VA | IB | VB | -  | -  |

| 3*  | VA (IA - IB)/2 + VC IC     | 2 element, 4W 3ø Delta | IA                                         | VA | IB | -  | IC | VC |

| 4*  | VA(IA-IB)/2 + VB(IC-IB)/2) | 2 element, 4W 3ø Wye   | IA                                         | VA | IB | VB | IC | -  |

| 5   | VA IA + VB IB + VC IC      | 3 element, 4W 3ø Wye   | IA                                         | VA | IB | VB | IC | VC |

Note: Equations 1\*, 3\*, 4\* available only when IMAGE = 00 (CT mode).

**Table 1: Meter Equations**

Table 2 shows how the elements of the meter are mapped for the six possible equations.

### **DATA SHEET**

MARCH 2008

|     | Watt & VAR Formula                                            | Element Output Mapping |                   |                   |             |             |             |

|-----|---------------------------------------------------------------|------------------------|-------------------|-------------------|-------------|-------------|-------------|

| EQU | (WSUM/VARSUM)                                                 | WOSUM/<br>VAROSUM      | WISUM/<br>VARISUM | W2SUM/<br>VAR2SUM | IOSQ<br>SUM | IISQ<br>SUM | I2SQ<br>SUM |

| 0   | VA IA (1 element, 2W 1φ)                                      | VA*IA                  | ı                 | -                 | IA          | -           | ı           |

| 1   | VA*(IA-IB)/2<br>(1 element, 3W 1φ)                            | VA*(IA-IB)/2           | VA*IB             | -                 | IA-IB       | IB          | -           |

| 2   | VA*IA + VB*IB<br>(2 element, 3W 3φ Delta)                     | VA*IA                  | VB*IB             | -                 | IA          | IB          | -           |

| 3   | VA*(IA-IB)/2 + VC*IC<br>(2 element, 4W 3\phi Delta)           | VA*(IA-IB)/2           | 1                 | VC*IC             | IA-IB       | IB          | IC          |

| 4   | VA*(IA-IB)/2 + VB*(IC-IB)/2<br>(2 element, 4W 3\( \phi\) Wye) | VA*(IA-IB)/2           | VB*(IC-IB)/2      |                   | IA-IB       | IC-IB       | IC          |

| 5   | VA*IA + VB*IB + VC*IC<br>(3 element, 4W 3φ Wye)               | VA*IA                  | VB*IB             | VC*IC             | IA          | IB          | IC          |

**Table 2: Meter Element Output Mapping**

#### **ANALOG FRONT END**

#### A/D Converter (ADC)

A single delta-sigma A/D converter (ADC) digitizes the inputs to the device. The resolution of the ADC is 21 bits. The ADC operates at 5MHz oversampling rate and places the digital results in CE memory. Each analog input is sampled at 2520Hz. Once each accumulation interval, it refreshes the temperature value that is placed in the  $TEMP\_RAW$  register. The analog reference for all inputs is V3P3A, i.e. the ADC processes voltages between the input pins and V3P3A.

#### **Voltage Reference**

The device includes an on-chip precision bandgap voltage reference that incorporates auto-zero techniques as well as production trims to minimize errors caused by component mismatch and drift. The result is a voltage output with a predictable temperature coefficient.

The CE compensates for temperature characteristics of the voltage reference by modifying the gain applied to the V and I channels based on the coefficients *PPMC* and *PPMC2*. See the section "TEMPERATURE COMPENSATION" for details.

#### **DIGITAL COMPUTATION**

The six ADC outputs are processed and accumulated digitally. The default product summation is based on 42\*60 (if the  $SUM\_CYCLES$  register is set to 60) samples per accumulation interval. At the end of each accumulation interval, a ready interrupt (IRQZ) is signaled (if enabled with the READY bit in STMASK), indicating that fresh data is available to the host. For instance, if  $SUM\_CYCLES$  =30, the IRQZ rate will be 2Hz (500ms).

A dedicated 32-bit Computation Engine (CE) performs the precision computations necessary to accurately measure energy. Internal CE calculations include frequency-insensitive offset cancellation on all six channels and a frequency insensitive  $90^{\circ}$  phase shifter for VAR calculations. The CE also includes LPF smoothing filters after each product and squaring circuit to attenuate ripple and eliminate beat frequencies between the power line fundamental and the accumulation time. The CE directly calculates Watts, VARs,  $V^2$ , and  $I^2$  and accumulates them for one interval.

At the end of each CE computation cycle, the accumulated data are post-processed to calculate RMS amplitudes, phase angles, and VAh. When post-processing is complete, the IRQZ signal is activated.

The minimum combined cycle time for CE and post-processor is 400ms, which makes the maximum frequency for the IRQZ signal 2.5Hz.

### **DATA SHEET**

**MARCH 2008**

If the 71M6515H is interfacing to an external DSP (typically, but not necessarily through the SSI interface), the host may turn off post-processing by setting the *CE\_ONLY* bit in the *CONFIG* word. This will permit setting *SUM\_CYCLES* below its recommended lower limit of 24. *SUM\_CYCLES* may then be reduced to 1, creating an accumulation interval of only 42 samples. The outputs available in CE only mode are limited to temperature, frequency, voltage phases, input signal zero crossings, plus WSUM and VARSUM for each phase and VSQSUM, ISQSUM, and ISQFRACT for each phase.

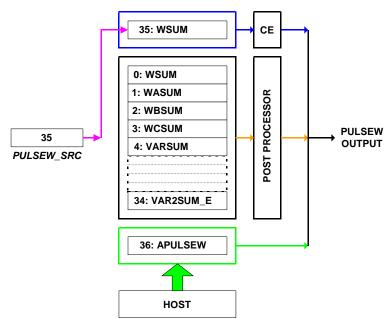

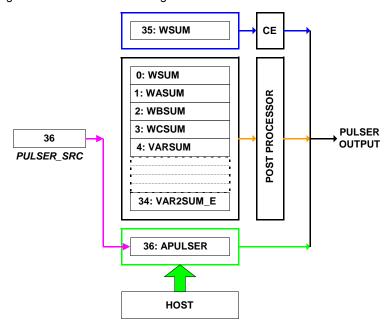

#### **Pulse Generators**

The chip contains four pulse generators connected to the pins PULSEW, PULSER, PULSE3, and PULSE4 that create low jitter pulses from 32-bit data. The peak time jitter for PULSEW and PULSER is the 397µs MUX frame period, and is independent of the rate of the generator or the length of time the generator is monitored. Thus, if the pulse generator is monitored for 1 second, the peak jitter is 400PPM. After 10 seconds, the peak jitter is 40PPM.

PULSE3 and PULSE4 are updated at a slower rate and have four times higher jitter, i.e. 160PPM after 10 seconds.

The average jitter is always zero. If it is attempted to drive either pulse generator faster than its maximum rate, it will simply output at its maximum rate without exhibiting any roll-over characteristics.

Pulse generator inputs may be from three sources:

- Internal (directly from the CE), PULSEW and PULSER only

- External (controlled by the host writing to registers APULSEW, APULSER, APULSE3, APULSE4)

- Post-processed values

The source is selected individually for each pulse output with the *PULSEW\_SRC*, *PULSES\_SRC*, *PULSE3\_SRC*, and *PULSE4\_SRC* registers. Figure 8 shows internal pulse generation for the PULSEW output selected by writing the value 35 into the *PULSEW\_SRC* register.

Figure 8: Internal Pulse Generation Selected in the PULSEW\_SRC Register

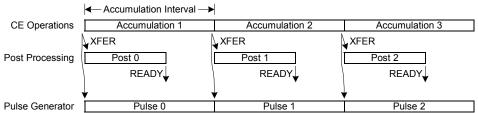

Internal data is pulsed out during the accumulation interval immediately following its accumulation interval. Post-processed values are pulsed out one accumulation interval after that.

### **DATA SHEET**

**MARCH 2008**

The pulse generator output rate depends on its input value, *WRATE*, *PULSE\_SLOW*, and *PULSE\_FAST*. Additionally, its maximum pulse width (negative going pulse) is controlled by *PULSEWIDTH*. High frequency pulses will have 50% duty cycle until their rate slows enough that their pulse width is limited by *PULSEWIDTH*.

In internal and post-processed modes, the pulse rate, expressed as Kh (Wh per pulse) is given by the formula:

$$Kh = \frac{VMAX\ IMAX}{In\ 8 \cdot SUM\ CYCLES \cdot WRATE \cdot X} 1.5757 \quad Wh / Pulse$$

where

**VMAX** is the meter voltage corresponding to an input voltage of 176mV (rms) at the VA, VB, and VC input pins, **IMAX** is the meter current corresponding to an input voltage of 176mV (rms) at the IA, IB, and IC input pins, **In\_8** is the additional ADC gain (1 or 8), as controlled by the *IA\_X*, *IB\_X* and *IC\_X* bits in the *CONFIG* register. **X** is the pulse speed factor determined from Table 3.

| PULSE_SLOW  | PULSE_FAST  | Х                            |

|-------------|-------------|------------------------------|

| 0           | 0           | 1.5*2 <sup>2</sup> =6        |

| 0           | 1           | 1.5*2 <sup>6</sup> =96       |

| 1           | 0           | 1.5*2 <sup>-4</sup> =0.09375 |

| 1 (default) | 1 (default) | 1.5                          |

Table 3: Pulse Speed Factor X

In external pulse mode, the pulse rate is given by the formula:

Rate(Hz) =

$$WRATE * X * input * 35.82*10^{-12}$$

,

where **input** is the value in registers *APULSER*, *APULSEW*. *APULSE3* or *APULSE4*, **X** is the pulse speed factor determined from Table 3.

External pulse generation can be seen as providing the raw voltage and current readings equivalent to  $V_{in}^*I_{in}$  / LSB directly to the pulse generator.

The maximum pulse rate is 7.56kHz for PULSEW and PULSER, and 150Hz for PULSE3 and PULSE4.

In external pulse mode, the pulse generators load their data at the beginning of each CE accumulation interval, preserving any partially implemented pulses from the previous interval. The source of data is controlled by the entries in the *PULSE\_SRCS* register. *PULSER\_SRCS* contains 8-bit entries for each pulse source, PULSEW, PULSER, PULSE3, and PULSE4. See the register description for details.

The procedure for accurate external pulse generation controlled by the host is:

- 1) Respond to a READY interrupt by reading the accumulated values.

- 2) Process the accumulated values.

- 3) Write the processed value(s) to *APULSER*, *APULSEW*, *APULSE3*, or *APULSE4*. The host must write to *APULSER*, *APULSEW*, *APULSE3*, and *APULSE4* before the next READY interrupt for the pulse generation to be beginning in the following accumulation interval.

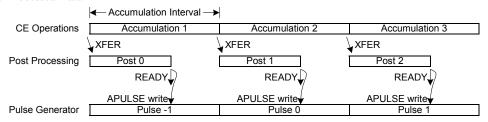

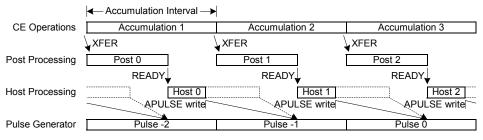

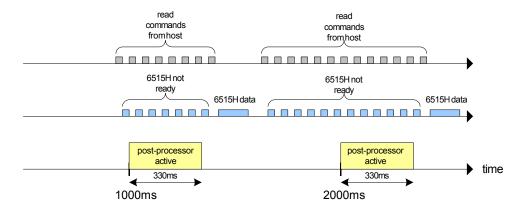

Figure 9 illustrates pulse generator timing.

Regardless of the source, the pulse generators should receive new data during each accumulation interval. If this does not occur and if the corresponding bit in the *STMASK* register is set, an *APULSE\_ERR* interrupt will be issued.

The PULSEW, PULSER, PULSE3 and PULSE4 pins are suitable for driving LEDs through a current limiting resistor. The LED should be connected so it is on when the pulse pin is low.

The pin PULSE\_INIT determines the logic level applied to the pulse pins on power-up, i.e. with PULSE\_INIT low, the pulse pins will be initialized to low (default = 1).

### **DATA SHEET**

MARCH 2008

The pulse width  $P_W$  is controlled with the PULSEWIDTH register for the PULSER and PULSEW output pins per the following formula:

$$P_W = \frac{2 \cdot PULSEWIDTH + 1}{2520.6}$$

The PULSE3 and PULSE4 output pins will always generate pulses with 50% duty cycle.

Internal Data (Directly by CE)

Post-Processed Data

External (Host data is transferred to the pulse generator in the first accumulation interval after the next READY)

**Figure 9: Pulse Generator Timing**

**DATA SHEET**

MARCH 2008

#### Internal Resources

#### **Oscillator**

The oscillator drives a standard 32.768kHz watch crystal. Crystals of this type are accurate and do not require a high current oscillator circuit. The 71M6515H oscillator has been designed specifically to handle watch crystals and is compatible with their high impedance and limited power handling capability. The oscillator power dissipation is very low to maximize the lifetime of any battery backup device attached to VBAT. Using PLL techniques, all internal clocks, such as the 4.915MHz clock for the ADC and the post-processor, are derived from the watch crystal frequency.

#### Real-Time Clock (RTC)

The RTC is driven directly by the crystal oscillator. In the absence of V3P3, it is powered by the battery-backed up supply. The RTC consists of a counter chain and output registers. The counter chain consists of registers for seconds, minutes, hours, day of week, day of month, month, and year. The nominal quadratic temperature coefficient of the crystal is automatically compensated in the RTC. **The RTC is capable of processing leap years.**

#### I/O Peripherals

The 71M6515H includes several I/O peripheral functions that improve the functionality of the device and reduce the component count for most meter applications. The I/O peripherals include a UART and digital I/O.

#### Digital I/O

The device includes eight pins of general purpose digital I/O (D0...D7). Each pin can be configured independently as an input or output with the  $D\_DIR$  bits. Inputs are standard CMOS with no pull-ups or pull-downs. Outputs are standard CMOS. The DIO pins are controlled by the  $D\_CONFIG$  register.

Immediately after reset or power-up, D0 through D7 are in tri-state mode (floating). 140 ms after reset, D0 through D7 are configured as outputs and driven low.

#### **UART Host Interface**

The UART is a dedicated 2-wire serial interface, which can communicate with the host processor. The operation of each pin is as follows:

**RX:** Is the pin accepting the serial input data. It inputs data to internal registers. The bytes are input LSB first. The voltage applied to this pin must be restricted to 0 to 3.6V.

TX: Is the pin used for serial output data. It outputs the contents of a block of internal registers. The bytes are output LSB first.

**BAUD\_RATE:** The baud rate can be selected with the BAUD RATE pin (38.4bps when high, 19.2bps when low).

**UARTCSZ:** This pin enables the UART when low. The UART can be reset by taking UARTCSZ briefly to the high state and then low again.

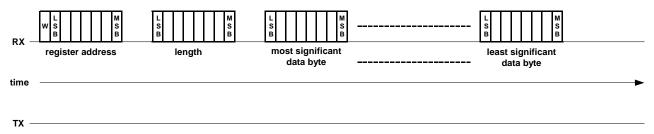

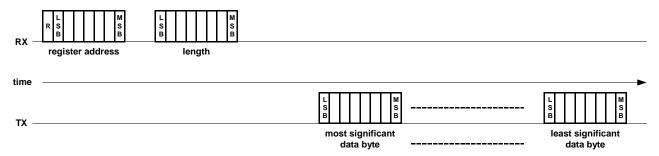

The 71M6515H has several on-chip registers, which can be read and written. All transfers start with a stream of 8-bit bytes (LSB first) from the host on the RX input, followed by a (possibly null) stream of 8-bit bytes (LSB first) to the host on the TX output (see Figure 10 and Figure 11). The UART is configured as 8N1 (8 bits, no parity, 1 stop bit).

If the *READY* bit in *STMASK* is enabled, the IRQZ pin can be used to signal data availability to the host. If data read cycles exceeding 1 second are used, care should be taken to prevent data overflow.

#### **UART Write Register Operation**

The registers are written by sending a byte, consisting of a starting register address in the seven MSBs and '0' in the LSB indicating this is a write operation. It is followed by a one byte length of bytes to write. If more bytes arrive than fit in the addressed register, subsequent registers will be written. The bytes are processed in "big-endian" order (i.e. most significant byte first). See Figure 10 (read bits and bytes from left to right).

### **DATA SHEET**

MARCH 2008

Figure 10: UART Write Operation

#### **UART Read Register Operation**

The registers are read by sending a byte, consisting of a start register address in the seven MSBs and '1' in the LSB indicating this is a read operation. It is followed by a one byte length of bytes to read. If more bytes are asked for than the size of the addressed register, subsequent registers will be read. The bytes are in "big-endian" order (i.e. most significant byte first). See Figure 11.

Figure 11: UART Read Operation

Note: In both register read and write operations, the register address can be 0 through 127 (0x7F). The register address byte is obtained by left-shifting the register address by one bit and setting bit 0 to 1 for read or setting bit 0 to 0 for write.

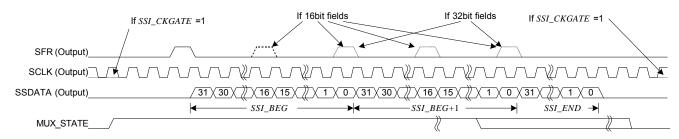

#### Synchronous Serial Interface (SSI)

A high speed, handshake, serial interface is available to send a contiguous block of CE data to an external data logger or DSP. The block of data, configurable as to location and size, is sent at the beginning of each ADC multiplex cycle. The SSI interface is enabled by the  $SSI\_EN$  bit and consists of the outputs SSCLK, SSDATA, and SFR and of the SRDY input pin. The interface is compatible with 16-bit and 32-bit processors. The operation of each pin is as follows:

**SSCLK:** This pin provides the serial clock. The clock can be 5MHz or 10MHz, as specified by the *SSI\_10M* bit. The *SSI\_CKGATE* bit controls whether SSCLK runs continuously or is gated off when no SSI activity is occurring. If SSCLK is gated, it will begin three cycles before SFR rises and will persist three cycles after the last data bit is output.

**SSDATA:** This pin provides the serial output data. SSDATA changes on the rising edge of SSCLK and outputs the contents of a block of CE words starting with address *SSI\_STRT* and ending with *SSI\_END*. The words are output MSB first. SSDATA is stable with the falling edge of SSCLK.

**SFR:** This pin provides the framing pulse. Although CE words are always 32 bits, the SSI interface will frame the entire data block as a single field, as multiple 16 bit fields, or as multiple 32 bit fields. The SFR pulse is one clock cycle wide, changes state on the rising edge of SSCLK and precedes the first bit of each field. The field size is set with *SSI\_FSIZE*: 0-entire data block, 1-8 bit fields, 2-16 bit fields, 3-32 bit fields. The polarity of the SFR pulse can be inverted with *SSI\_FPOL*. The first SFR pulse in a frame will rise on the third SSCLK clock period after MUX\_SYNC (fourth SSCLK period, if SSCLK is 10MHz). MUX\_SYNC can be used to synchronize the fields arriving at the data logger or DSP.

**SRDY:** The SRDY input should always be tied to GND.

### **DATA SHEET**

MARCH 200

The SSI timing is shown in Figure 12.

Figure 12: SSI Timing  $(SSI\_FPOL = SSI\_RDYPOL = 0)$

#### **Fault and Reset Behavior**

#### **Reset Mode**

When RESETZ is pulled low or when VFLT < V3P3/2, all activity (i.e. sampling of analog signals, CE, generation of digital outputs) in the chip stops while the analog circuits are active. The exceptions are the oscillator and RTC module, which continue to run. Additionally, all I/O Register bits are cleared. As long as VFLT > V3P3/2, the internal 2.5V regulator will continue to provide power to the digital section.

Once initiated, the reset mode will persist until the reset timer times out. This will occur in 4100 cycles of the real time clock after RESETZ goes high, at which time the 71M6515H will begin executing its preboot and boot sequences.

#### **Power Fault Circuit**

The power fault comparator compares the voltage at the VFLT pin to V3P3/2. The comparator output internally enables the battery backup protection for oscillator, RTC and RAM during the power fail mode.

#### **Temperature Compensation**

#### Voltage Reference

The internal voltage reference of the 71M6515H is calibrated at 25°C during device manufacture. The 71M6515H is given additional temperature-related calibrations which further compensate its ADC gain and allow it to achieve 10PPM/°C over ±60°C temperature range.

#### **Temperature Sensor**

The device includes an on-chip temperature sensor for determining the temperature of the bandgap reference. The primary use of the temperature data is to determine the magnitude of compensation required to offset thermal drift in the system. The temperature sensor is read once per accumulation interval.

Temperature measurement can be implemented with the following steps:

- 1) At a known temperature T<sub>N</sub>, read the *TEMP\_RAW* register and write the value into *TEMP\_NOM* register.

- Read the DELTA\_T register at the known temperature. The obtained value should be <±0.1°C.</li>

- 3) The temperature T (in °C) at any environment can be obtained by reading the *DELTA\_T* register and applying the following formula:

$$T = T_N + \frac{DELTA\_T}{10}$$

#### **Temperature Compensation for Energy Measurements**

*TEMP\_NOM* is one of the calibration parameters that must be loaded by the host in order to enable temperature measurement and thereby temperature compensation.

### **DATA SHEET**

**MARCH 2008**

*PPMC* and *PPMC2*, the linear and quadratic compensation coefficients, compensate for temperature drift in the 71M6515H reference that affects the meter performance. *PPMC* and *PPMC2* describe how the 71M6515H calculations are to respond to temperature. This means they should be the negative of the meter behavior before compensation. *PPMC* and *PPMC2* are scaled from PPM/°C and PPM/°C² values. See the register description for details. Temperature compensation can be selected to operate in one of two modes shown in the table below:

| Temperature Compensation Mode | rature Compensation Mode DEFAULT_PPM Bit in CONFIG Register |                                                         |

|-------------------------------|-------------------------------------------------------------|---------------------------------------------------------|

| Internal (CE)                 | 1                                                           | By post-processor, based on stored VREF characteristics |

| External (host)               | 0                                                           | By host                                                 |

When the part is first powered up, *TEMP\_NOM*, *PPMC*, and *PPMC2* are zero. When the host writes its calibration value into *TEMP\_NOM* (after setting the *DEFAULT\_PPM* bit on the *CONFIG* register to 1), *PPMC* and *PPMC2* will automatically be initialized to the values that best compensate for the temperature drift of the internal reference. These parameters will be individually customized for 71M6515H parts. If, for some reason, the host writes to *TEMP\_NOM* again, *PPMC* and *PPMC2* will not be changed since they will no longer be zero.

If *TEMP\_NOM* is not loaded by the host, *PPMC* and *PPMC2* are ignored, and their values are permanently held at zero. If *TEMP\_NOM* is zero, no temperature compensation occurs, even if *PPMC* and *PPMC2* are loaded.

If the host wishes to provide its own compensation, it should read *PPMC* and *PPMC* and modify them by merging the additional compensation into to them. In that case, the *DEFAULT\_PPM* bit in the CONFIG register must be zero.

#### **Temperature Compensation for the Crystal and RTC**

The crystal oscillator contributes negligible error to energy calculations. However, sometimes specifications for the real time clock (RTC) require better accuracy than that provided by the untrimmed watch crystal. The 71M6515H therefore allows calibration of the RTC clock. Calibration requires that frequency tolerance and frequency stability either be obtained from the manufacturer or be independently measured (the RTC clock is available on the TMUX pin). Calibration does not change the frequency of the RTC clock, but rather increments or decrements the clock by one second when sufficient error has accumulated. Positive correction makes the clock run faster.

The formula for the RTC correction factor is as follows:

$$\mathsf{CORRECTION}\left[\mathsf{PPM}\right] = \frac{Y\_CALC0}{10} + \frac{Y\_CALC1}{100} \, \Delta T \quad + \frac{Y\_CALC2}{1000} \, \Delta T^2$$

Where  $Y_{CALC0} = 10 *$  crystal frequency deviation from ideal (measured)

Y\_CALC1 = 100 \* crystal skew (nominally zero)

Y CALC2 = 1000 \* crystal frequency stability (specified)

$\Delta T$  = T - Calibration Temperature in °C

Calibration

#### **Calibration Factors for CT and Resistive Shunt**

Once installed in a meter, the TERIDIAN 71M6515H IC has to be calibrated for the tolerances of current sensors, voltage dividers and signal conditioning components. The room temperature reading of its temperature sensor must also be entered. These calibration factors must be stored by the host and, upon power up, loaded into the TERIDIAN 71M6515H. Typical calibration constants are listed in Table 4.

|    |     | _            |    |    |

|----|-----|--------------|----|----|

| МΔ | RCI | <b>-</b> 1 2 | በበ | ١Q |

|    |     |              |    |    |

| Name     | Description                                                        |  |  |  |

|----------|--------------------------------------------------------------------|--|--|--|

| CAL_IA   |                                                                    |  |  |  |

| CAL_VA   |                                                                    |  |  |  |

| CAL_IB   | Gain factors for current and voltage of each phase.                |  |  |  |

| CAL_VB   | Gain factors for current and voltage of each phase.                |  |  |  |

| CAL_IC   |                                                                    |  |  |  |

| CAL_VC   |                                                                    |  |  |  |

| TEMP_NOM | The value of <i>TEMP_RAW</i> at nominal temperature.               |  |  |  |

| PHADJ_A  | Phase compensation for each current. If phase compensation is 0 or |  |  |  |

| PHADJ_B  | current sensors have predictable phase, PHADJ may not need to be   |  |  |  |

| PHADJ_C  | measured on every meter.                                           |  |  |  |

**Table 4: Typical Calibration Parameters (CT)**

Gain adjustment ( $CAL\_Xn$  parameters) is used to compensate for tolerances of components used for signal conditioning, especially the resistive components. A 1% increase in  $CAL\_Xn$  will cause a 1% increase in the channel gain.

The phase compensation circuit in the TERIDIAN 71M6515H is optimized for operation with current transformers (CT's). These devices have a low frequency pole and therefore have a slight amount of phase lead at 50 or 60Hz—more at 50Hz than at 60Hz. The phase lead diminishes at higher harmonics. When *PHADJ\_n* is calibrated as shown below at either 50Hz or 60Hz, the CT will be correctly compensated from below 25Hz to beyond 1100Hz.

This phase compensator is markedly superior to the more common technique of programming a time delay to compensate for CT phase. The time delay technique results in phase compensation that is correct at only one frequency, and actually amplifies the phase error at harmonics of the frequency.

#### Calibration Factors for Rogowski Coil Sensors

If *IMAGE* is set to 01, i.e. the 71M6515H can be operated with Rogowski Coil sensors. In this case, one more calibration factor per phase is needed. The *PHADJ* parameters have non-zero defaults and do not obey the same formula used for CT calibration. The feedthrough parameter has to be determined by a separate crosstalk measurement. Table 5 shows the parameters involved in the calibration procedure for the Rogowski sensor.

| Name     | Description                                                           |  |  |

|----------|-----------------------------------------------------------------------|--|--|

| CAL_IA   |                                                                       |  |  |

| CAL_VA   |                                                                       |  |  |

| CAL_IB   | Gain constants for current and voltage of each phase.                 |  |  |

| CAL_VB   | Gain constants for current and voltage of each phase.                 |  |  |

| CAL_IC   |                                                                       |  |  |

| CAL_VC   |                                                                       |  |  |

| TEMP_NOM | The value of <i>TEMP_RAW</i> at nominal temperature.                  |  |  |

| PHADJ_A  | Phase compensation for each current. If phase compensation is 0 or if |  |  |

| PHADJ_B  | current sensors have predictable phase, PHADJ may not need to be      |  |  |

| PHADJ_C  | measured on every meter.                                              |  |  |

| VFEED_A  |                                                                       |  |  |

| VFEED_B  | Feedthrough compensation for each current.                            |  |  |

| VFEED_C  |                                                                       |  |  |

Table 5: Typical Calibration Parameters (Rogowski)

### **DATA SHEET**

**MARCH 2008**

#### **General Notes on Calibration**

= 1.875Hz will be established.

The calibration procedures described below should be followed after interfacing the voltage and current sensors to the 71M6515H chip. When properly interfaced, the V3P3 power supply is connected to the meter neutral and is the DC reference for each input. Each voltage and current waveform, as seen by the 6515H, is scaled to be less than 250mV (peak).

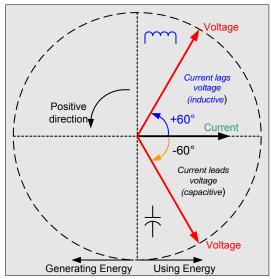

Each meter phase must be calibrated individually. The procedures below show how to calibrate a meter phase with either three or five measurements. Note that there is no need to calibrate for VARh if the Wh measurement is calibrated correctly. Note that positive load angles correspond to lagging current (see Figure 13).

For a typical calibration, a meter calibration system is used to apply a calibrated load, e.g. 240V at 30A, while interfacing the voltage and current sensors to the 71M6515H. This load should result in an observable pulse rate at the PULSEW output depending on the selected energy per pulse. For example, 7.2kW will result in an energy rate corresponding to 7200Wh/3600s = 2Wh/s, i.e., when 7.2kW are applied per phase (resulting in a total power of 21.6kW, equivalent to 6Wh/s) and a Kh of 3.2 (Wh/pulse) has been configured, a pulse rate of 6Wh/3.2Whs

#### Figure 13: Definition of Load Angles

It is entirely possible to calibrate piece-wise, i.e. in segments, to compensate for non-linear sensors. For example, one set of calibration factors can be applied by the host when the current is below 0.5A, while another set is applied when the current is at or above 0.5A.

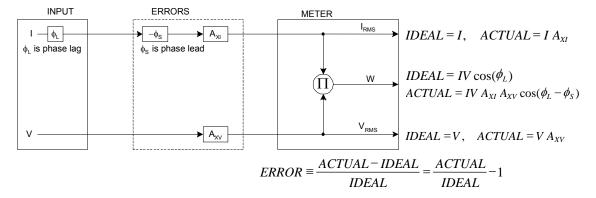

#### Calibration Procedure for CT and Resistive Shunt

A typical meter has phase and gain errors as shown by  $\phi_S$ ,  $A_{XI}$ , and  $A_{XV}$  in Figure 14. Following the typical meter convention of current phase being in the lag direction, the small amount of phase lead in a typical current sensor is represented as  $-\phi_S$ . The errors shown in Figure 14 represent the sum of all gain and phase errors. They include errors in voltage attenuators, current sensors, signal conditioning circuits, and in ADC gains. In other words, no errors are made in the 'input' or 'meter' boxes.

Figure 14: Watt Meter with Gain and Phase Errors.

During the calibration phase, we measure errors and then introduce correction factors to nullify their effect. With three unknowns to determine, we must make at least three measurements. If we make more measurements, we can average the results.

#### **Calibration with Three Measurements**

The simplest calibration method is to make three measurements. Typically, a voltage measurement and two Watt-hour (Wh) measurements are made.

If the voltage measurement has the error  $E_V$  and the two Wh measurements have errors  $E_0$  and  $E_{60}$ , where  $E_0$  is measured with  $\phi_L$  = 0 and  $E_{60}$  is measured with  $\phi_L$  = 60. These values should be simple ratios—not percentage values. They should be zero when the meter is accurate and negative when the meter runs slow. The fundamental frequency is  $f_0$ . T is equal to  $1/f_S$ , where  $f_S$  is the sample frequency (2520.62Hz). Set all calibration factors to nominal:  $CAL_IA$  = 16384,  $CAL_VA$  = 16384,  $PHADJ_A$  = 0.

From the voltage measurement, we determine that

1.

$$\rightarrow$$

$A_{xy} = E_y + 1$

We use the other two measurements to determine  $\phi_S$  and  $A_{XI}$ .

2.

$$E_0 = \frac{IV A_{XV} A_{XI} \cos(0 - \phi_S)}{IV \cos(0)} - 1 = A_{XV} A_{XI} \cos(\phi_S) - 1$$

2a.

$$A_{XV}A_{XI} = \frac{E_0 + 1}{\cos(\phi_s)}$$

3.

$$E_{60} = \frac{IV A_{XV} A_{XI} \cos(60 - \phi_S)}{IV \cos(60)} - 1 = A_{XV} A_{XI} \frac{\cos(60 - \phi_S)}{\cos(60)} - 1$$

3a.

$$E_{60} = \frac{A_{XV}A_{XI}\left[\cos(60)\cos(\phi_S) + \sin(60)\sin(\phi_S)\right]}{\cos(60)} - 1$$

$$= A_{XV} A_{XI} \cos(\phi_S) + A_{XV} A_{XI} \tan(60) \sin(\phi_S) - 1$$

Combining 2a and 3a:

4.

$$E_{60} = E_0 + (E_0 + 1) \tan(60) \tan(\phi_S)$$

5.

$$\tan(\phi_S) = \frac{E_{60} - E_0}{(E_0 + 1)\tan(60)}$$

6.

$$\Rightarrow$$

$\phi_S = \tan^{-1} \left( \frac{E_{60} - E_0}{(E_0 + 1)\tan(60)} \right)$

and from 2a:

$$7. \Rightarrow A_{XI} = \frac{E_0 + 1}{A_{XV} \cos(\phi_S)}$$

Now that we know the A<sub>XV</sub>, A<sub>XI</sub>, and  $\phi_S$  errors, we calculate the new calibration voltage gain coefficient from the previous ones:

$$CAL_{V_{NEW}} = \frac{CAL_{V}}{A_{XV}}$$

### **DATA SHEET**

MARCH 200

We calculate PHADJ from  $\phi_S$ , the desired phase lags

$$PHADJ = 2^{20} \left[ \frac{\tan(\phi_S) \left[ 1 + (1 - 2^{-9})^2 - 2(1 - 2^{-9})\cos(2\pi f_0 T) \right]}{(1 - 2^{-9})\sin(2\pi f_0 T) - \tan(\phi_S) \left[ 1 - (1 - 2^{-9})\cos(2\pi f_0 T) \right]} \right]$$

Finally, we calculate the new calibration current gain coefficient, including compensation for a slight gain increase in the phase calibration circuit.

$$CAL_{I_{NEW}} = \frac{CAL_{I}}{A_{XI}} \frac{1}{\sqrt{1 + \frac{2^{-20}PHADJ(2 + 2^{-20}PHADJ - 2(1 - 2^{-9})\cos(2\pi f_{0}T))}{1 - 2(1 - 2^{-9})\cos(2\pi f_{0}T) + (1 - 2^{-9})^{2}}}}$$

#### **Calibration with Five Measurements**

The five measurement method provides more orthogonality between the gain and phase error derivations. This method involves measuring  $E_V$ ,  $E_0$ ,  $E_{180}$ ,  $E_{60}$ , and  $E_{300}$ . Again, set all calibration factors to nominal, i.e.  $CAL\_IA$  = 16384,  $CAL\_VA$  = 16384,  $PHADJ\_A$  = 0..

First, calculate  $A_{XV}$  from  $E_{V}$ :

$$1. \Rightarrow A_{XV} = E_V + 1$$

Calculate  $A_{XI}$  from  $E_0$  and  $E_{180}$ :

2.

$$E_0 = \frac{IV A_{XV} A_{XI} \cos(0 - \phi_S)}{IV \cos(0)} - 1 = A_{XV} A_{XI} \cos(\phi_S) - 1$$

3.

$$E_{180} = \frac{IV A_{XV} A_{XI} \cos(180 - \phi_S)}{IV \cos(180)} - 1 = A_{XV} A_{XI} \cos(\phi_S) - 1$$

4.

$$E_0 + E_{180} = 2A_{XV}A_{XI}\cos(\phi_S) - 2$$

5.

$$A_{XV}A_{XI} = \frac{E_0 + E_{180} + 2}{2\cos(\phi_S)}$$

6.

$$A_{XI} = \frac{(E_0 + E_{180})/2 + 1}{A_{XV} \cos(\phi_S)}$$

Use above results along with  $E_{60}$  and  $E_{300}$  to calculate  $\varphi_S.$

7.

$$E_{60} = \frac{IV A_{XV} A_{XI} \cos(60 - \phi_S)}{IV \cos(60)} - 1$$

$$= A_{XV} A_{XI} \cos(\phi_S) + A_{XV} A_{XI} \tan(60) \sin(\phi_S) - 1$$

8.

$$E_{300} = \frac{IV A_{XV} A_{XI} \cos(-60 - \phi_S)}{IV \cos(-60)} - 1$$

$$= A_{XV} A_{XI} \cos(\phi_S) - A_{XV} A_{XI} \tan(60) \sin(\phi_S) - 1$$

### **DATA SHEET**

MARCH 2008

Subtract 8 from 7:

9.

$$E_{60} - E_{300} = 2A_{XV}A_{XI} \tan(60)\sin(\phi_S)$$

use equation 5:

10.

$$E_{60} - E_{300} = \frac{E_0 + E_{180} + 2}{\cos(\phi_S)} \tan(60) \sin(\phi_S)$$

11.

$$E_{60} - E_{300} = (E_0 + E_{180} + 2) \tan(60) \tan(\phi_S)$$

12.

$$\phi_S = \tan^{-1} \left( \frac{(E_{60} - E_{300})}{\tan(60)(E_0 + E_{180} + 2)} \right)$$

Now that we know the  $A_{XV}$ ,  $A_{XI}$ , and  $\phi_S$  errors, we calculate the new calibration voltage gain coefficient from the previous ones:

$$CAL_{V_{NEW}} = \frac{CAL_{V}}{A_{xv}}$$

We calculate PHADJ from  $\phi_S$ , the desired phase lag:

$$PHADJ = 2^{20} \left[ \frac{\tan(\phi_S) \left[ 1 + (1 - 2^{-9})^2 - 2(1 - 2^{-9})\cos(2\pi f_0 T) \right]}{(1 - 2^{-9})\sin(2\pi f_0 T) - \tan(\phi_S) \left[ 1 - (1 - 2^{-9})\cos(2\pi f_0 T) \right]} \right]$$

Finally, we calculate the new calibration current gain coefficient, including compensation for a slight gain increase in the phase calibration circuit.

$$CAL_{I_{NEW}} = \frac{CAL_{I}}{A_{XI}} \frac{1}{\sqrt{1 + \frac{2^{-20}PHADJ(2 + 2^{-20}PHADJ - 2(1 - 2^{-9})\cos(2\pi f_{0}T))}{1 - 2(1 - 2^{-9})\cos(2\pi f_{0}T) + (1 - 2^{-9})^{2}}}}$$

#### **Alternative Calibration Procedures**

It is possible to implement a fast calibration based on only one measurement with a zero-degree load angle. Details can be found in the TERIDIAN Application Note AN\_651X\_022 (Calibration Procedures).

#### Calibration Procedure for Rogowski Sensor

Rogowski coils generate an output signal that is the derivative of the input current. The 6515H Rogowski module implemented in the Rogowski CE image digitally compensates for this effect and has the usual gain and phase calibration adjustments. Additionally, calibration adjustments are provided to eliminate voltage coupling from the sensor input.

Current sensors built from Rogowski coils have relatively high output impedances that are susceptible to capacitive coupling from the large voltages present in the meter. The most dominant coupling is usually capacitance between the primary of the coil and the coil's output. This coupling adds a component proportional to the derivative of voltage to the sensor output. This effect is compensated by the voltage coupling calibration coefficients.

As with the CT procedure, the calibration procedure for Rogowski sensors uses the meter's display to calibrate the voltage path and the pulse outputs to perform the remaining energy calibrations. The calibration procedure must be performed to each phase separately, making sure that the pulse generator is driven by the accumulated real energy for just that phase. In other words, the pulse generator input should be set to WhA, WhB, or WhC, depending on the phase being calibrated. The IC has to be configured for Rogowski mode (*IMAGE*=01). In preparation of the calibration, all calibration parameters are set to their default values. *VMAX* and *IMAX* are set to reflect the system design parameters. *WRATE* and *PULSE\_SLOW*, *PULSE\_FAST* are adjusted to obtain the desired Kh.

For details on calibrating a meter for Rogowski coil sensors, see the TERIDIAN Application Note AN\_6515\_036.

### **DATA SHEET**

MARCH 2008

#### Meter Design - Scaling of Measured Values

An actual meter will always use sensors that scale the voltages and currents managed by the meter to small voltages that can be processed by the 71M6515H. This scaling is reflected in the system parameters *VMAX* and *IMAX*. Scaling is physically implemented with resistor dividers for the voltage signals and current transformers, shunt resistors or Rogowski coils for the current signals.

*IMAX* is the RMS meter current that results in 250mV peak signal (or 177mV RMS) at the ADC input (IA, IB, IC pins). *VMAX* is the RMS meter voltage that results in 250mV peak signal at the ADC input (VA, VB, VC pins). In\_8 is either 1 or 8, depending on *In\_8x*, the ADC gain configuration bit for element n (see *IA\_8*, *IB\_8*, *IC\_8*) in the *CONFIG* register.

Only the host is aware of the system parameters VMAX and IMAX, while the CE and the post-processor know signal amplitudes only as values relative to their maximum peak levels (250mV). This makes the host itself responsible for translating the measured values from the 71M6515H registers into real-world values by applying the parameters VMAX, IMAX and  $In_{-}8$ . Equally, the host is responsible for non-volatile storage of accumulated energy values, calibration factors, default settings et cetera.

Measured values and values determining the function of the 71M6515H, as controlled by the registers described in the following section, are often stated as fractions or multiples of the system parameters VMAX, IMAX and  $In\_8$ .

#### **Host Interface - REGISTER DESCRIPTION**

Communication between the host and the 71M6515H is established by writing to and reading from the registers described in this section. The registers are accessible via the UART (see UART Write and Read Operation).

The tables below contain the registers that can be accessed by the host to obtain data from the 71M6515H or to control and configure the IC.

Bits with a W (write) direction are written by the host. Bits with R (read) direction can only be read by the host. Write operations attempted to read-only registers will result in the  $CMD\_IGNORED$  bit set in the STATUS register. Unless stated otherwise, all registers are four bytes (32 bits), 2's complement, and have a range of ( $2^{31}$ -1) to -( $2^{31}$ -1).

#### **Register Groups**

Each register belongs to one of the following functional groups:

- Pulse Generation

- Calibration

- Control of Basic Functions

- Temperature

- Temperature Compensation

- Output Signals

- Accumulated Energy and V/I Values

- Alarms and Thresholds

- Time (RTC)

- Test

- Digital I/O Control (pins D0...D7)

## **DATA SHEET**

**MARCH 2008**

#### **Registers in Alphabetical Order**

| Name                                     | Address<br>(hex)             | R/W                      | Default                            | Group                       | Comment                     |