LMS5258 150mA, μCap, Low Dropout Voltage Regulator with Power Good

## LMS5258 150mA, µCap, Low Dropout Voltage Regulator with **Power Good General Description**

The LMS5258 is a µCap, precise CMOS voltage regulator with power good output.

It provides up to 150mA and consumes a typical of 10nA in shutdown mode. The LMS5258 output stage is designed with a push pull output for faster transient response.

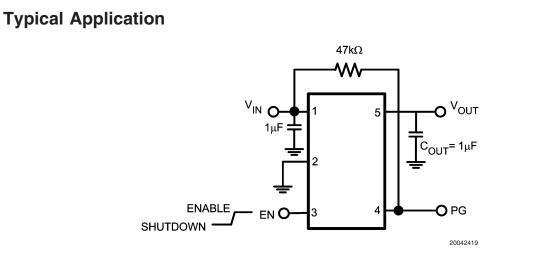

The LMS5258 is optimized to work with low value, low cost ceramic capacitors. The output typically require only 1µF of output capacitance for stability. The enable pin can be tied to V<sub>IN</sub> for easy device layout.

The LMS5258 is designed for portable, battery powered equipment applications with small space requirements.

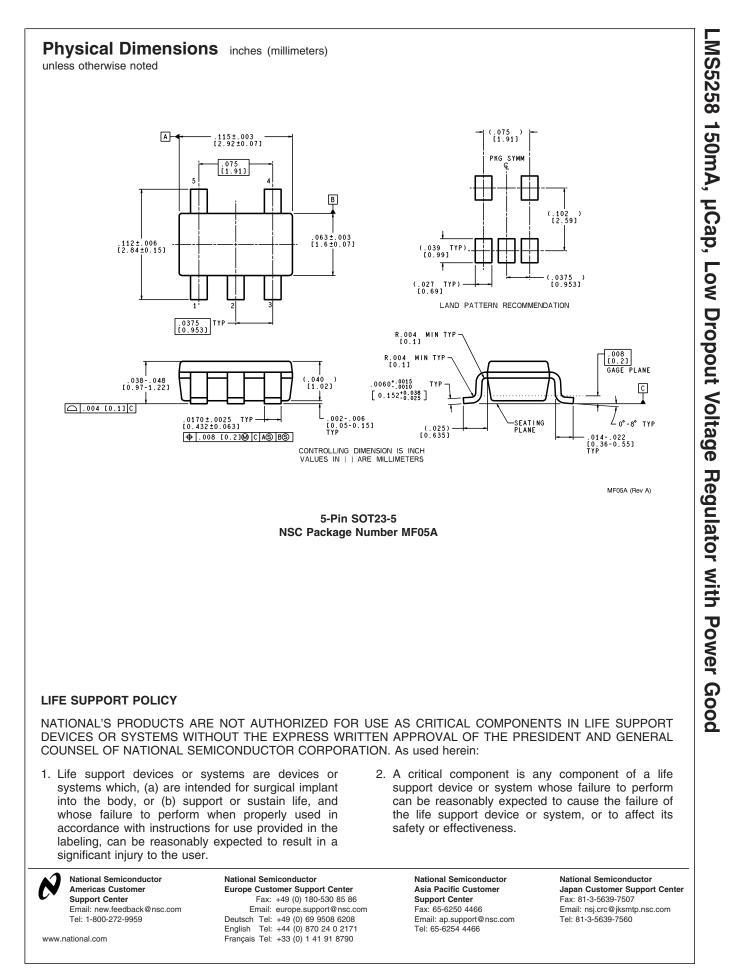

The LMS5258 is available in a 5-pin SOT-23 package. Performance is specified for the -40°C to +125°C temperature range and is available in a fixed 1.2V. For other output voltage options, please contact National Semiconductor.

### Features

- Power good indicator

- Stability with low ESR capacitors

- Low ground current: 120µA

- 150mA output current

- "Zero" shutdown mode current

- Fast transient response

- Auto Discharge

- Thermal shutdown

- Current limiting

- TTL-Logic-controlled enable input

- Pin-to-pin replacement for Mic<sup>™</sup> 5258

### Applications

- Processor power-up sequencing

- Laptop, notebook and palm top computer

- PCMCIA V<sub>CC</sub> and V<sub>PP</sub> regulation switching

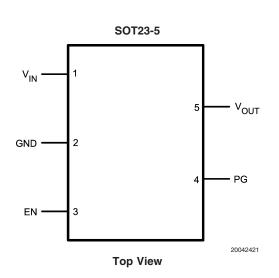

## **Pin Description**

| Pin Number | Pin Name                      | Pin Function         |

|------------|-------------------------------|----------------------|

| 1          | V <sub>IN</sub> Input Voltage |                      |

| 2          | GND                           | Ground               |

| 3          | EN                            | Enable Input Logic,  |

|            |                               | Logic High = Enabled |

|            |                               | Logic Low = Shutdown |

|            |                               | (Do not leave open)  |

| 4          | PG Power Good Output          |                      |

| 5          | V <sub>OUT</sub>              | Output Voltage       |

**Connection Diagram**

LMS5258

## **Ordering Information**

| Package      | Part Number    | Package Marking | Transport Media        | NSC<br>Drawing |  |

|--------------|----------------|-----------------|------------------------|----------------|--|

| 5-Pin SOT-23 | LMS5258MF-1.2  | LF9B            | 1k Units Tape and Reel | MF05A          |  |

|              | LMS5258MFX-1.2 | LF9D            | 3k Units Tape and Reel |                |  |

## Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| ESD Tolerance (Note 2)          |                   |

|---------------------------------|-------------------|

| Human Body Model                | 2000V             |

| Junction Temperature            | 150°C             |

| $V_{IN}, V_{OUT}, V_{EN}$       | –0.3 TO 6.5V      |

| Soldering Information           |                   |

| Infrared or Convection (20 sec) | 235°C             |

| Wave Soldering (10 sec)         | 260°C (lead temp) |

## **Operating Ratings**

Supply VoltagesVIN2.7V to 6VVEN0V to VINJunction Temp. Range (Note 3)-40°C to +125°CStorage Temperature Range-65°C to 150°CPackage Themal Resistance235°C/W

## **Electrical Characteristics**

Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}$ C,  $V_{IN} = 2.7$ V,  $I_L = 100\mu$ A,  $C_{OUT} = 1\mu$ F,  $V_{EN} \ge 2.0$ V. **Boldface** limits apply over the entire operating temperature range,  $-40^{\circ}$ C to  $125^{\circ}$ C.

| Symbol                 | Parameter                   | Conditions                                                       | Min      | Тур      | Max      | Units |

|------------------------|-----------------------------|------------------------------------------------------------------|----------|----------|----------|-------|

|                        |                             |                                                                  | (Note 5) | (Note 4) | (Note 5) | Í     |

| V <sub>o</sub> Out     | Output Voltage Accuracy     |                                                                  | -3       |          | 3        | %     |

|                        |                             |                                                                  | -4       |          | 4        |       |

| $\Delta V_O/V_O$       | Line Regulation             | $V_{IN} = 2.7V$ to 6V                                            | -0.3     |          | 0.3      | %     |

| $\Delta V_{O}/V_{O}$   | Load Regulation             | I <sub>L</sub> = 0.1mA to 150mA (Note 6)                         |          | 1        | 4        | %     |

| l <sub>Q</sub>         | Quiescent Current           | $V_{EN} \le 0.4V$ (Shutdown), PG = NC                            |          | .01      | 1        | μA    |

| I <sub>GND</sub> Groun | Ground Pin Current (Note 5) | $V_{EN} \ge 2.0V$ (active),                                      |          | 120      | 180      | μA    |

|                        |                             | $V_{IN} = 6V, I_L = 0mA$                                         |          |          |          |       |

|                        |                             | $I_L = 150 \text{mA}, V_{EN} \ge 2.0 \text{V} \text{ (active)},$ |          | 160      | 225      |       |

|                        |                             | $V_{IN} = 6V$                                                    |          |          |          |       |

| PSRR Power St          | Power Supply Rejection      | $f = 120H_Z, C_{OUT} = 4.7\mu F,$                                |          | 62       |          | dB    |

|                        |                             | I <sub>L</sub> = 150mA                                           |          |          |          |       |

| I <sub>LIMIT</sub>     | Current Limit               | V <sub>OUT</sub> = 0V                                            | 160      | 350      |          | mA    |

| Thermal Pr             | otection                    |                                                                  | •        |          |          |       |

|                        | Thermal Shutdown            |                                                                  |          | 150      |          | °C    |

|                        | Temperature                 |                                                                  |          |          |          |       |

| Enable Inpu            | ut                          |                                                                  | •        |          |          |       |

| V <sub>IL</sub>        | Enable Input Voltage Level  | Logic Low (off), $V_{IN} = 5.5V$                                 |          |          | 0.4      | V     |

| V <sub>IH</sub>        |                             | Logic High (on), V <sub>IN</sub> = 5.5V                          | 2        |          |          | V     |

| I <sub>IL</sub>        | Enable Input Current        | $V_{IL} \leq 0.4V, \ V_{IN} = 5.5V$                              |          | 0.01     |          | μA    |

| I <sub>IH</sub>        |                             | $V_{IH} \ge 2.0V, V_{IN} = 5.5V$                                 |          | 0.01     |          | μA    |

| Power Goo              | d                           |                                                                  | •        |          |          |       |

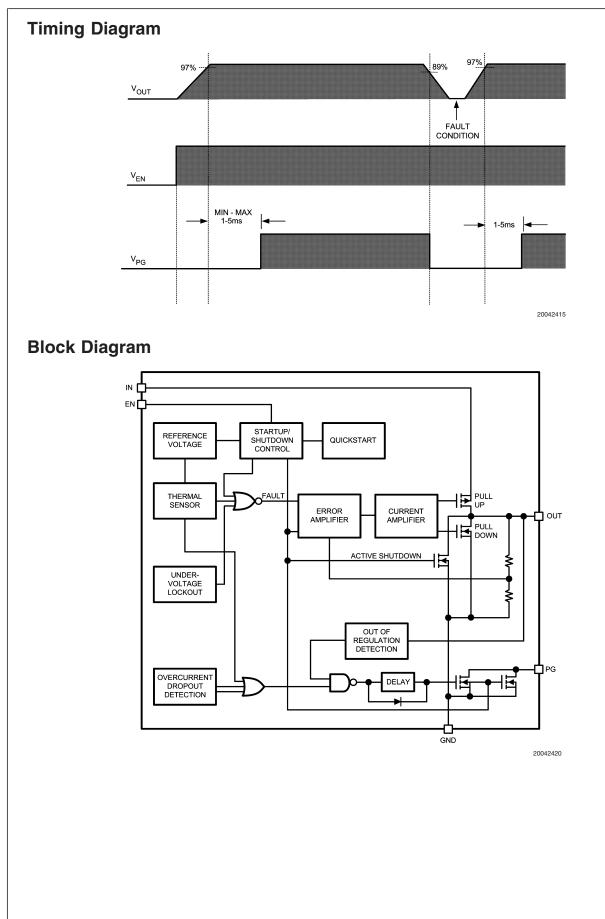

| V <sub>PG</sub>        | Low Threshold               | % of V <sub>OUT</sub> (PG ON)                                    | 89       |          |          | 0/    |

|                        | High Threshold              | % of V <sub>OUT</sub> (PG OFF)                                   |          |          | 97       | %     |

| V <sub>OL</sub>        | PG Output Logic-Low         | Ipowergood = 100µA, Fault                                        |          | 0.02     | 0.1      | V     |

|                        | Voltage                     | Condition                                                        |          |          |          |       |

| I <sub>PG</sub>        | Power Good Leakage          | Power Good Off, V <sub>PG</sub> = 5.5V                           |          | 0.01     |          | μA    |

|                        | Current                     |                                                                  |          |          |          |       |

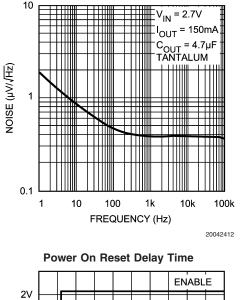

| V <sub>PG</sub> Delay  | Delay Time to Power Good    | See Timing Diagram                                               | 1        |          | 5        | ms    |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications and the test conditions, see the Electrical Characteristics. Note 2: Human body model, 1.5kΩ in series with 100pF.

Note 3: The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A)/\theta_{JA}$ . All numbers apply for packages soldered directly into a PC board.

Note 4: Typical Values represent the most likely parametric norm.

Note 5: All limits are guaranteed by testing or statistical analysis.

Note 6: Regulation is measured at constant junction temperature using low duty cycle pulse testing.

Note 7: Ground pin current is the regulator quiescent current. The total current drawn from the supply is the sum of the load current plus the ground pin current.

3

Downloaded from Elcodis.com electronic components distributor

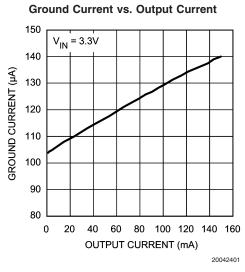

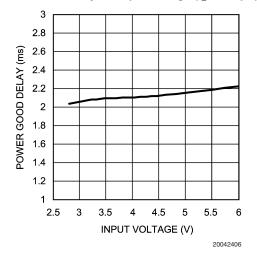

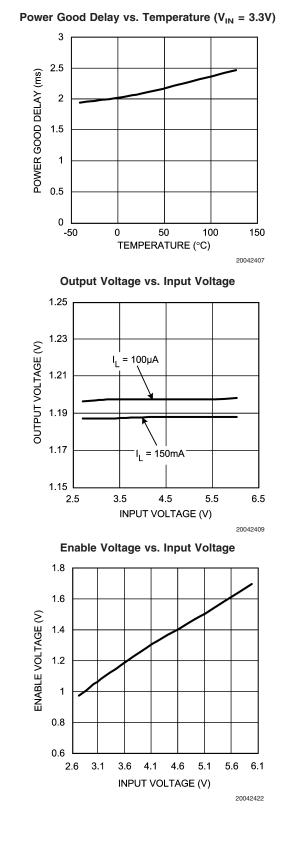

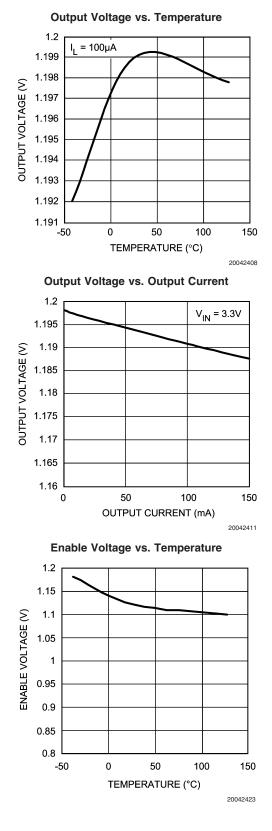

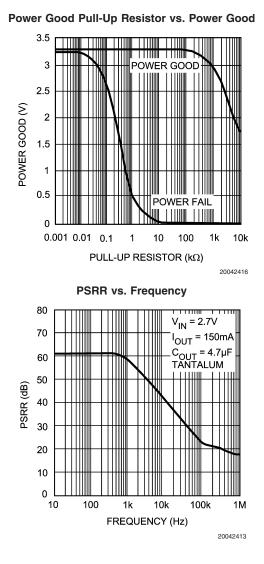

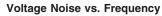

## **Typical Performance Characteristics** Unless otherwise specified, $V_{IN} = 3.3V$ , $C_{OUT} = 1\mu$ F, $T_A = 25^{\circ}$ C and powergood pull up resistor = $47k\Omega$ .

# LMS5258

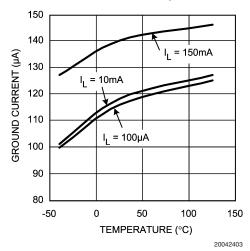

Ground Current vs. Temperature

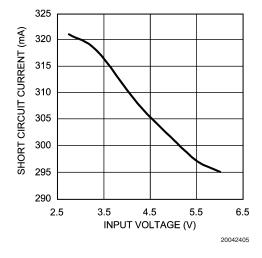

Short Circuit Current vs. Input Voltage

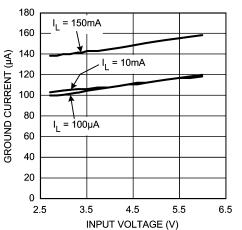

Ground Current vs. Input Voltage

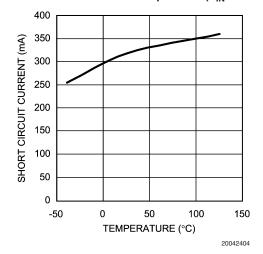

Short Circuit Current vs. Temperature ( $V_{IN} = 3.3V$ )

Power Good Delay vs. Input Voltage ( $I_L = 100 \mu A$ )

**Typical Performance Characteristics** Unless otherwise specified,  $V_{IN} = 3.3V$ ,  $C_{OUT} = 1\mu$ F,  $T_A = 25^{\circ}$ C and powergood pull up resistor =  $47k\Omega$ . (Continued)

20042414

## **Application Notes**

LMS5258 is a linear regulator designed to be used with a low ESR, low cost ceramic capacitors.

### **EXTERNAL CAPACITORS**

The LMS5258 regulator requires an output capacitor to maintain stability. The capacitor must be at least  $1\mu$ F or greater. The capacitor can be low-ESR ceramic chip capacitor, however for improved capacitance over temperature, tantalum capacitors can be used.

A  $1\mu$ F input capacitor is recommended when the supply capacitance is more than 10 inches away from the device, or when the supply is a battery.

X7R dielectric ceramic capacitors are recommended because of their temperature performance. X7R-type capacitors change capacitance by 15% over their operating temperature range and are the most stable type of ceramic capacitors. Z5U and Y5V dielectric capacitors change value by as much 50% and 60% respectively over their operating temperature range. To use a ceramic chip capacitor with Y5V dielectric, the value must be much higher than an X7R ceramic or a tantalum capacitor to ensure the same minimum capacitance value over the operating temperature range. Tantalum capacitors have a very stable dielectric (10% over their operating temperature range) and can also be used with this device.

### ENABLE/SHUTDOWN

The LMS5258 has an active high enable pin that allows the regulator to be disabled. Applying a Logic Level low (<0.4 V) to the Shutdown pin will cause the output to turn off, in this state current consumed by the regulator goes nearly to zero. Applying a logic level high (>2.0) enables the output voltage. The enable/shutdown pin can't be left floating; a floating enable pin may cause an indeterminate state on the output.

#### ACTIVE SHUTDOWN

The LMS5258 designed with a N-channel MOSFET that acts as a shutdown clamp. The N-channel turns on when the device is disabled to allow the output capacitor and load to discharge.

### POWER GOOD

The power good output is an open-drain output. It is designed essentially to work as a power-on reset generator once the regulated voltage was up and/ or a fault condition. When a fault condition and an undervoltage detection occur, the output of the power good pin goes low. The power good output comes back up once the output has reached 97% of its nominal value and 1ms to 5ms delay has passed , see timing diagram.

The LMS5258 internal circuit monitors overcurrent, temperature and falling output voltage. If one of these conditions is flaged that indicates a fault condition.

The flaged condition output is fed into an onchip delay circuit that drives the open drain output transistor.

### TRANSIENT RESPONSE

The LMS5258 implements a unique output stage to dramatically improve transient response recovery time. The output is a totem-pole configuration with a P-channel MOSFET pass device and a N-channel MOSFET clamp. The N-channel clamp is a significantly smaller device that prevents the output voltage from overshooting when a heavy load is removed. This feature helps to speed up the transient response by significantly decreasing transient response recovery time during the transition from heavy load to light load.

### THERMAL BEHAVIOR

The LMS5258 regulator has internal thermal shutdown to protect the device from over heating. Under all operating conditions, the maximum junction temperature of the LMS5258 must be below 125°C. Maximum power dissipation can be calculated based on the output current and the voltage drop across the part. The maximum power dissipation is

### $\mathsf{P}_{\mathsf{D}(\mathsf{MAX})} = (\mathsf{T}_{\mathsf{J}(\mathsf{MAX})} - \mathsf{T}_{\mathsf{A}})/\theta_{\mathsf{J}\mathsf{A}}$

$\theta_{JA}$  is the junction-to-ambient thermal resistance, 235°C/W for the LMS5258 in the SOT23-5 package.  $T_A$  is the maximum ambient temperature T  $_{J(MAX)}$  is the maximum junction temperature of the die, 125°C.

When operating the LMS5258 at room temperature, the maximum power dissipation is 425mW.

The actual power dissipated by the regulator is

$$P_{D} = (V_{IN} - V_{OUT}) I_{L} + V_{IN} I_{GND}$$

Substituting  $P_{D(MAX)}$ , determined above, for  $P_D$  and solving for the operating condition that are critical to the application will give the maximum operating conditions for the regulator circuit. To prevent the device from entering thermal shutdown, maximum power dissipation cannot be exceeded.

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.