#### TENTATIVE TOSHIBA MOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

512Mbits Network FCRAM1 (SSTL\_2 Interface) - 4,194,304-WORDS × 8 BANKS × 16-BITS

### DESCRIPTION

Network FCRAM<sup>TM</sup> is Double Data Rate Fast Cycle Random Access Memory. TC59LM913AMB is Network FCRAM<sup>TM</sup> containing 536,870,912 memory cells. TC59LM913AMB is organized as 4,194,304-words  $\times$  8 banks  $\times$  16 bits. TC59LM913AMB feature a fully synchronous operation referenced to clock edge whereby all operations are synchronized at a clock input which enables high performance and simple user interface coexistence. TC59LM913AMB can operate fast core cycle compared with regular DDR SDRAM.

TC59LM913AMB is suitable for Network, Server and other applications where large memory density and low power consumption are required. The Output Driver for Network FCRAM<sup>TM</sup> is capable of high quality fast data transfer under light loading condition.

### **FEATURES**

| PARAMETER         |                                       | TC59LM913AMB-50 |

|-------------------|---------------------------------------|-----------------|

| t <sub>CK</sub>   | Clock Cycle Time (min)                | 5.0 ns          |

| t <sub>RC</sub>   | Random Read/Write Cycle Time (min)    | 25.0 ns         |

| t <sub>RAC</sub>  | Random Access Time (max)              | 22.0 ns         |

| I <sub>DD1S</sub> | Operating Current (single bank) (max) | 240 mA          |

| I <sub>DD2P</sub> | Power Down Current (max)              | 80 mA           |

| I <sub>DD6</sub>  | Self-Refresh Current (max)            | 20 mA           |

#### • Fully Synchronous Operation

- Double Data Rate (DDR)

- Data input/output are synchronized with both edges of L/UDQS.

- Differential Clock (CLK and CLK) inputs

CS, FN and all address input signals are sampled on the positive edge of CLK.

Output data (DQs, LDQS and UDQS) is aligned to the crossings of CLK and CLK.

- Fast clock cycle time of 5 ns minimum

- Clock: 200 MHz maximum

- Data: 400 Mbps/pin maximum

- Fast cycle and Short Latency

- Eight independent banks operation When BA2 input assign to A14 input, TC59LM913AMB can function as 4bank device (Keep backward compatibility of address assignment to 256Mb)

- Bidirectional Data Strobe Signal

- Distributed Auto-Refresh cycle in 3.9 μs

- Self-Refresh

•

- Power Down Mode

- Variable Write Length Control

- Write Latency = CAS Latency-1

- Programable CAS Latency and Burst Length CAS Latency = 4

- Burst Length = 2, 4

- Organization: TC59LM913AMB : 4,194,304 words × 8 banks × 16 bits

- Power Supply Voltage VDD:  $2.5 V \pm 0.15V$

- VDDQ:  $2.5 V \pm 0.15 V$

- 2.5 V CMOS I/O comply with SSTL\_2 (half strength driver)

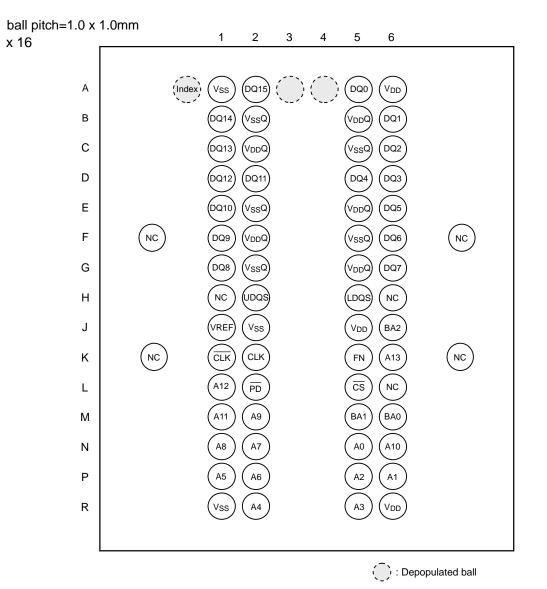

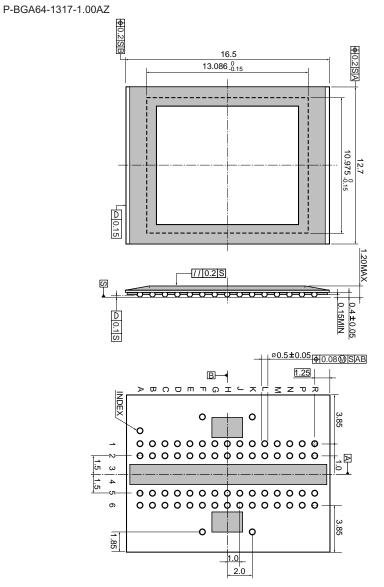

- Package: 60Ball BGA, 1mm × 1mm Ball pitch (P–BGA64–1317–1.00AZ)

Notice : FCRAM is trademark of Fujitsu Limited, Japan.

### PIN NAMES

| PIN      | NAME               |

|----------|--------------------|

| A0~A13   | Address Input      |

| BA0~BA2  | Bank Address       |

| DQ0~DQ15 | Data Input/Output  |

| CS       | Chip Select        |

| FN       | Function Control   |

| PD       | Power Down Control |

| CLK, CLK | Clock Input        |

| PIN              | NAME                            |

|------------------|---------------------------------|

| UDQS, LDQS       | Write/Read Data Strobe          |

| V <sub>DD</sub>  | Power (+2.5 V)                  |

| V <sub>SS</sub>  | Ground                          |

| V <sub>DDQ</sub> | Power (+2.5 V) (for I/O buffer) |

| V <sub>SSQ</sub> | Ground (for I/O buffer)         |

| V <sub>REF</sub> | Reference Voltage               |

| NC               | Not Connected                   |

4 bank operation can be performed using BA2 as A14.

### PIN ASSIGNMENT (TOP VIEW)

Rev 1.1

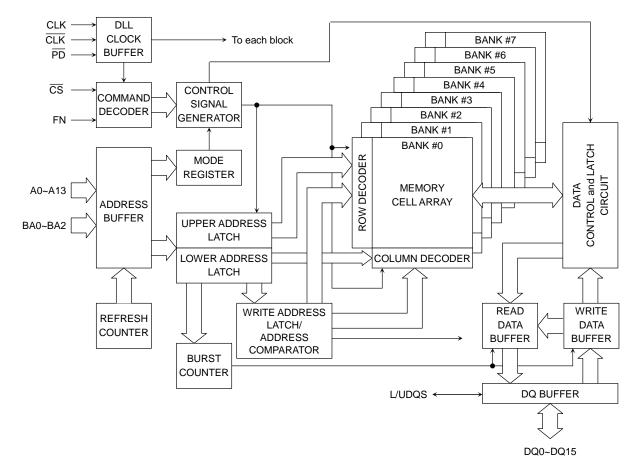

### **BLOCK DIAGRAM**

Note: TC59LM913AMB configuration is 8 Bank of 16384 x 256 x 16 of cell array with DQ pins numbered DQ0~DQ15.

### **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL              | PARAMETER                             | RATING                     | UNIT | NOTES |

|---------------------|---------------------------------------|----------------------------|------|-------|

| V <sub>DD</sub>     | Power Supply Voltage                  | -0.3~3.3                   | V    |       |

| V <sub>DDQ</sub>    | Power Supply Voltage (for I/O buffer) | -0.3~V <sub>DD</sub> + 0.3 | V    |       |

| V <sub>IN</sub>     | Input Voltage                         | -0.3~V <sub>DD</sub> + 0.3 | V    |       |

| V <sub>OUT</sub>    | Output and I/O pin Voltage            | $-0.3 \sim V_{DDQ} + 0.3$  | V    |       |

| V <sub>REF</sub>    | Input Reference Voltage               | -0.3~V <sub>DD</sub> + 0.3 | V    |       |

| T <sub>CASE</sub>   | Operating Temperature (case)          | 0~85                       | °C   |       |

| T <sub>stg</sub>    | Storage Temperature                   | -55~150                    | °C   |       |

| T <sub>solder</sub> | Soldering Temperature (10 s)          | 260                        | °C   |       |

| PD                  | Power Dissipation                     | 2                          | W    |       |

| IOUT                | Short Circuit Output Current          | ±50                        | mA   |       |

Caution: Conditions outside the limits listed under "ABSOLUTE MAXIMUM RATINGS" may cause permanent damage to the device. The device is not meant to be operated under conditions outside the limits described in the operational section of this specification.

Exposure to "ABSOLUTE MAXIMUM RATINGS" conditions for extended periods may affect device reliability.

### **<u>RECOMMENDED DC, AC OPERATING CONDITIONS</u> (Notes: 1)(T<sub>CASE</sub> = 0~85°C)**

| SYMBOL                | PARAMETER                                              | MIN                       | TYP.                | MAX                       | UNIT | NOTES |

|-----------------------|--------------------------------------------------------|---------------------------|---------------------|---------------------------|------|-------|

| V <sub>DD</sub>       | Power Supply Voltage                                   | 2.35                      | 2.5                 | 2.65                      | V    |       |

| V <sub>DDQ</sub>      | Power Supply Voltage (for I/O buffer)                  | 2.35                      | V <sub>DD</sub>     | V <sub>DD</sub>           | V    |       |

| V <sub>REF</sub>      | Input Reference Voltage                                | $V_{DDQ}/2 \times 96\%$   | V <sub>DDQ</sub> /2 | $V_{DDQ}/2 	imes 104\%$   | V    | 2     |

| V <sub>IH</sub> (DC)  | Input DC High Voltage                                  | V <sub>REF</sub> + 0.2    | _                   | V <sub>DDQ</sub> + 0.2    | V    | 5     |

| V <sub>IL</sub> (DC)  | Input DC Low Voltage                                   | -0.1                      | _                   | V <sub>REF</sub> – 0.2    | V    | 5     |

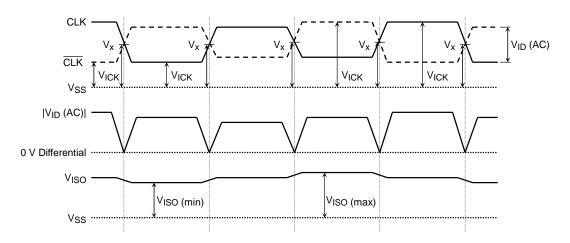

| V <sub>ICK</sub> (DC) | Differential Clock DC Input Voltage                    | -0.1                      | _                   | V <sub>DDQ</sub> + 0.1    | V    | 10    |

| V <sub>ID</sub> (DC)  | Input Differential Voltage.<br>CLK and CLK inputs (DC) | 0.4                       | _                   | V <sub>DDQ</sub> + 0.2    | V    | 7, 10 |

| V <sub>IH</sub> (AC)  | Input AC High Voltage                                  | V <sub>REF</sub> + 0.35   | _                   | V <sub>DDQ</sub> + 0.2    | V    | 3, 6  |

| V <sub>IL</sub> (AC)  | Input AC Low Voltage                                   | -0.1                      | _                   | V <sub>REF</sub> - 0.35   | V    | 4, 6  |

| V <sub>ID</sub> (AC)  | Input Differential Voltage.<br>CLK and CLK inputs (AC) | 0.7                       | _                   | V <sub>DDQ</sub> + 0.2    | V    | 7, 10 |

| V <sub>X</sub> (AC)   | Differential AC Input Cross Point Voltage              | V <sub>DDQ</sub> /2 - 0.2 | _                   | V <sub>DDQ</sub> /2 + 0.2 | V    | 8, 10 |

| V <sub>ISO</sub> (AC) | Differential Clock AC Middle Level                     | V <sub>DDQ</sub> /2 - 0.2 | _                   | V <sub>DDQ</sub> /2 + 0.2 | V    | 9, 10 |

NOTES:

- (1) All voltages referenced to VSS, VSSQ.

- (2)  $V_{REF}$  is expected to track variations in  $V_{DDQ}$  DC level of the transmitting device. Peak to peak AC noise on  $V_{REF}$  may not exceed  $\pm 2\%$   $V_{REF}$  (DC).

- (3) Overshoot limit: VIH (max) = VDDQ + 0.9 V with a pulse width  $\leq$  5 ns.

- (4) Undershoot limit: VIL (min) = -0.9 V with a pulse width  $\leq 5$  ns.

- (5) VIH (DC) and VIL (DC) are levels to maintain the current logic state.

- (6) V<sub>IH</sub> (AC) and V<sub>IL</sub> (AC) are levels to change to the new logic state.

- (7)  $V_{ID}$  is magnitude of the difference between CLK input level and  $\overline{CLK}$  input level.

- (8) The value of V<sub>X</sub> (AC) is expected to equal  $V_{DDQ}/2$  of the transmitting device.

- (9) VISO means  $\{V_{ICK} (CLK) + V_{ICK} (\overline{CLK})\}/2$

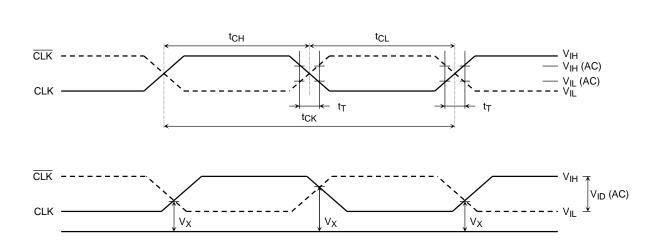

- (10) Refer to the figure below.

(11) In the case of external termination, VTT (termination voltage) should be gone in the range of VREF (DC)  $\pm$  0.04 V.

### <u>CAPACITANCE</u> ( $V_{DD} = 2.5V$ , $V_{DDQ} = 2.5V$ , f = 1 MHz, Ta = 25°C)

| SYMBOL           | PARAMETER                        | MIN | MAX | Delta | UNIT |

|------------------|----------------------------------|-----|-----|-------|------|

| C <sub>IN</sub>  | Input pin Capacitance            | 1.5 | 2.5 | 0.25  | pF   |

| C <sub>INC</sub> | Clock pin (CLK, CLK) Capacitance | 1.5 | 2.5 | 0.25  | pF   |

| C <sub>I/O</sub> | DQ, UDQS, LDQS Capacitance       | 2.5 | 4.0 | 0.5   | pF   |

| C <sub>NC</sub>  | NC pin Capacitance               | _   | 4.0 |       | pF   |

Note: These parameters are periodically sampled and not 100% tested.

# $\frac{\text{RECOMMENDED DC OPERATING CONDITIONS}}{(V_{DD}=2.5V\pm0.15V, V_{DDQ}=2.5V\pm0.15V, T_{CASE}=0{\sim}85^{\circ}\text{C})}$

| SYMBOL            | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                            | MAX | UNIT | NOTES   |      |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|---------|------|

| I <sub>DD1S</sub> | $ \begin{array}{l} Operating Current \\ t_{CK} = min, \ I_{RC} = min \ ; \\ Read/Write command cycling \ ; \\ 0 \ V \leq V_{IN} \leq V_{IL} \ (AC) \ (max), \ V_{IH} \ (AC) \ (min) \leq V_{IN} \leq V_{DDQ} \ ; \\ 1 \ bank \ operation, \ Burst \ length = 4 \ ; \\ Address \ change \ up \ to \ 2 \ times \ during \ minimum \ I_{RC}. \end{array} $                                                                                                              | 240 |      | 1, 2    |      |

| I <sub>DD2N</sub> | $\begin{array}{l} \mbox{Standby Current} \\ t_{CK} = min, \ \overline{CS} \ = V_{IH}, \ \overline{PD} \ = V_{IH} \ ; \\ 0 \ V \leq V_{IN} \leq V_{IL} \ (AC) \ (max), \ V_{IH} \ (AC) \ (min) \leq V_{IN} \leq V_{DDQ} \ ; \\ \mbox{All banks: inactive state } ; \\ \mbox{Other input signals are changed one time during } 4 \times t_{CK}. \end{array}$                                                                                                           | 100 |      | 1, 2    |      |

| I <sub>DD2P</sub> | $ \begin{array}{l} Standby \mbox{ (power down) Current} \\ t_{CK} = min, \ \overline{CS} \ = V_{IH}, \ \overline{PD} \ = V_{IL} \mbox{ (Power Down) }; \\ 0 \ V \leq V_{IN} \leq V_{DDQ} \ ; \\ All \ banks: \ inactive \ state \end{array} $                                                                                                                                                                                                                        | 80  |      | 1, 2    |      |

| I <sub>DD4W</sub> | $ \begin{array}{l} \mbox{Write Operation Current (4 Banks)} \\ \mbox{8 Bank Interleaved continuous burst write operation ;} \\ t_{CK} = min, I_{RC} = min ; \\ \mbox{Burst Length} = 4, \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ $                                                                                                                                                                                                                                        | 350 | mA   | mA      | 1, 2 |

| I <sub>DD4R</sub> | $\begin{array}{l} \mbox{Read Operation Current (4 Banks)} \\ \mbox{8 Bank Interleaved contious burst read operation ;} \\ t_{CK} = min, \ I_{RC} = min, \ I_{OUT} = 0mA ; \\ \mbox{Burst Length} = 4, \ \ \ \ \ \ CAS \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \$                                                                                                                                                                                                         | 350 |      | 1, 2    |      |

| I <sub>DD5B</sub> | $ \begin{array}{l} \text{Burst Auto Refresh Current} \\ \text{Refresh command at every } I_{REFC} \text{ interval }; \\ \underline{t_{CK}} = \min, \ I_{REFC} = \min; \\ \hline CAS \ Latency = 4; \\ 0 \ V \leq V_{IN} \leq V_{IL} \ (AC) \ (max), \ V_{IH} \ (AC) \ (min) \leq V_{IN} \leq V_{DDQ}; \\ \text{Address inputs change up to 2 times during minimum } I_{REFC}. \\ DQ \ and \ L/UDQS \ inputs \ change \ twice \ per \ clock \ cycle. \\ \end{array} $ | 250 |      | 1, 2, 3 |      |

| I <sub>DD6</sub>  | $ \begin{array}{l} \mbox{Self-Refresh Current} \\ \mbox{Self-Refresh mode }; \\ \mbox{$\overline{PD}$} &= 0.2 \ V, 0 \ V \leq V_{IN} \leq V_{DDQ} \end{array} $                                                                                                                                                                                                                                                                                                      | 20  |      | 2       |      |

Notes: 1. These parameters depend on the cycle rate and these values are measured at a cycle rate with the minimum values of t<sub>CK</sub>, t<sub>RC</sub> and I<sub>RC</sub>.

2. These parameters defines the current between  $V_{\mbox{DD}}$  and  $V_{\mbox{SS}}.$

3. I<sub>DD5B</sub> is specified under burst refresh condition. Actual system should use distributed refresh that meet  $t_{REFI}$ specification.

# $\frac{\text{RECOMMENDED DC OPERATING CONDITIONS}}{(V_{DD}=2.5V\pm0.15V, V_{DDQ}=2.5V\pm0.15V, T_{CASE}=0~85^{\circ}\text{C})}$

| SYMBOL               |                                        | PARAMETER                                                               | MIN | MAX | UNIT | NOTES |

|----------------------|----------------------------------------|-------------------------------------------------------------------------|-----|-----|------|-------|

| ILI                  | Input Leakage ( $0 V \le V_{IN} \le V$ | Current $C_{DDQ}$ , all other pins not under test = 0 V)                | -5  | 5   | μA   |       |

| I <sub>LO</sub>      | Output Leakao<br>(Output disabl        | ge Current<br>ed, 0 V $\leq$ V <sub>OUT</sub> $\leq$ V <sub>DDQ</sub> ) | -5  | 5   | μA   |       |

| I <sub>REF</sub>     | VREF Current                           |                                                                         | -5  | 5   | μA   |       |

| I <sub>OH</sub> (DC) | Normal                                 | Output Source DC Current<br>$V_{OH} = V_{DDQ} - 0.4V$                   | -10 | _   |      |       |

| I <sub>OL</sub> (DC) | Output Driver                          | Output Sink DC Current $V_{OL} = 0.4V$                                  | 10  | _   |      |       |

| I <sub>OH</sub> (DC) | Strong                                 | Output Source DC Current<br>V <sub>OH</sub> = V <sub>DDQ</sub> – 0.4V   | -11 | _   |      |       |

| I <sub>OL</sub> (DC) | Output Driver                          | Output Sink DC Current $V_{OL} = 0.4V$                                  | 11  | _   | mA   | 1     |

| I <sub>OH</sub> (DC) | Weaker                                 | Output Source DC Current<br>V <sub>OH</sub> = V <sub>DDQ</sub> – 0.4V   | -8  | _   | ma   | 1     |

| I <sub>OL</sub> (DC) | Output Driver                          | Output Sink DC Current $V_{OL} = 0.4V$                                  | 8   | _   |      |       |

| I <sub>OH</sub> (DC) | Weakest                                | Output Source DC Current<br>V <sub>OH</sub> = V <sub>DDQ</sub> – 0.4V   | -7  | _   |      |       |

| I <sub>OL</sub> (DC) | Output Driver                          | Output Sink DC Current<br>V <sub>OL</sub> = 0.4V                        | 7   | _   |      |       |

Notes: 1. Refer to output driver characteristics for the detail. Output Driver Strength is selected by Extended Mode Register.

# $\frac{AC \ CHARACTERISTICS \ AND \ OPERATING \ CONDITIONS}{(V_{DD} = 2.5V \pm 0.15V, \ V_{DDQ} = 2.5V \pm 0.15V, \ T_{CASE} = 0~85^{\circ}C)}$ (Notes: 1, 2)

| SYMBOL              | PARAMETER                                                              | MIN                                     | MAX                       | UNIT | NOTES |

|---------------------|------------------------------------------------------------------------|-----------------------------------------|---------------------------|------|-------|

| t <sub>RC</sub>     | Random Cycle Time                                                      | 25                                      | _                         |      | 3     |

| t <sub>CK</sub>     | Clock Cycle Time ( $C_L = 4$ )                                         | 5.0                                     | 8.5                       |      | 3     |

| t <sub>RAC</sub>    | Random Access Time                                                     | _                                       | 22.0                      |      | 3     |

| t <sub>CH</sub>     | Clock High Time                                                        | $0.45 \times t_{CK}$                    |                           |      | 3     |

| t <sub>CL</sub>     | Clock Low Time                                                         | $0.45 \times t_{CK}$                    | _                         |      | 3     |

| t <sub>CKQS</sub>   | QS Access Time from CLK                                                | -0.65                                   | 0.65                      |      | 3, 8  |

| t <sub>QSQ</sub>    | Data Output Skew from L/UDQS                                           | _                                       | 0.4                       |      | 4     |

| t <sub>AC</sub>     | Data Access Time from CLK                                              | -0.65                                   | 0.65                      |      | 3, 8  |

| t <sub>OH</sub>     | Data Output Hold Time from CLK                                         | -0.65                                   | 0.65                      |      | 3, 8  |

| t <sub>QSPRE</sub>  | L/UDQS (read) Preamble Pulse Width                                     | $0.9 \times t_{CK} - 0.2$               | $1.1 \times t_{CK} + 0.2$ |      | 3, 8  |

| t <sub>HP</sub>     | CLK half period (minimum of Actual t <sub>CH</sub> , t <sub>CL</sub> ) | min(t <sub>CH</sub> , t <sub>CL</sub> ) | _                         |      | 3     |

| t <sub>QSP</sub>    | L/UDQS (read) Pulse Width                                              | t <sub>HP</sub> - t <sub>QHS</sub>      | _                         |      | 4, 8  |

| t <sub>QSQV</sub>   | Data Output Valid Time from L/UDQS                                     | t <sub>HP</sub> - t <sub>QHS</sub>      | _                         |      | 4, 8  |

| t <sub>QHS</sub>    | DQ Hold Skew factor                                                    | _                                       | 0.55                      | ns   |       |

| t <sub>DQSS</sub>   | L/UDQS (write) Low to High Setup Time                                  | $0.75 \times t_{CK}$                    | $1.25 \times t_{CK}$      |      | 3     |

| t <sub>DSPRE</sub>  | L/UDQS (write) Preamble Pulse Width                                    | $0.4 	imes t_{CK}$                      | _                         |      | 4     |

| t <sub>DSPRES</sub> | L/UDQS First Input Setup Time                                          | 0                                       | _                         |      | 3     |

| t <sub>DSPREH</sub> | L/UDQS First Low Input Hold Time                                       | $0.25 \times t_{CK}$                    | _                         |      | 3     |

| t <sub>DSP</sub>    | L/UDQS High or Low Input Pulse Width                                   | $0.45 \times t_{CK}$                    | $0.55 \times t_{CK}$      |      | 4     |

| t <sub>DSS</sub>    | L/UDQS Input Falling Edge to Clock Setup Time                          | 1.3                                     |                           |      | 3, 4  |

| t <sub>DSPST</sub>  | L/UDQS (write) Postamble Pulse Width                                   | $0.45 \times t_{CK}$                    |                           |      | 4     |

| t <sub>DSPSTH</sub> | L/UDQS (write) Postamble Hold Time                                     | 1.3                                     | —                         |      | 3, 4  |

| t <sub>DSSK</sub>   | UDQS – LDQS Skew (×16)                                                 | $-0.5 \times t_{CK}$                    | $0.5 \times t_{CK}$       |      |       |

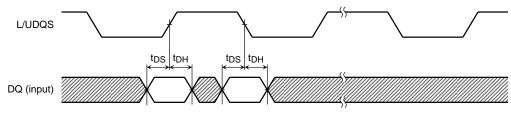

| t <sub>DS</sub>     | Data Input Setup Time from L/UDQS                                      | 0.5                                     | —                         |      | 4     |

| t <sub>DH</sub>     | Data Input Hold Time from L/UDQS                                       | 0.5                                     | —                         |      | 4     |

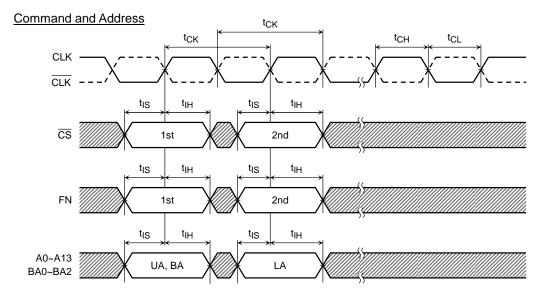

| t <sub>IS</sub>     | Command/Address Input Setup Time                                       | 0.9                                     |                           |      | 3     |

| t <sub>IH</sub>     | Command/Address Input Hold Time                                        | 0.9                                     |                           |      | 3     |

### AC CHARACTERISTICS AND OPERATING CONDITIONS (Notes: 1, 2) (continued)

| SYMBOL             | PARAMETER                                                       |                    | MIN                  | MAX  | UNIT    | NOTES |

|--------------------|-----------------------------------------------------------------|--------------------|----------------------|------|---------|-------|

| t <sub>LZ</sub>    | Data-out Low Impedance Time from CLK                            |                    | -0.65                | _    |         | 3,6,8 |

| t <sub>HZ</sub>    | Data-out High Impedance Time from CLK                           |                    | _                    | 0.65 |         | 3,7,8 |

| t <sub>QSLZ</sub>  | L/UDQS-out Low Impedance Time from CLK                          |                    | -0.65                | —    |         | 3,6,8 |

| t <sub>QSHZ</sub>  | L/UDQS-out High Impedance Time from CLK                         |                    | -0.65                | 0.65 |         | 3,7,8 |

| t QPDH             | Last output to PD High Hold Time                                |                    | 0                    | —    | ns      |       |

| t <sub>PDEX</sub>  | Power Down Exit Time                                            |                    | 0.9                  |      | 115     | 3     |

| t <sub>T</sub>     | Input Transition Time                                           |                    | 0.1                  | 1    |         |       |

| t <sub>FPDL</sub>  | PD Low Input Window for Self-Refresh Entry                      |                    | $-0.5 \times t_{CK}$ | 5    |         | 3     |

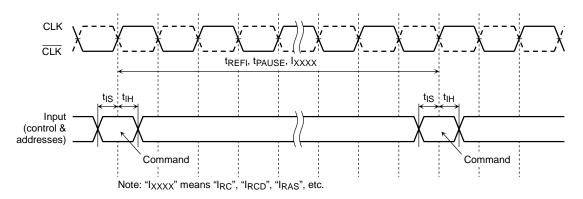

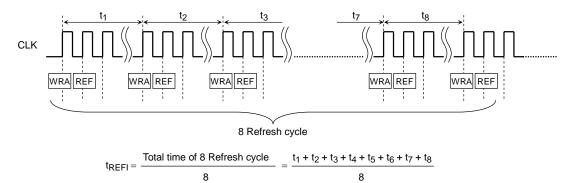

| t <sub>REFI</sub>  | Auto-Refresh Average Interval                                   |                    | 0.4                  | 3.9  | μS      | 5     |

| t <sub>PAUSE</sub> | Pause Time after Power-up                                       |                    | 200                  |      | μο      |       |

| I <sub>RC</sub>    | Random Read/Write Cycle Time<br>(applicable to same bank)       |                    | 5                    | —    |         |       |

| I <sub>RCD</sub>   | RDA/WRA to LAL Command Input Delay<br>(applicable to same bank) |                    | 1                    | 1    |         |       |

| I <sub>RAS</sub>   | LAL to RDA/WRA Command Input Delay<br>(applicable to same bank) |                    |                      | _    |         |       |

| I <sub>RBD</sub>   | Random Bank Access Delay<br>(applicable to other bank)          |                    | 2                    | _    |         |       |

| I <sub>RWD</sub>   | LAL IOIIOWING RDA IO WRA Delay                                  | B <sub>L</sub> = 2 | 2                    | _    |         |       |

| NWD                | (applicable to other bank)                                      | $B_L = 4$          | 3                    | —    |         |       |

| I <sub>WRD</sub>   | LAL following WRA to RDA Delay<br>(applicable to other bank)    |                    | 1                    | _    | - cycle |       |

| I <sub>RSC</sub>   | Mode Register Set Cycle Time                                    |                    | 5                    |      |         |       |

| I <sub>PD</sub>    | PD Low to Inactive State of Input Buffer                        |                    | _                    | 1    |         |       |

| I <sub>PDA</sub>   | PD High to Active State of Input Buffer                         |                    | _                    | 1    | 1       |       |

| I <sub>PDV</sub>   | Power down mode valid from REF command                          |                    | 18                   |      |         |       |

| I <sub>REFC</sub>  | Auto-Refresh Cycle Time                                         |                    | 18                   |      |         |       |

| ICKD               | REF Command to Clock Input Disable at Self-Re                   | efresh Entry       | 16                   | —    |         |       |

| ILOCK              | DLL Lock-on Time (applicable to RDA command)                    | )                  | 200                  |      |         |       |

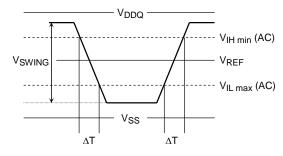

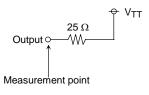

### AC TEST CONDITIONS

| SYMBOL                | PARAMETER                                   | VALUE                   | UNIT | NOTES |

|-----------------------|---------------------------------------------|-------------------------|------|-------|

| V <sub>IH (min)</sub> | Input High Voltage (minimum)                | V <sub>REF</sub> + 0.35 | V    |       |

| V <sub>IL (max)</sub> | Input Low Voltage (maximum)                 | V <sub>REF</sub> - 0.35 | V    |       |

| V <sub>REF</sub>      | Input Reference Voltage                     | V <sub>DDQ</sub> /2     | V    |       |

| V <sub>TT</sub>       | Termination Voltage                         | V <sub>REF</sub>        | V    |       |

| V <sub>SWING</sub>    | Input Signal Peak to Peak Swing             | 1.0                     | V    |       |

| Vr                    | Differential Clock Input Reference Level    | V <sub>X</sub> (AC)     | V    |       |

| V <sub>ID</sub> (AC)  | Input Differential Voltage                  | 1.5                     | V    |       |

| SLEW                  | Input Signal Minimum Slew Rate              | 1.0                     | V/ns |       |

| V <sub>OTR</sub>      | Output Timing Measurement Reference Voltage | V <sub>DDQ</sub> /2     | V    | 9     |

AC Test Load

$SLEW = (V_{IH min} (AC) - V_{IL max} (AC)) / \Delta T$

#### NOTES:

- (2) If the result of nominal calculation with regard to t<sub>CK</sub> contains more than one decimal place, the result is rounded up to the nearest decimal place.

(i.e., t<sub>DQSS</sub> = 0.75 × t<sub>CK</sub>, t<sub>CK</sub> = 5 ns, 0.75 × 5 ns = 3.75 ns is rounded up to 3.8 ns.)

(3) These parameters are measured from the differential clock (CLK and  $\overline{\text{CLK}}$ ) AC cross point.

- (4) These parameters are measured from signal transition point of DS crossing V<sub>REF</sub> level.

- (5) The t<sub>REFI</sub> (max) applies to equally distributed refresh method. The t<sub>REFI</sub> (min) applies to both burst refresh method and distributed refresh method. In such case, the average interval of eight consecutive Auto-Refresh commands has to be more than 400 ns always. In other words, the number of Auto-Refresh cycles which can be performed within 3.2 μs (8 × 400 ns) is to 8 times in the maximum.

- (6) Low Impedance State is specified at  $V_{DDQ}/2 \pm 0.2$  V from steady state.

- (7) High Impedance State is specified where output buffer is no longer driven.

- (8) These parameters depend on the clock jitter. These parameters are measured at stable clock.

- (9) Output timing is measured by using Normal driver strength.

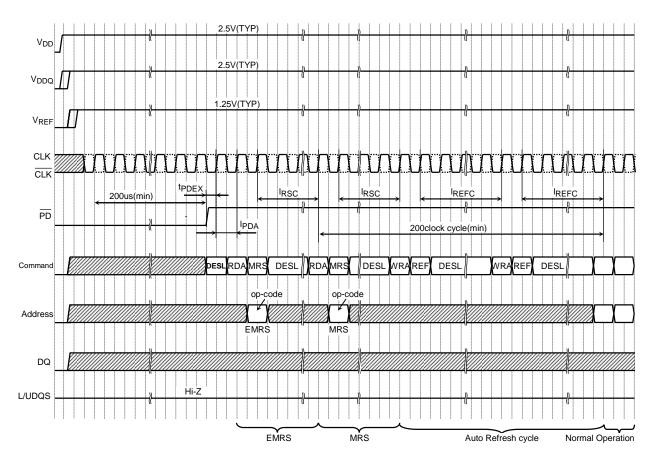

### POWER UP SEQUENCE

- (1) As for  $\overline{PD}$ , being maintained by the low state ( $\leq 0.2$  V) is desirable before a power-supply injection.

- (2) Apply  $V_{DD}$  before or at the same time as  $V_{DDQ}$ .

- (3) Apply  $V_{DDQ}$  before or at the same time as  $V_{REF}$ .

- (4) Start clock (CLK,  $\overline{\text{CLK}}$ ) and maintain stable condition for 200  $\mu$ s (min).

- (5) After stable power and clock, apply DESL and take  $\overline{PD} = H$ .

- (6) Issue EMRS to enable DLL and to define driver strength. (Note: 1)

- (7) Issue MRS for set CAS latency (CL), Burst Type (BT), and Burst Length (BL). (Note: 1)

- (8) Issue two or more Auto-Refresh commands (Note: 1).

- (9) Ready for normal operation after 200 clocks from Extended Mode Register programming.

#### NOTES:

- (1) Sequence 6, 7 and 8 can be issued in random order.

- (2) L = Logic Low, H = Logic High

### **TIMING DIAGRAMS**

### Input Timing

Data

Timing of the CLK, CLK

Refer to the Command Truth Table.

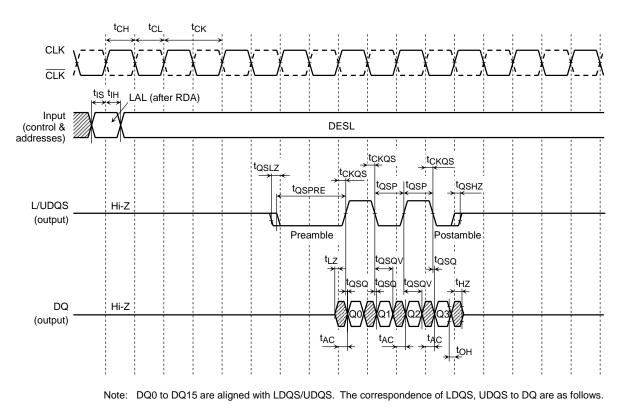

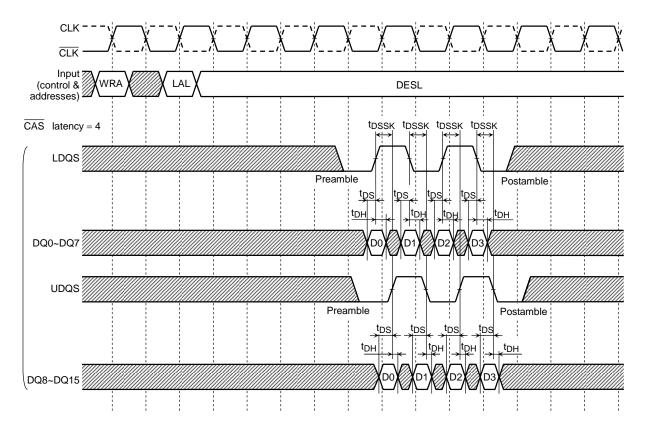

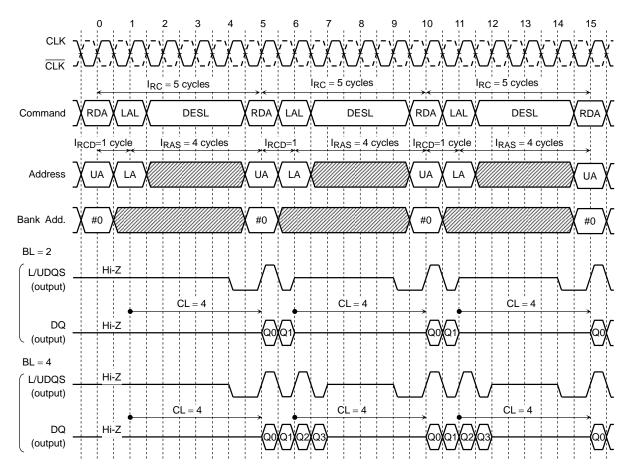

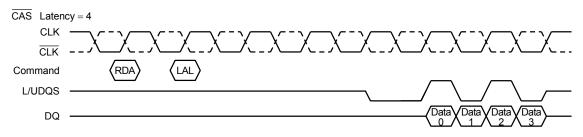

### Read Timing (Burst Length = 4)

| LDQS | DQ0~DQ7  |

|------|----------|

| UDQS | DQ8~DQ15 |

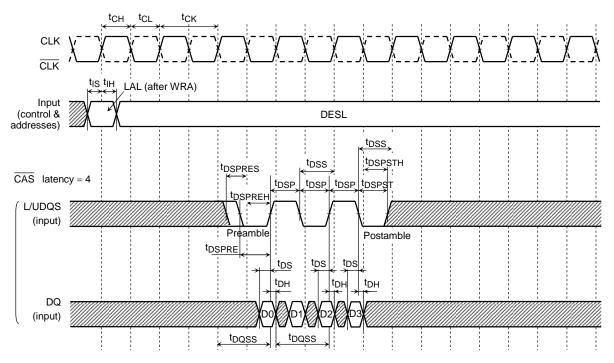

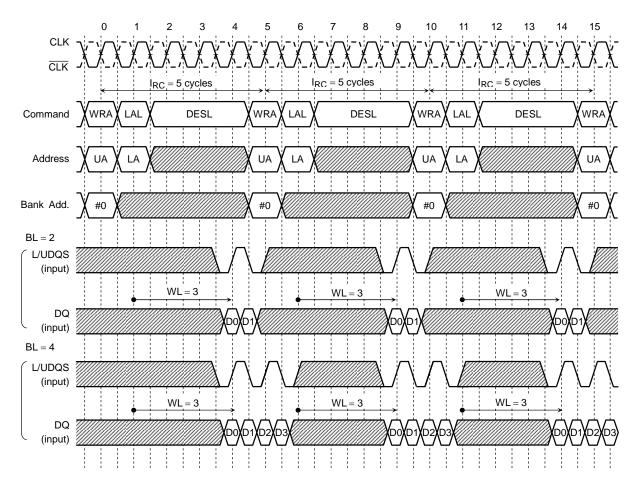

### Write Timing (Burst Length = 4)

Note: DQ0 to DQ15 are aligned with LDQS/UDQS. The correspondence of LDQS, UDQS to DQ are as follows.

| LDQS | DQ0~DQ7  |

|------|----------|

| UDQS | DQ8~DQ15 |

### tREFI, TPAUSE, IXXXX Timing

### Write Timing (x16 device) (Burst Length =4)

### FUNCTION TRUTH TABLE (Notes: 1, 2, 3)

#### Command Truth Table (Notes: 4)

#### • The First Command

| SYMBOL | FUNCTION              | CS | FN | BA1~BA0 | A0 BA2 A13~A9 |    | A8 | A7~A0 | NOTES |

|--------|-----------------------|----|----|---------|---------------|----|----|-------|-------|

| DESL   | Device Deselect       | н  | ×  | ×       | ×             | ×  | ×  | ×     | -     |

| RDA    | Read with Auto-close  | L  | н  | BA      | BA            | UA | UA | UA    | -     |

| WRA    | Write with Auto-close | L  | L  | BA      | BA            | UA | UA | UA    | -     |

#### • The Second Command (The next clock of RDA or WRA command)

| SYMBOL | FUNCTION            | CS | FN | BA1~BA0 | BA2 | A13~A11 | A10~A9 | A8 | A7~A0 | NOTES |

|--------|---------------------|----|----|---------|-----|---------|--------|----|-------|-------|

| LAL    | Lower Address Latch | н  | ×  | ×       | V   | V       | ×      | ×  | LA    | -     |

| REF    | Auto-Refresh        | L  | ×  | ×       | ×   | ×       | ×      | ×  | ×     | -     |

| MRS    | Mode Register Set   | L  | ×  | V       | L   | L       | L      | L  | V     | -     |

Notes: 1. L = Logic Low, H = Logic High,  $\times$  = either L or H, V = Valid (specified value), BA = Bank Address, UA = Upper Address, LA = Lower Address

2. All commands are assumed to issue at a valid state.

3. All inputs for command (excluding SELFX and PDEX) are latched on the crossing point of differential clock input where CLK goes to High.

4. Operation mode is decided by the combination of 1st command and 2nd command. Refer to "STATE DIAGRAM" and the command table below.

#### Read Command Table

| COMMAND (SYMBOL) | MMAND (SYMBOL) CS FN BA1~BA0 BA2 A13~A9 |   | A8 | A7~A0 | NOTES |    |    |   |

|------------------|-----------------------------------------|---|----|-------|-------|----|----|---|

| RDA (1st)        | L H BA BA UA                            |   | UA | UA    | UA    | -  |    |   |

| LAL (2nd)        | н                                       | × | ×  | ×     | ×     | LA | LA | 5 |

Note 5 : For x16 device, A8 is "X" (either L or H).

### Write Command Table

| COMMAND(SYMBOL) | CS | FN | BA1~BA0 | BA2  | A13  | A12  | A11  | A10~A8 | A7~A0 | NOTES |

|-----------------|----|----|---------|------|------|------|------|--------|-------|-------|

| WRA (1st)       | L  | L  | BA      | UA   | UA   | UA   | UA   | UA     | UA    | -     |

| LAL (2nd)       | н  | ×  | ×       | LVW0 | LVW1 | UVW0 | UVW1 | ×      | LA    | -     |

Notes: 6. BA2, A13 ~ A11 are used for Variable Write Length (VW) control at Write Operation.

### FUNCTION TRUTH TABLE (continued)

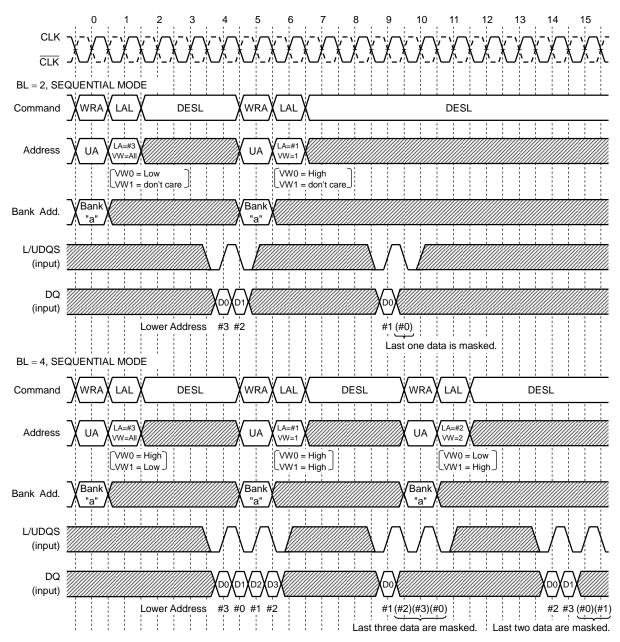

### VW Truth Table

| Burst Length | Function              | VW0 | VW1 |

|--------------|-----------------------|-----|-----|

| BL=2         | Write All Words       | L   | ×   |

| DL=2         | Write First One Word  | Н   | ×   |

|              | Reserved              | L   | L   |

| BL=4         | Write All Words       | н   | L   |

| DL=4         | Write First Two Words | L   | Н   |

|              | Write First One Word  | Н   | Н   |

Note 7 : LVW0 and LVW1 control DQ0~DQ7. UVW0 and UVW1 control DQ8~DQ15.

### Mode Register Set Command Table

| COMMAND (SYMBOL) | CS | FN | BA2~BA0 | A13~A8 | A7~A0 | NOTES |

|------------------|----|----|---------|--------|-------|-------|

| RDA (1st)        | L  | Н  | ×       | ×      | ×     |       |

| MRS (2nd)        | L  | ×  | V       | V      | V     | 8     |

Notes: 8. Refer to "MODE REGISTER TABLE".

### Auto-Refresh Command Table

| FUNCTION     | COMMAND   | CURRENT | P     | PD |    | FN  | BA2~BA0 | A13~A8 | A7~A0 | NOTES |

|--------------|-----------|---------|-------|----|----|-----|---------|--------|-------|-------|

| FUNCTION     | (SYMBOL)  | STATE   | n – 1 | n  | CS | FIN | BAZ~BAU | A13~A8 | A7~A0 | NUTES |

| Active       | WRA (1st) | Standby | н     | Н  | L  | L   | ×       | ×      | ×     |       |

| Auto-Refresh | REF (2nd) | Active  | н     | Н  | L  | ×   | ×       | ×      | ×     |       |

### Self-Refresh Command Table

| FUNCTION              | COMMAND   | CURRENT      | CURRENT PD CS FN B |   | BA2~BA0 | A13~A8 | A7~A0   | NOTES  |       |       |

|-----------------------|-----------|--------------|--------------------|---|---------|--------|---------|--------|-------|-------|

| FONCTION              | (SYMBOL)  | STATE        | n – 1              | n | 03      | FIN    | BAZ~BAU | A13~A0 | A7~A0 | NOTES |

| Active                | WRA (1st) | Standby      | Н                  | Н | L       | L      | ×       | ×      | ×     |       |

| Self-Refresh Entry    | REF (2nd) | Active       | н                  | L | L       | ×      | ×       | ×      | ×     | 9, 10 |

| Self-Refresh Continue | _         | Self-Refresh | L                  | L | ×       | ×      | ×       | ×      | ×     |       |

| Self-Refresh Exit     | SELFX     | Self-Refresh | L                  | Н | н       | ×      | ×       | ×      | ×     | 11    |

### Power Down Table

| FUNCTION            | COMMAND  | CURRENT    | $\begin{array}{c c} CURRENT & \overline{PD} & \\ STATE & n-1 & n \end{array}  \overrightarrow{CS}  FN  BA2-BA0 \end{array}$ |   | A13~A8  | A7~A0  | NOTES |       |   |    |

|---------------------|----------|------------|-----------------------------------------------------------------------------------------------------------------------------|---|---------|--------|-------|-------|---|----|

| FUNCTION            | (SYMBOL) | STATE      |                                                                                                                             |   | BAZ~BAU | A13~A0 | A7~A0 | NUTES |   |    |

| Power Down Entry    | PDEN     | Standby    | н                                                                                                                           | L | Н       | ×      | ×     | ×     | × | 10 |

| Power Down Continue | _        | Power Down | L                                                                                                                           | L | ×       | ×      | ×     | ×     | × |    |

| Power Down Exit     | PDEX     | Power Down | L                                                                                                                           | Н | Н       | ×      | ×     | ×     | × | 11 |

Notes: 9.  $\overline{PD}$  has to be brought to Low within t<sub>FPDL</sub> from REF command.

10.  $\overline{PD}$  should be brought to Low after DQ's state turned high impedance.

11. When  $\overline{PD}$  is brought to High from Low, this function is executed asynchronously.

### **FUNCTION TRUTH TABLE** (continued)

|                            | P      | D      | CS |    |                  | COMMAND    | ACTION                                                       | NOTES |

|----------------------------|--------|--------|----|----|------------------|------------|--------------------------------------------------------------|-------|

| CURRENT STATE              | n – 1  | n      | LS | FN | ADDRESS          | COMMAND    | ACTION                                                       | NOTES |

|                            | Н      | Н      | Н  | ×  | ×                | DESL       | NOP                                                          |       |

|                            | Н      | Н      | L  | Н  | BA, UA           | RDA        | Row activate for Read                                        |       |

| Idle                       | н      | Н      | L  | L  | BA, UA           | WRA        | Row activate for Write                                       |       |

|                            | Н      | L      | Н  | ×  | ×                | PDEN       | Power Down Entry                                             | 12    |

|                            | Н      | L      | L  | ×  | ×                | —          | Illegal                                                      |       |

|                            | L      | ×      | ×  | ×  | ×                | _          | Refer to Power Down State                                    |       |

|                            | Н      | Н      | Н  | ×  | LA               | LAL        | Begin Read                                                   |       |

|                            | Н      | Н      | L  | ×  | Op-code          | MRS/EMRS   | Access to Mode Register                                      |       |

| Row Active for Read        | Н      | L      | Н  | ×  | ×                | PDEN       | Illegal                                                      |       |

|                            | н      | L      | L  | ×  | ×                | MRS/EMRS   | Illegal                                                      |       |

|                            | L      | ×      | ×  | ×  | ×                | —          | Invalid                                                      |       |

|                            | Н      | Н      | Н  | ×  | LA               | LAL        | Begin Write                                                  |       |

|                            | Н      | Н      | L  | ×  | ×                | REF        | Auto-Refresh                                                 |       |

| Row Active for Write       | Н      | L      | Н  | ×  | ×                | PDEN       | Illegal                                                      |       |

|                            | н      | L      | L  | ×  | ×                | REF (self) | Self-Refresh Entry                                           |       |

|                            | L      | ×      | ×  | ×  | ×                | —          | Invalid                                                      |       |

|                            | н      | Н      | Н  | ×  | ×                | DESL       | Continue Burst Read to End                                   |       |

|                            | н      | н      | L  | н  | BA, UA           | RDA        | Illegal                                                      | 13    |

| <b>_</b>                   | н      | Н      | L  | L  | BA, UA           | WRA        | Illegal                                                      | 13    |

| Read                       | Н      | L      | Н  | ×  | ×                | PDEN       | Illegal                                                      |       |

|                            | н      | L      | L  | ×  | ×                |            | Illegal                                                      |       |

|                            | L      | ×      | ×  | ×  | ×                |            | Invalid                                                      |       |

|                            | н      | Н      | Н  | ×  | ×                | DESL       | Data Write & Continue Burst Write to                         |       |

|                            | н      | н      | L  | Н  | BA, UA           | RDA        | End<br>Illegal                                               | 13    |

| Write                      | н      | н      | L  | L  | BA, UA           | WRA        | Illegal                                                      | 13    |

| VVIILE                     | Н      | L      | H  | ×  | ×                | PDEN       | Illegal                                                      | 13    |

|                            | н      | L      | L  | ×  | ×                |            | Illegal                                                      |       |

|                            | L      | ×      | ×  | ×  | ×                |            | Invalid                                                      |       |

|                            | H      | Ĥ      | Ĥ  | ×  | ×                | DESL       | NOP $\rightarrow$ Idle after I <sub>REFC</sub>               |       |

|                            | Н      | н      | L  | Ĥ  | A<br>BA, UA      | RDA        |                                                              |       |

|                            | Н      | н      | L  | L  | BA, UA<br>BA, UA | WRA        | Illegal                                                      |       |

| Auto-Refreshing            | Н      | L      | H  | ×  | ×                | PDEN       | Self-Refresh Entry                                           | 14    |

|                            | Н      | L      | L  | ×  | ×                |            | Illegal                                                      | 14    |

|                            | L      |        |    |    |                  |            | Refer to Self-Refreshing State                               |       |

|                            | H      | ×      | ×  | ×  | ×                | DESL       | NOP $\rightarrow$ Idle after I <sub>RSC</sub>                |       |

|                            |        |        |    | ×  |                  | RDA        |                                                              |       |

| Mada Daviatan              | H<br>H | H<br>H | L  | H  | BA, UA<br>BA, UA | WRA        | Illegal                                                      |       |

| Mode Register<br>Accessing |        |        |    | _  | ,                |            | Illegal                                                      |       |

| / locessing                | H      |        | H  | ×  | ×                | PDEN       | Illegal<br>Illegal                                           |       |

|                            | н      | L      | L  | ×  | ×                |            | -                                                            |       |

|                            | L      | ×      | ×  | ×  | ×                |            | Invalid                                                      |       |

|                            | н      | ×      | ×  | ×  | ×                | —          | Invalid                                                      |       |

| Power Down                 | L      | L      | ×  | ×  | ×                | —          | Maintain Power Down Mode                                     |       |

|                            | L      | Н      | Н  | ×  | ×                | PDEX       | Exit Power Down Mode $\rightarrow$ Idle after<br>tPDEX       |       |

|                            | L      | Н      | L  | ×  | ×                |            | Illegal                                                      |       |

|                            | н      | ×      | ×  | ×  | ×                | _          | Invalid                                                      |       |

| 0 K D K                    | L      | L      | ×  | ×  | ×                | _          | Maintain Self-Refresh                                        |       |

| Self-Refreshing            | L      | H      | Н  | ×  | ×                | SELFX      | Exit Self-Refresh $\rightarrow$ Idle after I <sub>REFC</sub> |       |

|                            | L      | н      | L  | ×  | ×                |            | Illegal                                                      |       |

Notes: 12. Illegal if any bank is not idle.

13. Illegal to bank in specified states; Function may be legal in the bank inidicated by Bank Address (BA).

14. Illegal if t<sub>FPDL</sub> is not satisfied.

### **MODE REGISTER TABLE**

Regular Mode Register (Notes: 1)

| AD | DRESS   |    | BA1 <sup>*1</sup> | BA0 <sup>*1</sup> | BA2, A13~,       | -A8 A <sup>-</sup> | 7 <sup>*3</sup> | A6~ | -A4 | A3            | A2~A0  |

|----|---------|----|-------------------|-------------------|------------------|--------------------|-----------------|-----|-----|---------------|--------|

| Re | egister |    | 0                 | 0                 | 0                | Т                  | Ē               | С   | L   | BT            | BL     |

|    |         |    |                   |                   |                  |                    |                 |     |     |               |        |

|    |         | A7 | TEST N            | NODE (TE)         |                  |                    |                 | A3  | BU  | RST TYPE (BT) |        |

|    |         | 0  | Regula            | ar (default)      |                  |                    |                 | 0   |     | Sequential    |        |

|    |         | 1  | Test N            | lode Entry        |                  |                    |                 | 1   |     | Interleave    |        |

| _  |         |    |                   |                   |                  |                    |                 |     |     |               |        |

| Γ  | A6      | A5 | A4                | CAS LATEN         | NCY (CL)         |                    | A2              | A1  | A0  | BURST LENGT   | H (BL) |

| Γ  | 0       | 0  | ×                 | Reserve           | ed <sup>*2</sup> |                    | 0               | 0   | 0   | Reserved      | 2      |

| F  | 0       | 1  | 0                 | Reserve           |                  |                    | 0               | 0   | 1   | 2             |        |

| Γ  | 0       | 1  | 1                 | Reserve           | ed <sup>*2</sup> |                    | 0               | 1   | 0   | 4             |        |

|    | 1       | 0  | 0                 | 4                 |                  |                    | 0               | 1   | 1   | Reserved      | 2      |

|    | 1       | 0  | 1                 | Reserve           |                  |                    | 1               | ×   | ×   |               |        |

|    | 1       | 1  | 0                 | Reserve           |                  | -                  |                 |     |     |               |        |

|    | 1       | 1  | 1                 | Reserve           | ed <sup>*2</sup> |                    |                 |     |     |               |        |

### Extended Mode Register (Notes: 4)

|          | BA1 <sup>*4</sup> | BA0 <sup>*4</sup> | BA2, / | A13~A7 | A6                   | A5~A2             | A1           | A0 <sup>*5</sup> |

|----------|-------------------|-------------------|--------|--------|----------------------|-------------------|--------------|------------------|

| Register | 0                 | 1                 |        | 0      | DIC                  | 0                 | DIC          | DS               |

|          |                   |                   |        |        |                      |                   |              |                  |

|          |                   | A                 | .6 A   | 1 OU   | ITPUT DRIVE          | IMPEDANCE CO      | ONTROL (DIC) |                  |

|          |                   | (                 | ) (    | )      | Normal Output Driver |                   |              |                  |

|          |                   | (                 | 0 1    |        | Stro                 | ong Output Drive  | r            |                  |

|          |                   |                   | 1 (    | )      | Wea                  | ker Output Drive  | r            |                  |

|          |                   |                   | 1 1    |        | Wea                  | kest Output Drive | er           |                  |

| A0 | DLL SWITCH (DS) |

|----|-----------------|

| 0  | DLL Enable      |

| 1  | DLL Disable     |

Notes: 1. Regular Mode Register is chosen using the combination of BA0 = 0 and BA1 = 0.

- 2. "Reserved" places in Regular Mode Register should not be set.

- 3. A7 in Regular Mode Register must be set to "0" (low state).

- Because Test Mode is specific mode for supplier.

- 4. Extended Mode Register is chosen using the combination of BA0 = 1 and BA1 = 0.

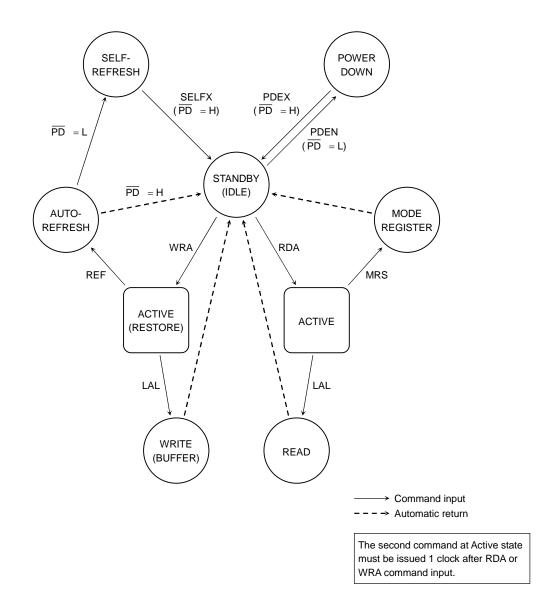

### STATE DIAGRAM

### TIMING DIAGRAMS

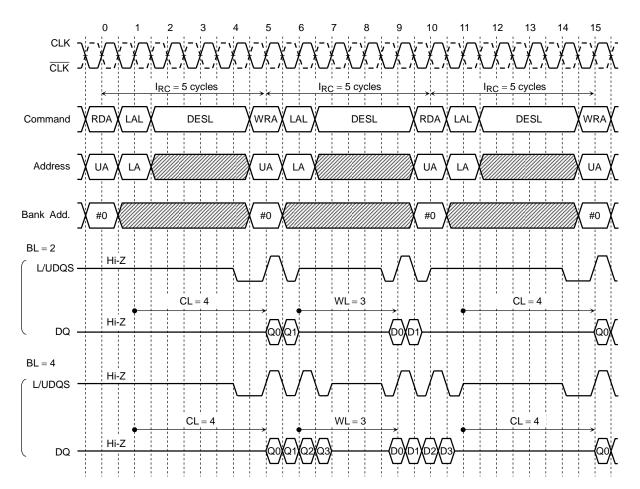

### SINGLE BANK READ TIMING

### SINGLE BANK WRITE TIMING

### SINGLE BANK READ-WRITE TIMING

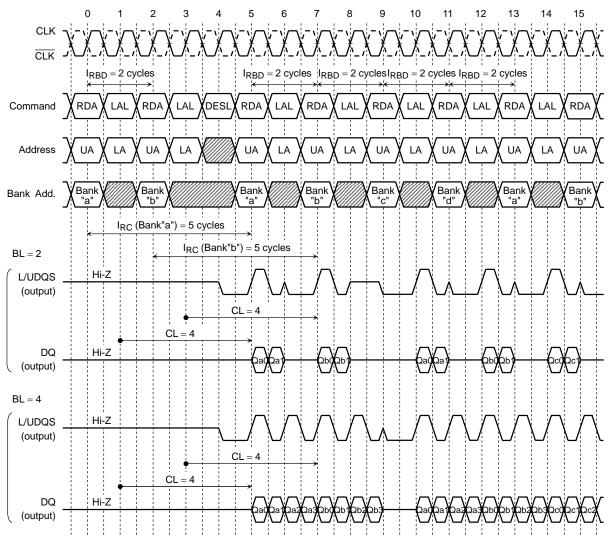

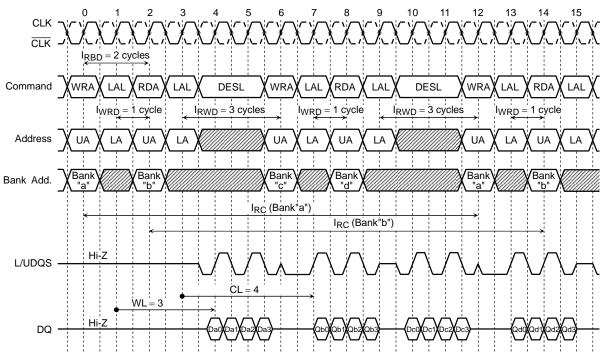

### MULTIPLE BANK READ TIMING

Note:  $\ensuremath{\mathsf{I}_{\mathsf{RC}}}$  to the same bank must be satisfied.

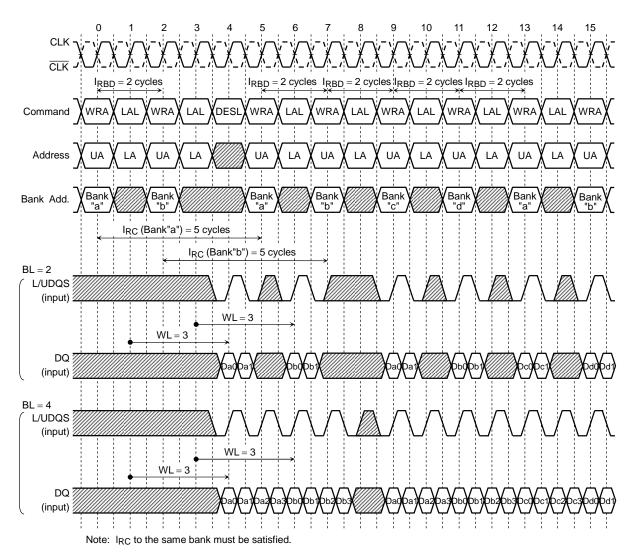

### MULTIPLE BANK WRITE TIMING

### <u>TOSHIBA</u>

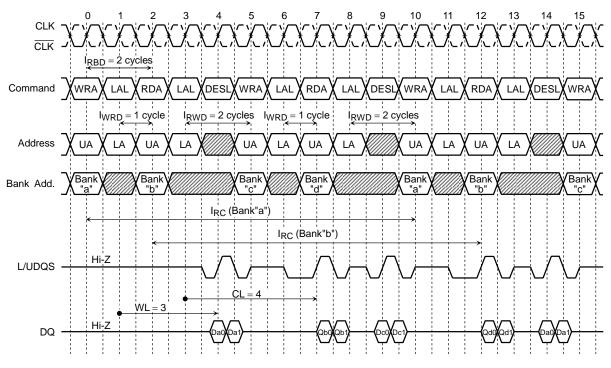

### MULTIPLE BANK READ-WRITE TIMING (BL = 2)

Note: I<sub>RC</sub> to the same bank must be satisfied.

Rev 1.1 2005-11-08 27/46

### <u>TOSHIBA</u>

### MULTIPLE BANK READ-WRITE TIMING (BL = 4)

Note:  $I_{RC}$  to the same bank must be satisfied.

Rev 1.1 2005-11-08 28/46

### WRITE with VARIAVLE WRITE LENGTH (VW) CONTROL

Note: L/UDQS input must be continued till end of burst count even if some of laster data is masked.

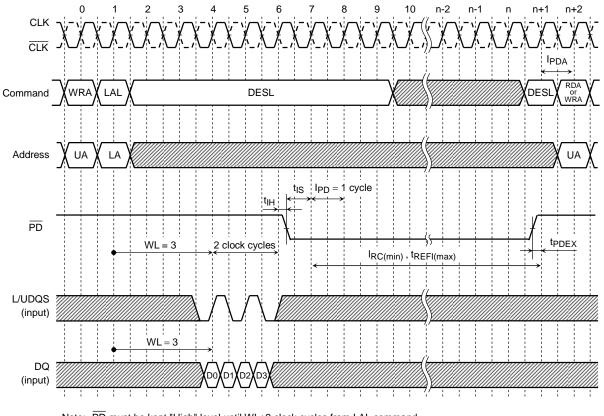

#### POWER DOWN TIMING (CL = 4, BL = 4) Read cycle to Power Down Mode 10 n-2 n+2 3 n-1 n n+1 CLK CLK IPDA RDA or WRA Command RDA DESL DESL LAL Address UA LA UA $I_{PD} = 1$ cycle t<sub>IS</sub> t<sub>IH</sub> PD **t**QPDH **t**PDEX IRC(min) , tREFI(max) Hi-Z L/UDQS (output) CL = 4DQ Hi-Z Hi-Z (output) Power Down Exit Power Down Entry

Note: PD must be kept "High" level until end of Burst data output.

$\overrightarrow{PD}$  should be brought to "High" within t<sub>REFI</sub>(max.) to maintain the data written into cell. In Power Down Mode,  $\overrightarrow{PD}$  "Low" and a stable clock signal must be maintained. When  $\overrightarrow{PD}$  is brought to "High", a valid executable command may be applied I<sub>PDA</sub> cycles later.

### <u>POWER DOWN TIMING</u> (CL = 4, BL = 4)

Write cycle to Power Down Mode

Note:

PD

must be kept "High" level until WL+2 clock cycles from LAL command.

PD

should be brought to "High" within t<sub>REFI</sub>(max.) to maintain the data written into cell.

In Power Down Mode,

PD

"Low" and a stable clock signal must be maintained.

When

PD

is brought to "High", a valid executable command may be applied I<sub>PDA</sub> cycles later.

Rev 1.1 2005-11-08 31/46 DQ

(output)

LAL

LA

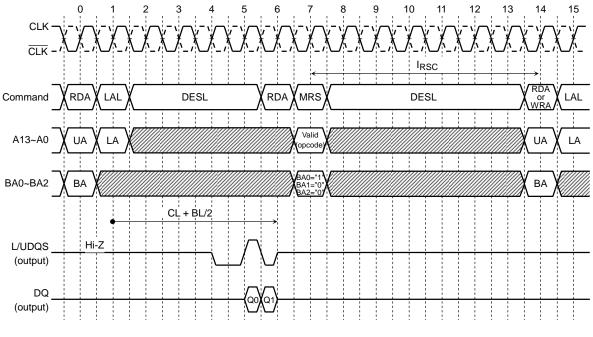

#### MODE REGISTER SET TIMING (CL = 4, BL = 2) From Read operation to Mode Register Set operation. 10 11 12 2 3 6 8 9 13 CLK CLK I<sub>RSC</sub> RDA or WRA Command RDA LAL DESL RDA MRS DESL ÷ Valid A13~A0 UA LA UA opcode 3A0="( BA0~BA2 ΒA ΒA CL + BL/2 Hi-Z L/UDQS (output)

Note: Minimum delay from LAL following RDA to RDA of MRS operation is CL+BL/2.

÷

1

ł

#### MODE REGISTER SET TIMING (CL = 4, BL = 4) From Write operation to Mode Register Set operation. 10 11 12 13 6 8 9 2 3 5 14 CLK CLK IRSC RDA or WRA WRA LAL DESL RDA MRS DESL Command LAL ł Valid A13~A0 UA LA UA LA opcode ÷. ł ł A0="0 BA0~BA2 ΒA ΒA WL+BL/2 L/UDQS (input) DQ 7 D2 D3 DC D1 (input)

Note: Minimum delay from LAL following WRA to RDA of MRS operation is WL+BL/2.

Rev 1.1 2005-11-08 33/46

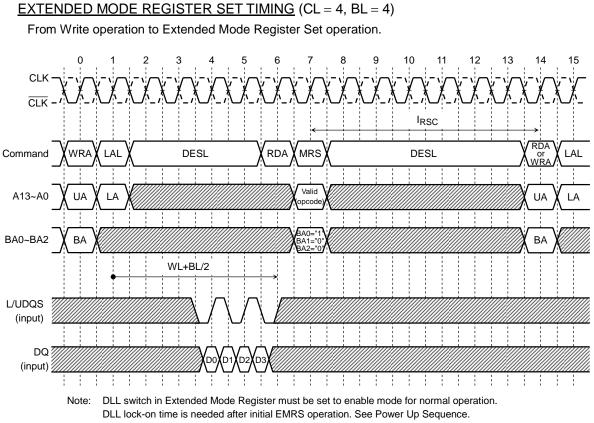

### EXTENDED MODE REGISTER SET TIMING (CL = 4, BL = 2)

From Read operation to Extended Mode Register Set operation.

Note: Minimum delay from LAL following RDA to RDA of EMRS operation is CL+BL/2. DLL switch in Extended Mode Register must be set to enable mode for normal operation. DLL lock-on time is needed after initial EMRS operation. See Power Up Sequence.

Minimum delay from LAL following WRA to RDA of EMRS operation is WL+BL/2.

Rev 1.1 2005-11-08 35/46

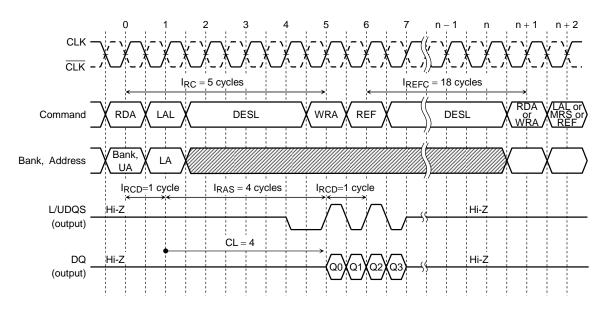

### AUTO-REFRESH TIMING (CL = 4, BL = 4)

Note: In case of CL = 4,  $I_{REFC}$  must be meet 18 clock cycles.

When the Auto-Refresh operation is performed, the synthetic average interval of Auto-Refresh command specified by  $t_{\mathsf{REFI}}$  must be satisfied.

tREFI is average interval time in 8 Refresh cycles that is sampled randomly.

$t_{\mbox{REFI}}$  is specified to avoid partly concentrated current of Refresh operation that is activated larger area than Read / Write operation.

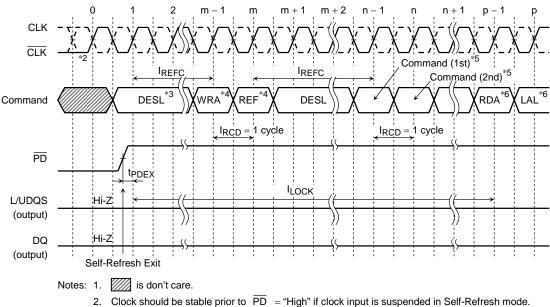

### SELF-REFRESH ENTRY TIMING

- 2. PD must be brought to "Low" within the timing between t<sub>FPDL</sub>(min) and t<sub>FPDL</sub>(max) to Self Refresh mode. When PD is brought to "Low" after I<sub>PDV</sub>, TC59LM913AMB perform Auto Refresh and enter Power down mode. In case of PD fall between t<sub>FPDL</sub>(max) and I<sub>PDV</sub>, TC59LM913AMB will either entry Self-Refresh mode or Power down mode after Auto-Refresh operation. It can't be specified which mode TC59LM913AMB operates.

- It is desirable that clock input is continued at least I<sub>CKD</sub> from REF command even though PD is brought to "Low" for Self-Refresh Entry.

- 4. In case of Self-Refresh entry after Write Operation, the delay time from the LAL command following WRA to the REF command is Write latency (WL)+3 clock cycles minimum.

### SELF-REFRESH EXIT TIMING

- 3. DESL command must be asserted during I<sub>REFC</sub> after PD is brought to "High".

- 4. It is desirable that one Auto-Refresh command is issued just after Self-Refresh Exit before any other operation.

- 5. Any command (except Read command) can be issued after  $\mathsf{I}_{\mathsf{REFC}}.$

- 6. Read command (RDA + LAL) can be issued after  $I_{LOCK}.$

### FUNCTIONAL DESCRIPTION

### Network FCRAM

FCRAM<sup>TM</sup> is an acronym of Fast Cycle Random Access Memory. The Network FCRAM<sup>TM</sup> is competent to perform fast random core access, low latency and high-speed data transfer.

### PIN FUNCTIONS

### CLOCK INPUTS: CLK & CLK

The CLK and  $\overline{\text{CLK}}$  inputs are used as the reference for synchronous operation. CLK is master clock input. The  $\overline{\text{CS}}$ , FN and all address input signals are sampled on the crossing of the positive edge of CLK and the negative edge of  $\overline{\text{CLK}}$ . The L/UDQS and DQ output are aligned to the crossing point of CLK and  $\overline{\text{CLK}}$ . The timing reference point for the differential clock is when the CLK and  $\overline{\text{CLK}}$  signals cross during a transition.

### POWER DOWN: PD

The PD input controls the entry to the Power Down or Self-Refresh modes. The  $\overline{PD}$  input does not have a Clock Suspend function like a CKE input of a standard SDRAMs, therefore it is illegal to bring  $\overline{PD}$  pin into low state if any Read or Write operation is being performed.

### CHIP SELECT & FUNCTION CONTROL: CS & FN

The  $\overline{CS}$  and FN inputs are a control signal for forming the operation commands on FCRAM<sup>TM</sup>. Each operation mode is decided by the combination of the two consecutive operation commands using the  $\overline{CS}$  and FN inputs.

#### BANK ADDRESSES: BA0~BA2

The BA0 to BA2 inputs are latched at the time of assertion of the RDA or WRA command and are selected the bank to be used for the operation. BA0 and BA1 also define which mode register is loaded during the Mode Register Set command (MRS or EMRS).

|         | BA0 | BA1 | BA2 |

|---------|-----|-----|-----|

| Bank #0 | 0   | 0   | 0   |

| Bank #1 | 1   | 0   | 0   |

| Bank #2 | 0   | 1   | 0   |

| Bank #3 | 1   | 1   | 0   |

| Bank #4 | 0   | 0   | 1   |

| Bank #5 | 1   | 0   | 1   |

| Bank #6 | 0   | 1   | 1   |

| Bank #7 | 1   | 1   | 1   |

Also, when BA2 input assign to A14 input, TC59LM913AMB can function as 4bank devices.

#### ADDRESS INPUTS: A0~A13

Address inputs are used to access the arbitrary address of the memory cell array within each bank. The Upper Addresses with Bank addresses are latched at the RDA or WRA command and the Lower Addresses are latched at the LAL command. The A0 to A13 inputs are also used for setting the data in the Regular or Extended Mode Register set cycle.

|                  | UPPER ADDRESS    | LOWER ADDRESS |

|------------------|------------------|---------------|

| 8 bank operation | A0~A13           | A0~A7         |

| 4 bank operation | A0~A13, BA2(A14) | A0~A7         |

### DATA INPUT/OUTPUT: DQ0~DQ15

The input data of DQ0 to DQ15 are taken in synchronizing with the both edges of L/UDQS input signal. The output data of DQ0 to DQ15 are outputted synchronizing with the both edges of L/UDQS signal.

### DATA STROBE: LDQS / UDQS

The L/UDQS is bi-directional signal. Both edges of L/UDQS are used as the reference of data input or output. In write operation, the L/UDQS used as an input signal is utilized for a latch of write data. In read operation, the L/UDQS is an output signal provides the read data strobe.

#### POWER SUPPLY: VDD, VDDQ, VSS, VSSQ

$V_{DD}$  and  $V_{SS}$  are power supply pins for memory core and peripheral circuits.  $V_{DDQ}$  and  $V_{SSQ}$  are power supply pins for the output buffer.

#### **REFERENCE VOLTAGE: VREF**

VREF is reference voltage for all input signals.

### COMMAND FUNCTIONS and OPERATIONS

TC59LM913AMB are introduced the two consecutive command input method. Therefore, except for Power Down mode, each operation mode decided by the combination of the first command and the second command from stand-by states of the bank to be accessed.

#### <u>Read Operation</u> (1st command + 2nd command = RDA + LAL)

Issuing the RDA command with Bank Addresses and Upper Addresses to the idle bank puts the bank designated by Bank Address in a read mode. When the LAL command with Lower Addresses is issued at the next clock of the RDA command, the data is read out sequentially synchronizing with the both edges of L/UDQS output signal (Burst Read Operation). The initial valid read data appears after  $\overline{CAS}$  latency from the issuing of the LAL command. The valid data is outputted for a burst length. The  $\overline{CAS}$  latency, the burst length of read data and the burst type must be set in the Mode Register beforehand. The read operated bank goes back automatically to the idle state after IRC.

#### Write Operation (1st command + 2nd command = WRA + LAL)

Issuing the WRA command with Bank Addresses and Upper Addresses to the idle bank puts the bank designated by Bank Address in a write mode. When the LAL command with Lower Addresses is issued at the next clock of the WRA command, the input data is latched sequentially synchronizing with the both edges of L/UDQS input signal (Burst Write Operation). The data and L/UDQS inputs have to be asserted in keeping with clock input after  $\overline{CAS}$  latency-1 from the issuing of the LAL command. The L/UDQS has to be provided for a burst length. The  $\overline{CAS}$  latency and the burst type must be set in the Mode Register beforehand. The write operated bank goes back automatically to the idle state after IRC. Write Burst Length is controlled by VW0 and VW1 inputs with LAL command. See VW truth table.

#### Auto-Refresh Operation (1st command + 2nd command = WRA + REF)

TC59LM913AMB are required to refresh like a standard SDRAM. The Auto-Refresh operation is begun with the REF command following to the WRA command. The Auto-Refresh mode can be effective only when all banks are in the idle state. In a point to notice, the write mode started with the WRA command is canceled by the REF command having gone into the next clock of the WRA command instead of the LAL command. The minimum period between the Auto-Refresh command and the next command is specified by  $l_{REFC}$ . However, about a synthetic average interval of Auto-Refresh command, it must be careful. In case of equally distributed refresh, Auto-Refresh command has to be issued within once for every 3.9  $\mu$ s by the maximum. In case of burst refresh or random distributed refresh, the average interval of eight consecutive Auto-Refresh commands has to be more than 400 ns always. In other words, the number of Auto-Refresh cycles that can be performed within 3.2  $\mu$ s (8 × 400 ns) is to 8 times in the maximum.

#### <u>Self-Refresh Operation</u> (1st command + 2nd command = WRA + REF with $\overline{PD}$ = "L")

In case of Self-Refresh operation, refresh operation can be performed automatically by using an internal timer. When all banks are in the idle state and all outputs are in Hi-Z states, the TC59LM913AMB become Self-Refresh mode by issuing the Self-Refresh command.  $\overrightarrow{PD}$  has to be brought to "Low" within tFPpL from the REF command following to the WRA command for a Self-Refresh mode entry. In order to satisfy the refresh period, the Self-Refresh entry command should be asserted within 3.9 µs after the latest Auto-Refresh command. Once the device enters Self-Refresh mode, the DESL command must be continued for lREFC period. In addition, it is desirable that clock input is kept in lCKD period. The device is in Self-Refresh mode as long as  $\overrightarrow{PD}$  held "Low". During Self-Refresh mode, all input and output buffers are disabled except for  $\overrightarrow{PD}$ , therefore the power dissipation lowers. Regarding a Self-Refresh mode exit,  $\overrightarrow{PD}$  has to be continuously issued in the number of clocks specified by lREFC. The Self-Refresh exit function is asynchronous operation. It is required that one Auto-Refresh command has to be continuously issued in the number of clocks specified by lREFC.

#### <u>Power Down Mode</u> ( $\overline{PD} = L$ )

When all banks are in the idle state and DQ outputs are in Hi-Z states, the TC59LM913AMB become Power Down Mode by asserting  $\overline{PD}$  is "Low". When the device enters the Power Down Mode, all input and output buffers are disabled after specified time except for  $\overline{PD}$ . Therefore, the power dissipation lowers. To exit the Power Down Mode,  $\overline{PD}$  has to be brought to "High" and the DESL command has to be issued for two clocks cycle after  $\overline{PD}$  goes high. The Power Down exit function is asynchronous operation.

Rev 1.1

Mode Register Set (MRS) and Extended Mode Register Set (EMRS)

(1st command + 2nd command = RDA + MRS)

When all banks are in the idle state, issuing the MRS command following to the RDA command can program the Mode Register. In a point to notice, the read mode started with the RDA command is canceled by the MRS command having gone into the next clock of the RDA command instead of the LAL command. The data to be set in the Mode Register is transferred using A0 to A14, BA0 to BA1 address inputs. The TC59LM913AMB have two mode registers. These are Regular and Extended Mode Register. The Regular or Extended Mode Register is chosen by BA0 and BA1 in the MRS command. The Regular Mode Register designates the operation mode for a read or write cycle. The Regular Mode Register has four function fields.

The four fields are as follows:

- (R-1) Burst Length field to set the length of burst data

- (R-2) Burst Type field to designate the lower address access sequence in a burst cycle

- (R-3)  $\overline{CAS}$  Latency field to set the access time in clock cycle

- (R-4) Test Mode field to use for supplier only.

The Extended Mode Register has two function fields. The two fields are as follows:

- (E-1) DLL Switch field to choose either DLL enable or DLL disable

- (E-2) Output Driver Impedance Control field.

Once those fields in the Mode Register are set up, the register contents are maintained until the Mode Register is set up again by another MRS command or power supply is lost. The initial value of the Regular or Extended Mode Register after power-up is undefined, therefore the Mode Register Set command must be issued before proper operation.

• Regular Mode Register/Extended Mode Register change bits (BA0, BA1). These bits are used to choose either Regular MRS or Extended MRS

| BA1 | BA0 | Mode Register Set |

|-----|-----|-------------------|

| 0   | 0   | Regular MRS       |

| 0   | 1   | Extended MRS      |

| 1   | ×   | Reserved          |

#### Regular Mode Register Fields

(R-1) Burst Length field (A2 to A0)

This field specifies the data length for column access using the A2 to A0 pins and sets the Burst Length to be 2 or 4 words.

| A2 | A1 | A0 | BURST LENGTH |

|----|----|----|--------------|

| 0  | 0  | 0  | Reserved     |

| 0  | 0  | 1  | 2 words      |

| 0  | 1  | 0  | 4 words      |

| 0  | 1  | 1  | Reserved     |

| 1  | ×  | ×  | Reserved     |

(R-2) Burst Type field (A3)

The Burst Type can be chosen Interleave mode or Sequential mode. When the A3 bit is "0", Sequential mode is selected. When the A3 bit is "1", Interleave mode is selected. Both burst types support burst length of 2 and 4 words.

| A3 | BURST TYPE |

|----|------------|

| 0  | Sequential |

| 1  | Interleave |

• Addressing sequence of Sequential mode (A3)

A column access is started from the inputted lower address and is performed by incrementing the lower address input to the device.

Addressing sequence for Sequential mode

| DATA   | ACCESS ADDRESS | BURST LENGTH                                                   |

|--------|----------------|----------------------------------------------------------------|

| Data 0 | Ν              | 2 words (address bits is LA0)                                  |

| Data 1 | n + 1          | from LA0~LA1                                                   |

| Data 2 | n + 2          | 4 words (address bits is LA1, LA0)<br>not carried from LA1~LA2 |

| Data 3 | n + 3          |                                                                |

• Addressing sequence of Interleave mode A column access is started from the inputted lower address and is performed by interleaving the address bits in the sequence shown as the following.

| DATA   |       | ACCESS ADDRESS |    |    |    |    |    |    |               | BURST LENGTH |

|--------|-------|----------------|----|----|----|----|----|----|---------------|--------------|

| Data 0 | ···A8 | A7             | A6 | A5 | A4 | A3 | A2 | A1 | A0            | ) } 2 words  |

| Data 1 | ···A8 | A7             | A6 | A5 | A4 | A3 | A2 | A1 | <del>A0</del> |              |

| Data 2 | ···A8 | A7             | A6 | A5 | A4 | A3 | A2 | A1 | A0            | 4 words      |

| Data 3 | ···A8 | A7             | A6 | A5 | A4 | A3 | A2 | A1 | ĀŪ            |              |

Addressing sequence for Interleave mode

(R-3)  $\overline{CAS}$  Latency field (A6 to A4)

This field specifies the number of clock cycles from the assertion of the LAL command following the RDA command to the first data read. The minimum values of  $\overline{CAS}$  Latency depends on the frequency of CLK. In a write mode, the place of clock that should input write data is  $\overline{CAS}$  Latency cycles – 1.

| A6 | A5 | A4 | CAS LATENCY |

|----|----|----|-------------|

| 0  | 0  | 0  | Reserved    |

| 0  | 0  | 1  | Reserved    |

| 0  | 1  | 0  | Reserved    |

| 0  | 1  | 1  | Reserved    |

| 1  | 0  | 0  | 4           |

| 1  | 0  | 1  | Reserved    |

| 1  | 1  | 0  | Reserved    |

| 1  | 1  | 1  | Reserved    |

(R-4) Test Mode field (A7)

This bit is used to enter Test Mode for supplier only and must be set to "0" for normal operation.

(R-5) Reserved field in the Regular Mode RegisterReserved bits (A8 to A13, BA2)

These bits are reserved for future operations. They must be set to "0" for normal operation.

Rev 1.1

### Extended Mode Register fields

(E-1) DLL Switch field (A0)

This bit is used to enable DLL. When the A0 bit is set "0", DLL is enabled. This bit must be set to "0" for normal operation.

(E-2) Output Driver Impedance Control field (A1, A6)

This field is used to choose Output Driver Strength. Four types of Driver Strength are supported.

| A6 | A1 | OUTPUT DRIVER IMPEDANCE CONTROL |

|----|----|---------------------------------|

| 0  | 0  | Normal Output Driver            |

| 0  | 1  | Strong Output Driver            |

| 1  | 0  | Weaker Output Driver            |

| 1  | 1  | Weakest Output Driver           |

(E-3) Reserved field (A2 to A5, A7 to A13, BA2)

These bits are reserved for future operations and must be set to "0" for normal operation.

### PACKAGE DIMENSIONS

Note: In order to support a package, four outer balls located on F and K row are required to assembly to board. These four ball is not connected to any electrical level.

Weight: 0.23g (typ.)

### **REVISION HISTORY**

- Rev.0.9 ( Feb.27th '2004 )

- Rev0.91 ( Mar.16<sup>th</sup> '2004 )

- Corrected TYPO(page50). Pin name is changed from "Q" to "R".

- Rev0.92 ( Apr.21th '2004 )

- +  $I_{DD6}$  spec changed from 20mA to 40mA (page 1, 7).

- IDD5B spec changed as below (page 7). "-50": 250mA  $\rightarrow$  420mA, "-55": 240mA  $\rightarrow$  400mA, "-60": 230mA  $\rightarrow$  380mA

- Corrected TYPO (page 7).  $\overline{\text{CAS}}\,$  Latency condition is changed from CL5 to CL4.

- Rev0.93 ( Jun. 9th '2004 )

- Auto-Refresh Average Interval (tREFI) changed from  $7.8\mu s$  to  $3.9\mu s$  (page 1, 10, 46).

- IDD6 spec changed from 40mA to 20mA (page 1, 7).

- IDD5B spec changed as below (page 7). "-50" : 420mA  $\rightarrow$  250mA, "-55": 400mA  $\rightarrow$  240mA, "-60": 380mA  $\rightarrow$  230mA

- Rev1.0 (Aug. 20th '2004)

- "-60" version dropped.

- Package name (P-BGA64-1317-1.00AZ) added (page 1).

- Some Note in the page 8 moved to page 7 (page 7, 8).

- Note 2 changed as below (page 7).

- Before: These parameters depend on the output loading. The specified values are obtained with the output open.

- After: These parameters define the current between VDD and VSS.

- Corrected TYPO (page 14, 15, 17).

- Package weight (0.23g) added (page 50).

- $\ Rev1.1$  ( Nov.8th '2005 )

- CAS Latency=3 feature dropped.

- 8 I/O feature dropped.

- "-55" speed version dropped.

- Deleted below sentence because of CL3 feature is dropped( page 1 ).

- "Keep backward compatibility for TC59LM814CFT(256Mbits) except package design" dropped. "

- Corrected figure of lPDA based AC timing spec table (page 11, 30, 31, 37).

### **RESTRICTIONS ON PRODUCT USE**

030619EBA

- The information contained herein is subject to change without notice.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others.

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor

devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical

stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of

safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of

such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- TOSHIBA products should not be embedded to the downstream products which are prohibited to be produced and sold, under any law and regulations.