## Product Preview Dual Channel Synchronous Rectified Buck MOSFET Driver

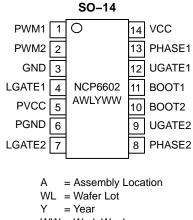

The NCP6602 is a two-channel dual MOSFET gate driver optimized to drive the gates of both the high and low-side Power MOSFETs in a MultiPhase Synchronous Buck converter. Each of the drivers is capable of driving a 3000 pF load with only a 12 nS transition time. Together with a wide 5–12 V MOSFET gate drive voltage range, adaptive shoot-through protection and reduced non-overlap time, the NCP6602 allows optimizing applications for the highest converter efficiency.

Internal bootstrapping on the upper gates utilizes only a single external capacitor to reduce parts cost and count, and allows the use of high–performance cost–effective N–Channel MOSFETs. Undervoltage Lockout circuitry ensures that both driver outputs are low when the supply voltage is low, and a Thermal Shutdown function provides the IC with overtemperature protection.

The NCP6602 is pin-to-pin compatible with the Intersil HIP6602B with the following advantages:

- Faster Rise and Fall Times with Higher Drive Capability

- Reduced Nonoverlap Times for Better Efficiency

- Thermal Shutdown for System Protection

#### Features

- Adaptive Shoot–Through Protection

- Three-State Input for Bridge Shutdown

- Undervoltage Lockout to Prevent Switching when the Input Voltage is Low

- LGATE to Phase Pull–Down Resistor Prevents HV Supply–Induced Turn On of High–Side MOSFET

- LGATE to PGND Pull–Down Resistor Prevents Transient Turn On of Low–Side MOSET

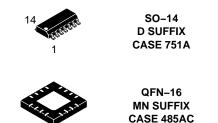

- Available in 14 Lead SOIC or 16 Lead QFN Thermally Enhanced Package

## ON Semiconductor®

http://onsemi.com

# PIN CONNECTIONS AND

MARKING DIAGRAMS

WW = Work Week

#### **ORDERING INFORMATION**

| Device      | Package | Shipping <sup>†</sup> |

|-------------|---------|-----------------------|

| NCP6602DR2  | SO-14   | 2500 Tape & Reel      |

| NCP6602MNR2 | QFN–16  | 3000 Tape & Reel      |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

This document contains information on a product under development. ON Semiconductor reserves the right to change or discontinue this product without notice.

Figure 1.

#### **PIN FUNCTION DESCRIPTION**

| Pin<br>(QFN) | Pin<br>(SOIC) | Pin Symbol     | Description                                                                                                                                                                                                                           |

|--------------|---------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11, 10       | 11, 10        | BOOT1, BOOT2   | Upper MOSFET floating Bootstrap Supply. A capacitor connected between BOOT and PHASE pins holds this bootstrap voltage for the high–side MOSFET as it is switched. The recommended capacitor value is between 100 nF and 1.0 $\mu F.$ |

| 15, 16       | 1, 2          | PWM1, PWM2     | This pin has primary control of the drive outputs from the controller.                                                                                                                                                                |

| 1            | 3             | GND            | Ground. Ground for $V_{CC}$ .                                                                                                                                                                                                         |

| 14           | 14            | VCC            | Input Supply. A 1.0 $\mu\text{F}$ ceramic capacitor should be connected from this pin to GND.                                                                                                                                         |

| 12, 9        | 12, 9         | UGATE1, UGATE2 | Buck Drive. Output drive for the Upper MOSFET.                                                                                                                                                                                        |

| 4            | 6             | PGND           | Power Ground. Should be closely connected to the source of the lower MOSFET.                                                                                                                                                          |

| 13, 7        | 13, 8         | Phase1, Phase2 | Return path for the upper gate drive.                                                                                                                                                                                                 |

| 2, 6         | 4, 7          | LGATE1, LGATE2 | Synchronous Rectifier Drive. Output drive for the Lower MOSFET.                                                                                                                                                                       |

| 3            | 5             | PVCC           | Supplies the Upper & Lower Gate Drive Voltage. Connect from 5.0 V to 12 V. A 1.0 $\mu$ F ceramic capacitor should be connected from this pin to PGND.                                                                                 |

| 5, 8         | -             | NC             | No Connect.                                                                                                                                                                                                                           |

#### MAXIMUM RATINGS\*

| Rating                                                                                 | Symbol                               | Value                                  | Unit |

|----------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------|------|

| Operating Ambient Temperature                                                          | T <sub>A</sub>                       | 0–85                                   | °C   |

| Operating Junction Temperature                                                         | Тյ                                   | internally limited by thermal shutdown |      |

| Package Thermal Resistance:<br>Junction to Ambient (QFN)<br>Junction to Ambient (SOIC) | R <sub>θJA</sub><br>R <sub>θJA</sub> | 36<br>68                               | °C/W |

| Storage Temperature Range                                                              | Τ <sub>S</sub>                       | -65 to 150                             | °C   |

| Lead Temperature Soldering (10 sec): Reflow: (SMD styles only) (Note 1)                | -                                    | 300                                    | °C   |

| JEDEC Moisture Sensitivity<br>(QFN)<br>(SOIC)                                          | MSL<br>MSL                           | 2<br>1                                 | -    |

1. 60 seconds maximum above  $183^{\circ}C$ .

\*The maximum package power dissipation must be observed.

NOTE: This device is ESD sensitive. Use standard ESD precautions when handling.

#### MAXIMUM RATINGS

| Pin Symbol        | Pin Name       | V <sub>MAX</sub>                | V <sub>MIN</sub>                                                                  | ISOURCE                           | I <sub>SINK</sub>                 |

|-------------------|----------------|---------------------------------|-----------------------------------------------------------------------------------|-----------------------------------|-----------------------------------|

| V <sub>CC</sub>   | Supply Voltage | 15 V                            | –0.3 V                                                                            | NA                                | 250 mA DC                         |

| P <sub>VCC</sub>  | Supply Voltage | V <sub>CC</sub> + 0.3 V         | –0.3 V                                                                            | NA                                | 2.0 A Peak (<100 μs)<br>250 mA DC |

| BOOT1,<br>BOOT2   | Boot Voltage   | 30 V wrt/PGND<br>15 V wrt/Phase | –0.3 V wrt/Phase                                                                  | NA                                | 2.0 A Peak (<100 μs)<br>250 mA DC |

| Phase1,<br>Phase2 | Switch Node    | 15 V DC<br>26 V<br>(<400 nS)    | PGND - 5.0 V<br>(<400 nS)<br>PGND - 0.3 V<br>(>400 nS)                            | 2.0 A Peak (<100 μs)<br>250 mA DC | NA                                |

| UGATE1,<br>UGATE2 | Upper Gate     | V <sub>BOOT</sub> + 0.3 V       | V <sub>PHASE</sub> –5.0 V<br>(<400 nS)<br>V <sub>PHASE</sub> – 0.3 V<br>(>400 nS) | 2.0 A Peak (<100 μs)<br>250 mA DC | 2.0 A Peak (<100 μs)<br>250 mA DC |

| LGATE1,<br>LGATE2 | Lower Gate     | V <sub>PVCC</sub> + 0.3 V       | PGND - 5.0 V<br>(<400 nS)<br>PGND - 0.3 V<br>(>400 nS)                            | 2.0 A Peak (<100 μs)<br>250 mA DC | 2.0 A Peak (<100 μs)<br>250 mA DC |

| PWM1,<br>PWM2     | Input          | 7.0 V                           | GND -0.3 V                                                                        | 1.0 mA                            | 1.0 mA                            |

| PGND              | Power Ground   | 0 V                             | 0 V                                                                               | 2.0 A Peak (<100 μs)<br>250 mA DC | NA                                |

| GND               | Ground         | PGND + 0.3 V                    | PGND – 0.3 V                                                                      | -                                 | _                                 |

NOTE: All voltages are with respect to PGND except where noted.

| Characteristic                    | Symbol                | Conditions                                                                                | Min        | Тур        | Max | Unit |

|-----------------------------------|-----------------------|-------------------------------------------------------------------------------------------|------------|------------|-----|------|

| V <sub>CC</sub> SUPPLY CURRENT    |                       |                                                                                           | •          |            |     | •    |

| Bias Supply Current               | I <sub>VCC</sub>      | $f_{PWM}$ = 500 kHz, $V_{PVCC}$ = 12 V                                                    | -          | 3.7        | 5.0 | mA   |

| Power Supply Current              | I <sub>PVCC</sub>     | $f_{PWM}$ = 500 kHz, $V_{PVCC}$ = 12 V                                                    | -          | 2.0        | 4.0 | mA   |

| POWER-ON RESET                    |                       | •                                                                                         | -          |            | -   | -    |

| V <sub>CC</sub> Rising Threshold  | -                     | -                                                                                         | -          | 9.6        | _   | V    |

| V <sub>CC</sub> Falling Threshold | -                     | -                                                                                         | -          | 7.6        | _   | V    |

| PWM INPUT                         |                       |                                                                                           |            |            |     |      |

| Input Current                     | I <sub>PWM</sub>      | V <sub>PWM</sub> = 0 or 5.0 V                                                             | -          | 500        | -   | μA   |

| PWM Rising Threshold              | -                     | V <sub>PVCC</sub> = 12 V                                                                  | -          | 3.2        | 3.6 | V    |

| PWM Falling Threshold             | -                     | V <sub>PVCC</sub> = 12 V                                                                  | 1.4        | 1.6        | -   | V    |

| Shutdown Window                   | -                     |                                                                                           | 1.4        | -          | 3.6 | V    |

| Shutdown Holdoff Time             | -                     |                                                                                           | -          | 230        | -   | ns   |

|                                   |                       | •                                                                                         |            |            |     |      |

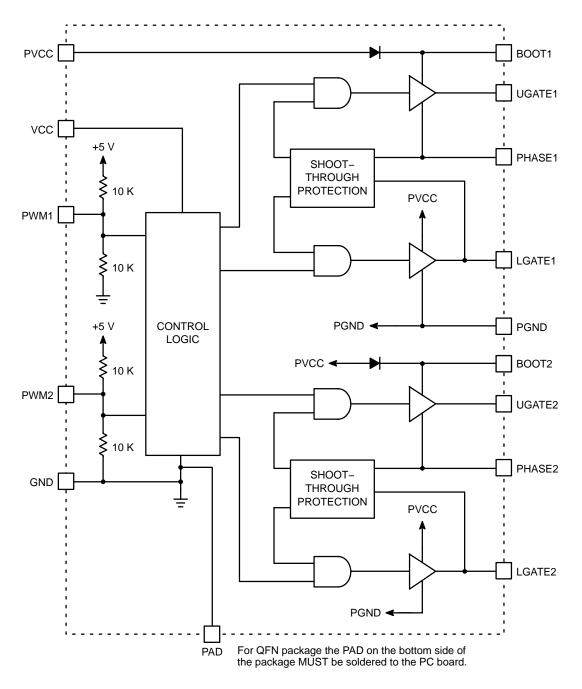

| UGATE Rise Time                   | TR <sub>UGATE</sub>   | $V_{PVCC} = V_{VCC} = 12 V, 3.0 nF Load$                                                  | -          | 16         | -   | ns   |

| LGATE Rise Time                   | TR <sub>LGATE</sub>   | $V_{PVCC} = V_{VCC} = 12 V, 3.0 nF Load$                                                  | -          | 12         | -   | ns   |

| UGATE Fall Time                   | TF <sub>UGATE</sub>   | $V_{PVCC} = V_{VCC} = 12 V, 3.0 nF Load$                                                  | -          | 15         | -   | ns   |

| LGATE Fall Time                   | TF <sub>LGATE</sub>   | $V_{PVCC} = V_{VCC} = 12 V, 3.0 nF Load$                                                  | _          | 12         | _   | ns   |

| UGATE Turn–Off Propagation Delay  | TPDL <sub>UGATE</sub> | $V_{PVCC} = V_{VCC} = 12 V$ , 3.0 nF Load                                                 | -          | 25         | -   | ns   |

| UGATE Non-Overlap Time            | TPDH <sub>UGATE</sub> | $V_{PVCC} = V_{VCC} = 12 V, 3.0 nF Load$                                                  | _          | 30         | _   | ns   |

| LGATE Turn–Off Propagation Delay  | TPDL <sub>LGATE</sub> | $V_{PVCC} = V_{VCC} = 12 V, 3.0 nF Load$                                                  | -          | 25         | -   | ns   |

| LGATE Non-Overlap Time            | TPDH <sub>LGATE</sub> | $V_{PVCC} = V_{VCC} = 12 V$ , 3.0 nF Load                                                 | -          | 27         | _   | ns   |

| UGATE Source Impedance            | R <sub>UGATE</sub>    | $V_{PVCC} = 5.0 \text{ V}, V_{VCC} = 12 \text{ V}$<br>$V_{PVCC} = V_{VCC} = 12 \text{ V}$ |            | TBD<br>1.0 |     | Ω    |

| UGATE Sink Impedance              | R <sub>UGATE</sub>    | $V_{PVCC} = 5.0 \text{ V}, V_{VCC} = 12 \text{ V}$<br>$V_{PVCC} = V_{VCC} = 12 \text{ V}$ |            | TBD<br>1.0 | -   | Ω    |

| LGATE OUTPUT                      |                       |                                                                                           |            |            |     |      |

| LGATE Source Current              | I <sub>LGATE</sub>    | $V_{PVCC} = 5.0 \text{ V}, V_{VCC} = 12 \text{ V}$<br>$V_{PVCC} = V_{VCC} = 12 \text{ V}$ | TBD<br>TBD | TBD<br>TBD | -   | mA   |

| LGATE Source Impedance            | R <sub>LGATE</sub>    | $V_{PVCC} = 5.0 \text{ V}, V_{VCC} = 12 \text{ V}$<br>$V_{PVCC} = V_{VCC} = 12 \text{ V}$ |            | TBD<br>1.1 |     | Ω    |

|                                   | R <sub>LGATE</sub>    | V <sub>PVCC</sub> = 5.0 V, V <sub>VCC</sub> = 12 V                                        |            | TBD        |     | Ω    |

| Over Temperature Protection (Note 2) |  | 150 | 170 | Ι | °C |

|--------------------------------------|--|-----|-----|---|----|

| Hysteresis (Note 2)                  |  | _   | 20  | - | °C |

All limits at temperature extremes are guaranteed via correlation using Standard Statistical Quality (SQC).

AC specifications are guaranteed by characterization, but not production tested.

For propagation delays, "tpdh" refers to the specified signal going high; "tpdl" refers to it going low. Specifications subject to change without notice.

Figure 2. Timing Diagram

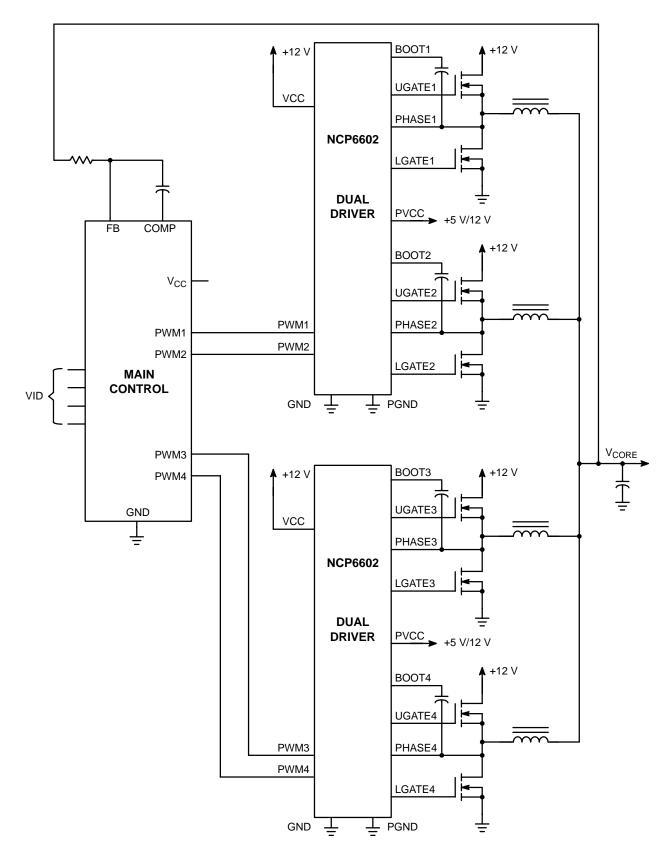

Figure 3. Four Phase Converter Using Two NCP6602 Gate Drivers

### PACKAGE DIMENSIONS

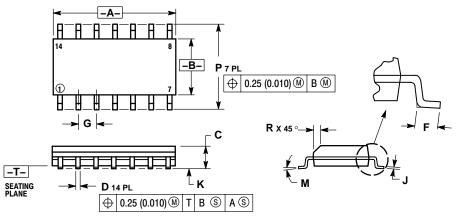

SO-14 **D SUFFIX** CASE 751A-03 **ISSUE F**

NOTES: 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. 2. CONTROLLING DIMENSION: MILLIMETER. 3. DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION. 4. MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE. 5. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION. SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION. MILLIMETERS INCHES

|     | MILLIN   | IETERS | INC       | HES   |

|-----|----------|--------|-----------|-------|

| DIM | MIN      | MAX    | MIN       | MAX   |

| Α   | 8.55     | 8.75   | 0.337     | 0.344 |

| В   | 3.80     | 4.00   | 0.150     | 0.157 |

| C   | 1.35     | 1.75   | 0.054     | 0.068 |

| D   | 0.35     | 0.49   | 0.014     | 0.019 |

| F   | 0.40     | 1.25   | 0.016     | 0.049 |

| G   | 1.27 BSC |        | 0.050 BSC |       |

| J   | 0.19     | 0.25   | 0.008     | 0.009 |

| K   | 0.10     | 0.25   | 0.004     | 0.009 |

| Μ   | 0 °      | 7°     | 0 °       | 7°    |

| Ρ   | 5.80     | 6.20   | 0.228     | 0.244 |

| R   | 0.25     | 0.50   | 0.010     | 0.019 |

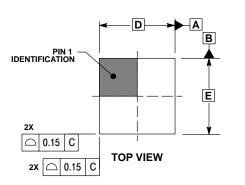

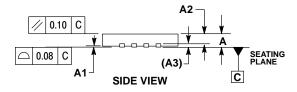

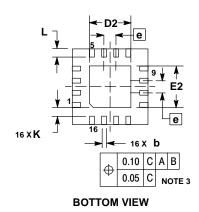

#### PACKAGE DIMENSIONS

16 PIN QFN, 5X5, 0.8 MM **MN SUFFIX** CASE 485AC-01 ISSUE O

- NOTES:

DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS.

DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.25 AND 0.30 MM FROM TERMINAL.

COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

|     | MILLIMETERS |      |  |

|-----|-------------|------|--|

| DIM | MIN         | MAX  |  |

| Α   | 0.80        | 1.00 |  |

| A1  | 0.00        | 0.05 |  |

| A2  | 0.65        | 0.75 |  |

| A3  | 0.20        | REF  |  |

| q   | 0.25        | 0.35 |  |

| D   | 5.00 BSC    |      |  |

| D2  | 2.55        | 2.85 |  |

| Е   | 5.00        | BSC  |  |

| E2  | 2.55        | 2.85 |  |

| e   | 0.80 BSC    |      |  |

| κ   | 0.20        |      |  |

| L   | 0.35        | 0.75 |  |

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters subciding "Typicals" must be validated for each customer applications by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications in which the Failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Japan: ON Semiconductor, Japan Customer Focus Center 2–9–1 Kamimeguro, Meguro–ku, Tokyo, Japan 153–0051 Phone: 81–3–5773–3850 ON Semiconductor Website: http://onsemi.com

Order Literature: http://www.onsemi.com/litorder

For additional information, please contact your local Sales Representative.