# X5643, X5645

(Replaces X25643, X25645)

Data Sheet

July 18, 2005

FN8135.1

## **CPU Supervisor with 64Kbit SPI EEPROM**

#### **FEATURES**

- Selectable watchdog timer

- Low V<sub>CC</sub> detection and reset assertion

- Five standard reset threshold voltages

Re-program low V<sub>CC</sub> reset threshold voltage using special programming sequence

Reset signal valid to V = 1V

- —Reset signal valid to  $V_{CC} = 1V$

- Determine watchdog or low voltage reset with a volatile flag bit

- Long battery life with low power consumption —<50µA max standby current, watchdog on —<1µA max standby current, watchdog off —<400µA max active current during read</li>

- 64Kbits of EEPROM

- Built-in inadvertent write protection

- -Power-up/power-down protection circuitry

- -Protect 0, 1/4, 1/2 or all of EEPROM array with Block Lock<sup>™</sup> protection

- -In circuit programmable ROM mode

- 2MHz SPI interface modes (0,0 & 1,1)

- Minimize EEPROM programming time —32-byte page write mode

- -Self-timed write cycle

- —5ms write cycle time (typical)

- 2.7V to 5.5V and 4.5V to 5.5V power supply operation

- Available packages —8-lead PDIP, 14-lead SOIC

#### DESCRIPTION

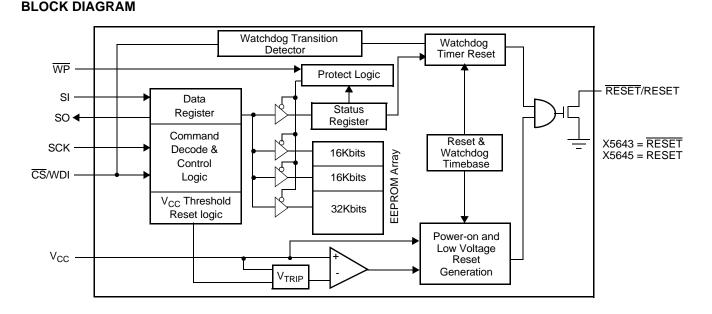

These devices combine four popular functions, Poweron Reset Control, Watchdog Timer, Supply Voltage Supervision, and Block Lock Protect Serial EEPROM Memory in one package. This combination lowers system cost, reduces board space requirements, and increases reliability.

Applying power to the device activates the power-on reset circuit which holds RESET/RESET active for a period of time. This allows the power supply and oscillator to stabilize before the processor can execute code.

The Watchdog Timer provides an independent protection mechanism for microcontrollers. When the microcontroller fails to restart a timer within a selectable time out interval, the device activates the RESET/RESET signal. The user selects the interval from three preset values. Once selected, the interval does not change, even after cycling the power.

The device's low V<sub>CC</sub> detection circuitry protects the user's system from low voltage conditions, resetting the system when V<sub>CC</sub> falls below the minimum V<sub>CC</sub> trip point. RESET/RESET is asserted until V<sub>CC</sub> returns to proper operating level and stabilizes. Five industry standard V<sub>TRIP</sub> thresholds are available, however, Intersil's unique circuits allow the threshold to be reprogrammed to meet custom requirements or to fine-tune the threshold for applications requiring higher precision.

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. 1-888-INTERSIL or 1-888-352-6832 | Intersil (and design) is a registered trademark of Intersil Americas Inc. Copyright Intersil Americas Inc. 2005. All Rights Reserved All other trademarks mentioned are the property of their respective owners.

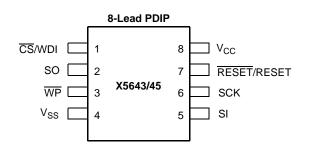

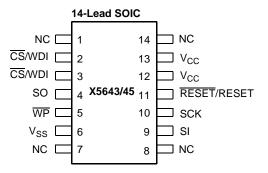

## **PIN CONFIGURATION**

| Pin<br>PDIP | Pin<br>SOIC    | Pin<br>TSSOP                  | Name            | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|-------------|----------------|-------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1           | 2&3            | 2                             | CS/WDI          | <b>Chip Select Input.</b> $\overline{CS}$ HIGH, deselects the device and the SO output pin is at a high impedance state. Unless a nonvolatile write cycle is underway, the device will be in the standby power mode. $\overline{CS}$ LOW enables the device, placing it in the active power mode. Prior to the start of any operation after power-up, a HIGH to LOW transition on $\overline{CS}$ is required.                                                                                                                                                                                          |  |  |  |

|             |                |                               |                 | <b>Watchdog Input.</b> A HIGH to LOW transition on the WDI pin restarts the watchdog timer. The absence of a HIGH to LOW transition within the watchdog time out period results in RESET/RESET going active.                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 2           | 4              | 3                             | SO              | <b>Serial Output.</b> SO is a push/pull serial data output pin. A read cycle shifts data out on this pin. The falling edge of the serial clock (SCK) clocks the data out.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 5           | 9              | 13                            | SI              | <b>Serial Input.</b> SI is a serial data input pin. Input all opcodes, byte addresses, and memory data on this pin. The rising edge of the serial clock (SCK) latches the input data. Send all opcodes (Table 1), addresses and data MSB first.                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 6           | 10             | 14                            | SCK             | <b>Serial Clock.</b> The serial clock controls the serial bus timing for data input and output. The rising edge of SCK latches in the opcode, address, or data bits present on the SI pin. The falling edge of SCK changes the data output on the SO pin.                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 3           | 5              | 7                             | WP              | Write Protect. The $\overline{WP}$ pin works in conjunction with a nonvolatile WPEN bit to<br>"lock" the setting of the watchdog timer control and the memory write protect bits.                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| 4           | 6              | 8                             | V <sub>SS</sub> | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 8           | 12 & 13        | 19                            | V <sub>CC</sub> | Supply Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 7           | 11             | 18                            | RESET/<br>RESET | <b>Reset Output</b> . RESET/RESET is an active LOW/HIGH, open drain output which goes active whenever $V_{CC}$ falls below the minimum $V_{CC}$ sense level. It will remain active until $V_{CC}$ rises above the minimum $V_{CC}$ sense level for 200ms. RESET/RESET goes active if the watchdog timer is enabled and $\overline{CS}$ remains either HIGH or LOW longer than the selectable watchdog time out period. A falling edge of $\overline{CS}$ will reset the watchdog timer. RESET/RESET goes active on power-up at about 1V and remains active for 200ms after the power supply stabilizes. |  |  |  |

|             | 1, 7, 8,<br>14 | 1, 4-6,<br>9-12,<br>15-17, 20 | NC              | No internal connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

#### **PRINCIPLES OF OPERATION**

#### **Power-on Reset**

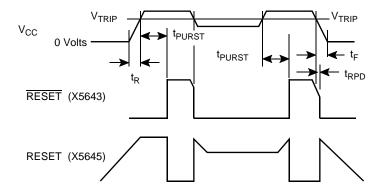

Application of power to the X5643/X5645 activates a power-on reset circuit. This circuit goes active at about 1V and pulls the RESET/RESET pin active. This signal prevents the system microprocessor from starting to operate with insufficient voltage or prior to stabilization of the oscillator. When  $V_{CC}$  exceeds the device  $V_{TRIP}$  value for 200ms (nominal) the circuit releases RESET/RESET, allowing the processor to begin executing code.

#### Low Voltage Monitoring

During operation, the X5643/X5645 monitors the V<sub>CC</sub> level and asserts RESET/RESET if supply voltage falls below a preset minimum V<sub>TRIP</sub> The RESET/RESET signal prevents the microprocessor from operating in a power fail or brownout condition. The RESET/RESET signal remains active until the voltage drops below 1V. It also remains active until V<sub>CC</sub> returns and exceeds V<sub>TRIP</sub> for 200ms.

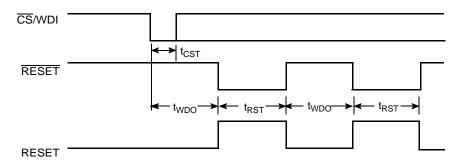

## Watchdog Timer

The watchdog timer circuit monitors the microprocessor activity by monitoring the WDI input. The microprocessor must toggle the  $\overline{CS}$ /WDI pin periodically to prevent a RESET/RESET signal. The  $\overline{CS}$ /WDI pin must be toggled from HIGH to LOW prior to the expiration of the watchdog time out period. The state of two nonvolatile control bits in the status register determine the watchdog timer period. The microprocessor can change these watchdog bits, or they may be "locked" by tying the WP pin LOW and setting the WPEN bit HIGH.

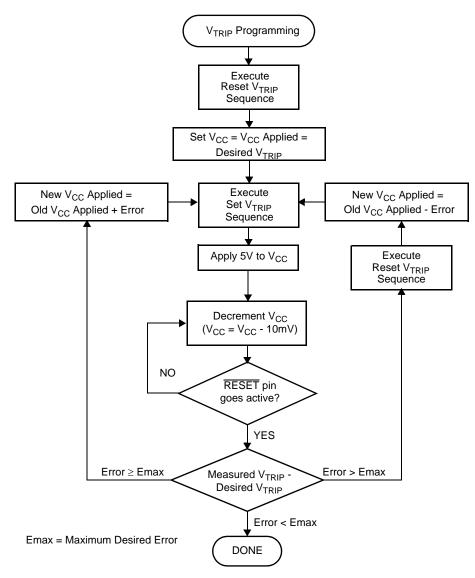

## V<sub>CC</sub> Threshold Reset Procedure

The X5643/X5645 has a standard V<sub>CC</sub> threshold (V<sub>TRIP</sub>) voltage. This value will not change over normal operating and storage conditions. However, in applications where the standard V<sub>TRIP</sub> is not exactly right, or for higher precision in the V<sub>TRIP</sub> value, the X5643/X5645 threshold may be adjusted.

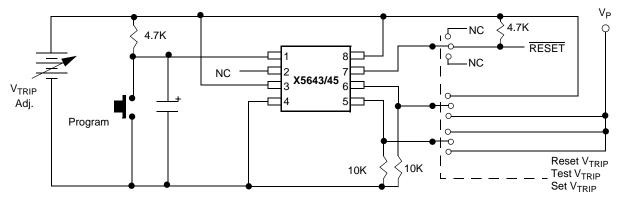

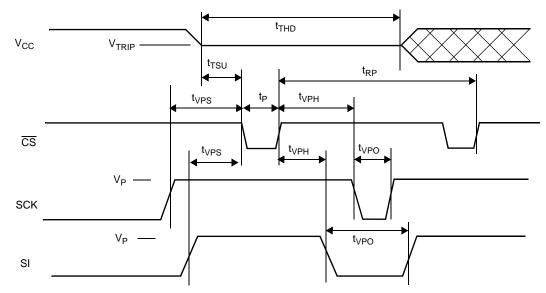

## Setting the V<sub>TRIP</sub> Voltage

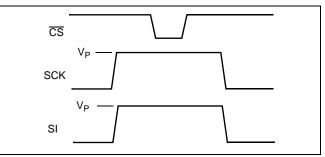

This procedure sets the V<sub>TRIP</sub> to a higher voltage value. For example, if the current V<sub>TRIP</sub> is 4.4V and the new V<sub>TRIP</sub> is 4.6V, this procedure directly makes the change. If the new setting is lower than the current setting, then it is necessary to reset the trip point before setting the new value.

3

To set the new  $V_{TRIP}$  voltage, apply the desired  $V_{TRIP}$  threshold to the Vcc pin and tie the  $\overline{CS}$ /WDI pin and the  $\overline{WP}$  pin HIGH. RESET/RESET and SO pins are left unconnected. Then apply the programming voltage  $V_P$  to both SCK and SI and pulse  $\overline{CS}$ /WDI LOW then HIGH. Remove  $V_P$  and the sequence is complete.

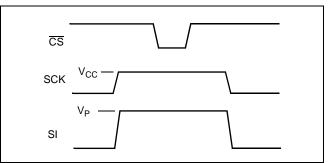

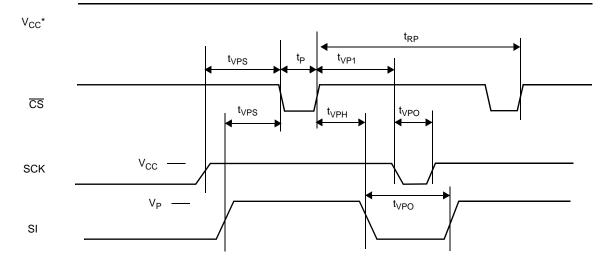

## Resetting the V<sub>TRIP</sub> Voltage

This procedure sets the  $V_{TRIP}$  to a "native" voltage level. For example, if the current  $V_{TRIP}$  is 4.4V and the  $V_{TRIP}$  is reset, the new  $V_{TRIP}$  is something less than 1.7V. This procedure must be used to set the voltage to a lower value.

To reset the V<sub>TRIP</sub> voltage, apply a voltage between 2.7 and 5.5V to the V<sub>CC</sub> pin. Tie the CS/WDI pin, the WP pin, and the SCK pin HIGH. RESET/RESET and SO pins are left unconnected. Then apply the programming voltage V<sub>P</sub> to the SI pin ONLY and pulse  $\overline{CS}$ /WDI LOW then HIGH. Remove V<sub>P</sub> and the sequence is complete.

#### Figure 2. Reset V<sub>TRIP</sub> Voltage

Figure 3. V<sub>TRIP</sub> Programming Sequence Flow Chart

#### Figure 4. Sample V<sub>TRIP</sub> Reset Circuit

### SPI SERIAL MEMORY

The memory portion of the device is a CMOS serial EEPROM array with Intersil's block lock protection. The array is internally organized as x 8. The device features a Serial Peripheral Interface (SPI) and software protocol allowing operation on a simple four-wire bus.

The device utilizes Intersil's proprietary Direct Write<sup>™</sup> cell, providing a minimum endurance of 100,000 cycles and a minimum data retention of 100 years.

The device is designed to interface directly with the synchronous Serial Peripheral Interface (SPI) of many popular microcontroller families. It contains an 8-bit instruction register that is accessed via the SI input, with data being clocked in on the rising edge of SCK.  $\overline{CS}$  must be LOW during the entire operation.

All instructions (Table 1), addresses and data are transferred MSB first. Data input on the SI line is latched on the first rising edge of SCK after  $\overline{CS}$  goes LOW. Data is output on the SO line by the falling edge of SCK. SCK is static, allowing the user to stop the clock and then start it again to resume operations where left off.

## Table 1. Instruction Set

## Write Enable Latch

The device contains a write enable latch. This latch must be SET before a write operation is initiated. The WREN instruction will set the latch and the WRDI instruction will reset the latch (Figure 3). This latch is automatically reset upon a power-up condition and after the completion of a valid Write Cycle.

#### **Status Register**

The RDSR instruction provides access to the status register. The status register may be read at any time, even during a write cycle. The status register is formatted as follows:

| 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------|-----|-----|-----|-----|-----|-----|-----|

| WPEN | FLB | WD1 | WD0 | BL1 | BL0 | WEL | WIP |

The Write-In-Progress (WIP) bit is a volatile, read only bit and indicates whether the device is busy with an internal nonvolatile write operation. The WIP bit is read using the RDSR instruction. When set to a "1", a nonvolatile write operation is in progress. When set to a "0", no write is in progress.

| Instruction Name | Instruction Format* | Operation                                                      |

|------------------|---------------------|----------------------------------------------------------------|

| WREN             | 0000 0110           | Set the write enable latch (enable write operations)           |

| SFLB             | 0000 0000           | Set flag bit                                                   |

| WRDI/RFLB        | 0000 0100           | Reset the write enable latch/reset flag bit                    |

| RSDR             | 0000 0101           | Read status register                                           |

| WRSR             | 0000 0001           | Write status register (watchdog, block lock, WPEN & flag bits) |

| READ             | 0000 0011           | Read data from memory array beginning at selected address      |

| WRITE            | 0000 0010           | Write data to memory array beginning at selected address       |

Note: \*Instructions are shown MSB in leftmost position. Instructions are transferred MSB first.

| WREN CMD | Status Register | Device Pin | Block           | Block             | Status Register            |

|----------|-----------------|------------|-----------------|-------------------|----------------------------|

| WEL      | WPEN            | WP#        | Protected Block | Unprotected Block | WPEN, BL0, BL1<br>WD0, WD1 |

| 0        | Х               | Х          | Protected       | Protected         | Protected                  |

| 1        | 1               | 0          | Protected       | Writable          | Protected                  |

| 1        | 0               | Х          | Protected       | Writable          | Writable                   |

| 1        | Х               | 1          | Protected       | Writable          | Writable                   |

#### Table 2. Block Protect Matrix

The Write Enable Latch (WEL) bit indicates the status of the write enable latch. When WEL = 1, the latch is set HIGH and when WEL = 0 the latch is reset LOW. The WEL bit is a volatile, read only bit. It can be set by the WREN instruction and can be reset by the WRDS instruction.

The block lock bits, BL0 and BL1, set the level of block lock protection. These nonvolatile bits are programmed using the WRSR instruction and allow the user to protect one quarter, one half, all or none of the EEPROM array. Any portion of the array that is block lock protected can be read but not written. It will remain protected until the BL bits are altered to disable block lock protection of that portion of memory.

| Status<br>Register Bits |     | Array Addresses Protected |

|-------------------------|-----|---------------------------|

| BL1                     | BL0 | X5643/X5645               |

| 0                       | 0   | None                      |

| 0                       | 1   | \$1800-\$1FFF             |

| 1                       | 0   | \$1000-\$1FFF             |

| 1                       | 1   | \$0000-\$1FFF             |

The watchdog timer bits, WD0 and WD1, select the watchdog time out period. These nonvolatile bits are programmed with the WRSR instruction.

| Status Re | gister Bits | Watchdog Time Out |

|-----------|-------------|-------------------|

| WD1       | WD0         | (Typical)         |

| 0         | 0           | 1.4 seconds       |

| 0         | 1           | 600 milliseconds  |

| 1         | 0           | 200 milliseconds  |

| 1         | 1           | disabled          |

The FLAG bit shows the status of a volatile latch that can be set and reset by the system using the SFLB and RFLB instructions. The flag bit is automatically reset upon power-up. This flag can be used by the system to determine whether a reset occurs as a result of a watchdog time out or power failure.

The nonvolatile WPEN bit is programmed using the WRSR instruction. This bit works in conjunction with the  $\overline{\text{WP}}$  pin to provide an in-circuit programmable ROM function (Table 2).  $\overline{\text{WP}}$  is LOW and WPEN bit programmed HIGH disables all status register write operations.

## In Circuit Programmable ROM Mode

This mechanism protects the block lock and watchdog bits from inadvertent corruption.

In the locked state (programmable ROM mode) the  $\overline{WP}$  pin is LOW and the nonvolatile bit WPEN is "1". This mode disables nonvolatile writes to the device's status register.

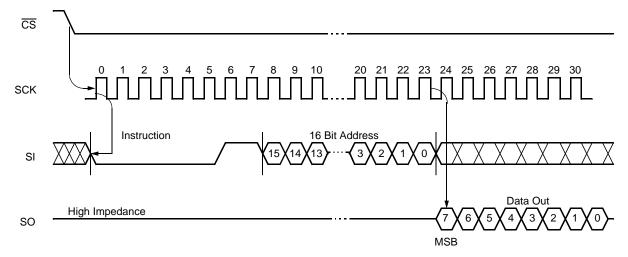

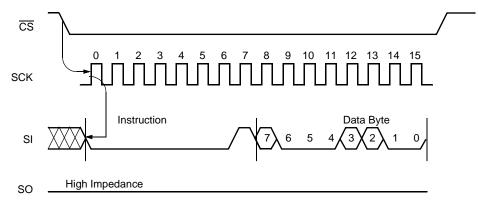

#### Figure 5. Read EEPROM Array Sequence

Setting the  $\overline{\text{WP}}$  pin LOW while WPEN is a "1" while an internal write cycle to the status register is in progress will not stop this write operation, but the operation disables subsequent write attempts to the status register.

When WP is HIGH, all functions, including nonvolatile writes to the status register operate normally. Setting the WPEN bit in the status register to "0" blocks the WP pin function, allowing writes to the status register when WP is HIGH or LOW. Setting the WPEN bit to "1" while the  $\overline{WP}$  pin is LOW activates the programmable ROM mode, thus requiring a change in the  $\overline{WP}$  pin prior to subsequent status register changes. This allows manufacturing to install the device in a system with  $\overline{WP}$  pin grounded and still be able to program the status register. Manufacturing can then load configuration data, manufacturing time and other parameters into the EEPROM, then set the portion of memory to be protected by setting the block lock bits, and finally set the "OTP mode" by setting the WPEN bit. Data changes now require a hardware change.

## **Read Sequence**

When reading from the EEPROM memory array,  $\overline{CS}$  is first pulled low to select the device. The 8-bit READ instruction is transmitted to the device, followed by the 16bit address. After the READ opcode and address are sent, the data stored in the memory at the selected address is shifted out on the SO line. The data stored in memory at the next address can be read sequentially by continuing to provide clock pulses. The address is automatically incremented to the next higher address after each byte of data is shifted out. When the highest address is reached, the address counter rolls over to address \$0000 allowing the read cycle to be continued indefinitely. The read operation is terminated by taking  $\overline{CS}$  high. Refer to the read EEPROM array sequence (Figure 1).

7

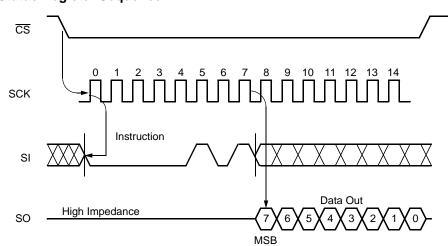

To read the status register, the  $\overline{CS}$  line is first pulled low to select the device followed by the 8-bit RDSR instruction. After the RDSR opcode is sent, the contents of the status register are shifted out on the SO line. Refer to the read status register sequence (Figure 2).

#### Write Sequence

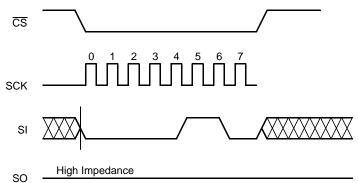

Prior to any attempt to write data into the device, the "Write Enable" Latch (WEL) must first be set by issuing the WREN instruction (Figure 3).  $\overline{CS}$  is first taken LOW, then the WREN instruction is clocked into the device. After all eight bits of the instruction are transmitted,  $\overline{CS}$  must then be taken HIGH. If the user continues the write operation without taking  $\overline{CS}$  HIGH after issuing the WREN instruction, the write operation will be ignored.

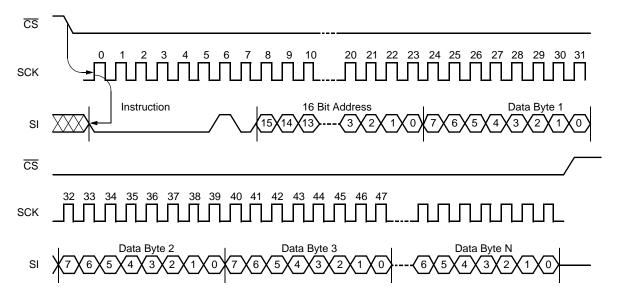

To write data to the EEPROM memory array, the user then issues the WRITE instruction followed by the 16 bit address and then the data to be written. Any unused address bits are specified to be "0's". The WRITE operation minimally takes 32 clocks.  $\overline{CS}$  must go low and remain low for the duration of the operation. If the address counter reaches the end of a page and the clock continues, the counter will roll back to the first address of the page and overwrite any data that may have been previously written.

For the page write operation (byte or page write) to be completed,  $\overline{CS}$  can only be brought HIGH after bit 0 of the last data byte to be written is clocked in. If it is brought HIGH at any other time, the write operation will not be completed (Figure 4).

To write to the status register, the WRSR instruction is followed by the data to be written (Figure 5). Data bits 0 and 1 must be "0".

While the write is in progress following a status register or EEPROM sequence, the status register may be read to check the WIP bit. During this time the WIP bit will be high.

#### **OPERATIONAL NOTES**

The device powers-up in the following state:

- The device is in the low power standby state.

- A HIGH to LOW transition on CS is required to enter an active state and receive an instruction.

- SO pin is high impedance.

## Figure 6. Read Status Register Sequence

- The write enable latch is reset.

- The flag bit is reset.

- Reset signal is active for t<sub>PURST</sub>.

#### **Data Protection**

The following circuitry has been included to prevent inadvertent writes:

- A WREN instruction must be issued to set the write enable latch.

- CS must come HIGH at the proper clock count in order to start a nonvolatile write cycle.

## Figure 7. Write Enable Latch Sequence

## Figure 8. Write Sequence

#### Figure 9. Status Register Write Sequence

#### SYMBOL TABLE

| WAVEFORM | INPUTS                            | OUTPUTS                             |

|----------|-----------------------------------|-------------------------------------|

|          | Must be<br>steady                 | Will be<br>steady                   |

|          | May change<br>from LOW<br>to HIGH | Will change<br>from LOW<br>to HIGH  |

|          | May change<br>from HIGH<br>to LOW | Will change<br>from HIGH<br>to LOW  |

|          | Don't Care:<br>Changes<br>Allowed | Changing:<br>State Not<br>Known     |

|          | N/A                               | Center Line<br>is High<br>Impedance |

#### ABSOLUTE MAXIMUM RATINGS

| Temperature under bias                | -65°C to +135°C          |

|---------------------------------------|--------------------------|

| Storage temperature                   | -65°C to +150°C          |

| Voltage on any pin with respect to VS | <sub>S</sub> 1.0V to +7V |

| D.C. output current                   | 5mA                      |

| Lead temperature (soldering, 10 seco  | onds) 300°C              |

## COMMENT

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only; the functional operation of the device (at these or any other conditions above those listed in the operational sections of this specification) is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **RECOMMENDED OPERATING CONDITIONS**

| Temperature | Min.  | Max.  |

|-------------|-------|-------|

| Commercial  | D°O   | 70°C  |

| Industrial  | -40°C | +85°C |

| Device Option  | Supply Voltage |

|----------------|----------------|

| -2.7 or -2.7A  | 2.7V to 5.5V   |

| Blank or -4.5A | 4.5V-5.5V      |

#### D.C. OPERATING CHARACTERISTICS (Over the recommended operating conditions unless otherwise specified.)

|                                |                                            |                       | Limits |                       |      |                                                                                                                                                                  |  |

|--------------------------------|--------------------------------------------|-----------------------|--------|-----------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Symbol                         | Parameter                                  | Min.                  | Тур.   | Max.                  | Unit | Test Conditions                                                                                                                                                  |  |

| I <sub>CC1</sub>               | V <sub>CC</sub> write current (active)     |                       |        | 5                     | mA   | SCK = V <sub>CC</sub> x 0.1/V <sub>CC</sub> x 0.9 @ 2MHz,<br>SO = Open                                                                                           |  |

| I <sub>CC2</sub>               | V <sub>CC</sub> read current (active)      |                       |        | 0.4                   | mA   | SCK = V <sub>CC</sub> x 0.1/V <sub>CC</sub> x 0.9 @ 2MHz,<br>SO = Open                                                                                           |  |

| I <sub>SB1</sub>               | V <sub>CC</sub> standby current<br>WDT=OFF |                       |        | 1                     | μA   | $\overline{\text{CS}} = \text{V}_{\text{CC}}, \text{V}_{\text{IN}} = \text{V}_{\text{SS}} \text{ or } \text{V}_{\text{CC}}, \text{V}_{\text{CC}} = 5.5 \text{V}$ |  |

| I <sub>SB2</sub>               | V <sub>CC</sub> standby current<br>WDT=ON  |                       |        | 50                    | μA   | $\overline{\text{CS}} = \text{V}_{\text{CC}}, \text{V}_{\text{IN}} = \text{V}_{\text{SS}} \text{ or } \text{V}_{\text{CC}}, \text{V}_{\text{CC}} = 5.5 \text{V}$ |  |

| I <sub>SB3</sub>               | V <sub>CC</sub> standby current<br>WDT=ON  |                       |        | 20                    | μA   | $\overline{CS} = V_{CC}, V_{IN} = V_{SS} \text{ or } V_{CC}, \\ V_{CC} = 3.6 V$                                                                                  |  |

| ILI                            | Input leakage current                      |                       | 0.1    | 10                    | μA   | $V_{IN} = V_{SS}$ to $V_{CC}$                                                                                                                                    |  |

| I <sub>LO</sub>                | Output leakage current                     |                       | 0.1    | 10                    | μA   | $V_{OUT} = V_{SS}$ to $V_{CC}$                                                                                                                                   |  |

| V <sub>IL</sub> <sup>(1)</sup> | Input LOW voltage                          | -0.5                  |        | V <sub>CC</sub> x 0.3 | V    |                                                                                                                                                                  |  |

| V <sub>IH</sub> <sup>(1)</sup> | Input HIGH voltage                         | V <sub>CC</sub> x 0.7 |        | V <sub>CC</sub> + 0.5 | V    |                                                                                                                                                                  |  |

| V <sub>OL1</sub>               | Output LOW voltage                         |                       |        | 0.4                   | V    | V <sub>CC</sub> > 3.3V, I <sub>OL</sub> = 2.1mA                                                                                                                  |  |

| V <sub>OL2</sub>               | Output LOW voltage                         |                       |        | 0.4                   | V    | $2V < V_{CC} \le 3.3V, I_{OL} = 1mA$                                                                                                                             |  |

| V <sub>OL3</sub>               | Output LOW voltage                         |                       |        | 0.4                   | V    | $V_{CC} \le 2V, I_{OL} = 0.5mA$                                                                                                                                  |  |

| V <sub>OH1</sub>               | Output HIGH voltage                        | V <sub>CC</sub> - 0.8 |        |                       | V    | V <sub>CC</sub> > 3.3V, I <sub>OH</sub> = -1.0mA                                                                                                                 |  |

| V <sub>OH2</sub>               | Output HIGH voltage                        | V <sub>CC</sub> - 0.4 |        |                       | V    | $2V < V_{CC} \le 3.3V$ , $I_{OH}$ = -0.4mA                                                                                                                       |  |

| V <sub>OH3</sub>               | Output HIGH voltage                        | V <sub>CC</sub> - 0.2 |        |                       | V    | $V_{CC} \le 2V$ , $I_{OH}$ = -0.25mA                                                                                                                             |  |

| V <sub>OLS</sub>               | Reset output LOW voltage                   |                       |        | 0.4                   | V    | I <sub>OL</sub> = 1mA                                                                                                                                            |  |

## **CAPACITANCE** $T_A = +25^{\circ}C$ , f = 1MHz, $V_{CC} = 5V$

| Symbol                          | Test                                 | Max. | Unit | Conditions     |

|---------------------------------|--------------------------------------|------|------|----------------|

| C <sub>OUT</sub> <sup>(2)</sup> | Output Capacitance (SO, RESET/RESET) | 8    | pF   | $V_{OUT} = 0V$ |

| C <sub>IN</sub> <sup>(2)</sup>  | Input Capacitance (SCK, SI, CS, WP)  | 6    | pF   | $V_{IN} = 0V$  |

Notes: (1)  $V_{IL}$  min. and  $V_{IH}$  max. are for reference only and are not tested. (2) This parameter is periodically sampled and not 100% tested.

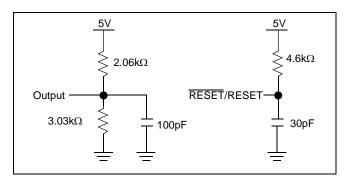

## EQUIVALENT A.C. LOAD CIRCUIT AT 5V $\rm V_{CC}$

## A.C. TEST CONDITIONS

| Input pulse levels            | $V_{CC} \ge 0.1$ to $V_{CC} \ge 0.9$ |  |  |

|-------------------------------|--------------------------------------|--|--|

| Input rise and fall times     | 10ns                                 |  |  |

| Input and output timing level | V <sub>CC</sub> x0.5                 |  |  |

A.C. CHARACTERISTICS (Over recommended operating conditions, unless otherwise specified)

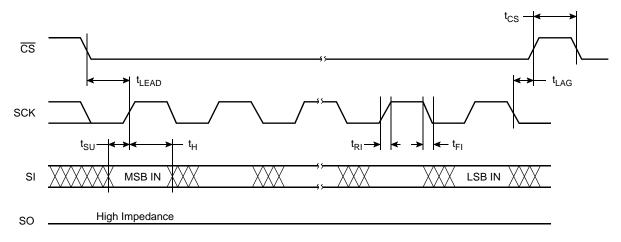

## Serial Input Timing

|                                | Parameter        | 2.7- | 2.7-5.5V |      |  |

|--------------------------------|------------------|------|----------|------|--|

| Symbol                         |                  | Min. | Max.     | Unit |  |

| f <sub>SCK</sub>               | Clock frequency  | 0    | 2        | MHz  |  |

| t <sub>CYC</sub>               | Cycle time       | 500  |          | ns   |  |

| t <sub>LEAD</sub>              | CS lead time     | 250  |          | ns   |  |

| t <sub>LAG</sub>               | CS lag time      | 250  |          | ns   |  |

| t <sub>WH</sub>                | Clock HIGH time  | 200  |          | ns   |  |

| t <sub>WL</sub>                | Clock LOW time   | 250  |          | ns   |  |

| t <sub>SU</sub>                | Data setup time  | 50   |          | ns   |  |

| t <sub>H</sub>                 | Data hold time   | 50   |          | ns   |  |

| t <sub>RI</sub> <sup>(3)</sup> | Input rise time  |      | 100      | ns   |  |

| t <sub>FI</sub> (3)            | Input fall time  |      | 100      | ns   |  |

| t <sub>CS</sub>                | CS deselect time | 500  |          | ns   |  |

| t <sub>WC</sub> <sup>(4)</sup> | Write cycle time |      | 10       | ms   |  |

## **Serial Input Timing**

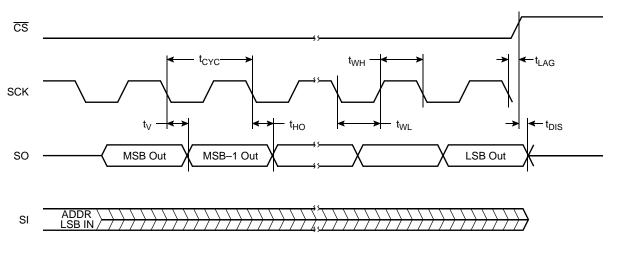

## Serial Output Timing

|                                |                             | 2.7-5.5V |      |     |  |

|--------------------------------|-----------------------------|----------|------|-----|--|

| Symbol                         | Parameter                   | Min.     | Unit |     |  |

| f <sub>SCK</sub>               | Clock frequency             | 0        | 2    | MHz |  |

| t <sub>DIS</sub>               | Output disable time         |          | 250  | ns  |  |

| t <sub>V</sub>                 | Output valid from clock low |          | 250  | ns  |  |

| t <sub>HO</sub>                | Output hold time            | 0        |      | ns  |  |

| t <sub>RO</sub> <sup>(3)</sup> | Output rise time            |          | 100  | ns  |  |

| t <sub>FO</sub> <sup>(3)</sup> | Output fall time            |          | 100  | ns  |  |

Notes: (3) This parameter is periodically sampled and not 100% tested.

(4) t<sub>WC</sub> is the time from the rising edge of  $\overline{CS}$  after a valid write sequence has been sent to the end of the self-timed internal nonvolatile write cycle.

#### **Serial Output Timing**

intersil

## Power-Up and Power-Down Timing

## **RESET** Output Timing

| Symbol                          | Parameter                                                              | Min. | Тур. | Max. | Unit |

|---------------------------------|------------------------------------------------------------------------|------|------|------|------|

| V <sub>TRIP</sub>               | Reset trip point voltage, X5643-4.5A, X5643-4.5A                       | 4.5  | 4.63 | 4.75 |      |

|                                 | Reset trip point voltage, X5643, X5645                                 | 4.25 | 4.38 | 4.5  | V    |

|                                 | Reset trip point voltage, X5643-2.7A, X5645-2.7A                       | 2.85 | 2.93 | 3.0  | v    |

|                                 | Reset trip point voltage, X5643-2.7, X5645-2.7                         | 2.55 | 2.63 | 2.7  |      |

| V <sub>TH</sub>                 | $V_{TRIP}$ hysteresis (HIGH to LOW vs. LOW to HIGH $V_{TRIP}$ voltage) |      | 20   |      | mV   |

| t <sub>PURST</sub>              | Power-up reset time out                                                | 100  | 200  | 280  | ms   |

| t <sub>RPD</sub> <sup>(5)</sup> | V <sub>CC</sub> detect to reset/output                                 |      |      | 500  | ns   |

| t <sub>F</sub> (5)              | V <sub>CC</sub> fall time                                              | 100  |      |      | μs   |

| t <sub>R</sub> <sup>(5)</sup>   | V <sub>CC</sub> rise time                                              | 100  |      |      | μs   |

| V <sub>RVALID</sub>             | Reset valid V <sub>CC</sub>                                            | 1    |      |      | V    |

Note: (5) This parameter is periodically sampled and not 100% tested.

## CS/WDI vs. RESET/RESET Timing

## **RESET/RESET** Output Timing

| Symbol           | Parameter Min.                       |     | Тур. | Max. | Unit |  |

|------------------|--------------------------------------|-----|------|------|------|--|

| t <sub>WDO</sub> | Watchdog time out period,            |     |      |      |      |  |

|                  | WD1 = 1, WD0 = 0                     | 100 | 200  | 300  | ms   |  |

|                  | WD1 = 0, WD0 = 1                     | 450 | 600  | 800  | ms   |  |

|                  | WD1 = 0, WD0 = 0                     | 1   | 1.4  | 2    | sec  |  |

| t <sub>CST</sub> | CS pulse width to reset the watchdog | 400 |      |      | ns   |  |

| t <sub>RST</sub> | Reset time out                       | 100 | 200  | 300  | ms   |  |

## V<sub>TRIP</sub> Set Conditions

## V<sub>TRIP</sub> Reset Conditions

$*V_{CC}$  > Programmed V<sub>TRIP</sub>

| Parameter         | Description                                                                                                                                 | Min. | Max. | Unit |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|

| t <sub>VPS</sub>  | SCK V <sub>TRIP</sub> program voltage setup time                                                                                            | 1    |      | μs   |

| t <sub>VPH</sub>  | SCK V <sub>TRIP</sub> program voltage hold time                                                                                             | 1    |      | μs   |

| t <sub>P</sub>    | V <sub>TRIP</sub> program pulse width                                                                                                       | 1    |      | μs   |

| t <sub>TSU</sub>  | V <sub>TRIP</sub> level setup time                                                                                                          | 10   |      | μs   |

| t <sub>THD</sub>  | V <sub>TRIP</sub> level hold (stable) time                                                                                                  | 10   |      | ms   |

| t <sub>WC</sub>   | V <sub>TRIP</sub> write cycle time                                                                                                          |      | 10   | ms   |

| t <sub>RP</sub>   | V <sub>TRIP</sub> program cycle recovery period (between successive programming cycles)                                                     | 10   |      | ms   |

| t <sub>VPO</sub>  | SCK V <sub>TRIP</sub> program voltage off time before next cycle                                                                            | 0    |      | ms   |

| VP                | Programming voltage                                                                                                                         | 15   | 18   | V    |

| V <sub>TRAN</sub> | V <sub>TRIP</sub> programed voltage range                                                                                                   | 1.7  | 5.0  | V    |

| V <sub>ta1</sub>  | Initial V <sub>TRIP</sub> program voltage accuracy (V <sub>CC</sub> applied-V <sub>TRIP</sub> ) (programmed at 25°C)                        | -0.1 | +0.4 | V    |

| V <sub>ta2</sub>  | Subsequent V <sub>TRIP</sub> Program Voltage accuracy [(V <sub>CC</sub> applied-V <sub>ta1</sub> )-V <sub>TRIP</sub> ] (programmed at 25°C) | -25  | +25  | mV   |

| V <sub>tr</sub>   | V <sub>TRIP</sub> Program Voltage repeatability (successive program operations)<br>(programmed at 25°C)                                     | -25  | +25  | mV   |

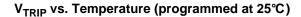

| V <sub>tv</sub>   | V <sub>TRIP</sub> program variation after programming (0-75°C). (prog rammed at 25°C)                                                       | -25  | +25  | mV   |

# $V_{TRIP}$ Programming Specifications $V_{CC}$ = 1.7-5.5V; Temperature = 0°C to 70° C

$V_{\mbox{TRIP}}$  programming parameters are periodically sampled and are not 100% tested.

#### TYPICAL PERFORMANCE

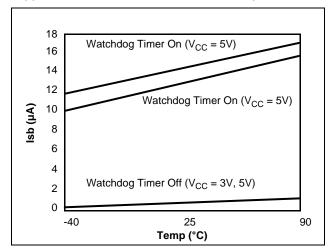

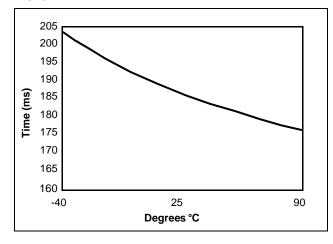

V<sub>CC</sub> Supply Current vs. Temperature (I<sub>SB</sub>)

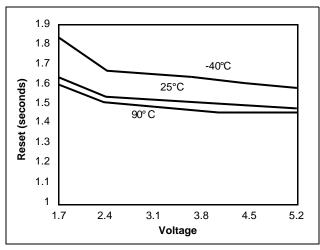

t<sub>WDO</sub> vs. Voltage/Temperature (WD1, 0 = 1, 1)

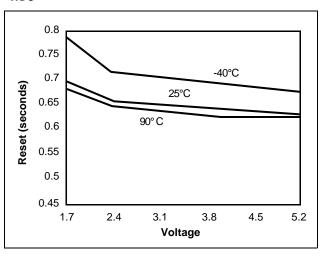

t<sub>WDO</sub> vs. Voltage/Temperature (WD1, 0 = 1, 0)

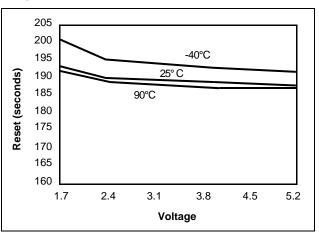

t<sub>WDO</sub> vs. Voltage/Temperature (WD1, 0 0 = 0, 1)

#### **PACKAGING INFORMATION**

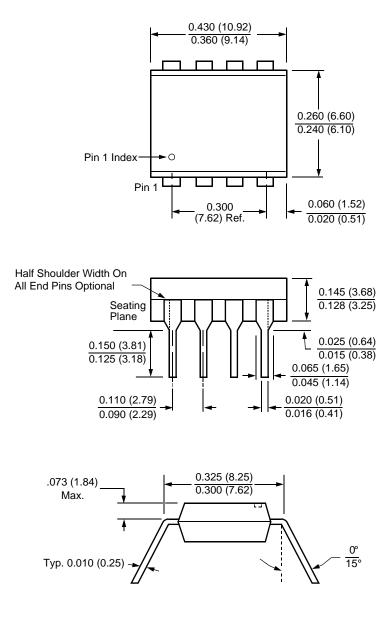

## 8-Lead Plastic Dual In-Line Package Type P

NOTE: 1. ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS) 2. PACKAGE DIMENSIONS EXCLUDE MOLDING FLASH

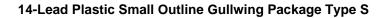

## **PACKAGING INFORMATION**

NOTE: ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS)

| V <sub>CC</sub> Range | V <sub>TRIP</sub><br>Range | Package    | Operating<br>Temperature Range | Part Number<br>RESET (Active LOW) | Part Number<br>RESET (Active HIGH) |

|-----------------------|----------------------------|------------|--------------------------------|-----------------------------------|------------------------------------|

| 4.5-5.5V              | 4.5.4.75                   | 8 pin PDIP | 0-70°C                         | X5643P-4.5A                       | X5645P-4.5A                        |

|                       |                            | 14L SOIC   | 0-70°C                         | X5643S14-4.5A                     | X5645S14-4.5A                      |

|                       |                            |            | -40-85°C                       | X5643S14I-4.5A                    | X5645S14I-4.5A                     |

| 4.5-5.5V              | 4.25.4.5                   | 8 pin PDIP | 0-70°C                         | X5643P                            | X5645P                             |

|                       |                            | 14L SOIC   | 0-70°C                         | X5643S14                          | X5645S14                           |

|                       |                            |            | -40-85°C                       | X5643S14I                         | X5645S14I                          |

| 2.7-5.5V              | 2.85-3.0                   | 14L SOIC   | 0-70°C                         | X5643S14-2.7A                     | X5645S14-2.7A                      |

| 2.7-5.5V              | 2.55-2.7                   | 14L SOIC   | 0-70°C                         | X5643S14-2.7                      | X5645S14-2.7                       |

#### **Ordering Information**

### Part Mark Information

$\label{eq:started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_started_st$

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com