# National Semiconductor

**PRELIMINARY**

# LH4004/LH4004C Wideband FET-Input Buffer/Amplifier

### **General Description**

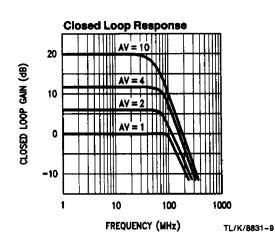

The LH4004 is an FET input, high speed differential amplifier optimized for unity gain applications. It eliminates most of the drawbacks of conventional open loop buffers and does not require compensation for unity and other low gain operations. It is an ideal choice for video distribution, driving flash converters, and summing amplifiers. Furthermore, the bandwidth does not decrease with increasing gain. At a closed loop gain of 4, the LH4004 still offers a 75 MHz bandwidth.

### **Features**

- ±0.5 dB gain flatness

- 500 V/µs slew rate

- Drives 50Ω directly

- 140 MHz bandwidth

- No external components required for unity gain operation

- Internal power supply bypassing

### **Applications**

- Unity gain buffer

- Low gain op amp

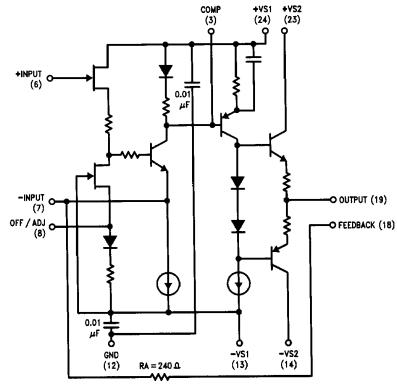

### **Simplified Schematic and Connection Diagram**

Order Number LH4004CD or LH4004D See NS Package Number D24D

TL/K/8831-1

### **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

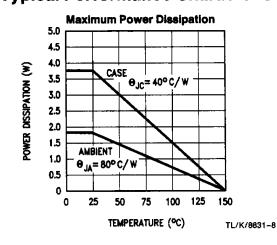

Supply Voltage, VS

Power Dissipation,  $P_D$   $T_A = 25^{\circ}\text{C}$ , derate linearly at 80°C/W  $T_C = 25^{\circ}\text{C}$ , derate linearly at 40°C/W

Input Voltage Range, VIN

1.8W

3.75W

$\pm V_S$

Operating Temperature Range, TA LH4004CD

LH4004D

-25°C to +85°C -55°C to +125°C

Storage Temperature Range, TSTG Maximum Junction Temperature, TJ

-65°C to +150°C 150°C

Lead Temperature (Soldering, < 10 sec)

300°C

ESD rating is to be determined.

# DC Electrical Characteristics $V_S = \pm 12V$ , $R_S = R_L = 50\Omega$ , $T_A = 25^{\circ}\text{C}$ unless otherwise noted (Note 1)

| Symbol              | Parameter                    |                                                                          |                   |      | Units                    |                          |                                     |

|---------------------|------------------------------|--------------------------------------------------------------------------|-------------------|------|--------------------------|--------------------------|-------------------------------------|

|                     |                              | Conditions                                                               |                   |      | Tested Limit<br>(Note 2) | Design Limit<br>(Note 3) | (Max Unless<br>Otherwise<br>Stated) |

| Vos                 | Input Offset Voltage         | V <sub>IN</sub> = 0V, T <sub>A</sub> = T <sub>J</sub> = 25°C<br>(Note 4) |                   | 8    | 15                       |                          | m∨                                  |

| V <sub>OS</sub> /ΔT | Offset Voltage Drift         |                                                                          |                   | 300  |                          | -                        | μV/°C                               |

| l <sub>B</sub>      | Input Bias Current           | $T_J = 25^{\circ}C$ , Pin 6 (Note                                        |                   | 400  |                          | pA                       |                                     |

|                     | Gain Accuracy                | $V_{IN} = \pm 1V$                                                        | $R_L = 500\Omega$ | 0.98 | 0.96                     | 0.93                     | V/V                                 |

|                     |                              | A <sub>V</sub> = +1                                                      | $R_L = 50\Omega$  | 0.98 | 0.96                     | 0.93                     | (Min)                               |

| V <sub>O</sub>      | Output Voltage Swing         | $V_{1N} = \pm 10V$                                                       | $R_L = 500\Omega$ | 9.6  | 9.2                      | 9.2                      | V (Min)                             |

| V <sub>O</sub>      | Output Voltage Current Swing | $V_{IN} = \pm 5V, R_L = 50\Omega$                                        |                   | ±4.5 | ±4                       | ·                        | V (Min)                             |

| Is                  | Supply Current               |                                                                          |                   | 35   | 40                       | -                        | mA                                  |

| PSRR                | Power Supply Rejection Ratio | $\pm$ V <sub>S</sub> = $\pm$ 11V to $\pm$ 15V                            |                   |      | 40                       | <del>.</del>             | dB (Min)                            |

# AC Electrical Characteristics $V_S = \pm 12V$ , $R_S = R_L = 50\Omega$ , $T_A = 25^{\circ}\text{C}$ (unless otherwise noted)

| Symbol              | Parameter              | Conditions $\Delta V_{\text{IN}} = 0.5 V$                                |                     |      | LH40040                  | Units                    |                                     |

|---------------------|------------------------|--------------------------------------------------------------------------|---------------------|------|--------------------------|--------------------------|-------------------------------------|

|                     |                        |                                                                          |                     | Тур  | Tested Limit<br>(Note 2) | Design Limit<br>(Note 3) | (Max Unless<br>Otherwise<br>Stated) |

| t <sub>r</sub>      | Small Signal Rise Time |                                                                          |                     | 3    |                          |                          | ns                                  |

| ts                  | Settling Time to 0.5%  | $V_{IN} = -2.5V \text{ to } +$                                           | -2.5V               | 30   |                          |                          | ns                                  |

| $f_{-3\mathrm{dB}}$ | Small Signal Bandwidth | $V_{IN} = -10  dBm$                                                      | A <sub>V</sub> = +1 | 140  | 125                      |                          | MHz                                 |

|                     |                        |                                                                          | A <sub>V</sub> = +4 | 85   | 75                       |                          | (Min)                               |

|                     | Large Signal Bandwidth | $V_{OUT} = \pm 2.5V$                                                     | A <sub>V</sub> = +1 |      | 70                       |                          | MHz                                 |

|                     | Gain Flatness          | $V_{IN} = -10 \text{ dBm}$ $A_{V} = +1$ $f = 0-50 \text{ MHz}$           |                     |      | ±0.5                     |                          | dB                                  |

|                     | Harmonic Distortion    | Second Order V <sub>IN</sub> = 4Vp-p, f <sub>IN</sub> =                  | = 10 MHz            |      |                          |                          | dB                                  |

| SR                  | Slew Rate              | $V_{IN} = -2.5V \text{ to } +2.5V$<br>$V_{IN} = +2.5V \text{ to } -2.5V$ |                     | 1500 |                          | 1200                     | V/µs                                |

|                     |                        |                                                                          |                     | 600  |                          | 500                      | (Min)                               |

DC Electrical Characteristics  $V_S=\pm 12V,\,R_S=R_L=50\Omega,\,T_A=25^{\circ}C$  unless otherwise noted (Notes 1 & 5)

| Symbol              |                                 | Conditions                                      |                   |      | LH4004                   | Units                    |                                     |

|---------------------|---------------------------------|-------------------------------------------------|-------------------|------|--------------------------|--------------------------|-------------------------------------|

|                     | Parameter                       |                                                 |                   |      | Tested Limit<br>(Note 2) | Design Limit<br>(Note 3) | (Max Unless<br>Otherwise<br>Stated) |

| Vos                 | Input Offset Voltage            | T <sub>A</sub> = T <sub>J</sub> = 25°C (Note 4) |                   | 8    | 15                       |                          | mV                                  |

| V <sub>OS</sub> /ΔT | Offset Voltage Drift            |                                                 |                   | 300  |                          |                          | μV/°C                               |

| I <sub>B</sub>      | Input Bias Current              | $T_A = T_J = 25^{\circ}C$ , Pin 6 (Note 4)      | )                 |      | 400                      |                          | pA                                  |

| J                   | ·                               |                                                 |                   |      | 400                      |                          | nA                                  |

|                     | Gain Accuracy                   | $V_{IN} = \pm 1V$                               | $R_L = 500\Omega$ | 0.98 | 0.96                     |                          |                                     |

|                     |                                 | A <sub>V</sub> = +1                             |                   | 0.50 | 0.93                     |                          | V/V<br>(Min)                        |

|                     |                                 |                                                 | $R_L = 50\Omega$  | 0.98 | 0.96                     |                          |                                     |

|                     |                                 |                                                 |                   |      | 0.93                     |                          |                                     |

| V <sub>O</sub>      | Output Voltage Swing            | V <sub>IN</sub> = ±10V                          | $R_L = 500\Omega$ | 9.6  | 9.2                      |                          | V (Min)                             |

| V <sub>O</sub>      | Output Voltage Swing            | $V_{IN} = \pm 5V, R_L = 50\Omega$               |                   | ±4.5 | ± <b>4</b>               |                          | V (Min)                             |

| l <sub>s</sub>      | Supply Current                  |                                                 |                   | 35   | 40                       |                          |                                     |

| PSRR                | Power Supply<br>Rejection Ratio |                                                 |                   |      | 40                       |                          | dB (Min)                            |

### AC Electrical Characteristics $V_S=\pm 12V, R_S=R_L=50\Omega, T_A=25^{\circ}C$ unless otherwise noted

| Symbol         | Parameter Small Signal Rise Time | Conditions $\Delta V_{\text{IN}} = 0.5 V$                         |                     |              | Units                    |                          |                                     |

|----------------|----------------------------------|-------------------------------------------------------------------|---------------------|--------------|--------------------------|--------------------------|-------------------------------------|

|                |                                  |                                                                   |                     | <b>Typ</b> 3 | Tested Limit<br>(Note 2) | Design Limit<br>(Note 3) | (Max Unless<br>Otherwise<br>Stated) |

| t <sub>r</sub> |                                  |                                                                   |                     |              |                          |                          |                                     |

| ts             | Settling Time to 0.5%            | $V_{IN} = -2.5V \text{ to } +2.5V$                                |                     | 30           |                          |                          | ns                                  |

| $f_{-3dB}$     | Small Signal Bandwidth           | $V_{IN} = -10  dBm$                                               | A <sub>V</sub> = +1 |              | 125                      |                          | MHz                                 |

|                | _                                |                                                                   | A <sub>V</sub> = +4 |              | 75                       |                          | (Min)                               |

|                | Large Signal Bandwidth           | $V_{OUT} = \pm 2.5V$                                              | A <sub>V</sub> = +1 |              | 70                       |                          | MHz                                 |

|                | Gain Flatness                    | $V_{IN} = 100 \text{ mV p-p}$ $A_{V} = +1$ $f = 0-50 \text{ MHz}$ |                     |              | ±0.5                     |                          | dB                                  |

|                | Harmonic Distortion              | Second Order V <sub>IN</sub> = 4V p-p, f <sub>IN</sub>            | = 10 MHz            |              |                          |                          | dB                                  |

| SR             | Slew Rate                        | $V_{IN} = -2.5V \text{ to } +2.5V$                                |                     | 1500         |                          | 1200                     | V/μs                                |

|                | $V_{IN} = +2.5^{\circ}$          |                                                                   | -2.5V               | 600          |                          | 500                      | (Min)                               |

Note 1: Boldface limits are guaranteed over full temperature range. Operating ambient temperature range of LH4004C is -25°C to +85°C, and LH4004 is -55°C to +125°C.

Note 2: Tested limits are guaranteed and 100% production tested.

Note 3: Design limits are guaranteed (but not 100% production tested) over the indicated temperature range. These limits are not used to calculate outgoing quality

Note 4: Specification is at 25°C junction temperature due to requirements of high speed automatic testing. Actual values at operating temperature will exceed value at  $T_J = 25^{\circ}C$ .

Note 5: When the LH4004 is operated at elevated temperature (such as 125°C), some form of heat sinking or forced air cooling is required. The quiescent power with  $V_S$  of  $\pm 12V$  is 960 mW, whereas the package is only rated to 800 mW without a heatsink at 125°C.

### **Application Hints**

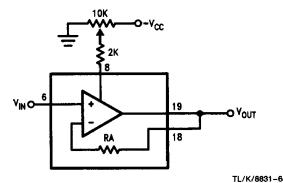

The front page figure shows the simplified schematic which includes the feedback resistor and the decoupling capacitors.

The essential difference from other op amps is that both inputs are radically different, the non-inverting input goes to a FET buffer follower and the inverting input is connected to the second stage emitter node. This topology is responsible for the unique bandwidth characteristic and transfer function of the amplifier.

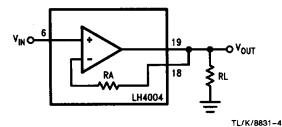

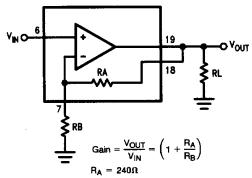

Let's consider the connection diagram of *Figure 1*. The typical transfer function in the case of a classical op amp would be:

$$\frac{V_{OUT}}{V_{IN}} = \frac{K(s)}{1 + K(s)/B}$$

where B =  $\frac{R_A + R_B}{R_B}$  and K(s) is the open loop gain of the amplifier and is frequency dependent. By rearranging the formula, we find;

(1)

$$\frac{V_{OUT}}{V_{IN}} = B * \frac{K(s)}{K(s) + B}$$

For the LH4004, a small signal analysis shows that the difference between the two inputs turns the previous typical equation into:

(2)

$$\frac{V_{OUT}}{V_{IN}} = B * \frac{K(s)}{K(s) + B + m R_A}$$

where m is an internal parameter to the device and K(s) is approximately 70 dB at DC with a  $50\Omega$  load.

In both equations, the second term is negligible when the open loop gain of the amplifier, K(s), approaches infinity, but in equation (1), when the signal frequency reaches a point where K(s) is small, say K(s) = 10 or less, then the term will be very sensitive to the value of the closed loop gain B and  $V_{OUT}/V_{IN}$  will fall earlier as B increases.

In equation (2), m is approximately 0.19 and  $R_A$  is provided inside the package, with a value which has been chosen to be  $240\Omega.$  The term  $mR_A$  is therefore equal to 46 and will dominate the term B as long as it is kept below 5. The result is that  $V_{OUT}/V_{IN}$  will not be as dependent on B as with traditional topologies. The gain will still fall with the open loop gain K(s) as the frequency increases, but the roll off will be virtually independent of the closed loop gain B.

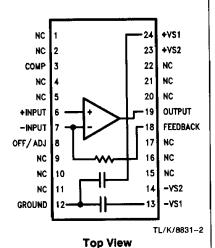

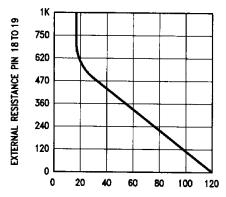

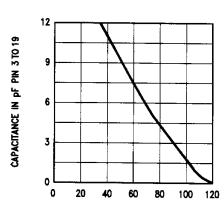

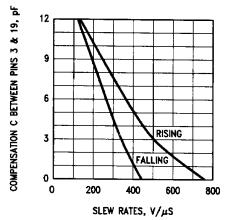

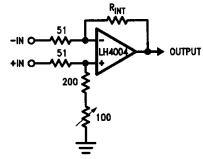

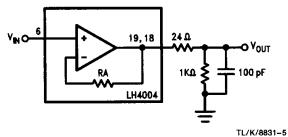

Resistor R<sub>B</sub> sets the overall closed loop gain, but has very little effect on stability and bandwidth. Another peculiarity of the LH4004 is that the loop compensation can be accomplished by changing the value of resistor R<sub>A</sub> (Figure 2). Even though this such as settling time, overshoot and phase margin, it will not affect the slew rate. Although this resistive compensation scheme is adequate in most cases, an alternate method is to place a capacitor between pins 3 and 19 (Figure 3). This method of compensation also reduces the device slew rate (Figure 4).

### **Low Gain Operation**

The small amount of stray capacitance present at the inverting input can cause peaking which increases with decreasing gain. The gain set resistor R<sub>B</sub> (in *Figure 1*) is effectively

in parallel with this capacitance and so a frequency domain pole results. With a small  $R_B$ , this pole is at a high frequency and it affects the closed loop gain of the LH4004 only slightly. At lower values of gain, this pole becomes significant. For example, at a gain of +2, the gain may peak as much as 1.5 dB to 2 dB at 100 MHz.

BANDWIDTH IN MHz FOR UNITY GAIN CONFIGURATION

TL/K/8831-10

FIGURE 2. Bandwidth vs Rext

BANDWIDTH IN MHz FOR UNITY GAIN CONFIGURATION

TL/K/8831-11

### FIGURE 3. Bandwidth vs Cext

TL/K/8831-13

FIGURE 4. Slew Rates vs Compensation C

### **Typical Applications**

FIGURE 5. Unity Gain Buffer

Note: Adjust pot for best CMRR.

TL/K/8831-12

FIGURE 6. Differential Amplifier

FIGURE 7. Driving Capacitive Loads

FIGURE 8. Offset Adjust

FIGURE 9. LH4004 Used in Amplifier Applications

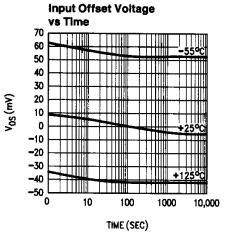

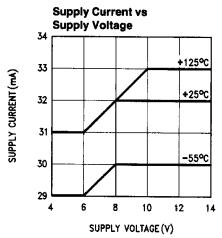

### **Typical Performance Characteristics**

TL/K/8831-7

## **Typical Performance Characteristics** (Continued)

TL/K/8831-14

TL/K/8831-15

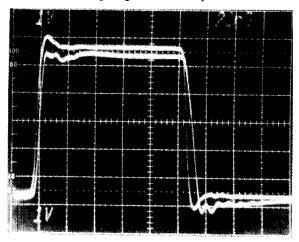

### Large Signal Pulse Response

TL/K/8831-16

Top Trace = Input Bottom Trace = Output

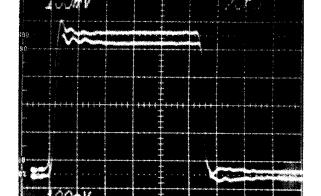

Small Signal Pulse Response

TL/K/8831-17

Top Trace = Input Bottom Trace = Output