# TC9192P/F

DOUBLE PLL FOR MOTOR CONTROL

This is a LSI designed for motor-controlling the copying machine of which motor-rotation speed is necessary to be varied freely. With built-in PLL and VCO for reference signal generation, reference frequency can voluntarily be varied externally.

- . Through using built-in VCO, PD, phase comparator and divider reference frequencies can be obtained.

- . AFC and APC applied with 8-bit D/A converter system is incorporated, and transistor of bipolar type is provided at the output for Buffer Amplifier

- . Lock range can be switched.

- . Reference voltage output for filiter-amplifier is provided.

- . Lock detection output and reverse rotation signal output are provided.

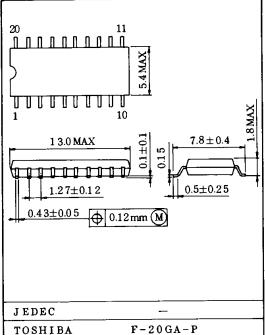

# 18 10 23MAX 23MAX 23MAX 250 254±0.25 2.54±0.25 40.1 1.4±0.15 Lead pitch is 2.54 and tolerance is ±0.25 against theoretical center of each lead that is obtained on the basis of No.1 and No.18 leads. JEDEC TOSHIBA 3D18A-P

# Unit in mm

Unit in mm

### MAXIMUM RATINGS (Ta=25°C)

| CHARACTERISTIC        | SYMBOL            | RATING                    | UNIT |

|-----------------------|-------------------|---------------------------|------|

| Power Supply Voltage  | $v_{\mathrm{DD}}$ | -0.3~7.0                  | v    |

| Input Voltage         | VIN               | -0.3~V <sub>DD</sub> +0.3 | v    |

| Power Dissipation     | PD                | 300                       | mW   |

| Operating Temperature | Topr              | -30~75                    | °C   |

| Storage Temperature   | Tstg              | -55~125                   | °C   |

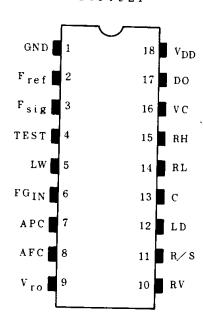

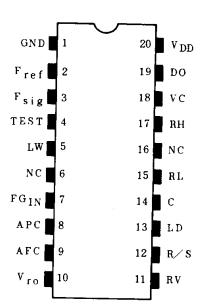

### PIN CONNECT

TC9192P

TC9192F

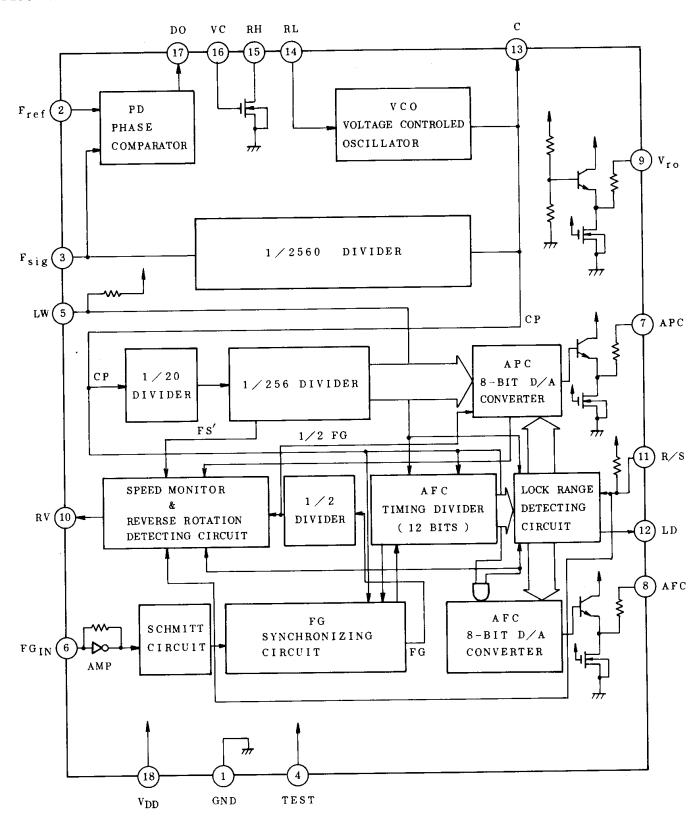

### BLOCK DIAGRAM TC9192P

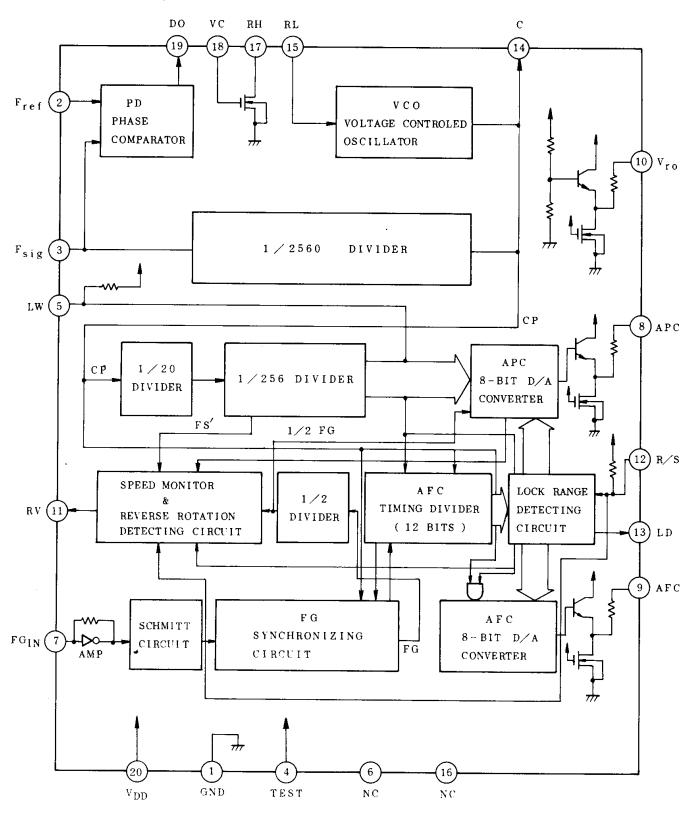

BLOCK DIAGRAM TC9192F

| CHARACTERI                     | STIC             | SYMBOL                           | TEST CONDITION                            | ON                  | MIN.                | TYP.                 | MAX.                 | U        |

|--------------------------------|------------------|----------------------------------|-------------------------------------------|---------------------|---------------------|----------------------|----------------------|----------|

| Operating Power Supply Voltage |                  | $v_{\mathrm{DD}}$                |                                           |                     | 4.5                 | ~                    | 5.5                  |          |

| Power Supply Cu                | rrent            | $I_{DD}$                         |                                           | *                   | -                   | 7                    | 20                   |          |

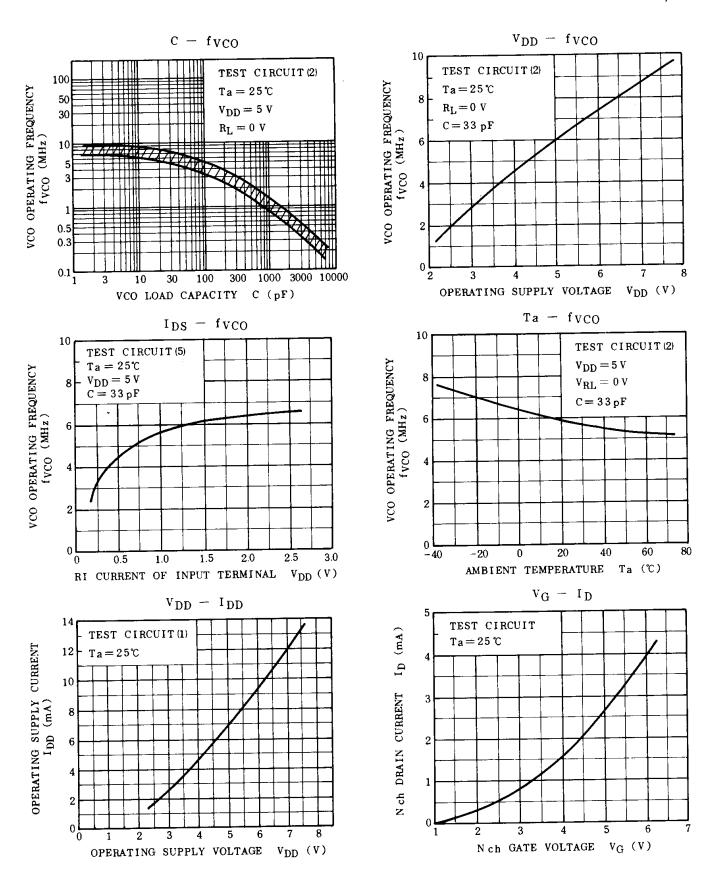

| VCO BLOCK                      |                  |                                  |                                           | · · · · · · · · ·   |                     |                      |                      |          |

| Max. Operating                 | Frequency        | f <sub>VCO Max</sub>             |                                           | *                   | 4.0                 | 6.0                  |                      | N        |

| VCO Applicable Range           |                  | fVCO                             | Constant of C is $\star$ varied with fVCO |                     | 0.5                 | ~                    | 4.0                  | <u> </u> |

| VCO Deviation                  |                  | ⊿fvco                            | C=Constant, R <sub>L</sub> =2.0V *        |                     |                     | ±50                  |                      |          |

| VCO Fsig Freque                | ncy Range        | fCPIN                            | F <sub>sig</sub> N=2560 *                 |                     | 0.5                 | ~_                   | 4.0                  | N        |

| FG AMPLIFIER BL                | OCK              | <del>,</del>                     |                                           |                     |                     |                      |                      |          |

| Operating Frequ                |                  | fFG                              | V <sub>IN</sub> =0.5Vp-p                  | *                   |                     | ~                    | 10                   | 1        |

| Input Operating                |                  | VFG                              | ffg=10kHz, Sine                           | wave *              | 0.5                 | ~                    | V <sub>DD</sub> -0.5 |          |

| Fref Frequency                 |                  | fref                             |                                           | *                   | 0.2                 | ~                    | 2.0                  |          |

| APC, AFC, D/A C                | ONVERTER B       | LOCK                             |                                           |                     |                     |                      |                      |          |

| Max. Deviation                 |                  |                                  | Measuring at buf                          | fer                 | _                   | <b>±2.</b> 5         | ±6.5                 |          |

| Resolution                     |                  |                                  |                                           |                     | _                   | V <sub>DD</sub> /256 | _                    |          |

| Ladder Resistance              |                  | RD                               |                                           |                     | 30                  | 50                   | 70                   |          |

|                                |                  | T CURRENT                        | (APC, AFC, V <sub>ro</sub> T              | ERMINAL             | )                   |                      |                      |          |

|                                | "H" Level        | I <sub>OHB</sub>                 | v <sub>OH</sub> =3v                       | -                   | _                   | -1.6                 | -0.8                 |          |

| Output Current                 | "L" Level        | IOLB                             | V <sub>OL</sub> =2V                       |                     | 30                  | 50                   | 200                  | L        |

| Output Voltage                 | Reference Output |                                  | 1.6                                       | 1.9                 | 2.2                 | L                    |                      |          |

| PHASE COMPARATO                | OR CHARACTE      | RISTIC (I                        | <del></del>                               |                     | <del></del>         |                      |                      |          |

|                                | "H" Level        | I <sub>OHDO</sub>                |                                           |                     | ~                   |                      | -1.0                 |          |

| Output Current                 | "L" Level        | <del></del>                      |                                           |                     | 1.0                 | 2.0                  | ~                    |          |

| Output Leak Cur<br>at OFF      |                  | I <sub>OZD</sub> 0               |                                           |                     | _                   | _                    | ±0.1                 | _        |

| Input Leak Cur                 | rent             | I <sub>IH</sub> /I <sub>IL</sub> | Fref, VC termina                          | a1                  | ~                   | -                    | ±1.0                 | L        |

| Pull-up Resista                |                  | RIN                              | LW, R/S termina                           | <u> </u>            | 15                  | 30                   | 45                   | L        |

|                                | "H" Level        | VIH                              | FG <sub>IN</sub> , LW, R/S to             | erminal             | 0.7×V <sub>DD</sub> | ~                    | VDD                  |          |

| Input Voltage                  | "L" Level        | VIL                              | Fref                                      |                     | 0                   | ~                    | 0.3×V <sub>DD</sub>  |          |

|                                | "H" Level        | ІОН                              |                                           | VOH=4V              | _                   | -1.0                 | -0.5                 |          |

| Output Current                 | "L" Level        | IOL                              | terminal                                  | V <sub>OL</sub> =1V | 0.5                 | 1.0                  |                      | L        |

| Nch OPEN DRAIN                 | CURRENT          | •                                |                                           |                     |                     |                      |                      | _        |

| Nch ON Current                 |                  | I <sub>OLD</sub>                 | DII tomminal                              | VG=5V               | 1.5                 | 2.5                  | _                    |          |

| Nch OFF Current                |                  | IOID                             | 1                                         | VG=0V               | _                   |                      | ±1.0                 |          |

| men ori ourien                 | <del> </del>     | <del></del>                      | $V_{DD}=4.5V\sim5.5V$ , T                 | 2=-30~75            | i°C                 |                      |                      |          |

## FUNCTIONAL DISCRIPTION OF EACH PIN

| PIN No. SYMBOL |      | CVMROI            | FUNCTION, OPERATION                                                                                                  | REMARKS                              |  |

|----------------|------|-------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------|--|

| P              | F    | SIMOL             | FUNCTION, OFERATION                                                                                                  | REPIARES                             |  |

| 18             | 20   | V <sub>DD</sub>   | Power supply voltage terminal and grounding                                                                          |                                      |  |

| 1              | 1    | GND               | terminal.                                                                                                            |                                      |  |

| 2              | 2    | Fref              | Reference frequency input terminal for phase comparator.                                                             | C-MOS input                          |  |

| 3              | 3    | $F_{sig}$         | 1/2560 dividing output terminal of VCO frequency, internally comparison signal is made.                              | C-MOS output                         |  |

| 5              | 5    | LW                | Switching terminal of lock range. at LW="L", double range.                                                           | Built-in pull-up<br>resistance speed |  |

| 6              | 7    | FGIN              | Pulse input terminal for indicating the rotation speed of motor.                                                     | Built-in amp.                        |  |

| 7              | 8    | APC               | Output terminal of APC 8-bit D/A converter output.                                                                   | Built-in bipolar<br>transistor       |  |

| 8              | 9    | AFC               | Output terminal of AFC 8-bit D/A converter output.                                                                   | Built-in bipolar<br>transistor       |  |

| 9              | 10   | V <sub>ro</sub> . | Output terminal for reference voltage.                                                                               | Built-in bipolar<br>transistor       |  |

| 10             | 11   | RV                | Reverse rotation signal for output driver.                                                                           | C-MOS output                         |  |

| 11             | 12   | R/S               | RUN/STOP switching terminal of motor at R/S="L", RUN. at R/S="H", STOP                                               | Built-in pull-up<br>resistance       |  |

| 12             | 13   | LD                | Lock detecting terminal. When the rotation frequency is within lock range, "H" level, and in other cases, "L" level. | C-MOS output                         |  |

| 13             | 14   | С                 | Terminal attached with capacitor for adjusting frequency. Internal control signal is made.                           |                                      |  |

| 14             | 15   | RL                | Current control terminal for controlling VCO frequency.                                                              |                                      |  |

| 15             | 17   | RH                | Current control output terminal for VCO                                                                              | VC RH                                |  |

| 16             | 18   | VC                | Voltage control input terminal for VCO                                                                               |                                      |  |

| 17             | 19   | DO                | Output terminal of phase comparator                                                                                  | C-MOS input                          |  |

| 4              | 4    | Tset              | Input terminal of internal test. Generally ground.                                                                   | C-MOS input                          |  |

| _              | 6,16 | NC                | No connect                                                                                                           |                                      |  |

### EXPLANATION OF OPERATION

TC9192P/F has double PLL which is consist of AFC/APC loop for motor-controlling and phase feedback loop for reference signal. In the following operation of respective block is explained.

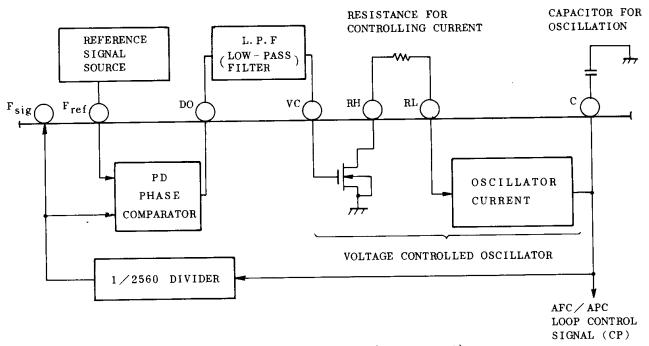

### 1. Phase Feedback Loop

- (1) Voltage controlled oscillator terminal (C,RL,RH,VC)

- . Voltage controlled oscillator (VCO) is consist of the Nch open drain FET (VC,RH, terminal) and current controlled oscillator (RL,C terminal) combinated.

- VCO is an oscillator of which oscillation frequency is controlled by given control voltage. The control voltage and oscillation frequency are proportional.

- . The operation frequency range of VCO is 0.5~4MHz.

- . Frequency which is obtained by VCO becomes control signal (CP) of AFC, APC loop in next step.

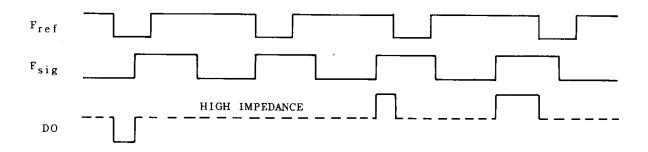

- (2) Phase comparator output terminal (Fsig, Fref, DO)

- . Phase comparator detects the input pulse difference, and outputs at DO the positive and the negative pulses proportioned with the phase difference.

### PHASE COMPARATOR TIMING CHART

• Fref terminal is reference signal input terminal of APC/AFC loop control signal (CP), the motor speed (the number of FG pulses of motor) is decided by it.

The relations between FG,  $F_{ref}$  and FG is as follows;

$f_{X}(CP)=2560 \times Fref[Hz]$ : Relation between Fref and control signal (CP)

$f_x(CP) = 20 \times 128 \times FG[Hz]$ : Relation between FG and control signal (CP)

- ... This relation becomes "FG=Fref[Hz]"

- . Fref input terminal is a C-MOS structure.

- . Fsig output terminal is output comparison signal of phase comparator.

### 2. APC/AFC Loop

- (1) FG pulse input terminal (FGIN)

- . This is the input terminal of FG pulse for indicating the motor speed, and this signal becomes the comparison frequency of internal PLL.

- . Since the amplifier and the Schmitt circuit are incorporated, operation is made with the small amplitude through the coupling capacitor.

TOSHIBA CORPORATION

# TC9192P/F

- (2) Output terminals (APC, AFC) of phase control system (APC) and speed control system.

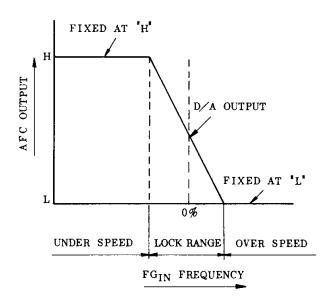

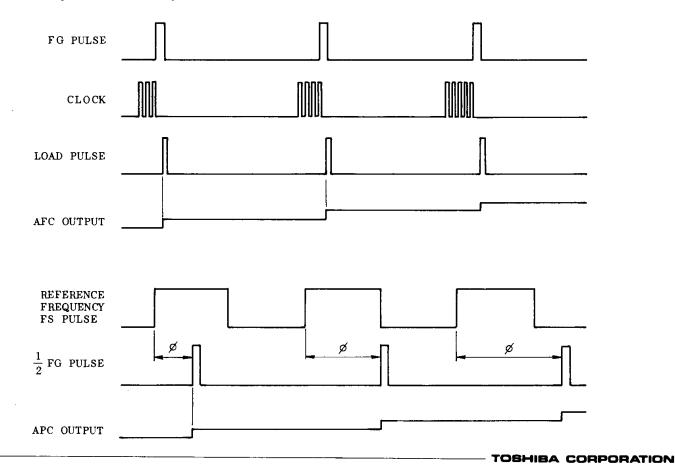

- . AFC is F-V converter against FGIN frequency and is fabricated with 8-bit D/A converter.

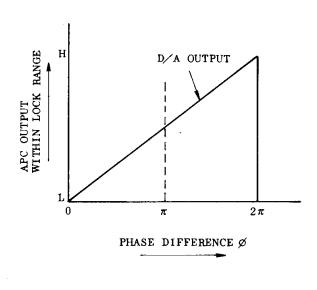

- . APC is the phase comparator ( $\phi$ -V converter) for comparing the phase difference  $\phi$  between  $\frac{1}{2}$ FG signal and the reference signal FS', and is also fabricated with 8-bit D/A converter. (Note) FS'=  $\frac{1}{2}$ FS

- . Both APC and AFC perform three kinds of operations described below.

- a) When FGIN frequency is within the lock range, both APC and AFC perform the normal operation against FGIN.

Against the reference synchronization FS, the lock range is

at LW="L",

$$+9.3\%$$

,  $-10.6\%$  (about  $\pm 10\%$ )

(Note) Reference frequency FS =

$$\frac{f_x(CP)}{20 \times 128}$$

[Hz]

- b) When FGIN frequency is under the lock range (under speed), the outputs of APC and AFC are fixed at "H" level.

- c) When FGIN frequency is over the lock range (over speed), the outputs of APC and AFC are fixed at "L" level.

- . When the motor is in STOP state (R/S=H or Open), both the outputs of AFC and APC are fixed at "L" level.

- . Bipolar transformer is incorporated at the output stage of both APC and AFC.

CHANGE OF APC OUTPUT AGAINST FGIN FREQUENCY

CHANGE OF APC OUTPUT AGAINST PHASE DIFFERENCE  $\phi$

- . Timing charts of AFC and APC within lock range

- a. AFC (speed control system)

# TC9192P/F

- (3) Output terminal for reference voltage generation (Vro)

- .  $V_{\text{ro}}$  is the transistor output terminal for the reference voltage of the operational amplifier which controls the motor by means of synthesizing the outputs of APC and AFC.

- .  $V_{\text{ro}}$  is fixed at  $\frac{1}{2}$  VDD -VF internally through dividing the resistance, and the output is fabricated into bipolar transistor construction.

- (4) Lock range switching input terminal (LW)

- . This is the terminal for switching the lock range of APC and AFC, and two kinds of lock ranges can be selected through operating this terminal.

- at LW="H", normal lock range (±5%)

- at LW="L", double lock range (±10%)

- (5) RUN/STOP input terminal (R/S)

- . RUN/STOP signals of motor are input. RUN="L", STOP="H" or open

- . During RUN(R/S=L), APC, AFC and LD perform the normal operation against  $FG_{\rm IN}$  frequency. During STOP(R/S=H or Open), APC, AFC and LD are all fixed at "L" level.

- . Pull-up resistance and chattering prevention circuit are incorporated.

- (6) Lock detection terminal (LD) This is the output terminal for lock detection. When FGIN frequency is within lock range, the terminal is at "H" level, and in other cases, at "L" level.

- (7) Reverse rotation signal output terminal (RV)

- . RV is the reverse rotation signal output for applying the brake to the motor when the motor is changed to STOP state.

- . When STOP state is turned out, RV becomes "H" level, and when the frequency of FGIN becomes below  $\frac{1}{8}$  FS, "L" level. In other cases, RV is fixed at "L" level.

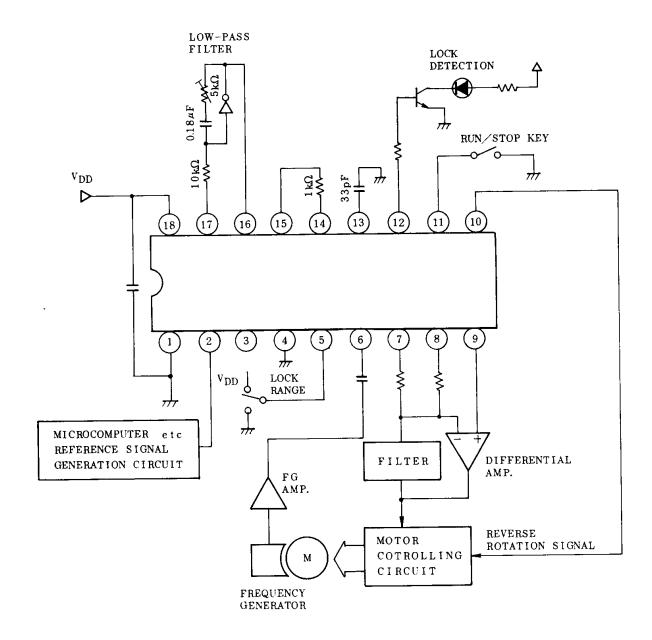

### EXAMPLE OF APPLICATION CIRCUIT (Pin connect is TC9192P)

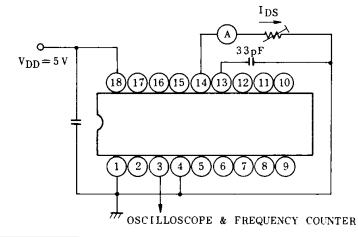

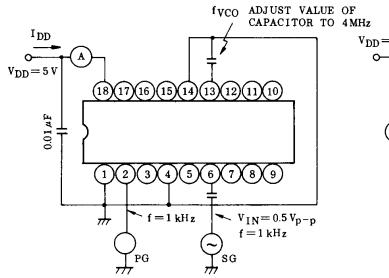

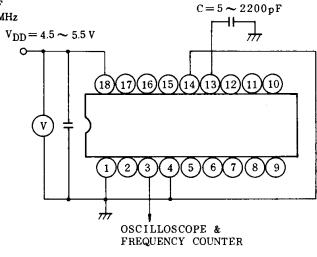

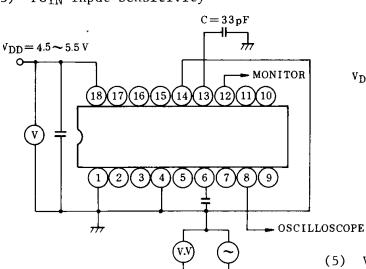

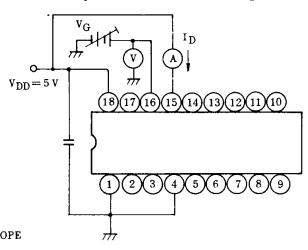

CHARACTERISTIC TEST CIRCUIT (Pin connect is TC9192P)

- (1) Operating Supply Current (IDD)

- (2) VCO Operating Frequency Range (fVCO)

(3) FGIN Input Sensitivity

(4) Nch Open Drain Current (ID)

(5) VCO Operating Frequency Range (2) (fvco)