# SX20AC/SX28AC

Configurable Communications Controllers with EE/Flash Program Memory, In-System Programming Capability and On-Chip Debug

# 1.0 **PRODUCT OVERVIEW**

#### 1.1. Introduction

The Parallax SX family of configurable communications controllers is fabricated in an advanced CMOS process technology. The advanced process, combined with a RISC-like architecture, allows high-speed computation, flexible I/O control, and efficient data manipulation. Throughput is enhanced by operating the device at frequencies up to 75 MHz and by optimizing the instruction set to include mostly single-cycle instructions. The deterministic architecture of the SX provides reliable performance for time-critical applications. In addition, the SX architecture is flash-based and therefore reprogrammable. On-chip functions include a generalpurpose 8-bit timer with prescaler, an analog comparator, a brown-out detector, a watchdog timer, a power-save mode with multi-source wakeup capability, an internal R/C oscillator, user-selectable clock modes, and highcurrent outputs. These features enable the SX to be used as a general-purpose, high-speed microcontroller in a variety of applications.

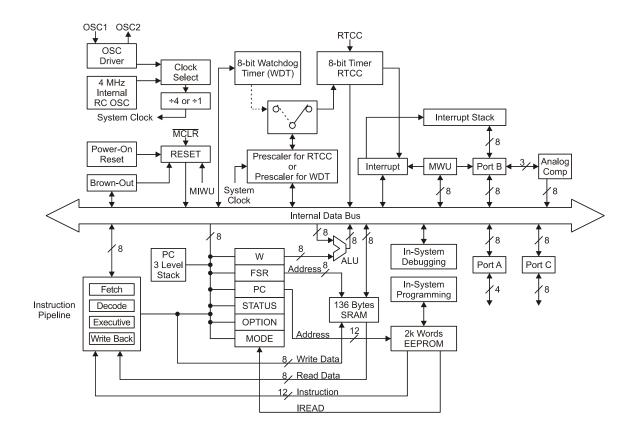

#### Figure 1-1: Block Diagram

Parallax and the Parallax logo are trademarks of Parallax, Inc. SX is a trademark of Ubicom Inc, used with permission.

$I^2C$  is a trademark of Philips Corporation. All other trademarks are the property of their respective holders.

#### **Table of Contents**

| <b>1.0</b><br>1.1.<br>1.2.<br>1.3.<br>1.4.<br>1.5.<br>1.6.<br>1.7.<br>1.8. | Product Overview       1         Introduction       1         Key Features       3         Architecture       4         Programming Benefits in Assembly and High-Level Languages 4         Programming and Debugging Support       4         Applications       4         Support       4         Part Numbering       5               |

|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>2.0</b><br>2.1.<br>2.2.<br>2.3.                                         | Connection Diagrams       6         Pin Assignments       6         Pin Descriptions       6         Typical Connection Diagrams       7                                                                                                                                                                                                |

| <b>3.0</b><br>3.1.<br>3.2.<br>3.2.1.<br>3.2.2.<br>3.2.2.<br>3.2.3.         | Port Descriptions       9         Reading and Writing the Ports       9         Read-Modify-Write Considerations       11         Port Configuration       11         MODE Register       11         Port Configuration Registers       11         Port Configuration Registers       11         Port Configuration Upon Reset       12 |

| <b>4.0</b><br>4.1.<br>4.2.<br>4.3.                                         | Special-Function Registers         13           PC Register (02h)         13           STATUS Register (03h)         13           OPTION Register         14                                                                                                                                                                            |

| <b>5.0</b><br>5.1.<br>5.2.<br>5.3.                                         | <b>Device Configuration Registers15</b><br>FUSE Word (Read/Program at FFFh in Main Memory Map)15<br>FUSEX Word (Read/Program via Programming Command)16<br>DEVICE Word (Hard-Wired Read-Only)16                                                                                                                                         |

| <b>6.0</b><br>6.1.<br>6.1.1.<br>6.1.2.<br>6.2.<br>6.2.1.                   | Memory Organization         17           Program Memory         17           Program Counter         17           Subroutine Stack         17           Data Memory         17           File Select Register (04h)         17                                                                                                          |

| <b>7.0</b><br>7.1.<br>7.2.                                                 | Power Down Mode19Multi-Input Wakeup19Port B MIWU/Interrupt Configuration20                                                                                                                                                                                                                                                              |

| 8.0                                                                        | Interrupt Support21                                                                                                                                                                                                                                                                                                                     |

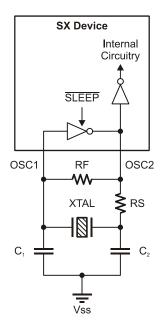

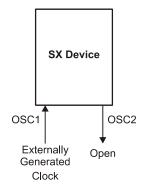

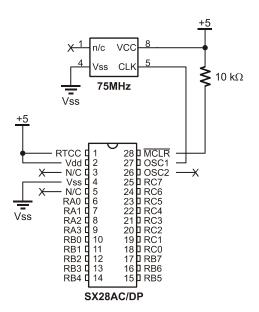

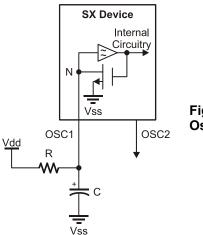

| <b>9.0</b><br>9.1.<br>9.2.<br>9.3.<br>9.4.                                 | Oscillator Circuits23XT, LP or HS modes2375 MHz Operation25External RC Mode25Internal RC Mode25                                                                                                                                                                                                                                         |

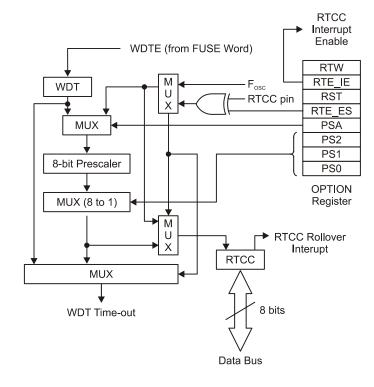

| <b>10.0</b><br>10.1.                                                       | Real Time Clock (RTCC)/Watchdog Timer                                                                                                                                                                                                                                                                                                   |

| 10.2.<br>10.3.       | Watchdog Timer<br>The Prescaler                  |    |

|----------------------|--------------------------------------------------|----|

| 11.0                 | Comparator                                       | 27 |

| 12.0                 | Reset                                            | 28 |

| 13.0                 | Brown-Out Detector                               | 29 |

| 14.0                 | Register States upon Different Reset Operations. | 30 |

| 15.0                 | Instruction Set                                  | 31 |

| 15.1.                | Instruction Set Features                         | 31 |

| 15.2.                | Instruction Execution                            | 31 |

| 15.3.                | Addressing Modes                                 | 31 |

| 15.4.                | RAM Addressing                                   | 32 |

| 15.5.                | The Bank Instruction                             | 32 |

| 15.6.                | Bit Manipulation                                 |    |

| 15.7.                | Input/Output Operation                           |    |

| 15.8.                | Increment/Decrement                              |    |

| 15.9.                | Loop Counting and Data Pointing Testing          |    |

| 15.10.               | Branch and Loop Call Instructions                |    |

| 15.10.1.             | Jump Operation                                   |    |

| 15.10.2.             | Page Jump Operation                              |    |

| 15.10.3.<br>15.10.4. | Call Operation<br>Page Call Operation            | 33 |

| 15.11.               | Return Instructions.                             |    |

| 15.12.               | Subroutine Operation                             |    |

| 15.12.1.             | Push Operation                                   |    |

| 15.12.2.             | Pop Operation                                    | 34 |

| 15.13.               | Comparison and Conditional Branch Instructions   | 34 |

| 15.14.               | Logical Instruction                              |    |

| 15.15.               | Shift and Rotate Instructions                    | 34 |

| 15.16.               | Complement and SWAP                              | 34 |

| 16.0                 | Native SX Instruction Set Summary Tables         | 35 |

| 16.1.                | Equivalent Assembler Mnemonics                   |    |

| 17.0                 | Electrical Characteristics                       |    |

| 17.1.                | Absolute Maximum Ratings                         |    |

| 17.2.                | DC Characteristics                               |    |

| 17.3.                | AC Characteristics                               |    |

| 17.4.                | Comparator DC and AC Specifications              |    |

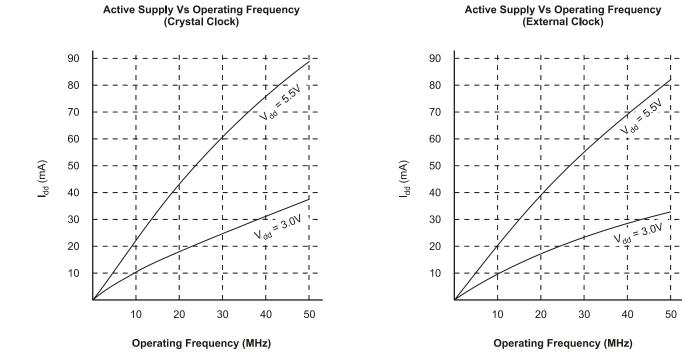

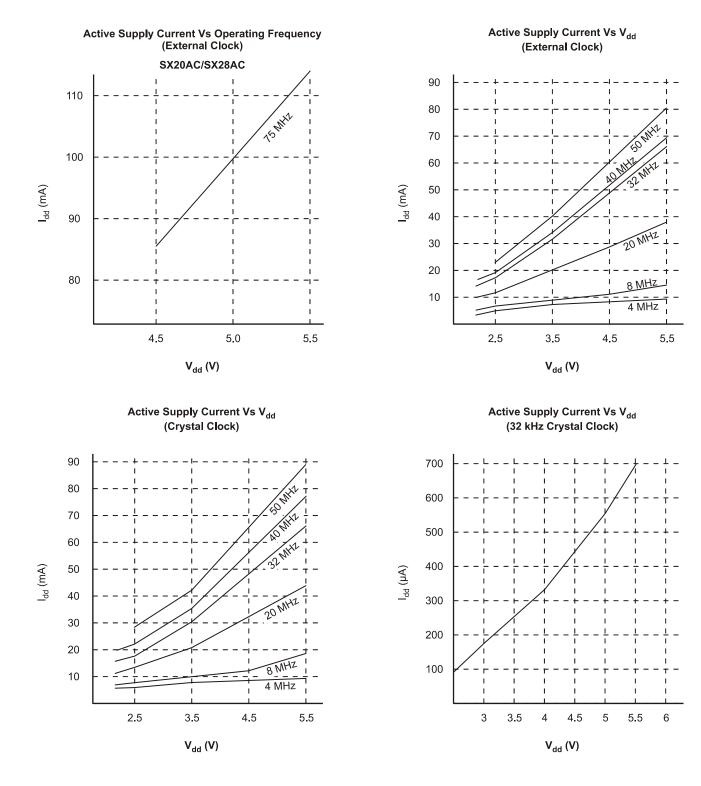

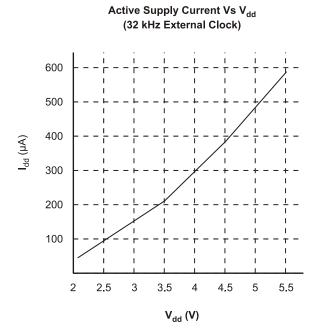

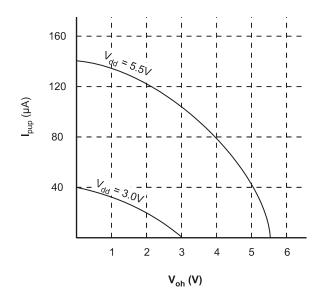

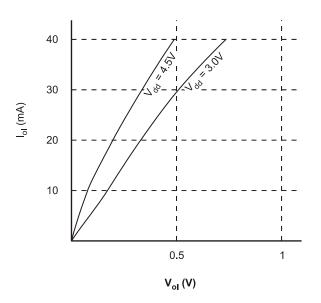

| 17.5.                | Typical Performance Characteristics (25°C)       | 43 |

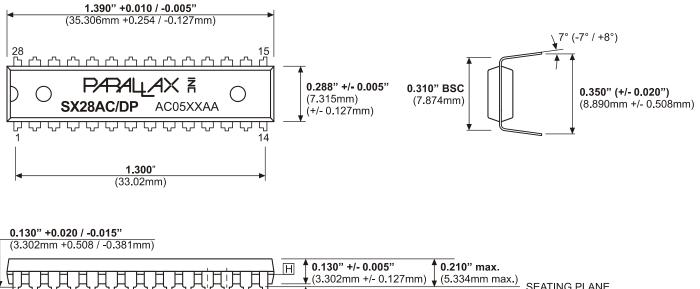

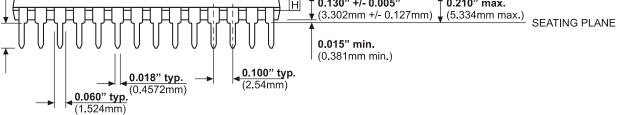

| 18.0                 | Package Dimensions                               | 46 |

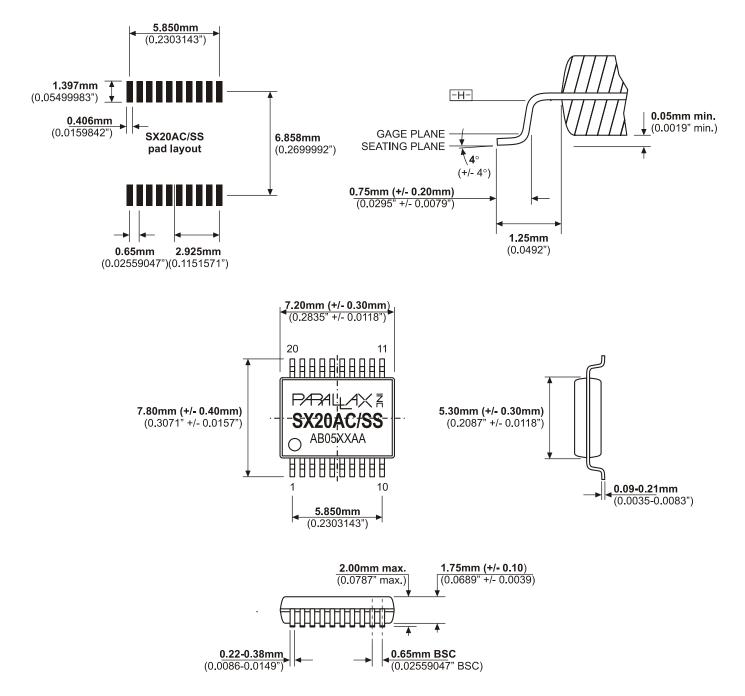

| 18.1.                | SX20AC/SS                                        | 46 |

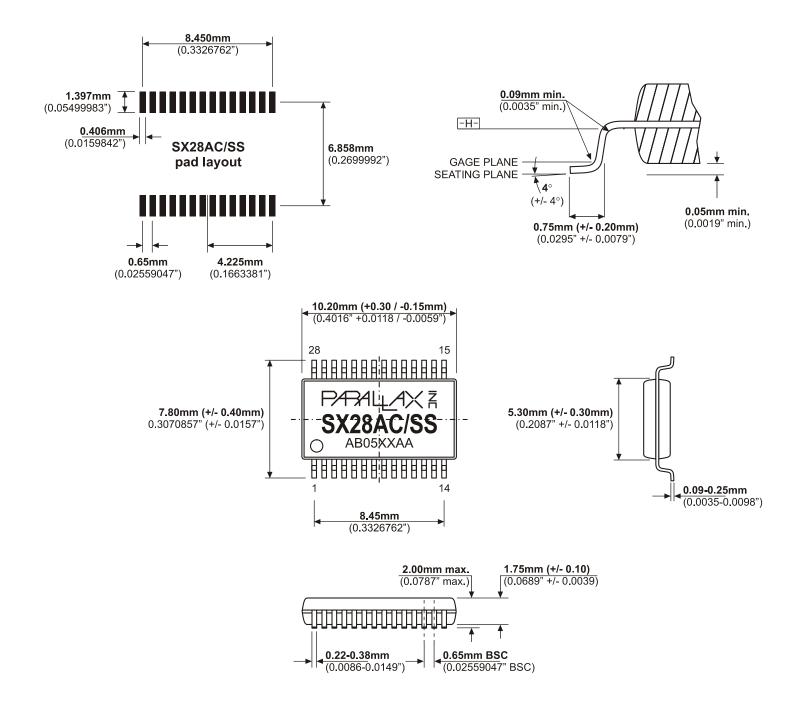

| 18.2.                | SX28AC/SS                                        |    |

| 18.3.                | SX28AC/DP                                        | 48 |

| 19.0                 | Manufacturing Information                        | 49 |

| 19.1.                | Reflow Peak Temperature                          |    |

| 19.2.                | MSL3 Compliance                                  |    |

| 19.3.                | Green/RoHS Compliance                            |    |

| 19.4.                | Stress Testing Data Summary                      | 49 |

### 1.2. Key Features

#### **75 MIPS Performance**

- SX20AC/SX28AC: DC 75 MHz

- SX20AC/SX28AC: as low as 13.3 ns instruction cycle, 39.9 ns internal interrupt response

- 1 instruction per clock for most instructions (skips require 2 clocks, branches require 3 clocks, IREAD requires 4)

#### EE/FLASH Program Memory and SRAM Data Memory

- Access time of < 13.3 ns provides single cycle access

- EE/Flash rated for > 10,000 rewrite cycles

- 2048 Words EE/Flash program memory

- 136x8 bits SRAM data memory

#### **CPU Features**

- Compact, RISC-like instruction set

- All non-branch instructions are single cycle

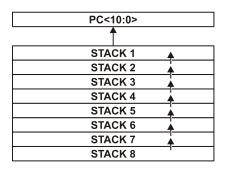

- Eight-level push/pop hardware stack for subroutine operation

- Fast table lookup capability through run-time readable code (IREAD instruction)

- Totally predictable program execution rate for precise real-time applications

#### **Fast and Deterministic Interrupt**

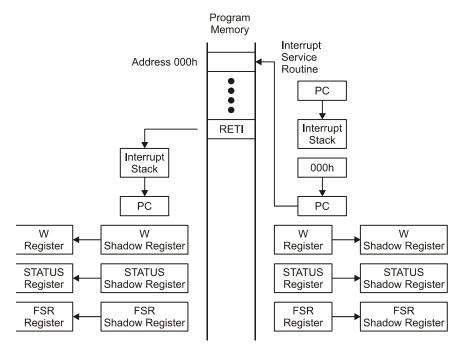

- Jitter-free 3-cycle internal interrupt response

- Hardware context save/restore of key resources such as PC, W, STATUS, and FSR within the 3-cycle interrupt response time

- External wakeup/interrupt capability on Port B (8 pins)

#### Flexible I/O

- All port pins individually programmable as I/O

- Inputs are TTL or CMOS level selectable

- All pins have selectable internal pull-ups

- Selectable Schmitt Trigger inputs on Ports B and C

- All output pins capable of sourcing/sinking 30 mA

- Port A outputs have symmetrical drive

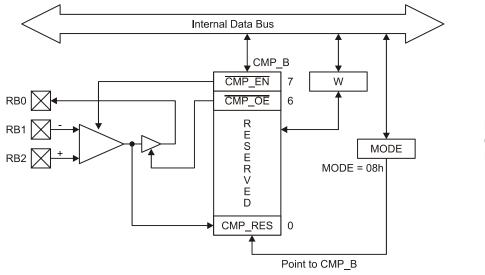

- Analog comparator support on Port B (RB0 OUT, RB1 IN-, RB2 IN+)

- Selectable I/O operation synchronous to the oscillator clock

#### **Hardware Peripheral Features**

- One 8-bit Real Time Clock/Counter (RTCC) with programmable 8-bit prescaler

- Watchdog Timer (shares the RTCC prescaler)

- Analog comparator

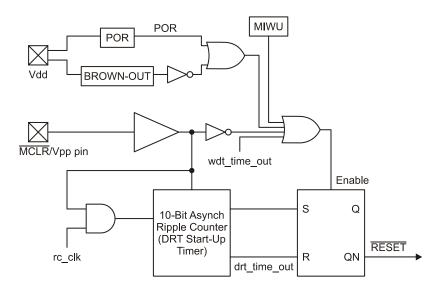

- Brown-out detector

- Multi-Input Wakeup logic on 8 pins

- Internal RC oscillator with configurable rate from 31.25 kHz to 4 MHz

- Power-On-Reset

#### Packages

• 20-pin SSOP, 28-pin DIP/SSOP

#### Programming and Debugging Support

- On-chip in-system serial programming support via the oscillator pins

- On-chip in-system debugging support logic

- Real-time emulation, full program debug, and integrated development environment offered by the Parallax SX-Key<sup>®</sup> programming device

- The language options available: Parallax Assembly; Parallax SX/B (BASIC); and CCS SX/C (C)

#### Software Support

- Native assembly instruction set

- Expanded assembly instruction set available in the SASM assembler of the Parallax SX-Key IDE

- Parallax SX/B compiler (BASIC)

- Several "C" compliers available from third-party vendors

The SX devices use a modified Harvard architecture. This architecture uses two separate memories with separate address buses, one for the program and one for data, while allowing transfer of data from program memory to SRAM. This ability allows accessing data tables from program memory. The advantage of this architecture is that instruction fetch and memory transfers can be overlapped with a multi-stage pipeline, which means the next instruction can be fetched from program memory while the current instruction is being executed using data from the data memory.

This RISC-like architecture and memory design is based on technology that makes it very fast, deterministic, jitter free, and totally reprogrammable.

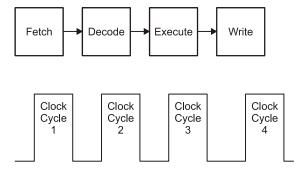

The SX family implements a four-stage pipeline (fetch, decode, execute, and write back), which results in execution of one instruction per clock cycle. For example, at the maximum operating frequency of 75 MHz, instructions are executed at the rate of one per 13.3 ns clock cycle.

# 1.4. Programming Benefits in Assembly and High-Level Languages

The SX's high speed enables a "software system on a chip" approach. Programming in assembly language provides a particularly high-level of access to the interrupt service routine, the stack and registers to take the highest advantage of the SX's deterministic timing. The primary technical resources for programming the SX in assembly language include the following:

- The SX20AC/SX28AC datasheet

- *SX-Key Development System User's Manual* by Parallax, Inc.

- *Programming the SX Microcontroller A Complete Guide* by Guenther Daubach

Customers with a high-level programming language background may prefer the use of a C or BASIC compiler.

### 1.4.1. Parallax SX/B Basic Compiler

Parallax's SX/B is a free BASIC language compiler for the SX microcontroller (SX20, SX28, and SX48). The compiler speeds the programming of the SX microcontrollers by providing a simple, yet robust highlevel language familiar to Parallax customers. SX/B includes the following features and commands:

- ASM directive to support in-line assembly language

- Program structure commands including BRANCH, DO..LOOP, GOTO, GOSUB, IF..THEN..ELSE

- Numeric formatters

Downloaded from Elcodis.com electronic components distributor

- WORD variable support

- Frequency generation with FREQOUT

www.parallax.com

- Synchronous serial communication for I<sup>2</sup>C, 1-Wire, SPI

- Asynchronous serial communication with SERIN and SEROUT

- Table data storage and retrieval with LOOKUP, LOOKDOWN

- I/O pin control with HIGH, LOW, TOGGLE, REVERSE

- Timing and delay with PAUSE, SLEEP

- PULSIN and PULSOUT

- Resistor/capacitor A/D with RCTIME

- RANDOM for pseudo-random number generation

- Non-volatile EEPROM memory access with DATA, READ

- Low-current SLEEP command

The complete SX/B command reference and examples are installed with the SX-Key IDE.

# 1.5. Programming and Debugging Support

The SX devices are supported by Parallax's programming and debugging tools. The Parallax SX-Blitz is a programming tool. The SX-Key supports programming and source-level debugging. On-chip in-system debug capabilities allow the Parallax tool to be an all-in-one integrated development environment with editor, macro assembler, debugger, and programmer. Unobtrusive insystem programming is provided through the OSC pins. Visit www.parallax.com for the SX-Key development tools, the IDE and support forum information.

The in-system programming specification is available to other 3rd party tool vendors upon request.

## 1.6. Applications

The SX may be used as a solution for process controllers, electronic appliances/tools, security/monitoring systems, sound and signal generation, GPS interface, robotic control, motor control, sensor interfacing and personal communication devices. Applications such as interactive toys, magnetic-stripe readers, infrared decoders, and other timing-sensitive projects are also common with the SX. Examples of customer applications may be seen on the Parallax web site.

## 1.7. Support

Parallax and our distributors provide all support for the SX microcontroller. Support is available free of charge via phone (888) 512-1024 in the U.S. Also be sure to participate in the SX discussion forum at http://forums.parallax.com/forums/. The on-line SX support community is actively involved in customer support 24 hours a day.

## 1.8. Part Numbering

|              | Table 1-1: Part Numbering |     |                     |                |                      |                                          |                                          |  |  |

|--------------|---------------------------|-----|---------------------|----------------|----------------------|------------------------------------------|------------------------------------------|--|--|

| Device Part# | Pins                      | I/O | EE/Flash<br>(Words) | RAM<br>(Bytes) | Voltage<br>Range (V) | Operating Temp @<br>3.0 – 5.5 V, 50 MHz* | Operating Temp @<br>4.5 – 5.5 V, 75 MHz* |  |  |

| SX20AC/SS    | 20                        | 12  | 2K                  | 137            | 3.0 - 5.5            | -40 °C to +85 °C                         | 0 °C to +70 °C                           |  |  |

| SX20AC/SS-G  | 20                        | 12  | 21                  | 157            | 5.0 - 5.5            | -40 0 10 700 0                           | 0 0 10 170 0                             |  |  |

| SX28AC/DP    | - 28                      | 20  | 2K                  | 136            | 3.0 - 5.5            | -40 °C to +85 °C                         | 0 °C to +70 °C                           |  |  |

| SX28AC/DP-G  | 20                        | 20  | 21                  | 130            | 3.0 - 5.5            | -40 C 10 +65 C                           | 0 0 10 70 0                              |  |  |

| SX28AC/SS    | 28                        | 20  | 2K                  | 136            | 3.0 - 5.5            | -40 °C to +85 °C                         | 0 °C to +70 °C                           |  |  |

| SX28AC/SS-G  | 20                        | 20  | 21                  | 130            | 3.0 - 5.5            | -40 0 10 705 0                           | 0000700                                  |  |  |

\* Ratings are preliminary

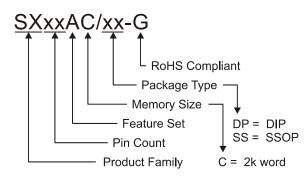

Figure 1-2

Part Number Reference Guide

28 MCLR

SX 28-PIN

1

Г

RTCC

#### 2.0 **CONNECTION DIAGRAMS**

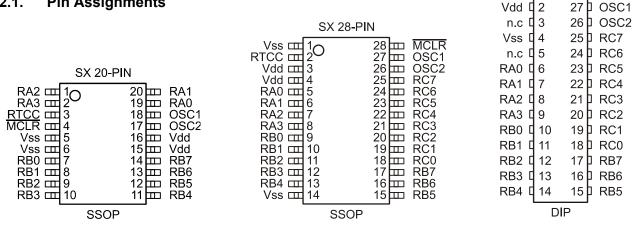

#### 2.1. **Pin Assignments**

Figure 2-1: Pin Assignments

#### 2.2. **Pin Descriptions**

|                 | Table 2-1: Pin Descriptions |              |                                                                                                                                    |  |  |  |  |

|-----------------|-----------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Name            | Pin Type                    | Input Levels | Description                                                                                                                        |  |  |  |  |

| RA0             | I/O                         | TTL/CMOS     | Bidirectional I/O Pin; symmetrical source / sink capability                                                                        |  |  |  |  |

| RA1             | I/O                         | TTL/CMOS     | Bidirectional I/O Pin; symmetrical source / sink capability                                                                        |  |  |  |  |

| RA2             | I/O                         | TTL/CMOS     | Bidirectional I/O Pin; symmetrical source / sink capability                                                                        |  |  |  |  |

| RA3             | I/O                         | TTL/CMOS     | Bidirectional I/O Pin; symmetrical source / sink capability                                                                        |  |  |  |  |

| RB0             | I/O                         | TTL/CMOS/ST  | Bidirectional I/O Pin; comparator output; MIWU/Interrupt input                                                                     |  |  |  |  |

| RB1             | I/O                         | TTL/CMOS/ST  | Bidirectional I/O Pin; comparator negative input; MIWU/Interrupt input                                                             |  |  |  |  |

| RB2             | I/O                         | TTL/CMOS/ST  | Bidirectional I/O Pin; comparator positive input; MIWU/Interrupt input                                                             |  |  |  |  |

| RB3             | I/O                         | TTL/CMOS/ST  | Bidirectional I/O Pin; MIWU/Interrupt input                                                                                        |  |  |  |  |

| RB4             | I/O                         | TTL/CMOS/ST  | Bidirectional I/O Pin; MIWU/Interrupt input                                                                                        |  |  |  |  |

| RB5             | I/O                         | TTL/CMOS/ST  | Bidirectional I/O Pin; MIWU/Interrupt input                                                                                        |  |  |  |  |

| RB6             | I/O                         | TTL/CMOS/ST  | Bidirectional I/O Pin; MIWU/Interrupt input                                                                                        |  |  |  |  |

| RB7             | I/O                         | TTL/CMOS/ST  | Bidirectional I/O Pin; MIWU/Interrupt input                                                                                        |  |  |  |  |

| RC0             | I/O                         | TTL/CMOS/ST  | Bidirectional I/O Pin                                                                                                              |  |  |  |  |

| RC1             | I/O                         | TTL/CMOS/ST  | Bidirectional I/O Pin                                                                                                              |  |  |  |  |

| RC2             | I/O                         | TTL/CMOS/ST  | Bidirectional I/O Pin                                                                                                              |  |  |  |  |

| RC3             | I/O                         | TTL/CMOS/ST  | Bidirectional I/O Pin                                                                                                              |  |  |  |  |

| RC4             | I/O                         | TTL/CMOS/ST  | Bidirectional I/O Pin                                                                                                              |  |  |  |  |

| RC5             | I/O                         | TTL/CMOS/ST  | Bidirectional I/O Pin                                                                                                              |  |  |  |  |

| RC6             | I/O                         | TTL/CMOS/ST  | Bidirectional I/O Pin                                                                                                              |  |  |  |  |

| RC7             | I/O                         | TTL/CMOS/ST  | Bidirectional I/O Pin                                                                                                              |  |  |  |  |

| RTCC            | 1                           | ST           | Input to Real-time Clock/counter                                                                                                   |  |  |  |  |

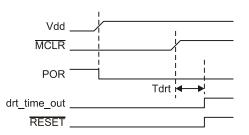

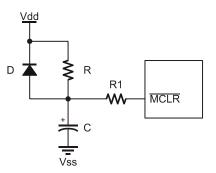

| MCLR            | I                           | ST           | Master Clear reset input – active low. When not controlled externally, this pin must be pulled high with a 10 k $\Omega$ resistor. |  |  |  |  |

| OSC1/In/Vpp     | 1                           | ST           | Crystal oscillator input; external clock source input                                                                              |  |  |  |  |

| OSC2/Out        | 0                           | CMOS         | Crystal oscillator output; in R/C mode, internally pulled to $V_{dd}$ through weak pull-up                                         |  |  |  |  |

| V <sub>dd</sub> | Р                           | -            | Positive supply pin                                                                                                                |  |  |  |  |

| V <sub>ss</sub> | Р                           | -            | Ground pin                                                                                                                         |  |  |  |  |

Note: I = input, O = output, I/O = Input/Output, P = Power, TTL = TTL input, CMOS = CMOS input, ST = Schmitt Trigger input, MIWU = Multi-Input Wakeup input.

© Parallax Inc.

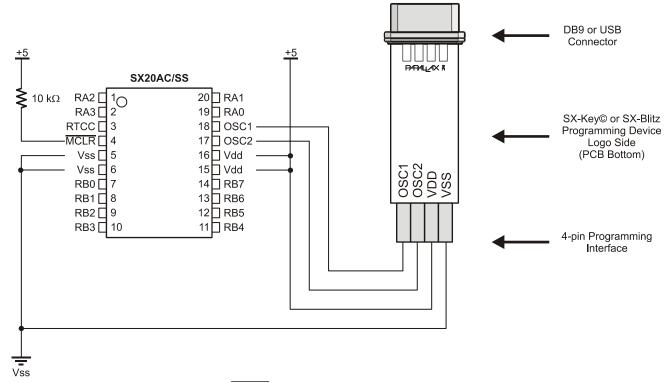

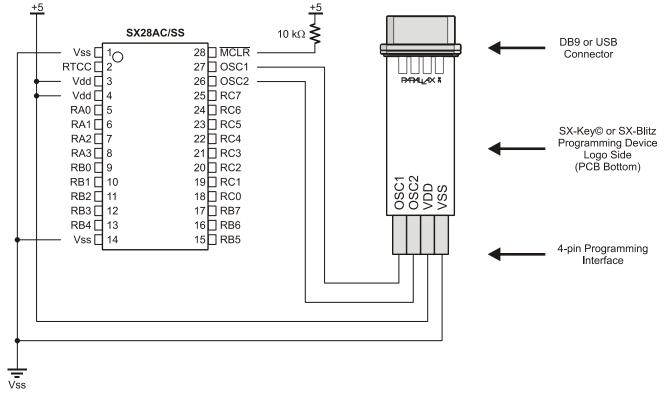

#### 2.3. Typical Connection Diagrams

Note: The 10 k $\Omega$  resistor connected to the MCLR pin is not needed when controlled externally.

Note: The 10 k $\Omega$  resistor connected to the MCLR pin is not needed when controlled externally.

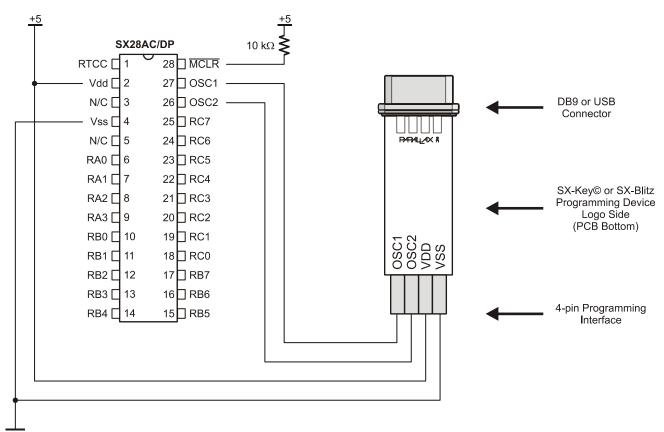

## **Typical Connection Diagrams (continued)**

Note: The 10 k $\Omega$  resistor connected to the  $\overline{MCLR}$  pin is not needed when controlled externally.

Vss

# 3.0 PORT DESCRIPTIONS

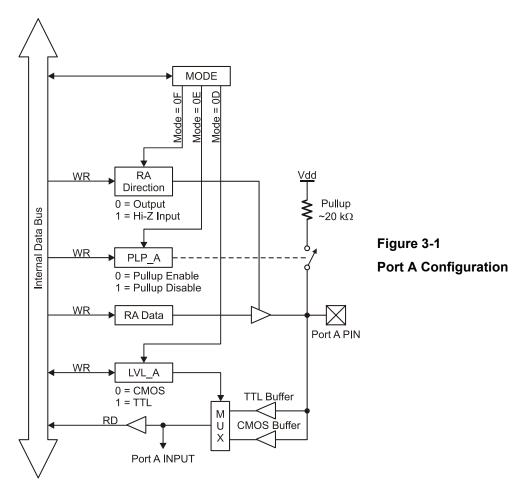

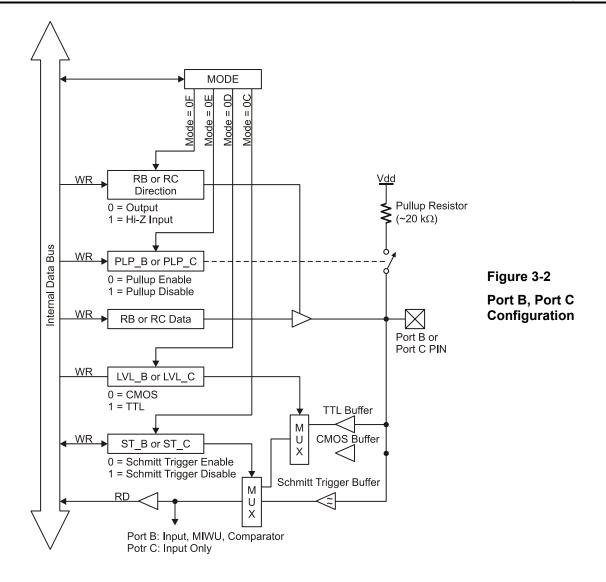

All models contain a 4-bit I/O port (Port A), an 8-bit I/O port (Port B). The SX28 also contains a second 8-bit I/O port (Port C). Port A provides symmetrical drive capability. Each port has three associated 8-bit registers (Direction, Data, TTL/CMOS Select, and Pull-Up Enable) to configure each port pin as Hi-Z input or output, to select TTL or CMOS voltage levels, and to enable/disable the weak pull-up resistor. The upper four bits of the

registers associated with Port A are not used. The least significant bit of the registers corresponds to the least significant port pin. To access these registers, an appropriate value must be written into the MODE register. Upon power-up, all bits in these registers are initialized to "1". The associated registers allow for each port bit to be individually configured under software controls as shown below.

| Table 3-1: Port Configuration                                                                                                                                                |            |      |     |        |         |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|-----|--------|---------|--|

| Data Direction Registers:         TTL/CMOS Selected Registers:         Pullup Enable Registers:           RA, RB, RC         LVL A, LVL B, LVL C         PLP A, PLP B, PLP C |            |      |     |        |         |  |

| 0                                                                                                                                                                            | 1          | 0    | 1   | 0      | 1       |  |

| Output                                                                                                                                                                       | Hi-Z Input | CMOS | TTL | Enable | Disable |  |

### 3.1. Reading and Writing the Ports

The three ports are memory-mapped into the data memory address space. To the CPU, the three ports are available as the RA, RB, and RC file registers at data memory addresses 05h, 06h, and 07h, respectively. Writing to a port data register sets the voltage levels of the corresponding port pins that have been configured to operate as outputs to a corresponding level, 1 = 5 V, 0 = 0 V. Reading from a register reads the voltage levels of all port pins.

© Parallax Inc.

Page 9 of 51

For example, suppose all four Port A pins are configured as outputs and you wish to set RA0 and RA1 high, and RA2 and RA3 low:

| mov | W,#\$03 | ;load W with the value 03h |

|-----|---------|----------------------------|

|     |         | ;(bits 0 and 1 high)       |

| mov | \$05,W  | ;write 03h to Port A data  |

|     |         | ;register                  |

The second "mov" instruction in this example writes the Port A data register (RA), which controls the output levels of the four Port A pins, RA0 through RA3. Because Port A has only four I/O pins, only the four least significant bits of this register are used. The four high-order register bits are "don't care" bits. Port B and Port C are both eight bits wide, so the full widths of the RB and RC registers are used. When a write is performed to a bit position for a port that has been configured as an input, a write to the port data register is still performed, but it has no immediate effect on the pin. If later that pin is configured to operate as an output, it will reflect the value that has been written to the data register.

When a read is performed from a bit position for a port, the operation is actually reading the voltage level on the pin itself, not necessarily the bit value stored in the port data register. This is true whether the pin is configured to operate as an input or an output. Therefore, with the pin configured to operate as an input, the data register contents have no effect on the value that you read. With the pin configured to operate as an output, what is read generally matches what has been written to the register.

#### 3.1.1. Read-Modify-Write Considerations

Caution must be exercised when performing two successive read-modify-write instructions (SETB or CLRB operations) on an I/O port pin. Input data used for an instruction must be valid during the time the instruction is executed, and the output result from an instruction is valid only after that instruction completes its operation. Unexpected results from successive readmodify-write operations on I/O pins can occur when the device is running at high speeds. Although the device has an internal write-back section to prevent such conditions, it is still recommended that the user program include a NOP instruction as a buffer between successive readmodify-write instructions performed on I/O pins of the same port.

Also note that reading an I/O port is actually reading the pins, not the output data latches. That is, if the pin output driver is enabled and driven high while the pin is held low externally, the port pin will read low.

#### 3.2. Port Configuration

Each port pin offers the following configuration options:

- data direction

- input voltage levels (TTL or CMOS)

- pullup type (pullup resistor enable or disable)

- Schmitt trigger input (for Port B and Port C only)

Port B offers the additional option to use the port pins for the Multi-Input Wakeup/Interrupt function and/or the analog comparator function.

Port configuration is performed by writing to a set of control registers associated with the port. A specialpurpose instruction is used to write these control registers:

- mov !RA,W (move W to Port A control register)

- mov !RB,W (move W to Port B control register)

- mov !RC,W (move W to Port C control register)

Each one of these instructions writes a port control register for Port A, Port B, or Port C. There are multiple control registers for each port. To specify which one you want to access, you use another register called the MODE register.

#### 3.2.1. MODE Register

The MODE register controls access to the port configuration registers. Because the MODE register is not memory-mapped, it is accessed by the following special purpose instructions:

- mov M, #lit (move literal to MODE register)

- mov M,W (move W to MODE register)

- mov W,M (move MODE register to W)

The value contained in the MODE register determines which port control register is accessed by the "mov !rx,W" instruction as indicated in Table 2-1. MODE register values not listed in the table are reserved for future expansion and should not be used. Therefore, the MODE register should always contain a value from 08h to 0Fh. Upon reset, the MODE register is initialized to 0Fh, which enables access to the port direction registers.

After a value is written to the MODE register, that setting remains in effect until it is changed by writing to the MODE register again. For example, you can write the value 0Eh to the MODE register just once, and then write to each of the three pullup configuration registers using the three "mov !rx,W" instructions.

| Table 3-2: MODE Register and<br>Port Control Register Access |                                           |              |              |  |  |  |  |

|--------------------------------------------------------------|-------------------------------------------|--------------|--------------|--|--|--|--|

| MODE Reg.                                                    | MODE Reg. Mov !RA,W Mov !RB, W Mov !Rc, W |              |              |  |  |  |  |

| 08h                                                          | not used                                  | CMP_B        | not used     |  |  |  |  |

| 09h                                                          | not used                                  | WKPND_B      | not used     |  |  |  |  |

| 0Ah                                                          | not used                                  | WKED_b       | not used     |  |  |  |  |

| 0Bh                                                          | not used                                  | WKEN_B       | not used     |  |  |  |  |

| 0Ch                                                          | not used                                  | ST_B         | ST_C         |  |  |  |  |

| 0Dh                                                          | LVL_A                                     | LVL_B        | LVL_C        |  |  |  |  |

| 0Eh                                                          | PLP_A                                     | PLP_B        | PLP_C        |  |  |  |  |

| 0Fh                                                          | RA Direction                              | RB Direction | RC Direction |  |  |  |  |

The following code example shows how to program the pullup control registers.

| mov M,#\$0E | ;MODE=0Eh to access port pullup<br>;registers |

|-------------|-----------------------------------------------|

| mov W,#\$03 | ;W = 0000 0011                                |

| mov !RA,W   | ;disable pullups for RA0 and RA1              |

| mov W,#\$FF | ;W = 1111 1111                                |

| mov !RB,W   | ;disable all pullups for RB0-RB7              |

| mov W,#\$00 | ;W = 0000 0000                                |

| mov !RC,W   | ;enable all pullups for RC0-RC7               |

First the MODE register is loaded with 0Eh to select access to the pullup control registers (PLP\_A, PLP\_B, and PLP\_C). Then the "mov !rx,W" instructions are used to specify which port pins are to be connected to the internal pullup resistors. Setting a bit to 1 disconnects the corresponding pullup resistor, and clearing a bit to 0 connects the corresponding pullup resistor.

#### 3.2.2. Port Configuration Registers

The port configuration registers that you control with the "mov !rx,W" instruction operate as described below.

#### RA, RB, and RC Data Direction Registers (MODE=0Fh)

Each register bit sets the data direction for one port pin. Set the bit to 1 to make the pin operate as a highimpedance input. Clear the bit to 0 to make the pin operate as an output.

# PLP\_A, PLP\_B, and PLP\_C: Pullup Enable Registers (MODE=0Eh)

Each register bit determines whether an internal pullup resistor is connected to the pin. Set the bit to 1 to disconnect the pullup resistor or clear the bit to 0 to connect the pullup resistor.

# LVL\_A, LVL\_B, and LVL\_C: Input Level Registers (MODE=0Dh)

Each register bit determines the voltage levels sensed on the input port, either TTL or CMOS, when the Schmitt trigger option is disabled. Program each bit according to the type of device that is driving the port input pin. Set the bit to 1 for TTL or clear the bit to 0 for CMOS.

# ST\_B and ST\_C: Schmitt Trigger Enable Registers (MODE=0Ch)

Each register bit determines whether the port input pin operates with a Schmitt trigger. Set the bit to 1 to disable Schmitt trigger operation and sense either TTL or CMOS voltage levels; or clear the bit to 0 to enable Schmitt trigger operation.

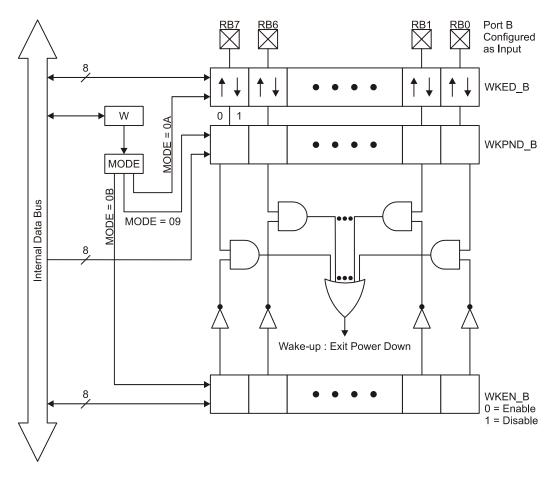

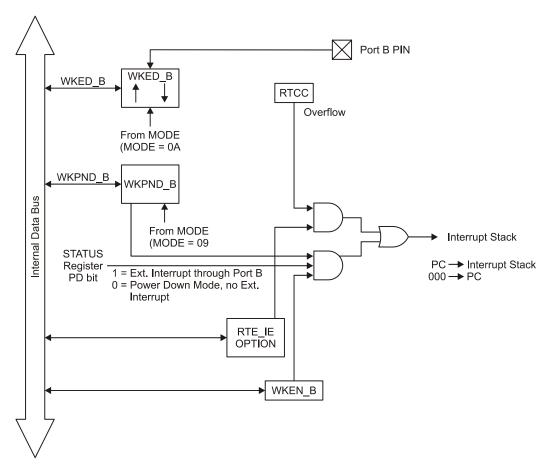

#### WKEN\_B: Wakeup Enable Register (MODE=0Bh)

Each register bit enables or disables the Multi-Input Wakeup/Interrupt (MIWU) function for the corresponding Port B input pin. Clear the bit to 0 to enable MIWU operation or set the bit to 1 to disable MIWU operation. For more information on using the Multi-Input Wakeup/Interrupt function, see Section 7.1.

#### WKED\_B: Wakeup Edge Register (MODE=0Ah)

Each register bit selects the edge sensitivity of the Port B input pin for MIWU operation. Clear the bit to 0 to sense rising (low-to-high) edges. Set the bit to 1 to sense falling (high-to-low) edges.

# WKPND\_B: Wakeup Pending Bit Register (MODE=09h)

When you access the WKPND\_B register using "mov !rx,W", the CPU does an exchange between the contents of W and WKPND\_B. This feature lets you read the WKPND\_B register contents while clearing the Wakeup Pending bits simultaneously. Each bit indicates the status of the corresponding MIWU pin. A bit set to 1 indicates that a valid edge has occurred on the corresponding MIWU pin, triggering a wakeup or interrupt. A bit set to 0 indicates that no valid edge has occurred on the MIWU pin.

#### CMP\_B: Comparator Register (MODE=08h)

When you access the CMP\_B register using MOV !RB,W, the CPU does an exchange between the contents of W and CMP\_B. This feature lets you read the CMP\_B register contents. Clear bit 7 to enable operation of the comparator. Clear bit 6 to place the comparator result on the RB0 pin. Bit 0 is a result bit that is set to 1 when the voltage on RB2 is greater than RB1, or cleared to 0 otherwise. (For more information using the comparator, see Section 11.0.)

#### 3.2.3. Port Configuration Upon Reset

Upon reset, all the port control registers are initialized to FFh. Thus, each pin is configured to operate as a high impedance input that senses TTL voltage levels, with no internal pullup resistor connected. The MODE register is initialized to 0Fh, which allows immediate access to the data direction registers using the "mov !rx,W" instruction.

# 4.0 SPECIAL-FUNCTION REGISTERS

The CPU uses a set of special-function registers to control the operation of the device.

The CPU registers include an 8-bit working register (W), which serves as a pseudo accumulator. It holds the second operand of an instruction, receives the literal in immediate type instructions, and also can be program selected as the destination register.

A set of 31 file registers serves as the primary accumulator. One of these registers holds the first operand of an instruction and another can be program-selected as the destination register. The first eight file registers include the Real-Time Clock/Counter register (RTCC), the lower eight bits of the 11-bit Program Counter (PC), the 8-bit STATUS register, three port control registers for Port A, Port B, Port C, the 8-bit File Select Register (FSR), and INDF used for indirect addressing.

The five low-order bits of the FSR register select one of the 31 file registers in the indirect addressing mode. Calling for the file register located at address 00h (INDF) in any of the file-oriented instructions selects indirect addressing, which uses the FSR register. It should be noted that the file register at address 00h is not a physically implemented register. The CPU also contains an 8 level, 11-bit hardware push/pop stack for subroutine linkage.

| Table 4-1: Special-Function Register |        |                              |  |  |  |

|--------------------------------------|--------|------------------------------|--|--|--|

| Address                              | Name   | Function                     |  |  |  |

| 00h                                  | INDF   | Used for indirect addressing |  |  |  |

| 01h                                  | RTCC   | Real Time Clock/Counter      |  |  |  |

| 02h                                  | PC     | Program Counter (low byte)   |  |  |  |

| 03h                                  | STATUS | Holds status bits of ALU     |  |  |  |

| 04h                                  | FSR    | File Select Register         |  |  |  |

| 05h                                  | RA     | Port RA control register     |  |  |  |

| 06h                                  | RB     | Port RB control register     |  |  |  |

| 07h                                  | RC*    | Port RC control register     |  |  |  |

\*In the SX20 package, Port C is not used, and address 07h is available as a general-purpose RAM location.

### 4.1. PC Register (02h)

The PC register holds the lower eight bits of the program counter. It is accessible at run time to perform branch operations.

### 4.2. STATUS Register (03h)

The STATUS register holds the arithmetic status of the ALU, the page select bits, and the reset state. The STATUS register is accessible during run time, except that bits PD and TO are read-only. It is recommended that only SETB and CLRB instructions be used on this

register. Care should be exercised when writing to the STATUS register as the ALU status bits are updated upon completion of the write operation, possibly leaving the STATUS register with a result that is different than intended.

| PA2   | PA1 | PA0 | TO | PD | Z | DC | С     |

|-------|-----|-----|----|----|---|----|-------|

| Bit 7 |     |     |    |    |   |    | Bit 0 |

Bit 7-5: Page select bits PA2:PA0 000 = Page 0 (000h - 01FFh)001 = Page 1 (200h - 03FFh)010 = Page 2 (400h - 05FFh)011 = Page 3 (600h - 07FFh) **Bit 4:** Time Out bit, TO 1 = Set to 1 after power up and upon execution of CLRWDT or SLEEP instructions 0 = A watchdog time-out occurred Bit 3: Power Down bit, PD 1= Set to a 1 after power up and upon execution of the CLRWDT instruction 0 = Cleared to a '0' upon execution of SLEEP instruction Bit 2: Zero bit. Z 1 =Result of math operation is zero 0 =Result of math operation is non-zero Bit 1: Digit Carry bit, DC After Addition: 1 = A carry from bit 3 occurred 0 = No carry from bit 3 occurred After Subtraction: 1 = No borrow from bit 3 occurred0 = A borrow from bit 3 occurred Bit 0: Carry bit, C After Addition. 1 = A carry from bit 7 of the result occurred 0 = No carry from bit 7 of the result occurred After Subtraction: 1 = No borrow from bit 7 of the result occurred 0 = A borrow from bit 7 of the result occurred

Rotate (RR or RL) Instructions:

The carry bit is loaded with the low or high order bit, respectively. When CF bit is cleared, Carry bit works as input For ADD and SUB instructions.

#### 4.3. OPTION Register

| RTW   | RTW_IE | RTS | RTE_ES | PSA | PS2 | PS1 | PS0   |

|-------|--------|-----|--------|-----|-----|-----|-------|

| Bit 7 |        |     |        |     |     |     | Bit 0 |

When the OPTIONX bit in the FUSE word is cleared, bits 7 and 6 of the OPTION register function as described below.

When the OPTIONX bit is set, bits 7 and 6 of the OPTION register read as '1's.

#### **RTW** RTCC/W register selection:

0 =Register 01h addresses W

1 = Register 01h addresses RTCC

#### **RTE\_IE** RTCC edge interrupt enable:

- 0 = RTCC roll-over interrupt is enabled

- 1 = RTCC roll-over interrupt is disabled

- **RTS** RTCC increment select:

0= RTCC increments on internal instruction cycle

1 = RTCC increments upon transition on RTCC pin

#### **RTE\_ES** RTCC edge select:

0 = RTCC increments on low-to-high transitions

1 = RTCC increments on high-to-low transitions

**PSA** Prescaler Assignment:

0 = Prescaler is assigned to RTCC, with divide rate determined by PS0-PS2 bits

1 = Prescaler is assigned to WDT, and divide rate on RTCC is 1:1

**PS2-PS0**: Prescaler divider (see table below)

| Table 4-2: Prescaler Divider Ratios |                     |                               |  |  |  |

|-------------------------------------|---------------------|-------------------------------|--|--|--|

| PS2, PS1, PS0                       | RTCC Divide<br>Rate | Watchdog Timer<br>Divide Rate |  |  |  |

| 000                                 | 1:2                 | 1:1                           |  |  |  |

| 001                                 | 1:4                 | 1:2                           |  |  |  |

| 010                                 | 1:8                 | 1:4                           |  |  |  |

| 011                                 | 1:16                | 1:8                           |  |  |  |

| 100                                 | 1:32                | 1:16                          |  |  |  |

| 101                                 | 1:64                | 1:32                          |  |  |  |

| 110                                 | 1:128               | 1:64                          |  |  |  |

| 07h111                              | 1:256               | 1:128                         |  |  |  |

Upon reset, all bits in the OPTION register are set to 1.

# 5.0 DEVICE CONFIGURATION REGISTERS

The SX device has three registers (FUSE, FUSEX, DEVICE) that control functions such as operating the device in Turbo mode, extended (8-level deep) stack operation, and speed selection for the internal RC oscillator. These registers are not programmable "on the

fly" during normal device operation. Instead, the FUSE and FUSEX registers can only be accessed when the SX device is being programmed. The DEVICE register is a read-only, hard-wired register, programmed during the manufacturing process.

| 5.1. | FUSE Word | (Read/Program at FFFh ir | Nain Memory Map) |

|------|-----------|--------------------------|------------------|

|------|-----------|--------------------------|------------------|

| TURBO           | SYNC   | Reserved                                                                                                                                                                     | Reserved       | IRC         | DIV1/<br>IFBD | DIV0/<br>FOSC2         | Reserved      | CP        | WDTE     | FOSC1 | FOSC0 |

|-----------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------|---------------|------------------------|---------------|-----------|----------|-------|-------|

| Bit 11          |        |                                                                                                                                                                              |                |             |               |                        |               |           |          |       | Bit 0 |

| TURBO           | Т      | urbo mode en                                                                                                                                                                 | able:          |             |               |                        |               |           |          |       |       |

|                 | 0      | 0 = turbo (instruction clock = osc/1)                                                                                                                                        |                |             |               |                        |               |           |          |       |       |

|                 | 1      | = instr clock                                                                                                                                                                | = osc/4        |             |               |                        |               |           |          |       |       |

| SYNC            | tł     | Synchronous input enable (for turbo mode): This bit synchronizes the signal presented at the input pin to the internal clock through two internal flip-flops.<br>0 = enabled |                |             |               |                        |               |           |          |       |       |

|                 | 1      | = disabled                                                                                                                                                                   |                |             |               |                        |               |           |          |       |       |

| IRC             | Iı     | nternal RC os                                                                                                                                                                | cillator enab  | le:         |               |                        |               |           |          |       |       |

|                 | 0      | = enabled - C                                                                                                                                                                | OSC1 pulled    | low by w    | eak pullup    | o, OSC2 pt             | ulled high b  | y weak pu | ıllup    |       |       |

|                 |        | = disabled - (                                                                                                                                                               |                |             | ve accordi    | ing to FOS             | C2: FOSC      | )         |          |       |       |

| DIV1: DIV       |        | nternal RC os                                                                                                                                                                | cillator divid | ler:        |               |                        |               |           |          |       |       |

|                 |        | 0b = 4 MHz                                                                                                                                                                   |                |             |               |                        |               |           |          |       |       |

|                 |        | 1b = 1  MHz                                                                                                                                                                  |                |             |               |                        |               |           |          |       |       |

|                 |        | 0 = 128  KHz                                                                                                                                                                 |                |             |               |                        |               |           |          |       |       |

|                 |        | 1b = 32 KHz                                                                                                                                                                  |                |             |               |                        |               |           |          |       |       |

| IFBD            |        | nternal crystal                                                                                                                                                              | /resonator o   | scillator f | eedback re    | esistor (1 N           | ΛQ:           |           |          |       |       |

|                 |        | = disabled                                                                                                                                                                   | 1 .            | r 11 (      | . 10          | 11 1                   | · 1)          |           |          |       |       |

|                 |        | nternal feedba<br>= enabled                                                                                                                                                  |                |             |               | -                      | ,             | (-1)      |          |       |       |

| $\overline{CP}$ |        |                                                                                                                                                                              |                | leeuback I  | esistor ena   | abled (vall            | d when IRC    | . – 1)    |          |       |       |

| CP              |        | ode protect er                                                                                                                                                               |                | and ID ma   | morias        | ad book og             | corblad dat   |           |          |       |       |

|                 |        | = enabled (F)<br>= disabled (F)                                                                                                                                              |                |             |               |                        | -             | a)        |          |       |       |

| WDTF W          |        | timer enable:                                                                                                                                                                |                |             |               |                        | normany)      |           |          |       |       |

| WDIE (          | -      | = disabled                                                                                                                                                                   |                |             |               |                        |               |           |          |       |       |

|                 |        | = enabled                                                                                                                                                                    |                |             |               |                        |               |           |          |       |       |

| FOSC2: F        | OSC0 E | xternal oscilla                                                                                                                                                              | ator configu   | ration (val | id when I     | $\overline{RC} = 1$ ): |               |           |          |       |       |

|                 |        | 00b = LP1 - 1c                                                                                                                                                               |                |             |               |                        |               |           |          |       |       |

|                 | 0      | 01b = LP2 - lo                                                                                                                                                               | ow power ci    | ystal/reso  | nator (32     | KHz to 1 M             | MHz)          |           |          |       |       |

|                 | 0      | 10b = XT1 - r                                                                                                                                                                | normal cryst   | al/resonat  | or (32 kHz    | z to 10 MF             | łz)           |           |          |       |       |

|                 | 0      | 11b = XT2 - r                                                                                                                                                                | normal cryst   | al/resonat  | or (1MHz      | to 24 MHz              | z)            |           |          |       |       |

|                 | 1      | 00b = HS1 - h                                                                                                                                                                | nigh speed c   | rystal/resc | onator/exte   | rnal crysta            | al oscillator | (1MHz to  | 50 MHz)  |       |       |

|                 | 1      | 01b = HS2 - h                                                                                                                                                                | nigh speed c   | rystal/resc | onator/exte   | rnal crysta            | al oscillator | (1 MHz t  | o 50 MHz | )     |       |

|                 |        | 10b = HS3 - h                                                                                                                                                                |                |             |               |                        |               |           |          | )     |       |

|                 | 1      | 11b = RC net                                                                                                                                                                 | work - OSC     | 2 is pulled | l high with   | n a weak pi            | ullup (no C   | LKOUT o   | utput)   |       |       |

|                 | N      | Note: The frequencies are target values.                                                                                                                                     |                |             |               |                        |               |           |          |       |       |

| 5.2. FU               | ISEX V    | vord (Rea                                                                                                                                                                                                                                                                                                                                                                                           | d/Progran                     | n via Prog                    | ramm      | ing Cor   | nmand)    |                                                 |               |          | 1       |

|-----------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------|-----------|-----------|-----------|-------------------------------------------------|---------------|----------|---------|

| IRCTRIM2              | PINS      | IRCTRIM1                                                                                                                                                                                                                                                                                                                                                                                            | IRCTRIM0                      | OPTIONX/<br>STACKX            | CF        | BOR1      | BOR0      | BORTR1                                          | BORTR0        | BP1      | BP0     |

| Bit 11                |           |                                                                                                                                                                                                                                                                                                                                                                                                     |                               |                               |           |           |           |                                                 |               |          | Bit 0   |

| IRCTRIM2:<br>IRCTRIM0 | or<br>ur  | perate within                                                                                                                                                                                                                                                                                                                                                                                       | the target f<br>e device reli | requency rar<br>es on the pro | nge 4 M   | IHz plus  | or minus  | on of the inter<br>8%. Parts an<br>the trimming | re shipped fr |          |         |

|                       | 11        | 1b = maxim                                                                                                                                                                                                                                                                                                                                                                                          | um frequenc                   | у                             |           |           |           |                                                 |               |          |         |

|                       | ea        | ch step abou                                                                                                                                                                                                                                                                                                                                                                                        | t 3%                          |                               |           |           |           |                                                 |               |          |         |

| PINS                  |           | elects the nur                                                                                                                                                                                                                                                                                                                                                                                      | -                             |                               |           |           |           |                                                 |               |          |         |

|                       |           | = 18/20 pins                                                                                                                                                                                                                                                                                                                                                                                        |                               |                               |           |           |           |                                                 |               |          |         |

|                       |           | = 28 pins                                                                                                                                                                                                                                                                                                                                                                                           |                               |                               |           |           |           |                                                 |               |          |         |

| OPTIONX/<br>STACKX    | in<br>lii | OPTION Register Extension and Stack Extension. Set to 1 to disable the programmability of bit 6 and bit 7 in the OPTION register, the RTW and RTE_IE bits (in other words, to force these two bits to 1) and to limit the program stack size to two locations. Clear to 0 to enable programming of the RTW and RTE_IE bits in the OPTION register, and to extend the stack size to eight locations. |                               |                               |           |           |           |                                                 |               |          |         |

| $\overline{CF}$       | А         | ctive low - m                                                                                                                                                                                                                                                                                                                                                                                       | akes carry b                  | it input to AI                | DD and    | SUB inst  | ructions. |                                                 |               |          |         |

| BOR1: BOF             | RO B      |                                                                                                                                                                                                                                                                                                                                                                                                     | set: These bi                 | 1                             |           |           |           | function and                                    | set the brow  | n-out th | reshold |

|                       | 00        | b = 4.2 V                                                                                                                                                                                                                                                                                                                                                                                           |                               |                               |           |           |           |                                                 |               |          |         |

|                       |           | b = 2.6 V                                                                                                                                                                                                                                                                                                                                                                                           |                               |                               |           |           |           |                                                 |               |          |         |

|                       |           | b = 2.2 V                                                                                                                                                                                                                                                                                                                                                                                           |                               |                               |           |           |           |                                                 |               |          |         |

|                       |           | b = Brown-C                                                                                                                                                                                                                                                                                                                                                                                         |                               |                               |           |           |           |                                                 |               |          |         |

| BORTR1:               |           |                                                                                                                                                                                                                                                                                                                                                                                                     |                               | are shipped of                | out of fa | ctory unt | rimmed).  |                                                 |               |          |         |

| BORTR0                |           | b = minimur                                                                                                                                                                                                                                                                                                                                                                                         | n threshold                   | voltage                       |           |           |           |                                                 |               |          |         |

|                       |           | b = LOW                                                                                                                                                                                                                                                                                                                                                                                             |                               |                               |           |           |           |                                                 |               |          |         |

|                       |           | b = HIGH                                                                                                                                                                                                                                                                                                                                                                                            | m threahold                   | valtaga                       |           |           |           |                                                 |               |          |         |

| BP1:BPO               |           | b = maximu<br>b = 1 page, 1                                                                                                                                                                                                                                                                                                                                                                         |                               | vonage                        |           |           |           |                                                 |               |          |         |

| DF1.DPU               |           | b = 1 page, $b = 2$ pages,                                                                                                                                                                                                                                                                                                                                                                          |                               |                               |           |           |           |                                                 |               |          |         |

|                       |           | b = 2 pages,<br>b = 4 pages,                                                                                                                                                                                                                                                                                                                                                                        |                               |                               |           |           |           |                                                 |               |          |         |

|                       |           | b = 4 pages,                                                                                                                                                                                                                                                                                                                                                                                        |                               | (default conf                 | iguratio  | n)        |           |                                                 |               |          |         |

|                       | 11        | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                               | o ounto                       | (actuall colli                | -ourun0   | )         |           |                                                 |               |          |         |

# 5.2. FUSEX Word (Read/Program via Programming Command)

# 5.3. DEVICE Word (Hard-Wired Read-Only)

| 1      | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 0     |

|--------|---|---|---|---|---|---|---|---|---|---|-------|

| Bit 11 |   |   |   |   |   |   |   |   |   |   | Bit 0 |

# 6.0 MEMORY ORGANIZATION

#### 6.1. Program Memory

The program memory is organized as 2K, 12-bit wide words. The program memory words are addressed sequentially by a binary program counter. The program counter starts at zero. If there is no branch operation, it will increment to the maximum value possible for the device and roll over and begin again.

Internally, the program memory has a semi-transparent page structure. A page is composed of 512 contiguous program memory words. The lower nine bits of the program counter are zeros at the first address of a page and ones at the last address of a page. This page structure has no effect on the program counter. The program counter will freely increment through the page boundaries.

#### 6.1.1. Program Counter

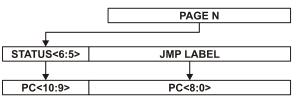

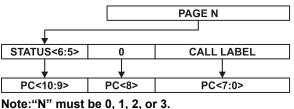

The program counter contains the 11-bit address of the instruction to be executed. The lower eight bits of the program counter are contained in the PC register (02h) while the upper bits come from the upper three bits of the STATUS register (PA0, PA1, PA2). This is necessary to cause jumps and subroutine calls across program memory page boundaries. Prior to the execution of a branch operation, the user program must initialize the upper bits of the STATUS register to cause subsequent branch instructions to vector to the desired page. An alternative method is to use the PAGE instruction, which automatically causes subsequent branch instructions to branch vector to the desired page, based on the value specified in the operand field. Upon reset, the program counter is initialized with 07FFh.

#### 6.1.2. Subroutine Stack

The subroutine stack consists of eight 11-bit save registers. A physical transfer of register contents from the program counter to the stack or vice versa, and within the stack, occurs on all operations affecting the stack, primarily calls and returns. The stack is physically and logically separate from data RAM. The program cannot read or write the stack.

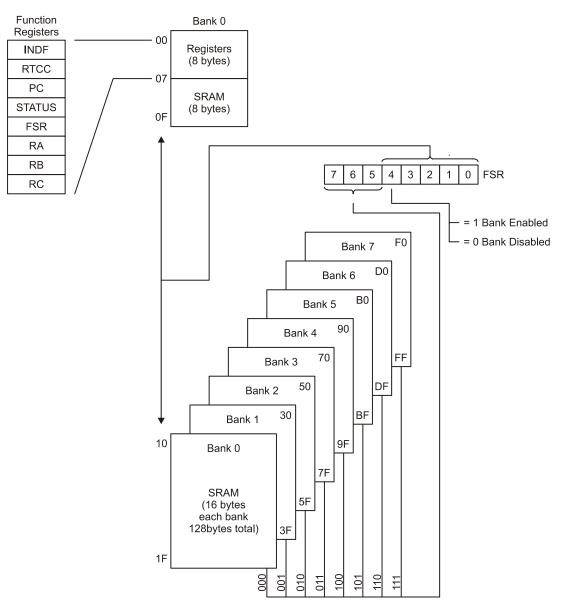

#### 6.2. Data Memory

The data memory consists of 136 bytes of RAM, organized as eight banks of 16 registers plus eight registers which are not banked. Both banked and non-banked memory locations can be addressed directly or indirectly using the FSR (File Select Register). The special-function registers are mapped into the data memory.

#### 6.2.1. File Select Register (04h)

Instructions that specify a register as the operand can only express five bits of register address. This means that only registers 00h to 1Fh can be accessed. The File Select Register (FSR) provides the ability to access registers beyond 1Fh.

Figure 6-1 shows how FSR can be used to address RAM locations. The three high-order bits of FSR select one of eight SRAM banks to be accessed. The five low-order bits select one of 32 SRAM locations within the selected bank. FSR.4 essentially enables or disables banked RAM. For the lower 16 addresses, Bank 0 is always accessed, irrespective of the three high-order bits. Thus, RAM register addresses 00h through 0Fh are "global" in that they can always be accessed, regardless of the contents of the FSR.

The entire data memory (including the dedicated-function registers) consists of the lower 16 bytes of Bank 0 and the upper 16 bytes of Bank 0 through Bank 7, for a total of (1+8)\*16 = 144 bytes. Eight of these bytes are for the function registers, leaving 136 general-purpose memory locations. In the 18-pin SX packages, register RC is not used, which makes address 07h available as an additional general-purpose memory location.

Below is an example of how to write to register 10h in Bank 4:

| mov | FSR,#\$90  | ;Select Bank 4 by                                                |

|-----|------------|------------------------------------------------------------------|