# M34225M1-XXXSP/FP M34225M2-XXXSP/FP

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

#### **DESCRIPTION**

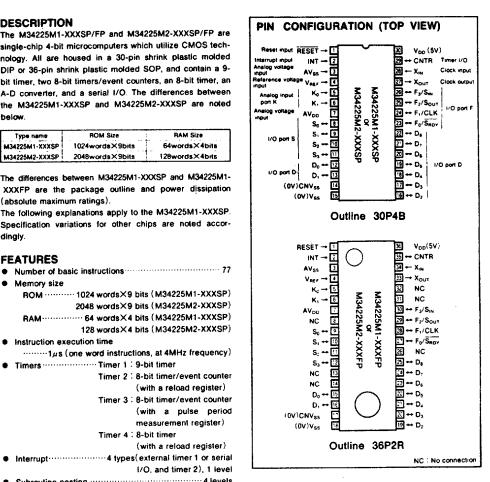

The M34225M1-XXXSP/FP and M34225M2-XXXSP/FP are single-chip 4-bit microcomputers which utilize CMOS technology. All are housed in a 30-pin shrink plastic molded DIP or 36-pin shrink plastic molded SOP, and contain a 9bit timer, two 8-bit timers/event counters, an 8-bit timer, an A-D converter, and a serial I/O. The differences between the M34225M1-XXXSP and M34225M2-XXXSP are noted

| Type name      | ROM Size        | RAM Size       |

|----------------|-----------------|----------------|

| M34225M1-XXXSP | 1024words×9bits | 64words×4bits  |

| M34225M2-XXXSP | 2048words×9bits | 128words×4bits |

The differences between M34225M1-XXXSP and M34225M1-XXXFP are the package outline and power dissipation (absolute maximum ratings).

The following explanations apply to the M34225M1-XXXSP. Specification variations for other chips are noted accordingly.

#### **FEATURES**

| • | Memory Size                                    |

|---|------------------------------------------------|

|   | ROM 1024 words×9 bits (M34225M1-XXXSP)         |

|   | 2048 words×9 bits (M34225M2-XXXSP)             |

|   | RAM 64 words×4 bits (M34225M1-XXXSP)           |

|   | 128 words×4 bits (M34225M2-XXXSP)              |

| • | Instruction execution time                     |

|   | 1µs (one word instructions, at 4MHz frequency) |

| • | Timers Timer 1 : 9-bit timer                   |

|   | Timer 2 : 8-bit timer/event counter            |

|   | (with a reload register)                       |

|   | Timer 3 : 8-bit timer/event counter            |

|   | (with a pulse period                           |

|   | measurement register)                          |

|   | Timer 4 . 8-bit timer                          |

|   | (with a reload register)                       |

| • | Interrupt 4 types (external timer 1 or serial  |

|   | I/O, and timer 2), 1 level                     |

| • | Subroutine nesting ······· 4 levels            |

#### **APPLICATION**

Washing machine, Rice cooker, Camera, Office automation equipment, Copying machine, Medical instruments, Learning equipment, Toys

Built-in feed back resistance for clock

Analog inputs (Port K) -----2 • Timer I/O port (CNTR) -------1 'A-D converter ...... 8-bit successive approximation Serial I/O ----- 8-bit X 1

### M34225M1-XXXSP/FP M34225M2-XXXSP/FP

# M34225M1-XXXSP/FP M34225M2-XXXSP/FP

# SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

# FUNCTIONS OF M34225M1-XXXSP/FP and M34225M2-XXXSP/FP

|                                  | Parameter                |                   | Functions                                                                     |

|----------------------------------|--------------------------|-------------------|-------------------------------------------------------------------------------|

| Number of basic instructions     |                          |                   |                                                                               |

| Instruction execution time       |                          |                   | 1//s Lone word instructions, at 4MHz frequency,                               |

|                                  | Clock frequency          |                   | 400kHz~4MHz                                                                   |

| Clock                            | Clock generating circuit |                   | Built-in (externally connected ceramic resonator, built-in feed back resistor |

|                                  | 7                        | M34225M1-XXXSP/FP | 1024wordsX9bits                                                               |

|                                  | ROM                      | M34225M2-XXXSP/FP | 2048words×9bits                                                               |

| Memory size                      | 1                        | M34225M1-XXXSP/FP | 64words×4bits                                                                 |

|                                  | RAM                      | M34225M2-XXXSP/FP | 128words×4bits                                                                |

|                                  | 10                       | 1/0               | 1-bn×9                                                                        |

|                                  | F                        | 1/0               | 4-bit×1                                                                       |

|                                  | \$                       | 1/0               | 4-bit×1                                                                       |

| Input/Output ports               | K                        | Input             | 2 (analog input), 2-bits X1 (digital input                                    |

|                                  | CNTR                     | 1/0               | 1-bitX1                                                                       |

|                                  | INT                      | Input             | 1-baX1                                                                        |

|                                  | :                        | D.S               | 12V (max )                                                                    |

|                                  | Input/Output voltage     | F                 | 10V (max )                                                                    |

| Input/Output                     | Input voltage            | Т К               | 5V (max.)                                                                     |

| characteristics                  |                          | D. S              | 12mA (avg.)                                                                   |

|                                  | Output current           | F                 | 5mA (avg )                                                                    |

| A-D converter                    | · ·                      | *                 | Built-in (absolute accuracy ±3LSB 8-bit successive approximation              |

| Serial I/O                       |                          |                   | 8-bit×1                                                                       |

| Series I/O                       | Timer I                  |                   | 9-bit timer, fixed division                                                   |

|                                  | Timer 2                  |                   | B-bit timer/event counter with an 8-bit reload register                       |

| Timers                           | Timer 3                  |                   | 8-bit timer/event counter with a pulse period measurement register            |

|                                  | Timer 4                  |                   | 8-bit timer with an B-bit reload register                                     |

|                                  | Types                    |                   | 4types external timer 1 or serial I.O and timer 2                             |

| Interrupts                       | Nesting                  |                   | level                                                                         |

| O bouldes and the                |                          | •                 | 4levels '3levels, when an interrupt is used or TABPp instruction is executed  |

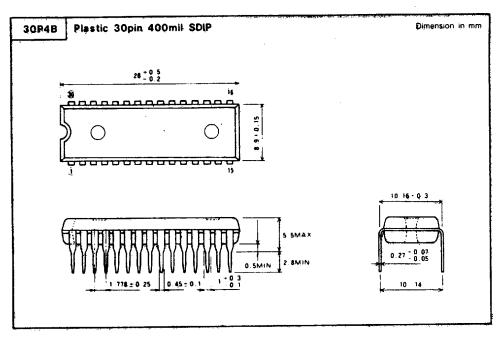

| Subroutine nesting               | M34225M1-XXXSP, M3       | 1225M2-XXXSP      | 30-pin shrink plastic molded DIP                                              |

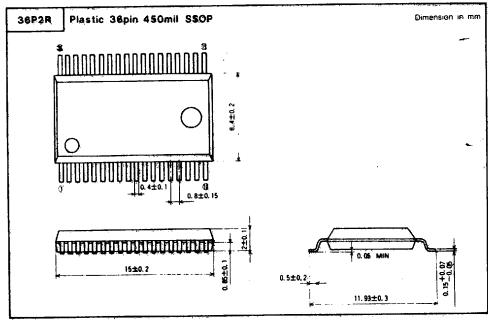

| Package                          | M34225M1-XXXFP, M3-      |                   | 36-pin shrink plastic molded SOP                                              |

|                                  | MO4550M (*AAATT, MG      |                   | 5V typ                                                                        |

| Supply voltage Power dissipation |                          |                   | 17.5mW typ 1 X., =4MHz at normal operation                                    |

# M34225M1-XXXSP/FP M34225M2-XXXSP/FP

#### SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

#### PIN DESCRIPTION

| Pin                            | Name                    | Input/<br>Output | Functions                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------|-------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DO</sub>                | Supply voltage          |                  | Connected to +5V power aupply.                                                                                                                                                                                                                                                                                                                               |

| V <sub>S8</sub>                | Ground                  |                  | Connected to 0V power supply.                                                                                                                                                                                                                                                                                                                                |

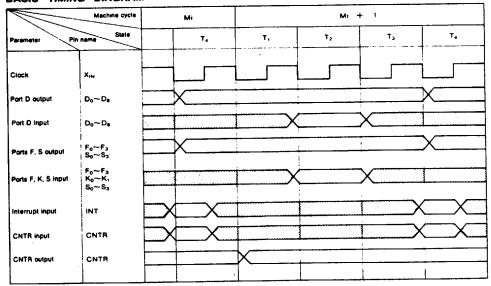

| D <sub>0</sub> ~D <sub>8</sub> | I/O port D              | 1/0              | Each pin functions as an 1-bit unit output or input This port is turned to an input enabled state when the output latch is set to "1". The output structure is N-channel open drain.                                                                                                                                                                         |

| F <sub>0</sub> ~F <sub>3</sub> | I/O port F              | 1/0              | This port functions as a 4-bit I/O This port is furned to an input enabled state when the output latch is set to "1". When senal I/O is used, F <sub>0</sub> , F <sub>1</sub> , F <sub>2</sub> , and F <sub>2</sub> work as S <sub>ROY</sub> , CLK, S <sub>OUT</sub> , and S <sub>IN</sub> pins, respectively. The output structure is N-channel open drain. |

| K <sub>0</sub> ~K <sub>1</sub> | Analog input port K     | Input            | This port functions as an input for A-D converter, and can use as a 2-bit normal input port.                                                                                                                                                                                                                                                                 |

| S₀~S₃                          | I/O port S              | 1/0              | This port functions as a 4-bit input.  This port is turned to an input enabled state when the output latch is set to "1".  The output structure is N-channel open drain.                                                                                                                                                                                     |

| CNTR                           | Timer I/O               | 1/0              | This port has an Input function for the event count of timer 2 and timer 3, or an output function for the over-<br>llow signal of timer 2. Both of these functions are selected by software.  The output structure is N-channel open drain.                                                                                                                  |

| INT                            | Interrupt input         | Input            | This is an interrupt input pin.                                                                                                                                                                                                                                                                                                                              |

| RESET                          | Reset input             | Input            | To enter the reset state, this input pin must be kept at a "L" for more than one machine cycle.                                                                                                                                                                                                                                                              |

| XIN                            | Clock input             | Input            | These are I/O pins of internal clock generating circuit.                                                                                                                                                                                                                                                                                                     |

| X <sub>OUT</sub>               | Clock output            | Output           | Connect either a ceramic resonator (400kHz~4MHz) to these pins.                                                                                                                                                                                                                                                                                              |

| CNVss                          | CNVss                   | input            | This is usually connected to Yss. and supply "L" (OV).                                                                                                                                                                                                                                                                                                       |

| AVDD                           | Analog voltage input    |                  | This is the power supply input pin for the A-D converter.                                                                                                                                                                                                                                                                                                    |

| AV <sub>5S</sub>               | Analog voltage input    |                  | This is the power supply input pin for the A-D converter.                                                                                                                                                                                                                                                                                                    |

| V <sub>REF</sub>               | Reference voltage input | Input            | This is the reference voltage input pin for the A-D converter                                                                                                                                                                                                                                                                                                |

### M34225M1-XXXSP/FP M34225M2-XXXSP/FP

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

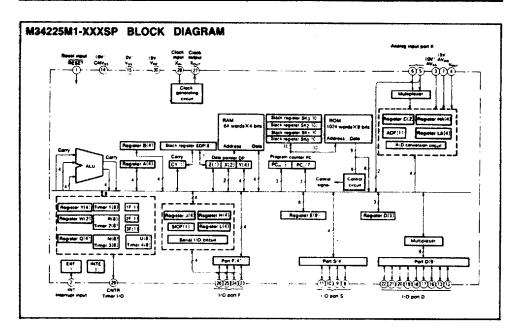

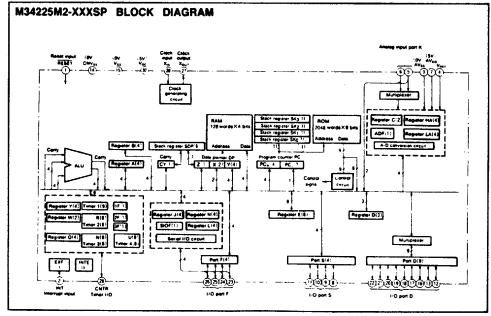

#### FUNCTION BLOCK OPERATIONS PROGRAM MEMORY (ROM)

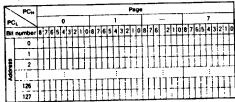

The memory is a mask ROM of 1024 words X 9 bits, and stores user-created instruction codes. The ROM is composed of 8 pages, each page consisting of addresses from 0~127. A ROM address map is shown in Figure 1. Page 2 is a special page used for subroutine calls. A page 2 subroutine can be called from an arbitrary page by using a one-word BM instruction.

Also, by executing a TABP<sub>p</sub> instruction ( $p=4\sim7$ ), pages 4  $\sim$ 7 can be used as data area. When executing this instruction, one of the stacks is used.

Fig.1 ROM address map

Note: The ROM of M34225M2-XXXSP is composed of 16 pages. By executing a TABPp instruction (p = 12  $\sim$ 15), pages 12~15 can be used as data area.

#### PROGRAM COUNTER (PC)

This counter is used to specify a ROM address, and determines the sequence in which instructions are read from the ROM. This program counter (PC) consists of 10 bits: the upper 3 bits (PCH) stand for a ROM page, and the lower 7 bits (PCL) stand for an address. The PC is a pure binary counter and is incremented each time an instruction is executed. However, when executing a branch instruction, subroutine call instruction or return instruction, its value takes that specified by that instruction.

The PC takes the zero address of the next page, after address 127 of that page is reached.

Note: The program counter (PC) of M34225M2-XXXSP consists of 11 bits ((PC<sub>H</sub>)=4 bits, (PC<sub>L</sub>) =7 bits).

# STACK REGISTERS (SKo, SK1, SK2, SK3)

When a branch to a subroutine or to an interrupt handling routine is executed, these registers are used to temporarily save the contents of the PC before the branch, and until control is returned to the routine.

Since there are four 10-bit registers (SK), up to four subroutine levels can be called. If one of the levels has been used for execution of an interrupt routine or TABP p instruction, however, only 3 levels can be used for subroutines.

The address of the stack register is specified by a stack pointer.

Note: The stack register (SK) of M34225M2-XXXSP consists of four 11-bit registers.

#### DATA MEMORY (RAM)

This is the memory in which various processing data and control data are stored. Its size is 64 words × 4 bits (256 bits). One word of RAM is composed of 4 bits. However, bit processing can be accomplished for the entire memory area. Figure 2 shows an address map of the RAM. An address in RAM can be selected by the registers Z, X, and Y of the data pointer (DP).

| File              | Register Z | 1 |   |   |   |   |     | _      | 0 |   |                                              |    |   |   |          |    |   |     |   | 1 |   |   |     |

|-------------------|------------|---|---|---|---|---|-----|--------|---|---|----------------------------------------------|----|---|---|----------|----|---|-----|---|---|---|---|-----|

| indication        | Register X |   | - | ) | - |   | 1   |        |   | 7 | 2                                            |    |   | 3 | <u> </u> | 2  |   | 0   |   |   | Ĺ | 3 | 3   |

| Br                | l number   | 3 | 2 | 1 | 0 | 3 | 2 1 | .0     | 3 | 2 | 1                                            | 0  | 3 | 2 | ١        | 0. | 3 | 2 1 | 0 | Ė | 3 | 2 | 1:0 |

|                   | 0          | 1 |   |   |   |   |     | Π      |   | Ĺ |                                              |    |   |   |          |    |   | :   |   | _ |   | _ | _   |

| <b>₹</b> ⊊        | 1          | 1 |   |   |   |   |     | !<br>! |   | : |                                              |    |   |   | _        |    |   | ī   | ì |   |   |   |     |

| E)                | 2          | ī | į |   |   |   |     |        | 1 | L | <u>į                                    </u> | :_ | _ | _ |          | _  |   | _   |   |   |   |   |     |

| Digit m<br>(Regis | :          | 1 |   |   |   |   | ī   |        | Ī |   | :                                            |    |   | - |          | _  | _ | :   | _ |   | : |   |     |

| ₹5                | 6          | 7 | i |   |   |   |     |        | 1 |   | :                                            |    |   | 1 |          |    |   |     | _ |   |   |   |     |

|                   | 7          |   | • |   |   |   |     | _      |   | - |                                              |    |   |   |          |    |   |     |   |   |   | • |     |

Fig.2 RAM address map

Note: The digit number in RAM of M34225M2-XXXSP is composed of 16 digits  $((Y)=0\sim15)$ .

#### DATA POINTER (DP)

This is a register to specify a RAM address and the bit location for I/O port D. The data pointer (DP) is composed of 7 bits

Register Z, the most significant bit of the DP, specifies the RAM file group, the middle 2-bit register (X) specifies the RAM file, and the lower 4-bit register (Y) specifies the RAM digit. Register Y also specifies the bit location for I/O port D.

#### 4-BIT ARITHMETIC AND LOGIC UNIT (ALU)

This is a 4-bit arithmetic unit, and consists of a 4-bit addition unit and its associated logical circuits. This unit performs addition, comparison, bit manipulation, and so on.

#### REGISTER A (ACCUMULATOR) AND CARRY FLAG (CY)

Register A is an accumulator exclusively used for computation. It is composed of 4 bits. The processing of data such as computation, transfer, exchange, transformation and I/O is executed using mainly this register. The carry flag (CY) stores the carry from the most significant bit of the ALU after executing an AMC instruction. It can also be used as an 1-bit flag

#### REGISTER B AND REGISTER E

Register B is composed of 4 bits, and can be used for storage of 4-bit data or transfer of 8-bit data in conjunction with register A. Register E is composed of 8 bits, and can be used for 8-bit data transfer to or from register A and B.

MITSUBISHI ELECTRIC

# SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

#### REGISTER D

Register D is composed of 3 bits and in conjunction with register A, can be used to store a 7-bit ROM address. This register is used with TABP p instruction execution.

#### INTERRUPT

The M34225M1-XXXSP has 4 types, 1 level interrupt function. It is a vector interrupt. Table 1 shows the interrupt sources and corresponding vector interrupt addresses.

Table 1. Interrupt types and vector interrupt addresses

|                                                  | Interrupt types                                                                                                                                     | Interrupt address |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Interrupt name                                   | Interrupting condition                                                                                                                              | Hiteliopi ecoress |

| External interrupt                               | When a rising pulse ("L"→"H") or a falling pulse ("H"→"L") is input to the INT pin (can be selected either of those wave-torms by the register Q)   | Page 1, address 0 |

| Timer 1 interrupt<br>or Senal I/O inter-<br>rupt | When the timer 1 is overflow, or receive or transmit of serial I/O is completed (can be selected either of those interrupt types by the register J1 | Page 1, address 2 |

| Timer 2 interrupt                                | When the timer 2 is overflow                                                                                                                        | Page 1, address 4 |

An interrupt is executed when one of the interrupting conditions shown in Table 1 above is satisfied, and the interrupt enable flag INTE is set to "1" (INTE ="1" when an El instruction is executed, enables the interrupt, and INTE ="0" when a DI instruction is executed, disables the interrupt.) While INTE="0", the interrupting condition is not changed, and an interrupt is executed only when INTE="1". Then the priority of the interrupt is the external interrupt, timer or serial I/O interrupt and timer 2 interrupt, respectively.

Either interrupting from timer 1 or serial I/O is determined by the bit 1 of the serial I/O mode register (register J).

The cause of each interrupt can be controlled by the soft-

The cause of each interrupt can be controlled by the software. If the interrupt is not executed, interrupting conditions are tested by skip instruction. Either to execute an interrupt or execute a skip instruction can be determined by bit  $0\sim2$  of the timer control register (register V).

When an interrupt handling program is executed, only one of the 4 sets of stack registers is needed to allowing the remaining 3 sets of stack registers to used for subroutine calls. After an interrupt handling program execution is started, the values of registers (such as register A or B) used in the interrupt handling program need to be saved by the program, and restored with an RTI instruction before returning to the main program. The data pointer (Z, X and Y) and carry flag however, are automatically saved and restored

When an interrupt is executed, the internal state of the mic-rocomputer enters the state described below:

(1) Program counter

The vector interrupt address, shown in Table 1, is set

after the next (main program) instruction address is saved in one of the stack registers.

(2) Interrupt enable flag (INTE)

The INTE flag is reset to the interrupt disable state.

(3) Skip flag

The skip flag enables the determination of whether to skip when a skip instruction (or a subsequent skip instruction) is encountered. This skip flag can access the stack so when an interrupt occurs the flag is automatically saved into the stack and its skip decision condition is retained.

#### TIMER/EVENT COUNTER

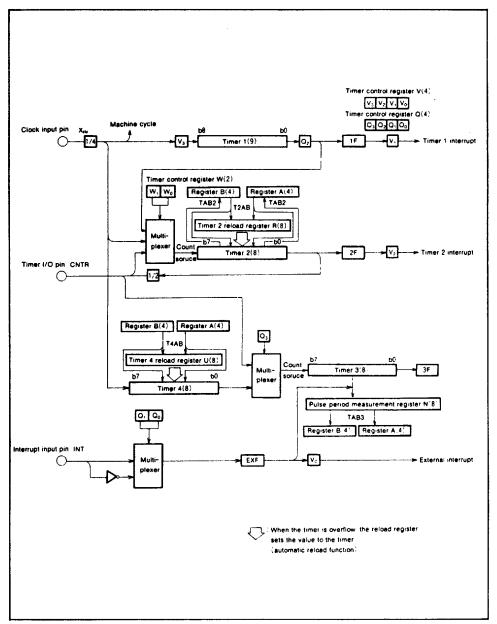

The timer/event counter can function as four counters (timers). As shown in Figure 4, it is composed of timer 1, timer 1 interrupt request flag (1F), timer 2, timer 2 reload register (register R), timer 2 interrupt request flag (2F), timer 3, timer 3 overflow flag (3F), pulse period measurement register (register N), timer 4, timer 4 reload register (register U), timer I/O port, and timer control registers (registers V, W and Q).

The two timers (timers 1, 2, 3 and 4) are controlled by the timer control register.

(1) Timer 1

This is a 9-bit counter, and sets the timer 1 interrupt request flag (1F) every time the machine cycle count (500kHz for 2MHz clock frequency) reaches 500 or 20. The reset and/or operation start and/or counting of the timer is controlled by the timer control register.

(2) Timer 2

Timer 2 is an 8-bit binary down counter, which has the timer 2 reload register (register R). The values of timer 2 and register R can be set by executing a T2AB instruction.

Also, the value of timer 2 can be read using a TAB2 instruction.

The start/stop of the counter and the selection of the count sources (the clock oscillating frequency divided by 4, the overflow signal from timer 1, and an external signal from the CNTR pin) can be controlled by the timer control register (W). Should it overflow, the timer 2 interrupt request flag (2F) is set and timer 2 obtains a value from the reload register (R) (auto-reload function) in order to continue counting.

(3) Timer 3

Timer 3 is an 8-bit binary down counter, which has the pulse period measurements register (register N). Timer 3 is set to FF<sub>16</sub> when data is set to timer 4, and it counts the overflow signal from timer 4 or the external signal. The count source is determined by the timer control register (Q). Should it overflow, the timer 3 overflow flag (3F) is set and timer 3 is set to FF<sub>16</sub> in order to continue counting.

The pulse period measurement register (register N)

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

latches the contents of timer 3 when the external interrupt request flag is set ("0" to "1"). The contents of register N can be read by using a TAB3 instruction.

(4) Timer 4

Timer 4 is an 8-bit binary down counter, which has a reload register (register U). The values of timer 4 and register U can be set by executing a T4AB instruction, and counts the oscillating frequency divided by four. When it overflows, timer 4 is automatically reloaded from register U and continues counting.

(5) Timer I/O (CNTR pin)

This is normally an input pin which is selected as the count source of timer 2 and timer 3 by the timer control register, otherwise this becomes an output pin for a 1/2 cycle of the timer 2 overflows.

Levels of these ports ("H" or "L") can be tested by execution of SNZC instruction.

(6) Timer 1 interrupt request flag (1F)

Timer 2 interrupt request flag (2F)

The timer 1 interrupt request flag (1F) is set every time timer 1 count reaches 500 or 20, and the timer 2 interrupt request flag (2F) is set every time timer 2 overflows. These flags can be tested by an interrupt or execution of skip instruction (SNZ1 or SNZ2). Whether to execute an interrupt or execute a skip instruction can be determined by the timer control register. Each of these tiemrs interrupt request flags (1F and 2F) can be reset by an interrupt or execution of a skip instruction.

(7) Timer 3 overflow flag (3F)

This flag sets every overflow of timer 3. The testing 3F flag can be determined by the execution of skip instruction (SN23).

The 3F flag can be reset after skip instruction is executed and the next instruction is skipped.

(8) External interrupt request flag (EXF)

External interrupt request flag is set when the interrupting conditions are satisfied. This flag is tested by the execution of interrupt or skip instruction (SNZO). Either interrupt or skip instruction is determined by the timer control register V. This flag is reset by the execution of interrupt or skip instruction.

INT pin (interrupt input) level can also be tested by executing the skip instruction (SNZO). Either testing INT pin levels or EXF flag is determined by the timer control register V and Q.

EXF flag cannot be reset if the skip instruction is selected for the testing of INT pin levels and is executed.

(9) Timer control registers (V, W and Q)

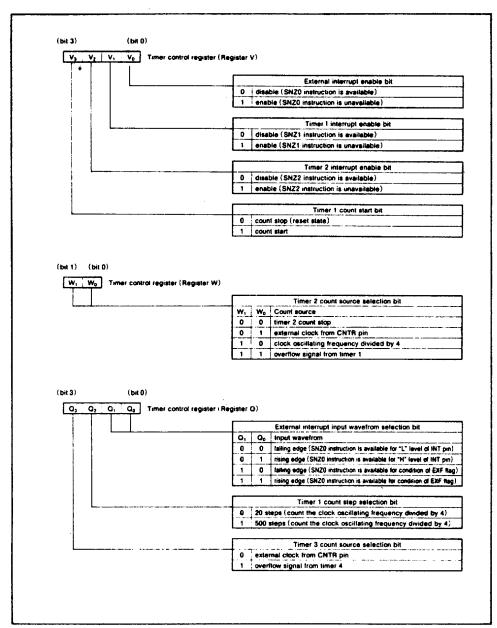

The timer control registers perform the above functions, and the data is transfered to these registers from register A by the TVA, TWA or TQA instruction. Figure 3 shows the structure of these registers.

#### M34225M1-XXXSP/FP M34225M2-XXXSP/FP

Fig.3 Structure of timer control registers (registers V, W, and Q)

### M34225M1-XXXSP/FP M34225M2-XXXSP/FP

Fig.4 Block diagram of timers

#### SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

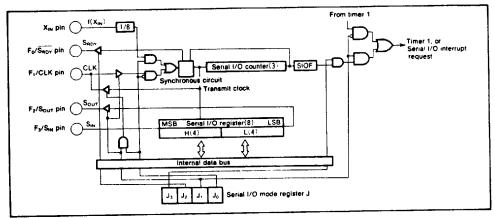

#### SERIAL I/O

The M34225M1-XXXSP houses a clock-synchronous serial I/O which can serially receive or send 8-bit data. This serial I/O is composed of serial I/O register (H and L), serial I/O counter. Each of the serial I/O register (J) and a serial I/O counter. Each of the serial I/O register (H and L) are used to transmit 4-bit data. The serial I/O mode register (J) is used to select the functions denoted by its 4 bits. This serial I/O performs data transfer with the internal CPU by using the data bus, and with the external CPU by using ports  $F_0 \sim F_3$ . Ports  $F_0 \sim F_3$  are not only I/O ports, but  $F_0$  is also a serial I/O receive ready pin  $(\overline{S_{ROV}})$ ,  $F_1$  is a synchronous clock input pins  $(C_{LK})$ , and  $F_2$  and  $F_3$  are serial data input/output pins  $(S_{OUT},$  and  $S_{IN})$ . The functions of these ports can be selected by the serial I/O mode register.

(1 Serial I/O regiser (H and L)

The serial I/O register is for transforming serial data to parallel data. Each of these registers H and L consists of 4 bits. The upper 4 bits of the transmitted data uses

register H and the lower 4 bits, register L. The received data is stored but by bit starting from the highest bit (bit 3) of register H, and the transmitted data is transmitted bit by bit starting from the lowest bit (bit 0) of register L.

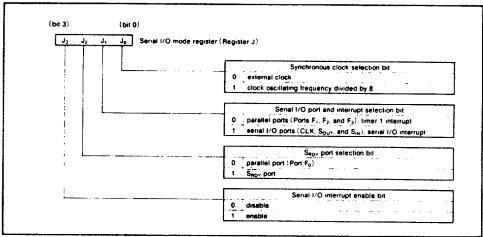

(2) Serial I/O mode register (J)

This is a 4-bit register used to select the clock source, or port function, and interrupt sources (interrupt from timer 1- or from serial I/O) with respect to the serial I/O.

(3) Serial I/O transmit/receive completion flag (StOF)

This flag is set when the serial data transmit/receive is completed. This flag can be tested by an interrupt and the execution of a skip instruction (SZS1). Whether to enable or disable an interrupt can be decided by the serial I/O mode register.

The SIOF flag is reset, either when an interrupt is accepted or after the next instruction is skipped by the execution of the skip instruction.

Fig.5 Structure of serial I/O mode register (register J)

#### M34225M1-XXXSP/FP M34225M2-XXXSP/FP

# SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

Fig.6 Block diagram of serial I/O

#### **A-D CONVERSION**

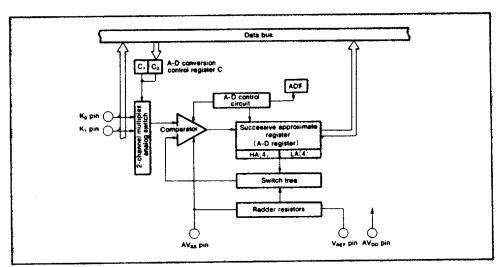

A-D conversion can be controlled such that the A-D control circuit controls those registers, etc., described below. The start and end of A-D conversion can be recognized by software. Figure 8 shows the A-D conversion circuit. The resolution of the A-D conversion is 8 bits, its analog input pins are  $K_0 \sim K_1$  and its conversion speed is  $36\mu s$  (when  $f(X_{IN}) = 4MHz$ ).

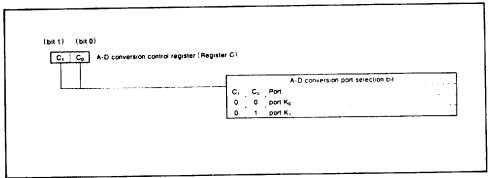

- (1) A-D control register (C)

- The A-D control register (C) is a 2-bit register. One of the two analog inputs is selected according to the combination of bits 0 and 1 of this register. Figure 7 shows the correspondence between the selected analog input pin and bit 0 or 1.

- (2) The A-D conversion start instruction (ADST) When the ADST instruction is executed, the A-D conversion begins.

- (3) A-D conversion termination flag (ADF)

- The A-D conversion termination flag is a 1-bit flag. When the A-D conversion is finished, this flag is set to "1".

- This flag value can be tested by a skip instruction (SZAD). By executing a skip instruction, the ADF flag is set to "0".

- (4) Successive approximation register (registers HA and LA)

The result of A-D conversion is stored in the succesive approximation registers. HA and LA Registers HA and LA are each composed of 4 bits, and can send their data to register A. The upper 4 bits of the 8-bit digital data (resulting from A-D conversion) are stored in register HA, and the lower 4 bits in register LA.

Fig.7 Structure of A-D conversion control register (register C)

### M34225M1-XXXSP/FP M34225M2-XXXSP/FP

#### SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

Fig.8 Block diagram of A-D conversion circuit

#### VO PORT

1 Port D (D<sub>0</sub>~D<sub>8</sub>)

This port performs 9-bit I/O's (SZD, SD, and RD). Its output has a latch which is capable of manipulating 1-bit, and the I/O can be carried out such that register Y of the data pointer specifies one of the D ports.

For input, the output latch of the corresponding bits must be set to "1". The instruction CLD, can set all of the port D latches to "1".

The output structure of this port is N-channel open drain.

12 Port F (F<sub>0</sub>~F<sub>3</sub>)

This port has a 4-bit output (OFA) and input (IAF) function. For input, the output latch for the corresponding bits must be set to "1".

The output structure of this port is N-channel open drain.

3' Port S (S0~S7)

This port has one 8-bit output (OSAB) and two 4-bit inputs (IAS).

For input, the output latch for the corresponding bits must be set to "1". The instruction CLS, can set all of the port S latches to "1".

The output structure of this port is N-channel open drain.

#### RESET FUNCTION

If an "L" input is supplied to the RESET pin for longer than one machine cycle, the processor is reset. After that, if the RESET pin is supplied with an "H" input, the program execution starts at address 0 of page 0. When the processor is reset, its status is as follows:

Address 0 of page 0 is input into the program counter.

(PC)→0

2 Interrupt is disabled. (INTE)←0 (the same as when a DI instruction is executed)

- 13. Registers V and W are set to "0". (V) ←0, and (W) ←0

- 4. Register Q is set to "F<sub>16</sub>". (Q)~F<sub>16</sub>

- 15 External interrupt request flag (EXF), timer 1 interrupt request flag (1F), timer 2 interrupt request flag (2F), and timer 3 overflow flag (3F) are all reset.

- (EXF)=(1F)=(2F)=(3F) $\leftarrow$ 0

6 Output latches of ports D, F, S and CNTR, are all set to "1".

(D)=(F)=(S)=(CNTR) $\leftarrow$ 1

- 7. A-D conversion termination flag (ADF) is set to "0". (ADF) ←0

- 8 Serial I/O send/receive completion flag (SIOF) is set to "0" (SIOF) → 0

- Serial I/O mode register (register J) and A-D control register (register C) is set to "0". (J)→0, (C)→0

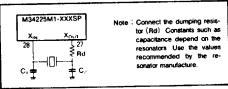

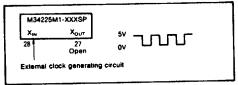

#### CLOCK GENERATING CIRCUIT

A clock generating circuit is built into the processor, so if a ceramic resonator is connected to the clock I/O pins a clock signals can be obtained. If the clock signals are input from an external circuit, connect the clock generating source to the  $X_{\rm IN}$  pin and leave the  $X_{\rm OUT}$  pin open.

Figures 9~10 show examples of the circuits.

#### M34225M1-XXXSP/FP M34225M2-XXXSP/FP

#### SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

Fig.9 External ceramic resonator circuit

Fig.10 External clock input circuit

#### DATA REQUIRED FOR MASK ORDERING

Please send the following data for mask orders.

- (1) M34225M1-XXXSP/FP or M34225M2-XXXSP/FP mask confirmation sheet

- (2) ROM data ····· EPROM 3 sets (Submit three sets of EPROM's with the same data)

- (3) Mark specification form for 30P4B

#### PRECAUTION FOR USE

Notes on noise and latch-up

In order to avoid noise and latch-up, connect the following external circuit.

- 1. Connect a bypass capacitor ( $\approx 0.1 \mu F$ ) directly between the V<sub>DD</sub> pin and V<sub>SS</sub> pin using a heavy wire, and connect the  $V_{\text{DD}}$  pin to the  $AV_{\text{DD}}$  pin and  $V_{\text{SS}}$  pin to the

- AV<sub>SS</sub> pin. ② Notes on INT pin

If the input polarity of the INT pin is changed by the bit 0 of the register Q (in the software program) care for the followina notes:

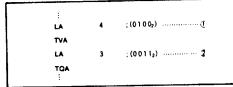

1. Set the bit 0 of the register V to "0" (1) and the bit 1 of the register Q to "1" (2) before the input polarity of the INT pin is changed (see Figure 11).

Fig.11 Example program-1

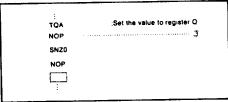

2. Depending on the input state of the INT pin, the external interrupt request flag EXF is set when the input polarity is changed. Therefore, execute SNZ0 instruc-

tion to reset the EXF flag after the setting of the register Q.

Also, more than one instruction is need before SNZ0 instruction (3)(see Figure 12).

Fig.12 Example program-2

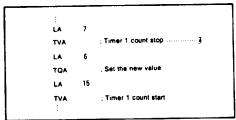

#### Notes on timer 1

When the count value of timer 1 is changed while it is counting, the first timing of timer 1 overflow just after the changing is unsettled. Therefore, change the count value while timer 1 is stopped (4) (see Figure 13).

Fig.13 Example program-3

#### Notes on serial I/O

So this microcomputer continues a serial transmission as long as an external clock inputs, when selected an external clock as synchronous clock, it must be controlled externally.

(When the SST instruction is executed and the serial I/O counter counts eight clocks, the SIOF flag is set to "1".)

#### Note on register Y

On M34225M1-XXXSP, when the contents of register Y are 8~15, this microcomputer has no correlative memory area. At this time, do not use the reading memory instructions (AM, AMC, SEAM, SZB, TAM, XAM, XAMI, and XAMD).

# SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

#### INSTRUCTION CODE TABLE

| The War                        | D <sub>6</sub> ~D <sub>4</sub> | 0 0000  | 0 000 | 0 0010 | 0 0011 | 0 0100  | 0 0101    | 0 0110            | 0 0111  | 0 1000 | 0 1001           | 0 1010     | 0 1011   | 0 1100             | 0 1101      | 0 1110           | 0 1111      | - 5  | 1 1000   |

|--------------------------------|--------------------------------|---------|-------|--------|--------|---------|-----------|-------------------|---------|--------|------------------|------------|----------|--------------------|-------------|------------------|-------------|------|----------|

| D <sub>3</sub> ~D <sub>0</sub> | Nede Cimer                     | 0.0     | 01    | 0 2    | 0 3    | 0.4     | 0 5       | 06                | 0.7     | 0.8    | 09               | 0.4        | 08       | 0 C                | 0.0         | 0 E              | 0 F         |      | 18~11    |

| 0000                           | 0                              | NOP     | BLA   | SZB    | BL     | ТАН     | BMLA      | XAM               | BML     | -      | -                | Α 0        | LA<br>O  | LXY<br>9, D        | LXY         | LXY<br>2. 0      | LXY         | ВМ   | В        |

| 0001                           | 1                              | BA      | CLD   | SZB    | BL     | TAL     | -         | XAM               | BML     | ADST   | <u> </u>         | ^          | LA       | LXY                | LXY         | LXY              | 3, 0<br>LXY | ВМ   | 8        |

| 0010                           | 2                              | _       | CLS   | SZB    | BL     | SZSI    | _         | 1<br>XAM          | <b></b> | TCA    |                  |            | LA       | 0, 1<br>LXY        | 1, 1<br>LXY | 2, 1<br>LXY      | 3, 1<br>LXY | ВМ   | 8        |

| 0011                           | 3                              |         | INY   | SZB    |        | SZAD    |           | XAM               | -       |        |                  | 2          | 2<br>LA  | 0, 2  <br>LXY      | 1, 2<br>LXY | 2. 2<br>LXY      | 3, 2<br>LXY |      | <u> </u> |

|                                | <b>_</b> ,                     |         |       | . 3    |        | 32AU    |           | 3<br>TAM          |         | TQA    | **               | 3<br>A     | 3<br>LA  | 0. 3<br>LXY        | 1, 3<br>LXY | 2, 3<br>LXY      | 3, 3<br>LXY | ВМ   | 8        |

| 0100                           | · 4                            | DI      | . RD  | SZD    | BL     | RT      |           | 0                 | BML     | OFA    | TABP             | 4.         | 4        | 0, 4               | 1, 4        | 2, 4             | 3, 4        | ВМ   | В        |

| 0101                           | 5                              | EI      | SD    | SEAn   | 8L     | RTS     | IAS       | .TAM<br>1         | BML     | T2AB   | TABP<br>5        | 5          | 5<br>5   | 0, 5               |             | 2, 5             | 3, 5        | Вм   | 8        |

| 0110                           | 6                              | RC      | -     | SEAM   | BL     | RTI '   | IAF       | TAM<br>2          | BML     | TVA.   | ##<br>TABP<br>6  | 6          | LA<br>6  | 0, 6               | LXY<br>1. 6 | LXY 2. 6         |             | ВМ   | В        |

| 0111                           | 7                              | sc      | DEY   | -      | BL     | _ :     | IAK       | MAT               |         | TWA    | * *<br>TABP<br>7 | A 7        | LA<br>7  | LXY                | LXY         | LXY              | LXY         | ₽м   | В        |

| 1000                           | 8                              | _       |       | ·-·    | *BL    | LZ<br>0 | TJA       | XAMI              | *BML    | TAHA   | _                | Α ,        | LA       | LXY                | LXY         | 2, 7             | LXY         | вм   | В        |

| 1001                           | 9                              | - ·     | T4AB  | TDA    | *BL    | LZ      | SST .     | ХАМІ <sup>°</sup> | ≠BML    | TALA   | _ :              | 8 :<br>A : | B<br>LA  |                    |             | 2, 8<br>LXY      |             | ВМ   | 8        |

| 1010                           | A                              | <br>AM  | TEAB  | TABE   | *BL    |         | THA       | XAMI              | * BML   | TAB2   |                  | 9 ±.       | LA       |                    | 1, 9<br>LXY | 2, 9<br>LXY      |             | ВМ   | В        |

| 1011                           |                                | <br>AMC | OSA   | - :    | *BL    |         | TLA       | 2<br>XAMI         | * BML   | TARR   |                  | 10<br>A    | 10<br>LA | 0, 10<br>LXY       |             |                  |             |      |          |

| 1100                           |                                |         | ;     |        |        | RB .    | i         | 3<br>XAMD         |         |        | TABP             | 11<br>A    | II.      | 0, 11<br>LXY       |             |                  |             | ВМ   | В        |

|                                |                                | TYA     | CMA   |        | *BL    | 0<br>RB | 0<br>SB ) | Ó KAMD            | + BML   |        | 12<br>TABP       | 12<br>A    | 12<br>LA | 0, 12              | 1, 12       | 2, 12            | 3, 12       | ВМ   | В        |

| 1101                           | - D                            | -       | RAR   | SNZ    | * BL   | 1       | 1         | 1                 | + BML   | SNZ2   | 13               | 13         | 13       | LXY<br>0, 13       | 1, 13       | 2, 13            | 3, 13       | BM   | В        |

| 1110                           | E                              | TBA :   | TAB   |        | * BL   | RB 2    | 2         | KAMD              | BML     |        | TABP             | A<br>14    | 14       | LXY : 1<br>0, 14 1 |             | LXY :<br>2, 14 ∷ |             | вм   | 8        |

| 1111                           | F                              | - '     | TAY   | szc    | + BL   | #B :    | SB 3      | (AMD<br>3         | * SML   |        | TABP             | #<br>15    | LA<br>15 | LXY . 1            | 1           |                  | 1           | BM ! | В        |

Note 1: The above table shows the correspondence between machine codes and machine instructions

D<sub>3</sub>-D<sub>0</sub> stands for the lower 4 bits of the machine codes, and D<sub>0</sub>-D<sub>4</sub> for the upper 5 bits of the machine codes.

Atso, the hexadecimal values of those codes are listed. There are two instruction types; 1-word and 2-word instructions, but in this table only the codes of the first word of each instruction is shown.

--

Do not use this code.

2 : The second word of 2-word instructions are listed below

|      |              | The | 2 56 | tca | nd ward | 7 |   |   |   |

|------|--------------|-----|------|-----|---------|---|---|---|---|

| BL   | 1            | 1   | 8    |     | a       |   | 8 | a | a |

| BML  | 1            | 0   | 8    | 8   | a       | a | ā |   |   |

| BA   | 1            | 3   |      | a   | a       | a |   | а | a |

| BLA  | $\mathbf{p}$ | 1   | ٠    | a   |         | 0 | P | p | P |

| BMLA | 1            | 0   |      | a   | a       | o | P | P | P |

| SEA  | 0            | 1   | 0    | 1   | 1       | n | n | n | n |

| SZD  | 0            | 0   | 0    | 1   | Ö.      | i | 0 | ť | i |

The BL, BML, and TABP codes marked with a asterisk are not available with the M34225M1-XXXSP.

The TABP codes marked with two asterisks are not available with the M34225M2-XXXSP.

## M34225M1-XXXSP/FP M34225M2-XXXSP/FP

### SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

SYMBOLS

The following notations are used for the following descriptions.

| Symbol   | Contents                                                | Symbol                                                      | Contents                                                                                                                                     |

|----------|---------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

|          | Register A (4-bit)                                      | x                                                           | Hexadecimal variable                                                                                                                         |

| <u> </u> | Register B (4-bit)                                      | у                                                           | Hexadecimal variable                                                                                                                         |

| B        | A-D conversion control register C (2-bit)               | Z                                                           | Hexadecimal variable                                                                                                                         |

| C        | Register D (3-bit)                                      | p                                                           | Hexadecimal variable                                                                                                                         |

| D        | Register E (8-bit)                                      | n                                                           | Hexadecimal constant                                                                                                                         |

| E        | The upper 4 bits of the serial I/O register H (4-bit)   | i                                                           | Hexadecimal constant                                                                                                                         |

| H        | The upper 4 bits of the successive approximation regis- | j                                                           | Hexadecimal constant                                                                                                                         |

| HA       | ter HA (4-bit)                                          | A <sub>3</sub> A <sub>2</sub> A <sub>1</sub> A <sub>0</sub> | Binary representation of the register A                                                                                                      |

|          | Serial I/O mode register J (4-bit)                      |                                                             | (the same as for other registers)                                                                                                            |

| J        | The lower 4 bits of the serial I/O register L (4-bit)   |                                                             | Direction in which data is transferred                                                                                                       |

| L        | The lower 4 bits of the serial (70 register £ (4-bit)   | ( )                                                         | The contents of register, memory, etc.                                                                                                       |

| LA       | The lower 4 bits of the successive approximation regis- | l ¥ ′                                                       | Exclusive logical OR                                                                                                                         |

|          | ter LA (4-bit)                                          | 1 <u>-</u>                                                  | Negation or condition of the flag is not change after the                                                                                    |

| N        | Pulse period measurement register N (8-bit)             | 1                                                           | instruction is executed                                                                                                                      |

| a        | Timer control register Q (4-bit)                        | M(DP)                                                       | RAM address which is specified by data pointer DP                                                                                            |

| R        | Timer 2 reload register (8-bit)                         | a                                                           | Label to show the address of \$6.85.84.83.82.81.80                                                                                           |

| U        | Timer 4 reload register U (8-bit)                       | p. a                                                        | Label to show the address of a <sub>6</sub> a <sub>6</sub> a <sub>8</sub> a <sub>3</sub> a <sub>2</sub> a <sub>1</sub> a <sub>0</sub> in the |

| V        | Timer control register V (4-bit)                        | p. 6                                                        | page P <sub>2</sub> P <sub>1</sub> P <sub>0</sub>                                                                                            |

| w        | Timer control register W (2-bit)                        | l c                                                         | Hexadecimal value C+hexadecimal value x (the same                                                                                            |

| x        | Register X (2-bit)                                      | 1 +                                                         | as for other value                                                                                                                           |

| Y        | Register Y (4-bit)                                      | i x                                                         |                                                                                                                                              |

| Z        | Register Z (1-bit)                                      | ^                                                           | *                                                                                                                                            |

| DP       | Data pointer (7-bit)                                    | ł                                                           |                                                                                                                                              |

|          | (consisting of the registers X, Y, and Z)               | Į.                                                          |                                                                                                                                              |

| PC       | Program counter (10-bit)                                | ļ                                                           |                                                                                                                                              |

| PCH      | The upper 3 bits of the program counter                 | l .                                                         |                                                                                                                                              |

| PCL      | The lower 7 bits of the program counter                 | 1                                                           |                                                                                                                                              |

| SK       | Stack register (10-bit×4)                               |                                                             | i                                                                                                                                            |

| SP       | Stack pointer (2-bit)                                   |                                                             |                                                                                                                                              |

| CY       | Carry flag                                              | 1                                                           |                                                                                                                                              |

| TI       | Timer 1                                                 |                                                             |                                                                                                                                              |

| T 2      | Timer 2                                                 |                                                             |                                                                                                                                              |

| T 3      | Timer 3                                                 |                                                             |                                                                                                                                              |

| T 4      | Timer 4                                                 | Į.                                                          |                                                                                                                                              |

| 1 F      | Timer 1 interrupt request flag                          | 1                                                           | •                                                                                                                                            |

| 2 F      | Timer 2 interrupt request flag                          | i                                                           |                                                                                                                                              |

| 3 F      | Timer 3 overflow flag                                   | İ                                                           |                                                                                                                                              |

|          | A-D conversion completion flag                          |                                                             |                                                                                                                                              |

| ADF      | External interrupt request flag                         |                                                             |                                                                                                                                              |

| EXF      | Interrupt enable flag                                   |                                                             |                                                                                                                                              |

| INTE     | External interrupt signal                               | 1                                                           | *                                                                                                                                            |

| INT      | Serial I/O transmit/receive completion flag             | 1                                                           |                                                                                                                                              |

| SIOF     | Timer I/O                                               |                                                             |                                                                                                                                              |

| CNTR     | 1                                                       |                                                             |                                                                                                                                              |

| D        | Port D (9-bit)                                          |                                                             |                                                                                                                                              |

| F        | Port F (4-bit)                                          | I                                                           |                                                                                                                                              |

| K        | Port K (2-bit)                                          | 1                                                           |                                                                                                                                              |

| S        | Port S (4-bit)                                          |                                                             | the instruction at the address pointed to by                                                                                                 |

Note 1: The M3422SM1-XXXSP performs a skip by ignoring the next instruction, and by not executing the instruction at the address pointed to by the contents of the program counter+2.

Therefore, the cycle number does not change, regardless of whether a skip is generated or not.

However, if TABP, RT, or RTS instruction is skipped, the cycle number becomes "1".

#### SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

#### MACHINE INSTRUCTIONS

| Parameter                      |           |                |                |                |                | los            | dructi         | on co      | de             |                |     |             |             | 10 SE            | 5 .      |                                                                                |

|--------------------------------|-----------|----------------|----------------|----------------|----------------|----------------|----------------|------------|----------------|----------------|-----|-------------|-------------|------------------|----------|--------------------------------------------------------------------------------|

| Typic of                       | Mnemonic  | D <sub>8</sub> | D <sub>7</sub> | D <sub>6</sub> | D <sub>3</sub> | D <sub>4</sub> | D <sub>3</sub> | D?         | D <sub>1</sub> | D <sub>0</sub> |     | adeci       | imel<br>n   | dental<br>dental | Mumber o | Functions                                                                      |

|                                | TAB       | 0              | 0              | 0              | 0              | 1              | 1              | 1          | 1              | 0              | 0   | 1           | E           | 1                | 1        | (A)←(B)                                                                        |

| Sers                           | TBA       | 0              | 0              | 0              | 0              | 0              | 1              | t          | 1              | 0              | 0   | 0           | E           | 1                | 1        | (B)←(A)                                                                        |

| Ten T                          | TAY       | 0              | 0              | 0              | 0              | ı              | ł              | 1          | 1              | 1              | 0   | 1           | F           | 1                | 1        | (A)←(Y)                                                                        |

| ž į                            | TYA       | 0              | 0              | 0              | 0              | 0              | 1              | 1          | 0              | 0              | 0   | 0           | С           | 1                | 1        | (Y)←(A)                                                                        |

| Register to register transfers | TEAB      | 0              | 0              | 0              | 0              | 1              | 1              | 0          | 1              | 0              | 0   | 1           | A           | 1                | 1        | (E <sub>7</sub> ~E <sub>4</sub> )~(B)<br>(E <sub>3</sub> ~E <sub>0</sub> )~(A) |

| ster                           | TDA       | 0              | 0              | 0              | 1              | 0              | 1              | 0          | 0              | 1              | 0   | 2           | 9           | 1                | 1        | (D)-(A)                                                                        |

| Reg                            | TABE      | 0              | 0              | 0              | 1              | 0              | 1              | 0          | 1              | 0              | 0   | 2           | A           | ,                | 1        | (B)←(E <sub>7</sub> ~E <sub>4</sub> )<br>(A)←(E <sub>3</sub> ~E <sub>0</sub> ) |

|                                | LXY x, y  | o              | 1              | 1              | ж,             | x <sub>o</sub> | уз             | <b>y</b> 2 | у <sub>1</sub> | Уo             | 0   | C<br>+<br>* | y           | 1                | 1        | (X) ← x, where x = 0 ~ 3<br>(Y) ← y, where y = 0 ~ 15                          |

| RAM addresses                  | LZ z      | 0              | 0              | 1              | 0              | 0              | 1              | 0          | 0              | z <sub>o</sub> | 0   | 4           | 8<br>+<br>z | 1                | 1        | (Z) — z, where z = 0 , 1                                                       |

| PAM 8                          | INY       | 0              | 0              | 0              | 0              | 1              | 0              | 0          | 1              | 1              | 0   | 1           | 3           | 1                | 1        | !<br>  ( <b>Y</b> )←( <b>Y</b> )+1<br>!                                        |

|                                | DEY       | 0              | 0              | 0              | a              | 1              | 0              | 1          | 1              | 1              | : 0 | 1           | 7           | 1                | 1        | (Y)←(Y)−1                                                                      |

|                                | , TAM )   | 0              | 0              | 1              | 1              | 0              | 0              | 1          | j,             | jo             | 0   | 6           | 4 +         | 1                | 1        | (A)(M(DP))                                                                     |

| ٠,                             |           |                | •              |                |                |                |                |            |                | ,              |     |             | •           | 1                | 1        | (X)←(X)¥ j, where j = 0 ~ 3<br>(A)←(M(DP))                                     |

| ş                              | XAM j     | 0              | 0              | 1              | 1              | 0              | 0              | 0          | jn             | jo             | . 0 | 6           | '           | ; <b>'</b>       | ! '      | $(X)\leftarrow (X) \forall j$ , where $j=0\sim3$                               |

| 1 2                            | XAMD j    | : 0            | 0              | ı              | 1              | 0              | i              | 1          | j۱             | jo             | . 0 | 6           | С           | 1                | 1        | (A)↔(M(DP))                                                                    |

| l ag                           |           |                |                | •              | •              | ٠              | •              | •          | ,,             | ю              | ľ   | ·           | +           | ļ .              | ľ        | (x)←(x) ¥ i                                                                    |

| to register transfers          | 1         | 1              |                |                |                |                |                |            |                |                | :   |             | •           | i                | !        | $(Y) \leftarrow (Y) - 1$ , where $j = 0 \sim 3$                                |

| AAM                            | : XAMI: j | 0              | 0              | 1              | 1              | 0              | 1              | 0          | jı             | jo             | 0   | 6           |             | ,                | 1        | (A)(M(DP))                                                                     |

| "                              |           |                |                |                |                |                |                |            |                |                |     |             | +           |                  |          | <br> (x)←(x)¥ j                                                                |

|                                |           |                |                |                |                |                |                |            |                |                |     |             |             |                  |          | $(Y)\leftarrow (Y)+1$ , where $j=0\sim 3$                                      |

| Arithmetic operations          | LA n      | 0              | 1              | 0              | 1              | 1              | n <sub>3</sub> | Пg         | n,             | no             | O   | В           | n           | 1                | 1        | (A)← n, where n = 0 ~15                                                        |

|                                |           |                |                |                |                |                |                |            |                |                |     |             |             |                  |          |                                                                                |

# M34225M1-XXXSP/FP M34225M2-XXXSP/FP

| The contents of register A are transferred to register A The contents of register Y are transferred to register A The contents of register Y are transferred to register A The contents of register A are transferred to register B The contents of register A are transferred to register E The contents of register A are transferred to register E The contents of register A are transferred to register B The contents of register B are transferred to register B The contents of register E are transferred to register B The contents of register E are transferred to register B The contents of register E are transferred to register B The contents of register E are transferred to register A and register B The contents of register Y are transferred to register A and register B The contents of register Y are transferred to register Y and the mediate field value y is loaded into register Y The contents of register Y are incremented by 1 As a result, if the contents of register Y are "0", the next instruction skipped  The contents of register Y are decremented by 1 As a result, if the contents of register Y are "15", the next matruction skipped  The contents of register Y are decremented by 1 As a result, if the contents of register Y are "15", the next matruction skipped  After exchanging the contents of M(DP) to register A an exclusive logical OR is performed between register X and the mediate field value y, and the result is stored into register X Alter exchanging the contents of M(DP) to register A an exclusive logical OR is performed between register X and the mediate field value y and the result is stored into register X Alter exchanging the contents of M(DP) to register A an exclusive logical OR is performed between register X and the mediate field value is and the result is stored into register X Alter exchanging the contents of M(DP) to register A an exclusive logical OR is performed between register X and the mediate field value is and the result is stored into register X Alter exchanging the contents of M(DP) to registe | Skip conditions         | Carry    | Detailed description                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------|

| The contents of register Y are transferred to register A The contents of register A and register B are transferred to register E The contents of register A and register B are transferred to register B The contents of register E are transferred to register D The contents of register E are transferred to register B The contents of register E are transferred to register B The contents of register E are transferred to register B The contents of register E are transferred to register A and register B The contents of register E are transferred to register A and register B The contents of register E are transferred to register A and register B The contents of register Y are incremented by 1 As a result, if the contents of register Y are "0", the next instruction skipped The contents of register Y are incremented by 1 As a result, if the contents of register Y are "0", the next instruction skipped The contents of register Y are decremented by 1 As a result, if the contents of register Y are "15", the next instruction skipped  After transferring the contents of MI(DP) to register A, an exclusive logical OR is performed between register X and the mediate field value j, and the result is stored into register X.  After exchanging the contents of MI(DP) to register A, an exclusive logical OR is performed between register X and the mediate field value j, and the result is stored into register X.  After exchanging the contents of MI(DP) to register A, an exclusive logical OR is performed between register X and the mediate field value j, and the result is stored into register X.  After exchanging the contents of MI(DP) to register A, an exclusive logical OR is performed between register X and the mediate field value j, and the result is stored into register X.  After exchanging the contents of MI(DP) to register A, an exclusive logical OR is performed between register X and the mediate field value j, and the result is stored into register X.  After exchanging the contents of register Y is incremented by 1 and the result is "0" | _                       | _        | The contents of register B are transferred to register A                                                                    |