September 1999

# COP87L88EB/RB Family 8-Bit CMOS OTP Microcontrollers with 16k or 32k Memory, CAN Interface, 8-Bit A/D, and USART

## **General Description**

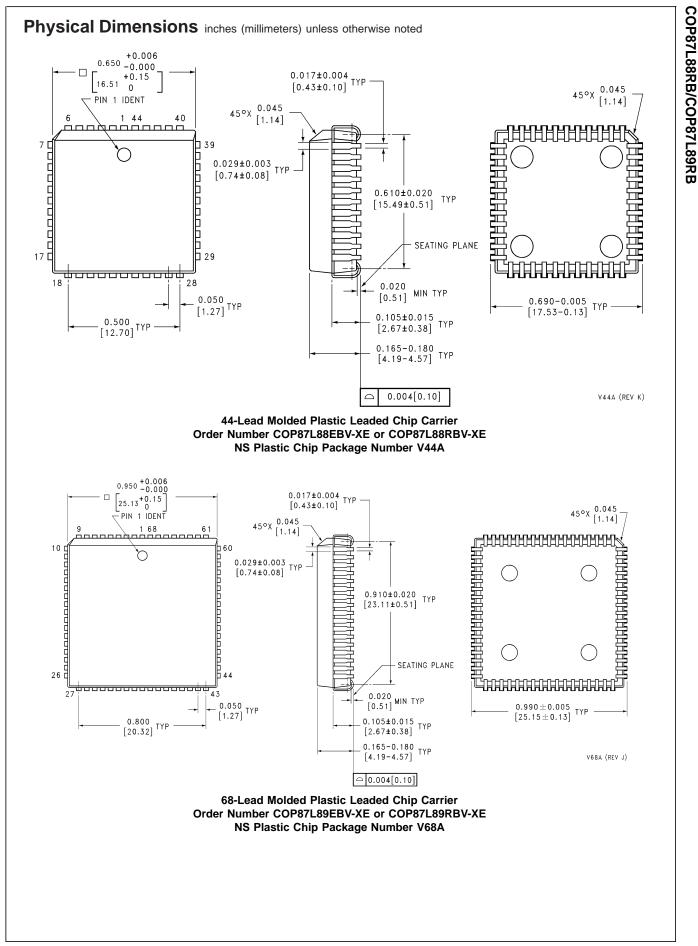

The COP87L88EB/RB Family OTP (One Time programmable) microcontrollers are highly integrated COP8<sup>™</sup> Feature core devices with 16k or 32k memory and advanced features including a CAN 2.0B (passive) interface, A/D and USART. These multi-chip CMOS devices are suited for applications requiring a full featured controller with a CAN interface, low EMI, and versatile communications interfaces, and as pre-production devices for ROM designs. Pin and software compatible 8k ROM versions (COP888EB) are available as well as a range of COP8 software and hardware development tools. Features include an 8-bit memory mapped architecture, 10 MHz CKI (-XE = crystal oscillator) with 1µs instruction cycle, two multi-function 16-bit timer/counters, WATCHDOG and clock monitor, idle timer, CAN 2.0B (passive) interface, MICROWIRE/PLUS<sup>™</sup> serial I/O, SPI master/slave interface, fully buffered USART, 8 bit A/D with 8 channels, two power saving HALT/IDLE modes, MIWU, software selectable I/O options, low EMI 4.5V to 5.5V operation, program code security, and 44/68 pin packages.

**Note:** A companion device with CAN interface, less I/O and memory, A/D, and PWM timer is the COP87L84BC. Devices included in this datasheet are:

Devices included in this datasheet are.

| Device     | Memory (bytes) | RAM (bytes) | I/O Pins | Packages | Temperature  |

|------------|----------------|-------------|----------|----------|--------------|

| COP87L88EB | 16k OTP EPROM  | 192         | 35       | 44 PLCC  | -40 to +85°C |

| COP87L89EB | 16k OTP EPROM  | 192         | 58       | 68 PLCC  | -40 to +85°C |

| COP87L88RB | 32k OTP EPROM  | 192         | 35       | 44 PLCC  | -40 to +85°C |

| COP87L89RB | 32k OTP EPROM  | 192         | 58       | 68 PLCC  | -40 to +85°C |

## **Key Features**

- CAN 2.0B (passive) bus interface, with Software Power save mode

- 8-bit A/D Converter with 8 channels

- Fully buffered USART

- Multi-input wake up (MIWU) on both Port L and M

- SPI Compatible Master/Slave Interface

- 16 or 32 kbytes of on-board OTP EPROM with security feature

Note: Mask ROMed device with equivalent on-chip features and program memory size of 8k is available.

192 bytes of on-board RAM

# **Additional Peripheral Features**

- Idle timer (programmable)

- Two 16-bit timer, with two 16-bit registers supporting

- Processor independent PWM mode

- External Event counter mode

- Input capture mode

- WATCHDOG<sup>™</sup> and Clock Monitor

- MICROWIRE/PLUS serial I/O

## **I/O Features**

- Software selectable I/O options (TRI-STATE<sup>®</sup> outputs, Push pull outputs, Weak pull up input, High impedance input)

- Schmitt trigger inputs on Port G, L and M

iceMASTER® is a registered trademark of MetaLink Corporation.

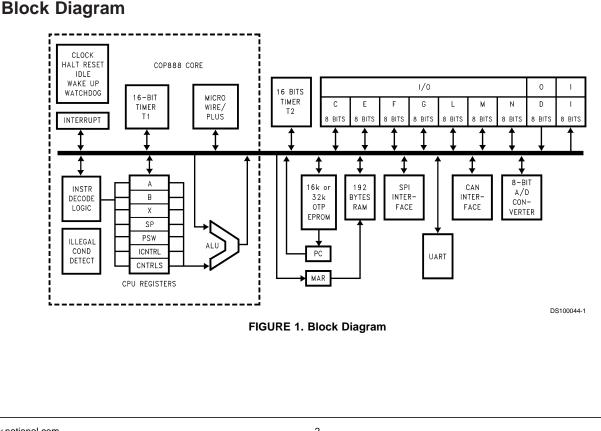

Packages: 44 PLCC with 35 I/O pins;

68 PLCC with 58 I/O pins

## **CPU/Instruction Set Features**

- 1 µs instruction cycle time

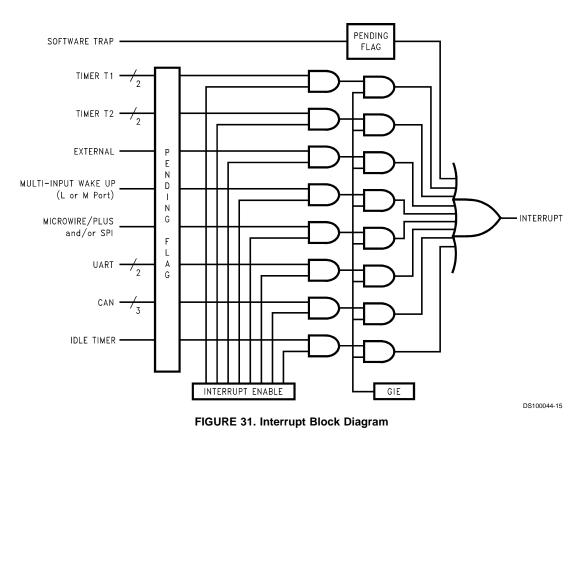

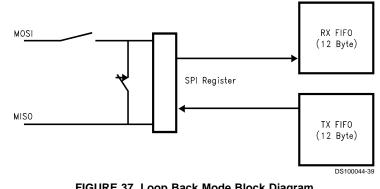

- Fourteen multi-sourced vectored interrupts servicing — External interrupt

- Idle Timer T0

- Timers (T1 and T2) (4 Interrupts)

- MICROWIRE/PLUS and SPI

- Multi-input Wake up

- Software Trap

- CAN interface (3 interrupts)

- USART (2 Inputs)

- Versatile easy to use instruction set

- 8-bit stacker pointer (SP) (Stack in RAM)

- Two 8-bit RegisterR Indirect Memory Pointers (B, X)

# **Fully Static CMOS**

- Two power saving modes: HALT, IDLE

- Single supply operation: 4.5V to 5.5V

- Temperature range: -40°C to +85°C

# **Development Support**

- Emulation device for COP888EB

- Real time emulation and full program debug offered by MetaLink Development System

© 2000 National Semiconductor Corporation DS100044

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

COP8™, MICROWIRE/PLUS™, WATCHDOG™ and MICROWIRE™ are trademarks of National Semiconductor Corporation.

Downloaded from Elcodis.com electronic components distributor

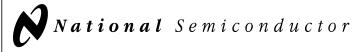

## **Basic Functional Description**

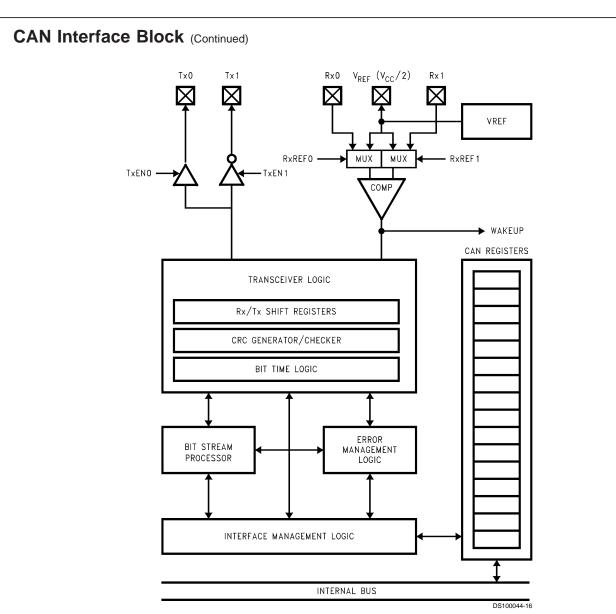

- CAN I/F—CAN serial bus interface block as described

- in the CAN specification part 2.0B (Passive)

Interface rates up to 250k bit/s are supported utilizing standard message identifiers

- Programmable double buffered USART

- A/D—8-bit, 8 channel, 1-LSB Resolution, with improved Source Impedance and improved channel to channel cross talk immunity

- Multi-Input-Wake-Up (MIWU)—edge selectable wake-up and interrupt capability via input port and CAN interface (Port L, Port M and CAN I/F); supports Wake-Up capability on SPI, USART, and T2

- Port C—8-bit bi-directional I/O port

- Port D—8-bit Output port with high current drive capability (10 mA)

- Port F—8-bit bidirectional I/O

- Port G—8-bit bidirectional I/O port, including alternate functions for:

- MICROWIRE<sup>™</sup> Input and Output

- Timer 1 Input or Output (Depending on mode selected)

- External Interrupt input

- WATCHDOG Output

- Port I—8-bit input port combining either digital input, or up to eight A/D input channels

- Port L—8-bit bidirectional I/O port, including alternate functions for:

- USART Transmit/Receive I/O

- Multi-input-wake up (MIWU on all pins)

- Port M—8-bit I/O port, with the following alternate function

- SPI Interface

- MIWU

- CAN Interface Wake-up (MSB)

- Timer 2 Input or Output (Depending on mode selected)

- Port N—8-bit bidirectional I/O

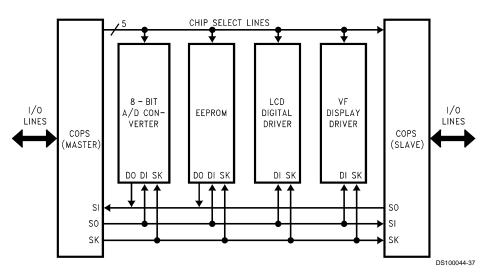

SPI Slave Select Expander

- Two 16-bit multi-function Timer counters (T1 and T2) plus supporting registers

- (I/P Capture, PWM and Event Counting)

- Idle timer—Provides a basic time-base counter, (with interrupt) and automatic wake up from IDLE mode programmable

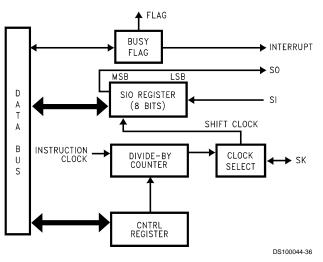

- MICROWIRE/PLUS—MICROWIRE serial peripheral interface, supporting both Master and Slave operation

- HALT and IDLE—Software programmable low current modes

- HALT Processor stopped, Minimum current

- IDLE Processor semi-active more than 60% power saving

- 16 or 32 kbytes OTP EPROM and 192 bytes of on board static RAM

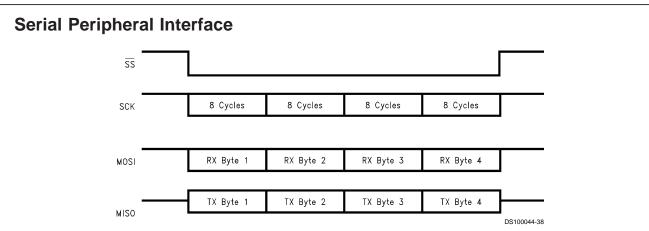

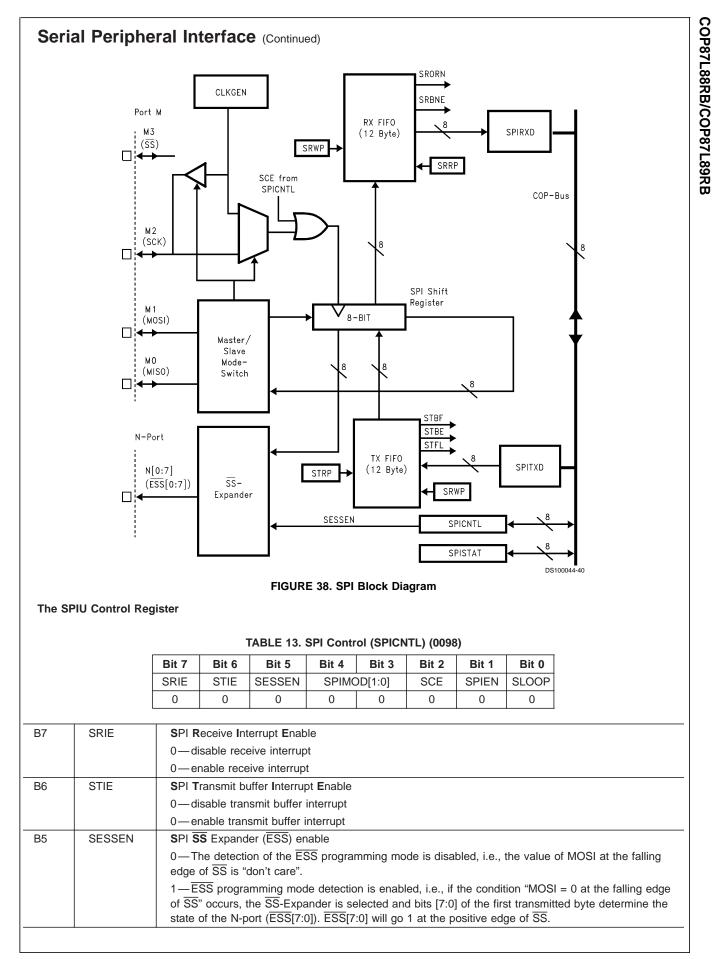

- SPI Master/Slave interface includes 12 bytes Transmit and 12 bytes Receive FIFO Buffers. Operates up to 1M Bit/S

- On board programmable WATCHDOG and CLOCK Monitor

# **Applications**

- Automobile Body Control and Comfort System

- Integrated Driver Information Systems

- Steering Wheel Control

- Car Radio Control Panel

- Sensor/Actuator Applications in Automotive and Industrial Control

| Port | Туре | ALT       | 44-Pin | 68-Pin |

|------|------|-----------|--------|--------|

| Pin  |      | Function  | PLCC   | PLCC   |

| G0   | I/O  | INT       | 44     | 1      |

| G1   | I/O  | WDOUT     | 1      | 2      |

| G2   | I/O  | T1B       | 2      | 3      |

| G3   | I/O  | T1A       | 3      | 4      |

| G4   | I/O  | SO        | 4      | 5      |

| G5   | I/O  | SK        | 5      | 6      |

| G6   | I    | SI        | 6      | 7      |

| G7   | I    | СКО       | 7      | 8      |

| D0   | 0    |           | 17     | 27     |

| D1   | 0    |           | 18     | 28     |

| D2   | 0    |           | 19     | 29     |

| D3   | 0    |           | 20     | 30     |

| D4   | 0    |           |        | 31     |

| D5   | 0    |           |        | 32     |

| D6   | 0    |           |        | 33     |

| D7   | 0    |           |        | 34     |

| 10   | I    | ADCH0     | 36     | 53     |

| 11   | I    | ADCH1     | 37     | 54     |

| 12   | I    | ADCH2     | 38     | 55     |

| 13   | I    | ADCH3     | 39     | 56     |

| 14   | I    | ADCH4     |        | 57     |

| 15   | I    | ADCH5     |        | 58     |

| 16   | I    | ADCH6     |        | 59     |

| 17   | I    | ADCH7     |        | 60     |

| L0   | I/O  | MIWU      | 40     | 61     |

| L1   | I/O  | MIWU;CKX  | 41     | 62     |

| L2   | I/O  | MIWU;TDX  | 42     | 63     |

| L3   | I/O  | MIWU;RDX  | 43     | 64     |

| L4   | I/O  | MIWU      |        | 65     |

| L5   | I/O  | MIWU      |        | 66     |

| L6   | I/O  | MIWU      |        | 67     |

| L7   | I/O  | MIWU      |        | 68     |

| M0   | I/O  | MIWU;MISO | 21     | 38     |

| M1   | I/O  | MIWU;MOSI | 22     | 39     |

| M2   | I/O  | MIWU;SCK  | 23     | 40     |

| M3   | I/O  | MIWU;SS   | 24     | 41     |

| M4   | I/O  | MIWU;T2A  | 25     | 42     |

| M5   | I/O  | MIWU;T2B  | 26     | 43     |

| M6   | I/O  | MIWU      | 27     | 44     |

| N0   | I/O  | ESS0      | 12     | 18     |

| N14  | 1/0  | F004      | 10     | 10     |

ESS1

ESS2

ESS3

ESS4

ESS5

ESS6 ESS7 13

14

15

19

20

21

22

23

24

25

I/O

I/O

I/O

I/O

I/O

I/O

I/O

| Port             | Туре | ALT      | 44-Pin    | 68-Pin        |

|------------------|------|----------|-----------|---------------|

| Pin              |      | Function | PLCC      | PLCC          |

| F0               | I/O  |          |           | 10            |

| F1               | I/O  |          |           | 11            |

| F2               | I/O  |          |           | 12            |

| F3               | I/O  |          |           | 13            |

| F4               | I/O  |          |           | 14            |

| C0               | I/O  |          |           | 35            |

| C1               | I/O  |          |           | 36            |

| C2               | I/O  |          |           | 37            |

| RX0              | Ι    |          | 31        | 48            |

| RX1              | Ι    |          | 30        | 47            |

| TX0              | 0    |          | 29        | 46            |

| TX1              | 0    |          | 28        | 45            |

| $CANV_{REF}$     |      |          | 32        | 49            |

| CKI              |      |          | 8         | 9             |

| RESET            |      |          | 16        | 26            |

| DV <sub>CC</sub> |      |          | 10, 33    | 16, 50        |

| GND              |      |          | 9, 11, 34 | 15, 17,<br>51 |

| A/D              |      |          | 35        | 52            |

| V <sub>REF</sub> |      |          |           |               |

www.national.com

N1

N2

N3

N4

N5

N6

N7

## Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage (V<sub>CC</sub>) Voltage at Any Pin

$$\rm 6V$$  –0.3V to V\_{CC} +0.3V

Total Current into  $V_{CC}$  Pins (Source)

Total Current out of GND Pins (Sink)

when operating the device at absolute maximum ratings.

Note 1: Absolute maximum ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications are not ensured

Storage Temperature Range

# **DC Electrical Characteristics**

$-40^{\circ}C \leq T_A \leq +85^{\circ}C$

| Parameter                                         | Conditions                                 | Min                | Тур                 | Max              | Units |

|---------------------------------------------------|--------------------------------------------|--------------------|---------------------|------------------|-------|

| Operating Voltage                                 |                                            | 4.5                |                     | 5.5              | V     |

| Power Supply Ripple (Note 2)                      | Peak-to-Peak                               |                    |                     | $0.1 V_{\rm CC}$ | V     |

| Supply Current                                    | $V_{\rm CC}$ = 5.5V, t <sub>c</sub> = 1 µs |                    |                     | 16               | mA    |

| CKI = 10 MHz (Note 3)                             |                                            |                    |                     |                  |       |

| HALT Current (Notes 4, 5)                         | $V_{CC} = 5.5V, CKI = 0 MHz$               |                    | < 1                 |                  | μA    |

| IDLE Current (Note 5)                             | $V_{\rm CC}$ = 5.5V, t <sub>c</sub> = 1 µs |                    |                     | 5.5              | mA    |

| CKI = 10 MHz                                      |                                            |                    |                     |                  |       |

| Input Levels (V <sub>IH</sub> , V <sub>IL</sub> ) |                                            |                    |                     |                  |       |

| Reset, CKI                                        |                                            |                    |                     |                  |       |

| Logic High                                        |                                            | 0.8V <sub>CC</sub> |                     |                  | V     |

| Logic Low                                         |                                            |                    |                     | $0.2V_{CC}$      | V     |

| All Other Inputs                                  |                                            |                    |                     |                  |       |

| Logic High                                        |                                            | 0.7V <sub>CC</sub> |                     |                  | V     |

| Logic Low                                         |                                            |                    |                     | $0.2V_{CC}$      | V     |

| Hi-Z Input Leakage                                | $V_{\rm CC} = 5.5 V$                       |                    |                     | ±2               | μA    |

| Input Pull-Up Current                             | $V_{\rm CC} = 5.5 V, V_{\rm IN} = 0 V$     | -40                |                     | -250             | μA    |

| Port G, L and M Input Hysteresis                  | (Note 8)                                   |                    | 0.05V <sub>CC</sub> |                  | V     |

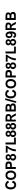

| Output Current Levels                             |                                            |                    |                     |                  |       |

| D Outputs                                         |                                            |                    |                     |                  |       |

| Source                                            | $V_{CC} = 4.5V, V_{OH} = 3.3V$             | -0.4               |                     |                  | mA    |

| Sink                                              | $V_{CC} = 4.5V, V_{OL} = 1.0V$             | 10                 |                     |                  | mA    |

| CAN Transmitter Outputs                           |                                            |                    |                     |                  |       |

| Source (Tx1)                                      | $V_{CC} = 4.5V, V_{OH} = V_{CC} - 0.1V$    | -1.5               |                     |                  | mA    |

|                                                   | $V_{CC} = 4.5V, V_{OH} = V_{CC} - 0.6V$    | -10                |                     | +5.0             | mA    |

| Sink (Tx0)                                        | $V_{CC} = 4.5V, V_{OL} = 0.1V$             | 1.5                |                     |                  | mA    |

|                                                   | $V_{CC} = 4.5V, V_{OL} = 0.6V$             | 10                 |                     |                  | mA    |

| All Others                                        |                                            |                    |                     |                  |       |

| Source (Weak Pull-Up)                             | $V_{CC} = 4.5V, V_{OH} = 2.7V$             | -10                |                     | -110             | μA    |

| Source (Push-Pull)                                | $V_{CC} = 4.5V, V_{OH} = 3.3V$             | -0.4               |                     |                  | mA    |

| Sink (Push-Pull)                                  | $V_{CC} = 4.5V, V_{OL} = 0.4V$             | 1.6                |                     |                  | mA    |

| TRI-STATE Leakage                                 | $V_{\rm CC} = 5.5V$                        |                    |                     | ±2.0             | μA    |

| Allowable Sink/Source Current per Pin             |                                            |                    |                     |                  | r     |

| D Outputs (sink)                                  |                                            |                    |                     | 15               | mA    |

| Tx0 (Sink) (Note 8)                               |                                            |                    |                     | 30               | mA    |

| Tx1 (Source) (Note 8)                             |                                            |                    |                     | 30               | mA    |

| All Other                                         |                                            |                    |                     | 3                | mA    |

| Maximum Input Current                             | Room Temp                                  |                    |                     | ±200             | mA    |

| without Latchup (Notes 6, 8)                      |                                            |                    |                     | 200              |       |

| RAM Retention Voltage, $V_r$ (Note 7)             | 500 ns Rise and Fall Time                  | 2.0                |                     |                  | V     |

| Input Capacitance                                 | (Note 8)                                   |                    |                     | 7                | pF    |

| Load Capacitance on D2                            | ()                                         |                    |                     | 1000             | pF    |

90 mA

100 mA

-65°C to +150°C

### DC Electrical Characteristics (Continued)

Note 3: Supply current is measured after running 2000 cycles with a square wave CKI input, CKO open, inputs at V<sub>CC</sub> or GND, and outputs open.

Note 4: The HALT mode will stop CKI from oscillating in the Crystal configurations. Halt test conditions: All inputs tied to V<sub>CC</sub>; Port C, G, E, F, L, M and N I/Os configured as outputs and programmed low; D outputs programmed high. Parameter refers to HALT mode entered via setting bit 7 of the Port G data register. Part will pull up CKI during HALT in crystal clock mode. Both CAN main comparator and the CAN Wakeup comparator need to be disabled.

Note 5: . HALT and IDLE current specifications assume CAN block comparators are disabled.

**Note 6:** Pins G6 and  $\overrightarrow{\text{RESET}}$  are designed with a high voltage input network. These pins allow input voltages greater than V<sub>CC</sub> and the pins will have sink current to V<sub>CC</sub> when biased at voltages greater than V<sub>CC</sub> (the pins do not have source current when biased at a voltage below V<sub>CC</sub>). The effective resistance to V<sub>CC</sub> is 750 $\Omega$  (typical). These two pins will not latch up. The voltage at the pins must be limited to less than 14V.

**Note 7:** Condition and parameter valid only for part in HALT mode.

Note 8: Parameter characterized but not tested.

# **AC Electrical Characteristics**

$-40^{\circ}C \le T_A \le +85^{\circ}C$

| Parameter                                                   | Conditions                                            | Min | Тур | Max | Units          |

|-------------------------------------------------------------|-------------------------------------------------------|-----|-----|-----|----------------|

| Instruction Cycle Time (t <sub>c</sub> )                    |                                                       |     |     |     |                |

| Crystal/Resonator                                           | $V_{CC} \ge 4.5V$                                     | 1.0 |     | DC  | μs             |

| Inputs                                                      |                                                       |     |     |     |                |

| t <sub>setup</sub>                                          | $V_{CC} \ge 4.5V$                                     | 200 |     |     | ns             |

| t <sub>HOLD</sub>                                           | $V_{CC} \ge 4.5V$                                     | 60  |     |     | ns             |

| Output Propagation Delay ( $t_{PD1}$ , $t_{PD0}$ ) (Note 9) | $C_{L} = 100 \text{ pF}, R_{L} = 2.2 \text{ k}\Omega$ |     |     |     |                |

| SK, SO                                                      | $V_{CC} \ge 4.5V$                                     |     |     | 0.7 | μs             |

| All others                                                  | $V_{CC} \ge 4.5V$                                     |     |     | 1   | μs             |

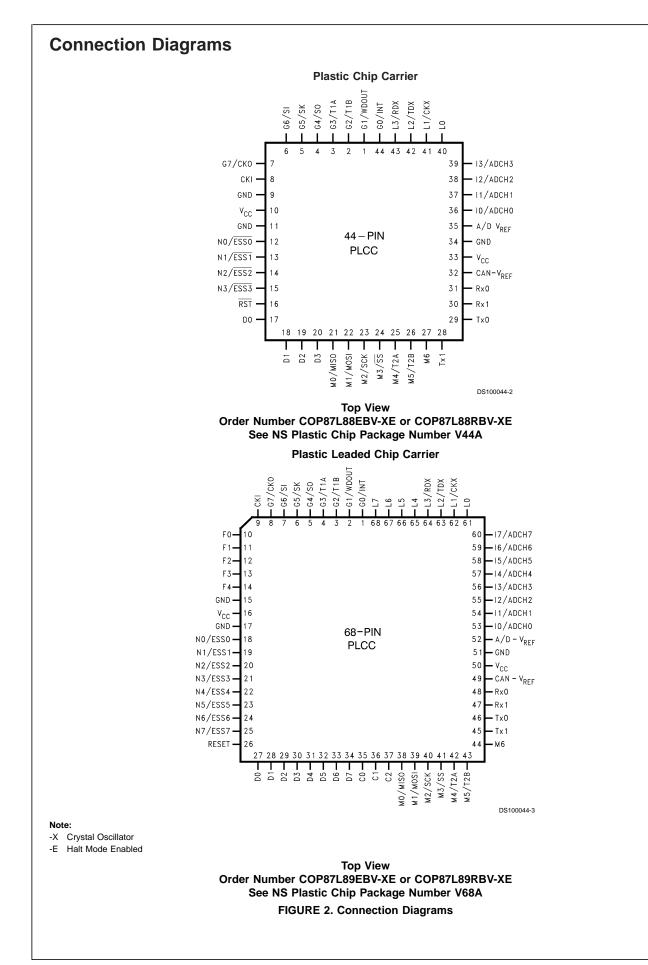

| MICROWIRE                                                   |                                                       |     |     |     |                |

| Setup Time (tUWS) (Note 10)                                 |                                                       | 20  |     |     | ns             |

| Hold Time (tUWH) (Note 10)                                  |                                                       | 56  |     |     | ns             |

| Output Pop Delay (tUPD)                                     |                                                       |     |     | 220 | ns             |

| Input Pulse Width                                           |                                                       |     |     |     |                |

| Interrupt High Time                                         |                                                       | 1   |     |     | t <sub>c</sub> |

| Interrupt Low Time                                          |                                                       | 1   |     |     | t <sub>c</sub> |

| Timer 1, 2 High Time                                        |                                                       | 1   |     |     | t <sub>c</sub> |

| Timer 1, 2 Low Time                                         |                                                       | 1   |     |     | t <sub>c</sub> |

| Reset Pulse Width (Note 10)                                 |                                                       | 1.0 |     |     | μs             |

t<sub>c</sub> = Instruction Cycle Time

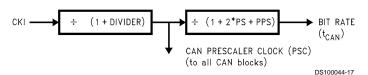

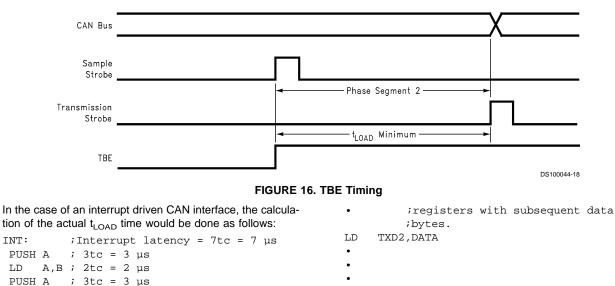

The maximum bus speed achievable with the CAN interface is a function of crystal frequency, message length and software overhead. The device can support a bus speed of up to 1 Mbit/S with a 10 MHz oscillator and 2 byte messages. The 1M bus speed refers to the rate at which protocol and data bits are transferred on the bus. Longer messages require slower bus speeds due to the time required for software intervention between data bytes. The device will support a maximum of 125k bits/s with eight byte messages and a 10 MHz oscillator.

For device testing purpose of all AC parameters,  $V_{\text{OH}}$  will be tested at 0.5\*V\_{CC}.

Note 9: The output propagation delay is referenced to the end of the instruction cycle where the output change occurs.

Note 10: Parameter not tested.

# **On-Chip Voltage Reference**

$-40^{\circ}C \le T_A \le +85^{\circ}C$

| Parameter                | Conditions                       | Min                      | Max                      | Units |

|--------------------------|----------------------------------|--------------------------|--------------------------|-------|

| Reference Voltage        | Ι <sub>ΟUT</sub> < 80 μΑ,        | 0.5V <sub>CC</sub> -0.12 | 0.5V <sub>CC</sub> +0.12 | V     |

| V <sub>REF</sub>         | $V_{CC} = 5V$                    |                          |                          |       |

| Reference Supply         | I <sub>OUT</sub> = 0A, (No Load) |                          | 120                      | μA    |

| Current, I <sub>DD</sub> | $V_{\rm CC} = 5V$ (Note 11)      |                          |                          |       |

Note 11: Reference supply I<sub>DD</sub> is supplied for information purposes only, it is not tested.

# CAN Comparator DC and AC Characteristics $4.8V \le V_{CC} \le 5.2V, \ -40^\circ C \le T_A \le +85^\circ C$

| Parameter                  | Conditions                          | Min | Тур | Max                  | Units |

|----------------------------|-------------------------------------|-----|-----|----------------------|-------|

| Differential Input Voltage |                                     |     |     | ±25                  | mV    |

| Input Offset Voltage       | $1.5V \le V_{IN} \le V_{CC} - 1.5V$ |     |     | ±10                  | mV    |

| Input Common Mode          |                                     | 1.5 |     | V <sub>CC</sub> –1.5 | V     |

| Voltage Range              |                                     |     |     |                      |       |

| Input Hysteresis           |                                     | 8   |     |                      | mV    |

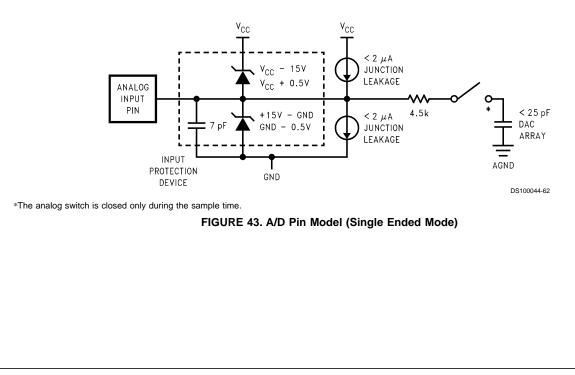

# **A/D Converter Specifications**

$(4.5V \le V_{CC} \le 5.5V) (V_{SS} - 0.050V) \le Any Input \le (V_{CC} + 0.050V)$

| Parameter                                            | Conditions         | Min | Тур | Max             | Units            |

|------------------------------------------------------|--------------------|-----|-----|-----------------|------------------|

| Resolution                                           |                    |     |     | 8               | Bits             |

| Absolute Accuracy                                    | $V_{REF} = V_{CC}$ |     |     | ±2              | LSB              |

| Non-Linearity                                        |                    |     |     | ±1              | LSB              |

| Deviation from the Best Straight Line                |                    |     |     |                 |                  |

| Differential Non-Linearity                           |                    |     |     | ±1              | LSB              |

| Common Mode Input Range (Note 14)                    |                    | GND |     | V <sub>cc</sub> | V                |

| DC Common Mode Error                                 |                    |     |     | ±0.5            | LSB              |

| Off Channel Leakage Current                          |                    |     | 1   | 2.0             | μA               |

| On Channel Leakage Current                           |                    |     | 1   | 2.0             | μA               |

| A/D Clock Frequency (Note 13)                        |                    | 0.1 |     | 1.67            | MHz              |

| Conversion Time (Note 12)                            |                    |     | 17  |                 | A/D Clock Cycles |

| Internal Reference Resistance Turn-On Time (Note 15) |                    |     |     | 1               | μs               |

Note 12: Conversion Time includes sample and hold time.

Note 13: See Prescaler description.

Note 14: For V<sub>IN</sub>(-) = V<sub>IN</sub>(+) the digital output code will be 0000 0000. Two on-chip doides are ties to each analog input. The diodes will forward conduct for analog input voltages below ground or above the V<sub>CC</sub> supply. Be careful, during testing at low V<sub>CC</sub> levels (4.5V), as high level analog inputs (5V) can cause this input diode to conduct - especially at elevated temperatures, and cause errors for analog inputs near full-scale. The spec allows 50 mV forward bias of either diode. This means that as long as the analog V<sub>IN</sub> does not exceed the supply voltage by more than 50 mV, the output code will be correct. To achieve an absolute 0 V<sub>DC</sub> to 5 V<sub>DC</sub> input voltage range will therefore require a minimum supply voltage of 4.950 V<sub>DC</sub> over temperature variations, initial tolerance and loading.

Note 15: Time for internal reference resistance to turn on after coming out of Halt or Idle Mode.

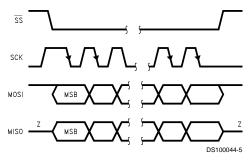

FIGURE 3. MICROWIRE/PLUS Timing Diagram

FIGURE 4. SPI Timing Diagram

# **Pin Description**

$V_{\text{CC}}$  and GND are the power supply pins.

CKI is the clock input. The clock can come from a crystal oscillator (in conjunction with CKO). See Oscillator Description section.

RESET is the master reset input. See Reset Description section.

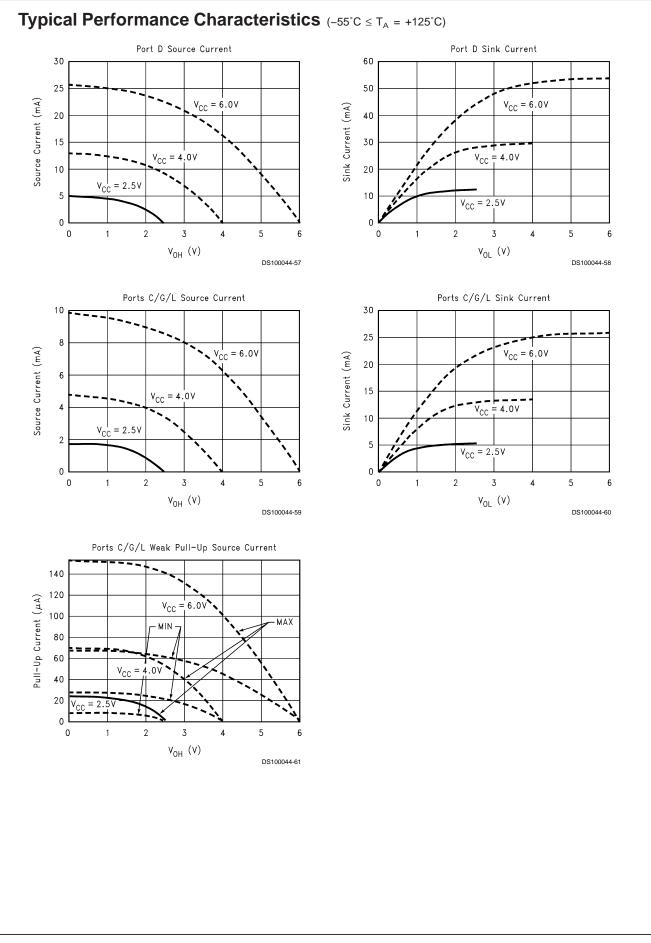

The device contains seven bidirectional 8-bit I/O ports (C, E, F, G, L, M, N) where each individual bit may be independently configured as an input (Schmitt trigger inputs on all ports), output or TRI-STATE under program control. Three data memory address locations are allocated for each of these I/O ports. Each I/O port has two associated 8-bit memory mapped registers, the CONFIGURATION register and the output DATA register. A memory mapped address is also reserved for the input pins of each I/O port. (See the memory map for the various addresses associated with the I/O ports.) *Figure 5* shows the I/O port configurations for the device. The DATA and CONFIGURATION registers allow for each port bit to be individually configured under software control as shown below:

| Configuration | Data     | Port Set-Up             |

|---------------|----------|-------------------------|

| Register      | Register |                         |

| 0             | 0        | Hi-Z Input              |

|               |          | (TRI-STATE Output)      |

| 0             | 1        | Input with Weak Pull-Up |

| 1             | 0        | Push-Pull Zero Output   |

| 1             | 1        | Push-Pull One Output    |

Port L and M are 8-bit I/O ports, they support Multi-Input Wake-up (MIWU) on all eight pins. All L-pins and M-pins have Schmitt triggers on the inputs.

Port L and M only have one (1) interrupt vector.

#### FIGURE 5. I/O Port Configurations

Port L has the following alternate features:

- L7 MIWU

- L6 MIWU

- L5 MIWU

- L4 MIWU

- L3 MIWU or RDX

- L2 MIWU or TDX

- L1 MIWU or CKX

- L0 MIWU

Port G is an 8-bit port with 5 I/O pins (G0–G5), an input pin (G6), and one dedicated output pin (G7). Pins G0–G6 all have Schmitt Triggers on their inputs. G7 serves as the dedicated output pin for the CKO clock output. There are two registers associated with the G Port, a data register and a configuration register. Therefore, each of the 6 I/O bits (G0–G5) can be individually configured under software control.

Since G6 is an input only pin and G7 is the dedicated CKO clock output pin the associated bits in the data and configuration registers for G6 and G7 are used for special purpose functions as outlined below. Reading the G6 and G7 data bits will return zeroes.

Note that the chip will be placed in the HALT mode by wirting a "1" to bit 7 of the Port G Data Register. Similarly the chip will be placed in the IDLE mode by writing a "1" to bit 6 of the Port G Data Register.

Writing a "1" to bit 6 of the Port G Configuration Register enables the MICROWIRE/PLUS to operate with the alternate phase of the SK clock

|    | Config. Reg. | Data Reg. |

|----|--------------|-----------|

| G7 | CLKDLY       | HALT      |

| G6 | Alternate SK | IDLE      |

Port G has the following alternate features:

- G6 SI (MICROWIRE Serial Data Input)

- G5 SK (MICROWIRE Serial Clock)

- G4 SO (MICROWIRE Serial Data Output)

- G3 T1A (Timer I/O)

- G2 (Timer T1 Capture Input)

- G1 Dedicated WATCHDOG output

- G0 INTR (External Interrupt Input)

Port G has the following dedicated function:

G7 CKO Oscillator dedicated output

Port M is a bidirectional I/O, it may be configured in software as Hi-Z input, weak pull-up, or push-pull output. These pins may be used as general purpose input/output pins or for selected altlernate functions.

Port M pins have optional alternate functions. Each pin (M0-M5) has been assigned an alternate data, configuration, or wakeup source. If the respective alternate function is selected the content of the associated bits in the configuration and/or data register are ignored. If an alternate wakeup source is selected the input level at the respective pin will be ignored for the purpose of triggering a wakeup event, however it will still be possible to read that pin by accessing the input register. The SPI (Serial Peripheral Interface) block, for example, uses four of the Port M pins to automatically reconfigure its MISO (Master Input, Slave Output), MOSI (Master Output, Slave Input), SCK (Serial Clock) and Slave-Select pins as inputs or outputs, depending on whether the interface has been configured as a Master or Slave. When the SPI interface is disabled those pins are available as general purpose I/O pins configurable by user software writing to the associated data and configuration bits. The CAN interface on the device makes use of one of the Port M's alternate wake-ups, to trigger a wakeup if such a condition has been detected on the CAN's dedicated receive pins.

Port M has the following alternate pin functions:

- M7 Multi-input Wakeup or CAN

- M6 Multi-input Wakeup

- M5 Multi-input Wakeup or T2B

#### Pin Description (Continued)

- M4 Multi-input Wakeup or T2A

- M3 Multi-input Wakeup or SS

- M2 Multi-input Wakeup or SCK

- M1 Multi-input Wakeup or MOSI

- M0 Multi-input Wakeup or MISO

Ports C, E, F and N are general-purpose, bidirectional I/O ports.

Any device package that has Port C, E, F, M, N but has fewer than eight pins, contains unbonded, floating pads internally on the chip. For these types of devices, the software should write a 1 to the configuration register bits corresponding to the non-existent port pins. This configures the port bits as outputs, thereby reducing leakage current of the device.

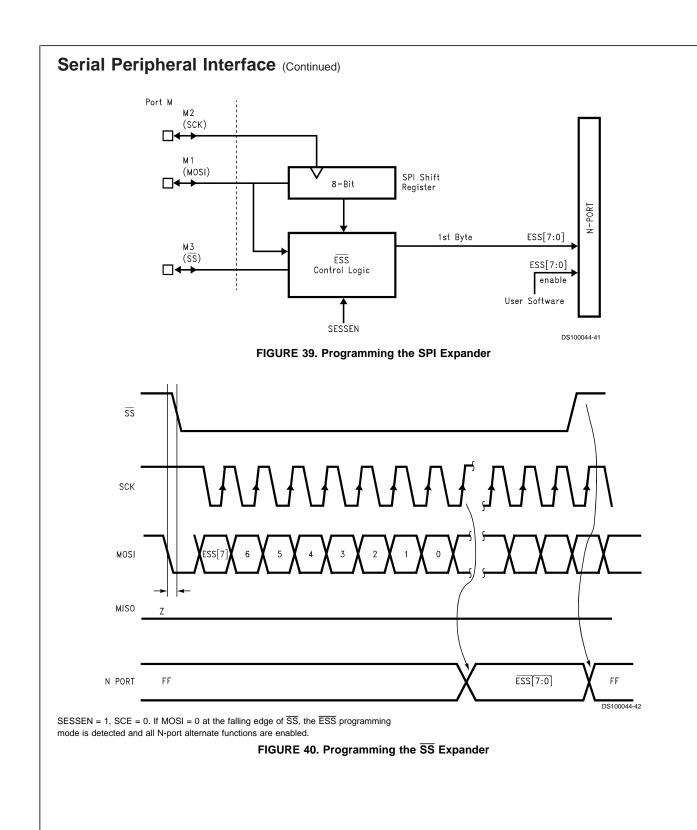

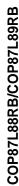

Port N is an 8-bit wide port with alternate function capability used for extending the slave select  $\overline{(SS)}$  lines of the on SPI interface. The SPI expander block provides mutually exclusive slave select extension signals (ESS0 to ESS7) according to the state of the  $\overline{SS}$  line and specific contents of the SPI shift register. These slave select extension lines can be routed to the Port N I/O pins by enabling the alternate function of the port in the PORTNX register. If enabled, the internal signal on the ESSx line causes the ports state to change exactly like a change to the PORTND register. It is the user's responsibility to switch the port to an output when enabling the alternate function.

Port N has the following alternate pin functions:

- N7 ESS7

- N6 ESS6

- N5 ESS5

- N4 ESS4

- N3 ESS3

- N2 ESS2

- N1 ESS1

- NO ESSO

CAN pins: For the on-chip CAN interface this device has five dedicated pins with the following features:

- $V_{\text{REF}}$   $\,$  On-chip reference voltage with the value of  $V_{\text{CC}}\!/\!2$

- Rx0 CAN receive data input pin.

- RX1 CAN receive data input pin.

- Tx0 CAN transmit data output pin. This pin may be put in the TRI-STATE mode with the TXEN0 bit in the CAN Bus control register.

- Tx1 CAN transmit data output pin. This pin may be put in the TRI-STATE mode with the TXEN1 bit in the CAN Bus control register.

#### ALTERNATE PORT FUNCTIONS

Many general-purpose pins have alternate functions. The software can program each pin to be used either for a general-purpose or for a specific function. The chip hardware determines which of the pins have alternate functions, and what those functions are. This section lists the alternate functions available on each of the pins.

Port D is an 8-bit output port that is preset high when RESET goes low. The user can tie two or more port D outputs (except D2) together in order to get a higher drive.

Note: Care must be exercised with D2 pin operation. At RESET, the external loads on this pin must ensure that the output voltages stay above 0.8  $V_{CC}$  to prevent the chip from entering special modes. Also keep the external loading on D2 to < 1000 pF.

www.national.com

Port I is an 8-bit Hi-Z input port, and also provides the analog inputs to the A/D converter. If unterminated, Port I pins will draw power only when addressed.

## **Functional Description**

The architecture of the device utilizes a modified Harvard architecture. With the Harvard architecture, the control store program memory (ROM) is separated from the data store memory (RAM). Both ROM and RAM have their own separate addressing space with separate address buses. The architecture, though based on Harvard architecture, permits transfer of data from ROM to RAM.

#### **CPU REGISTERS**

The CPU can do an 8-bit addition, subtraction, logical or shift operation in one instruction ( $t_c$ ) cycle time.

There are five CPU registers:

A is the 8-bit Accumulator Register

PC is the 15-bit Program Counter Register

PU is the upper 7 bits of the program counter (PC)

PL is the lower 8 bits of the program counter (PC)

B is an 8-bit RAM address pointer, which can be optionally post auto incremented or decremented.

X is an 8-bit alternate RAM address pointer, which can be optionally post auto incremented or decremented.

SP is the 8-bit stack pointer, which points to the subroutine/ interrupt stack (in RAM). The SP is initialized to RAM address 02F with reset.

All the CPU registers are memory mapped with the exception of the Accumulator (A) and the Program Counter (PC).

#### **PROGRAM MEMORY**

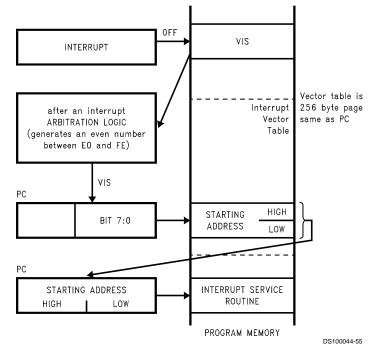

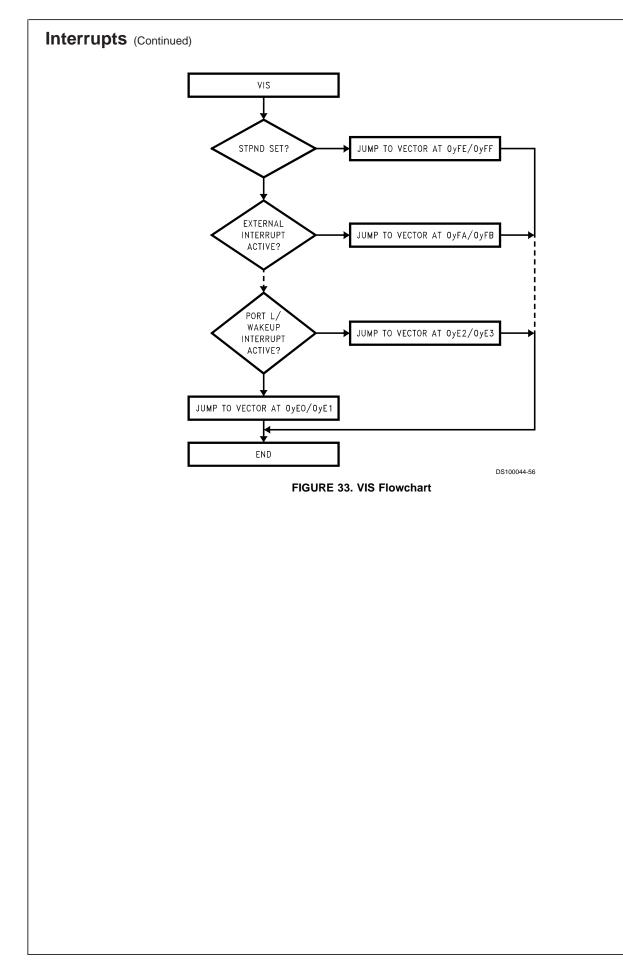

Program memory for the device consists of 8 or 32 kbytes of OTP EPROM. These bytes may hold program instructions or constant data (data tables for the LAID instruction, jump vectors for the JID instruction and interrupt vectors for the VIS instruction). The program memory is addressed by the 15-bit program counter (PC). All interrupts in the device vector to program memory location 0FF Hex.

The device can be configured to inhibit external reads of the program memory. This is done by programming the Security Byte.

#### SECURITY FEATURE

The program memory array has an associate Security Byte that is located outside of the program address range. This byte can be addressed only from programming mode by a programmer tool.

Security is an optional feature and can only be asserted after the memory array has been programmed and verified. A secured part will read all 00(hex) by a programmer. The part will fail Blank Check and will fail Verify operations. A Read operation will fill the programmer's memory with 00(hex). The Security byte itself is always readable with value of 00(hex) if unsecure and FF(hex) if secure.

#### DATA MEMORY

The data memory address space includes the on-chip RAM and data registers, the I/O registers (Configuration, Data and Pin), the control registers, the MICROWIRE/PLUS SIO shift register, and the various registers, and counters associated

# Functional Description (Continued)

with the timers (with the exception of the IDLE timer). Data memory is addressed directly by the instruction or indirectly by the B, X and SP pointers.

The device has 192 bytes of RAM. Sixteen bytes of RAM are mapped as "registers" at addresses 0F0 to 0FF Hex. These registers can be loaded immediately, and also decremented and tested with the DRSZ (decrement register and skip if zero) instruction. The memory pointer registers X, SP, and B are memory mapped into this space at address locations 0FC to 0FE Hex respectively, with the other registers (other than reserved register 0FF) being available for general usage.

The instruction set permits any bit in memory to be set, reset or tested. All I/O and registers (except A and PC) are memory mapped; therefore I/O bits and register bits can be directly and individually set, reset and tested. The accumulator (A) bits can also be directly and individually tested.

$\label{eq:Note: RAM contents are undefined upon power-up.}$

#### RESET

The RESET input when pulled low initializes the microcontroller. Initialization will occur whenever the RESET input is pulled low. Upon initialization, the data and configuration registers for Ports L and G, are cleared, resulting in these Ports being initialized to the TRI-STATE mode. Port D is initialized high with RESET. The PC, CNTRL, and INCTRL control registers are cleared. The Multi-Input Wakeup registers WKEN, WKEDG, and WKPND are cleared. The Stack Pointer, SP, is initialized to 06F Hex.

The following initializations occur with RESET:

SPI:

SPICNTRL: Cleared

SPISTAT: Cleared

STBE Bit: Set

T1CNTRL & T2CNTRL: Cleared

ITMR: Cleared and IDLE timer period is reset to 4k Instr. CLK

ENAD: Cleared

ADDSLT: Random

SIOR: Unaffected after RESET with power already applied.

Random after RESET at power on.

Port L: TRI-STATE

Port G: TRI-STATE

Port D: HIGH

PC: CLEARED

PSW, CNTRL and ICNTRL registers: CLEARED

Accumulator and Timer 1:

RANDOM after RESET with power already applied RANDOM after RESET at power-on

SP (Stack Pointer): Loaded with 6F Hex

B and X Pointers:

UNAFFECTED after RESET with power already applied RANDOM after RESET at power-up

RAM:

UNAFFECTED after RESET with power already applied

RANDOM after RESET at power-up

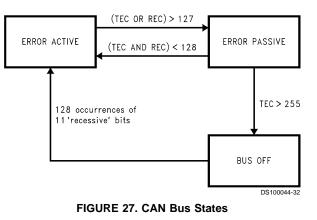

CAN: The CAN Interface comes out of external reset in the

"error-active" state and waits until the user's software sets either one or both of the TXEN0, TXEN1 bits to "1". After that, the device will not start transmission or reception of a frame util eleven consecutive "recessive" (undriven) bits have been received. This is done to ensure that the output drivers are not enamble during an active message on the bus.

CSCAL, CTIM, TCNTL, TEC, REC: CLEARED

RTSTAT: CLEARED with the exception of the TBE bit which is set to 1

RID, RIDL, TID, TDLC: RANDOM

WATCHDOG: The device comes out of reset with both the WATCHDOG logic and the Clock Monitor detector armed, with the WATCHDOG service window bits set and the Clock Monitor bit set. The WATCHDOG and Clock Monitor circuits are inhibited during reset. The WATCHDOG service window bits being initialized high default to the maximum WATCHDOG service window of 64k t<sub>o</sub> clock cycles. The Clock Monitor bit being initialized high will cause a Clock Monitor bit being initialized high will cause a Clock Monitor error following reset if the clock has not reached the minimum specified frequency at the termination of reset. A Clock Monitor error will cause an active low error output on pin G1. This error output will continue until 16 t<sub>c</sub>-32 t<sub>c</sub> clock cycles following the clock frequency reaching the minimum specified value, at which time the G1 output will enter the TRI-STATE mode.

The RESET signal goes directly to the HALT latch to restart a halted chip.

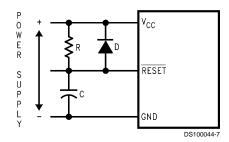

When using external reset, the external RC network shown in *Figure 6* should be used to ensure that the RESET pin is held low until the power supply to the chip stabilizes. Under no circumstances should the RESET pin be allowed to float.

RC 5 x Power Supply Rise Time

FIGURE 6. Recommended Reset Circuit

### **Oscillator Circuits**

The chip can be driven by a clock input on the CKI input pin which can be between DC and 10 MHz. The CKO output clock is on pin G7. The CKI input frequency is divided by 10 to produce the instruction cycle clock (1/ $t_c$ ).

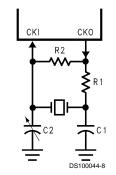

Figure 7 shows the Crystal diagram.

#### CRYSTAL OSCILLATOR

CKI and CKO can be connected to make a closed loop crystal (or resonator) controlled oscillator.

FIGURE 7. Crystal Oscillator Diagram

Table 1 shows the component values required for various standard crystal values.

| TABLE <sup>·</sup> | 1. Crvstal | Oscillator | Configuration,        | T <sub>∧</sub> = 25°C |

|--------------------|------------|------------|-----------------------|-----------------------|

|                    |            |            | ••••••••••••••••••••• | · A = =• •            |

| R1           | R2           | C1   | C2      | CKI Freq. | Conditions        |

|--------------|--------------|------|---------|-----------|-------------------|

| <b>(k</b> Ω) | <b>(M</b> Ω) | (pF) | (pF)    | (MHz)     |                   |

| 0            | 1            | 30   | 30–36   | 10        | $V_{\rm CC} = 5V$ |

| 0            | 1            | 30   | 30–36   | 4         | $V_{\rm CC} = 5V$ |

| 0            | 1            | 200  | 100–150 | 0.455     | $V_{CC} = 5V$     |

# **Control Registers**

#### CNTRL Register (Address X'00EE)

|         | 0        | •                                                                  |          | ,                   |          |           |        |  |

|---------|----------|--------------------------------------------------------------------|----------|---------------------|----------|-----------|--------|--|

| T1C3    | T1C2     | T1C1                                                               | T1C0     | MSEL                | IEDG     | SL1       | SL0    |  |

| Bit 7   |          |                                                                    |          |                     |          |           | Bit 0  |  |

| The Ti  | mer1 (T  | 1) and                                                             | MICRO    | WIRE/P              | LUS co   | ontrol re | gister |  |

| contain | s the fo | llowing l                                                          | bits:    |                     |          |           |        |  |

| T1C3    | 3        | Timer 7                                                            | T1 mode  | e contro            | l bit    |           |        |  |

| T1C2    | 2        | Timer 7                                                            | T1 mode  | e contro            | l bit    |           |        |  |

| T1C1    | l        | Timer 7                                                            | T1 mode  | e control           | l bit    |           |        |  |

| T1C0    | )        | Timer 7                                                            | T1 Start | Stop co             | ntrol in | timer     |        |  |

|         |          |                                                                    |          | 2, T1<br>n timer    |          | ow Inte   | errupt |  |

| MSEL    |          | Selects G5 and G4 as MICROWIRE/PLUS signals SK and SO respectively |          |                     |          |           |        |  |

| IEDG    | 6        | External interrupt edge polarity select                            |          |                     |          |           |        |  |

|         |          | (0 = Ri                                                            | sing edg | ge, 1 = F           | alling e | dge)      |        |  |

| SL1     | & SL0    |                                                                    |          | CROWIR<br>= 4, 1x : |          | Clock     | divide |  |

|         |          | 29 (00                                                             | , 01     | - , , , ,           | = 0,     |           |        |  |

|         |          |                                                                    |          |                     |          |           |        |  |

|         |          |                                                                    |          |                     |          |           |        |  |

|         |          |                                                                    |          |                     |          |           |        |  |

|         |          |                                                                    |          |                     |          |           |        |  |

#### PSW Register (Address X'00EF)

|       |      |            |                                                                                       | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |             |             |       |

|-------|------|------------|---------------------------------------------------------------------------------------|-----------------------------------------|-------------|-------------|-------|

| HC    | С    | T1PNDA     | T1ENA                                                                                 | EXPND                                   | BUSY        | EXEN        | GIE   |

| Bit 7 |      |            |                                                                                       |                                         |             |             | Bit 0 |

| The F | sw   | register c | ontains tl                                                                            | he followi                              | ng sele     | ct bits:    |       |

| HC    |      | Half Ca    | arry Flag                                                                             |                                         |             |             |       |

| С     |      | Carry F    | lag                                                                                   |                                         |             |             |       |

| T1F   | PND. | RA in I    | A Timer T1 Interrupt Pending<br>RA in mode 1, T1 Underflow<br>capture edge in mode 3) |                                         |             |             |       |

| T1E   | ENA  |            | Timer T1 Interrupt Enable for Timer Underflow or T1A Input capture edge               |                                         |             |             |       |

| EX    | PND  | Externa    | al interru                                                                            | ot pending                              | g           |             |       |

| BU    | SY   | MICRC      | OWIRE/PLUS busy shifting flag                                                         |                                         |             |             |       |

| EXE   | ΞN   | Enable     | Enable external interrupt                                                             |                                         |             |             |       |

| GIE   |      | Global     | interrupt                                                                             | enable (e                               | enables     | interrup    | ots)  |

| The L |      |            |                                                                                       | بيرط اممدهم                             | من مماد الم | at mustice. |       |

The Half-Carry flag is also affected by all the instructions that affect the Carry flag. The SC (Set Carry) and R/C (Reset Carry) instructions will respectively set or clear both the carry flags. In addition to the SC and R/C instructions, ADC, SUBC, RRC and RLC instructions affect the Carry and Half Carry flags.

#### ICNTRL Register (Address X'00E8)

| Reserved | LPEN | T0PND | T0EN | μWPND | μWEN | T1PNDB | T1ENB |

|----------|------|-------|------|-------|------|--------|-------|

| Bit 7    |      |       |      |       |      |        | Bit 0 |

The ICNTRL register contains the following bits:

Reserved This bit is reserved and should be zero

- LPEN L Port Interrupt Enable (Multi-Input Wakeup/ Interrupt)

- T0PND Timer T0 Interrupt pending

- TOEN Timer T0 Interrupt Enable (Bit 12 toggle)

- µWPND MICROWIRE/PLUS interrupt pending

- µWEN Enable MICROWIRE/PLUS interrupt

- T1PNDB Timer T1 Interrupt Pending Flag for T1B capture edge

- T1ENB Timer T1 Interrupt Enable for T1B Input capture edge

#### T2CNTRL Register (Address X'00C6)

| T2C3  | T2C2  | T2C1                                                                                                         | T2C0    | T2PNDA                 | T2ENA    | T2PNDB    | T2ENB   |

|-------|-------|--------------------------------------------------------------------------------------------------------------|---------|------------------------|----------|-----------|---------|

| Bit 7 |       |                                                                                                              |         |                        |          |           | Bit 0   |

| The T | 2CNTF | RL cont                                                                                                      | rol reg | ister cont             | ains the | following | j bits: |

| T2C   | 3     | Timer                                                                                                        | T2 mo   | ode contr              | ol bit   |           |         |

| T2C   | 2     | Timer                                                                                                        | T2 mo   | ode contr              | ol bit   |           |         |

| T2C   | 21    | Timer                                                                                                        | T2 mo   | ode contre             | ol bit   |           |         |

| T20   | 0     | Timer T2 Start/Stop control in tin<br>modes 1 and 2, T2 Underflow Interrupt Per<br>ing Flag in timer mode 3  |         |                        |          |           |         |

| T2F   | NDA   | Timer T2 Interrupt Pending Flag (Autorel<br>RA in mode 1, T2 Underflow in mode 2,<br>capture edge in mode 3) |         |                        |          |           |         |

| T2E   | NA    | Timer T2 Interrupt Enable for Timer Underflo<br>or T2A Input capture edge                                    |         |                        |          |           |         |

| T2F   | NDB   | Timer T2 Interrupt Pending Flag for T2B ture edge                                                            |         |                        |          |           |         |

| T2E   | NB    |                                                                                                              |         | errupt En<br>t capture |          | Timer Un  | derflow |

## Timers

The device contains a very versatile set of timers (T0, T1 and T2). All timers and associated autoreload/capture registers power up containing random data.

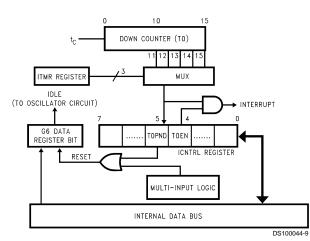

#### TIMER T0 (IDLE TIMER)

The device supports applications that require maintaining real time and low power with the IDLE mode. This IDLE mode support is furnished by the IDLE timer T0, which is a 16-bit timer. The Timer T0 runs continuously at the fixed rate of the instruction cycle clock,  $t_c$ . The user cannot read or write to the IDLE Timer T0, which is a count down timer. The Timer T0 supports the following functions:

The Timer TO supports the following functions:

- Exit out of the Idle Mode (See Idle Mode description)

- WATCHDOG logic (See WATCHDOG description)

- · Start up delay out of the HALT mode

*Figure 8* is a functional block diagram showing the structure of the IDLE Timer and its associated interrupt logic.

Bits 11 through 15 of the ITMR register can be selected for triggering the IDLE Timer interrupt. Each time the selected bit underflows (every 4k, 8k, 16k, 32k or 64k instruction cycles), the IDLE Timer interrupt pending bit TOPND is set, thus generating an interrupt (if enabled), and bit 6 of the Port G data register is reset, thus causing an exit from the IDLE mode if the device is in that mode.

In order for an interrupt to be generated, the IDLE Timer interrupt enable bit T0EN must be set, and the GIE (Global Interrupt Enable) bit must also be set. The T0PND flag and T0EN bit are bits 5 and 4 of the ICNTRL register, respectively. The interrupt can be used for any purpose. Typically, it is used to perform a task upon exit from the IDLE mode. For more information on the IDLE mode, refer to the Power Save Modes section.

FIGURE 8. Functional Block Diagram for Idle Timer T0

The Idle Timer period is selected by bits 0-2 of the ITMR register Bits 3-7 of the ITMR Register are reserved and should not be used as software flags.

#### ITMR Register (Address X'0xCF)

|       | Reserved | ITSEL2 | ITSEL1 | ITSLE0 |

|-------|----------|--------|--------|--------|

| Bit 7 |          |        |        | Bit 0  |

| TABLE 2 | . Idle | Timer | Window | Lenath |

|---------|--------|-------|--------|--------|

|         |        |       |        |        |

| ITSEL2 | ITSEL1 | ITSEL0 | Idle Timer Period    |

|--------|--------|--------|----------------------|

|        |        |        | (Instruction Cycles) |

| 0      | 0      | 0      | 4,096                |

| 0      | 0      | 1      | 8,192                |

| 0      | 1      | 0      | 16,384               |

| 0      | 1      | 1      | 32,768               |

| 1      | Х      | Х      | 65,536               |

The ITMR register is cleared on Reset and the Idle Timer period is reset to 4,096 instruction cycles.

Any time the IDLE Timer period is changed there is the possibility of generating a spurious IDLE Timer interrupt by setting the TOPND bit. The user is advised to disable IDLE Timer interrupts prior to changing the value of the ITSEL bits of the ITMR Register and then clear the TOPND bit before attempting to synchronize operation to the IDLE Timer.

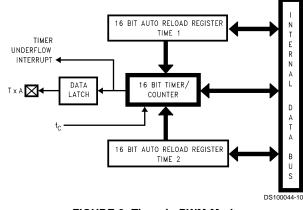

#### TIMER T1 and TIMER T2

The device has a set of three powerful timer/counter blocks, T1 and T2. The associated features and functioning of a timer block are described by referring to the timer block Tx. Since the three timer blocks, T1 and T2 are identical, all comments are equally applicable to either of the three timer blocks.

Each timer block consists of a 16-bit timer, Tx, and two supporting 16-bit autoreload/capture registers, RxA and RxB. Each timer block has two pins associated with it, TxA and TxB. The pin TxA supports I/O required by the timer block, while the pin TxB is an input to the timer block. The powerful and flexible timer block allows the device to easily perform all timer functions with minimal software overhead. The timer block has three operating modes: Processor Independent PWM mode, External Event Counter mode, and Input Capture mode.

The control bits TxC3, TxC2, and TxC1 allow selection of the different modes of operation.

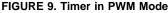

#### Mode 1. Processor Independent PWM Mode

As the name suggests, this mode allows the device to generate a PWM signal with very minimal user intervention.

The user only has to define the parameters of the PWM signal (ON time and OFF time). Once begun, the timer block will continuously generate the PWM signal completely indepen-

#### Timers (Continued)

dent of the microcontroller. The user software services the timer block only when the PWM parameters require updating.

In this mode the timer Tx counts down at a fixed rate of  $t_c$ . Upon every underflow the timer is alternately reloaded with the contents of supporting registers, RxA and RxB. The very first underflow of the timer causes the timer to reload from the register RxA. Subsequent underflows cause the timer to be reloaded from the registers alternately beginning with the register RxB.

The Tx Timer control bits, TxC3, TxC2 and TxC1 set up the timer for PWM mode operation.

Figure 9 shows a block diagram of the timer in PWM mode.

The underflows can be programmed to toggle the TxA output pin. The underflows can also be programmed to generate interrupts.

Underflows from the timer are alternately latched into two pending flags, TxPNDA and TxPNDB. The user must reset these pending flags under software control. Two control enable flags, TxENA and TxENB, allow the interrupts from the timer underflow to be enabled or disabled. Setting the timer enable flag TxENA will cause an interrupt when a timer underflow causes the RxA register to be reloaded into the timer. Setting the timer enable flag TxENB will cause an interrupt when a timer underflow causes the RxB register to be reloaded into the timer. Resetting the timer enable flags will disable the associated interrupts.

Either or both of the timer underflow interrupts may be enabled. This gives the user the flexibility of interrupting once per PWM period on either the rising or falling edge of the PWM output. Alternatively, the user may choose to interrupt on both edges of the PWM output.

#### Mode 2. External Event Counter Mode

This mode is quite similar to the processor independent PWM mode described above. The main difference is that the timer, Tx, is clocked by the input signal from the TxA pin. The Tx timer control bits, TxC3, TxC2 and TxC1 allow the timer to be clocked either on a positive or negative edge from the

TxA pin. Underflows from the timer are latched into the TxP-NDA pending flag. Setting the TxENA control flag will cause an interrupt when the timer underflows.

In this mode the input pin TxB can be used as an independent positive edge sensitive interrupt input if the TxENB control flag is set. The occurrence of the positive edge on the TxB input pin is latched to the TxPNDB flag.

*Figure 10* shows a block diagram of the timer in External Event Counter mode.

Note: The PWM output is not available in this mode since the TxA pin is being used as the counter input clock.

#### FIGURE 10. Timer in External Event Counter Mode

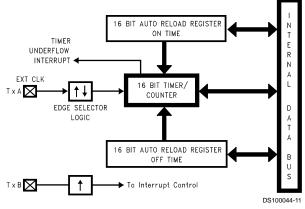

#### Mode 3. Input Capture Mode

The device can precisely measure external frequencies or time external events by placing the timer block, Tx, in the input capture mode.

In this mode, the timer Tx is constantly running at the fixed  $t_c$  rate. The two registers, RxA and RxB, act as capture registers. Each register acts in conjunction with a pin. The register RxA acts in conjunction with the TxA pin and the register RxB acts in conjunction with the TxB pin.

The timer value gets copied over into the register when a trigger event occurs on its corresponding pin. Control bits, TxC3, TxC2 and TxC1, allow the trigger events to be specified either as a positive or a negative edge. The trigger condition for each input pin can be specified independently.

The trigger conditions can also be programmed to generate interrupts. The occurrence of the specified trigger condition on the TxA and TxB pins will be respectively latched into the pending flags, TxPNDA and TxPNDB. The control flag TxENA allows the interrupt on TxA to be either enabled or disabled. Setting the TxENA flag enables interrupts to be generated when the selected trigger condition occurs on the TxA pin. Similarly, the flag TxENB controls the interrupts from the TxB pin.

Underflows from the timer can also be programmed to generate interrupts. Underflows are latched into the timer TxC0 pending flag (the TxC0 control bit serves as the timer underflow interrupt pending flag in the Input Capture mode). Consequently, the TxC0 control bit should be reset when entering the Input Capture mode. The timer underflow interrupt is enabled with the TxENA control flag. When a TxA interrupt occurs in the Input Capture mode, the user must check both whether a TxA input capture or a timer underflow (or both) caused the interrupt.

*Figure 11* shows a block diagram of the timer in Input Capture mode.

### Timers (Continued)

#### FIGURE 11. Timer in Input Capture Mode

#### TIMER CONTROL FLAGS

The control bits and their functions are summarized below.

| TxC3 | Timer mode | control |

|------|------------|---------|

|      |            |         |

- TxC2 Timer mode control TxC1 Timer mode control

- TxC0 Timer Start/Stop control in Modes 1 and 2 (Processor Independent PWM and External Event Counter), where 1 = Start, 0 = Stop Timer Underflow Interrupt Pending Flag in Mode 3 (Input Capture)

| •      |                              |

|--------|------------------------------|

| TxPNDA | Timer Interrupt Pending Flag |

| TxENA  | Timer Interrupt Enable Flag  |

|        | 1 = Timer Interrupt Enabled  |

|        | 0 = Timer Interrupt Disabled |

| TxPNDB | Timer Interrupt Pending Flag |

| TxENB  | Timer Interrupt Enable Flag  |

|        | 1 = Timer Interrupt Enabled  |

|        | 0 = Timer Interrupt Disabled |

The timer mode control bits (TxC3, TxC2 and TxC1) are detailed below:

| Mode | TxC3 | TxC2 | TxC1 | Description               | Interrupt A<br>Source | Interrupt B<br>Source | Timer<br>Counts On |

|------|------|------|------|---------------------------|-----------------------|-----------------------|--------------------|

|      | 1    | 0    | 1    | PWM: TxA Toggle           | Autoreload RA         | Autoreload RB         | t <sub>C</sub>     |

| 1    | 1    | 0    | 0    | PWM: No TxA<br>Toggle     | Autoreload RA         | Autoreload RB         | t <sub>c</sub>     |

| 0    | 0    | 0    | 0    | External Event<br>Counter | Timer<br>Underflow    | Pos. TxB Edge         | Pos. TxA<br>Edge   |

| 2    | 0    | 0    | 1    | External Event<br>Counter | Timer<br>Underflow    | Pos. TxB Edge         | Pos. TxA<br>Edge   |

|      | 0    | 1    | 0    | Captures:                 | Pos. TxA Edge         | Pos. TxB Edge         | t <sub>c</sub>     |

|      |      |      |      | TxA Pos. Edge             | or Timer              |                       |                    |

|      |      |      |      | TxB Pos. Edge             | Underflow             |                       |                    |

|      | 1    | 1    | 0    | Captures:                 | Pos. TxA              | Neg. TxB              | t <sub>C</sub>     |

|      |      |      |      | TxA Pos. Edge             | Edge or Timer         | Edge                  |                    |

| 0    |      |      |      | TxB Neg. Edge             | Underflow             |                       |                    |

| 3    | 0    | 1    | 1    | Captures:                 | Neg. TxA              | Neg. TxB              | t <sub>c</sub>     |

|      |      |      |      | TxA Neg. Edge             | Edge or Timer         | Edge                  |                    |

|      |      |      |      | TxB Neg. Edge             | Underflow             |                       |                    |

|      | 1    | 1    | 1    | Captures:                 | Neg. TxA              | Neg. TxB              | t <sub>c</sub>     |

|      |      |      |      | TxA Neg. Edge             | Edge or Timer         | Edge                  |                    |

|      |      |      |      | TxB Neg. Edge             | Underflow             |                       |                    |

#### **Power Save Modes**

The device offer the user two power save modes of operation: HALT and IDLE. In the HALT mode, all microcontroller activities are stopped. In the IDLE mode, the on-board oscillator circuitry and timer T0 are active but all other microcontroller activities are stopped. In either mode, all onboard RAM, registers, I/O states, and timers (with the exception of T0) are unaltered.

#### HALT MODE

The device is placed in the HALT mode by writing a "1" to the HALT flag (G7 data bit). All microcontroller activities, including the clock, and timers, are stopped. In the HALT mode, the power requirements of the device are minimal and the applied voltage ( $V_{\rm CC}$ ) may be decreased to Vr (Vr = 2.0V) without altering the state of the machine. CAN HALT/IDLE mode:

In order to reduce the device overall current consumption in HALT/IDLE mode a two step power save mechanism is implemented on the device:

- Step 1: Disable main receive comparator. This is done by resetting both the TxEN0 and TxEN1 bits in the CBUS register. Note: These bits should always be reset before entering HALT/IDLE mode to allow proper resynchronization to the CAN bus after exiting HALT/IDLE mode.

- Step 2: Disable the CAN wake-up comparators, this is done by resetting bit 7 in the port-m wakeup enable register (MWKEN) a transition on the CAN bus will then not wake the device up.

- Note: If both the main receive comparator and the wake-up comparator are disabled the on chip CAN voltage reference is also disabled. The CAN-V<sub>REF</sub> output is then High-Z

The following table shows the two CAN power save modes and the active CAN transceiver blocks:

| Step 1 | Step 2 | Main-Comp | Wake-Up-Comp | CAN-V <sub>REF</sub> | V <sub>REF</sub> Pin |

|--------|--------|-----------|--------------|----------------------|----------------------|

| 0      | 0      | on        | on           | on                   | V <sub>CC</sub> /2   |

| 0      | 1      | on        | off          | on                   | V <sub>CC</sub> /2   |

| 1      | 0      | off       | on           | on                   | V <sub>CC</sub> /2   |

| 1      | 1      | off       | off          | off                  | High-Z               |

The device supports two different ways of exiting the HALT mode. The first method of exiting the HALT mode is with the Multi-Input Wakeup feature on the L & M port. The second method of exiting the HALT mode is by pulling the RESET pin low.

Since a crystal or ceramic resonator may be selected as the oscillator, the Wakeup signal is not allowed to start the chip running immediately since crystal oscillators and ceramic resonators have a delayed start up time to reach full amplitude and frequency stability. The IDLE timer is used to generate a fixed delay to ensure that the oscillator has indeed stabilized before allowing instruction execution. In this case, upon detecting a valid Wakeup signal, only the oscillator circuitry is enabled. The IDLE timer is loaded with a value of 256 and is clocked with the  $t_c$  instruction cycle clock. The  $t_c$ clock is derived by dividing the oscillator clock down by a factor of 10. The Schmitt trigger following the CKI inverter on the chip ensures that the IDLE timer is clocked only when the oscillator has a sufficiently large amplitude to meet the Schmitt trigger specifications. This Schmitt trigger is not part of the oscillator closed loop. The start-up time-out from the IDLE timer enables the clock signals to be routed to the rest of the chip.

The device has two mask options associated with the HALT mode. The first mask option enables the HALT mode feature, while the second mask option disables the HALT mode. With the HALT mode enable mask option, the device will enter and exit the HALT mode as described above. With the HALT disable mask option, the device cannot be placed in the HALT mode (writing a "1" to the HALT flag will have to effect).

#### IDLE MODE

The device is placed in the IDLE mode by writing a "1" to the IDLE flag (G6 data bit). In this mode, all activity, except the associated on-board oscillator circuitry, ad the IDLE Timer T0, is stopped. The power supply requirements of the micro-controller in this mode of operation are typically around 30% of normal power requirement of the microcontroller.

www.national.com

As with the HALT mode, the device can be returned to normal operation with a reset, or with a Multi-Input Wakeup from the Port L or CAN Interface. Alternately, the microcontroller resumes normal operation from the IDLE mode when the thirteenth bit (representing 4.096 ms at internal clock frequency of 1 MHz,  $t_c = 1 \ \mu s$ ) of the IDLE Timer toggles.

This toggle condition of the thirteenth bit of the IDLE Timer T0 is latched into the T0PND pending flag.

The user has the option of being interrupted with a transition on the thirteenth bit of the IDLE Timer T0. The interrupt can be enabled or disabled via the T0EN control bit. Setting the T0EN flag enables the interrupt and vice versa.

The user can enter the IDLE mode with the Timer T0 interrupt enabled. In this case, when the T0PND bit gets set, the device will first execute the Timer T0 interrupt service routine and then return to the instruction following the "Enter Idle Mode" instruction.

Alternatively, the user can enter the IDLE mode with the IDLE Timer T0 interrupt disabled. In this case, the device will resume normal operation with the instruction immediately following the "Enter IDLE Mode" instruction.

Note: It is necessary to program two NOP instructions following both the set HALT mode and set IDLE mode instructions. These NOP instructions are necessary to allow clock resynchronization following the HALT or IDLE modes.

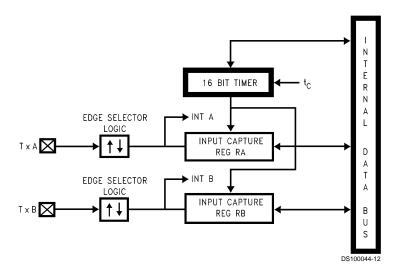

## Multi-Input Wakeup

The Multi-Input Wakeup feature is used to return (wakeup) the device from either the HALT or IDLE modes. Alternately, the Multi-Input Wakeup/Interrupt feature may also be used to generate up to 7 edge selectable external interrupts.

Note: The following description is for both the Port L and the M port. When the document refers to the registers WKEGD, WKEN or WKPND, the user will have to put either M (for M port) or L (for port) in front of the register, i.e., LWKEN (Port L WKEN), MWKEN (Port M WKEN).

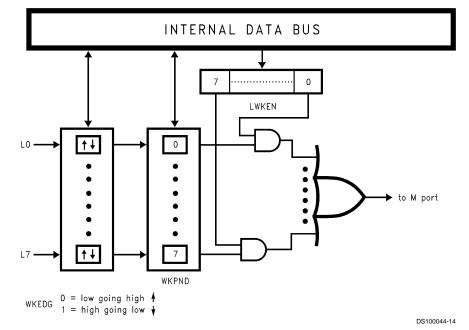

*Figures 12, 13* shows the Multi-Input Wakeup logic for the microcontroller. The Multi-Input Wakeup feature utilizes the L Port. The user selects which particular Port L bit (or combi-

# Multi-Input Wakeup (Continued)

nation of Port L bits) will cause the device to exit the HALT or IDLE modes. The selection is done through the Reg: WKEN. The Reg: WKEN is an 8-bit read/write register, which contains a control bit for every Port L bit. Setting a particular WKEN bit enables a Wakeup from the associated Port L pin.

The user can select whether the trigger condition on the selected Port L pin is going to be either a positive edge (low to high transition) or a negative edge (high to low transition). This selection is made via the Reg: WKEDG, which is an 8-bit control register with a bit assigned to each Port L pin. Setting the control bit will select the trigger condition to be a negative edge on that particular Port L pin. Resetting the bit selects the trigger condition to be a positive edge. Changing an edge select entails several steps in order to avoid a pseudo Wakeup condition as a result of the edge change. First, the associated WKEN bit should be reset, followed by the edge select change in WKEDG. Next, the associated WKPND bit should be cleared, followed by the associated WKEN bit being re-enabled. An example may serve to clarify this procedure. Suppose we wish to change the edge select from positive (low going high) to negative (high going low) for Port L bit 5, where bit 5 has previously been enabled for an input interrupt. The program would be as follows:

| RBIT | 5, | WKEN  | ;Disable MIWU         |

|------|----|-------|-----------------------|

| SBIT | 5, | WKEDG | ;Change edge polarity |

| RBIT | 5, | WKPND | ;Reset pending flag   |

| SBIT | 5, | WKEN  | ;Enable MIWU          |

|      |    |       |                       |

If the Port L bits have been used as outputs and then changed to inputs with Multi-Input Wakeup/Interrupt, a safety procedure should also be followed to avoid inherited pseudo wakeup conditions. After the selected Port L bits have been changed from output to input but before the associated WKEN bits are enabled, the associated edge select bits in WKEDG should be set or reset for the desired edge selects, followed by the associated WKPND bits being cleared.

FIGURE 12. Port M Multi-Input Wake-up Logic

This same procedure should be used following reset, since the Port L inputs are left floating as a result of reset. The occurrence of the selected trigger condition for Multi-Input Wakeup is latched to a pending register called WKPND. The respective bits of the WKPND register will be set on the occurrence of the selected trigger edge on the corresponding Port L and Port M pin. The user has the responsibility of clearing these pending flags. Since WKPND is a pending register for the occurrence of selected wakeup conditions, the device will not enter the HALT mode if any wakeup bit is both enabled and pending. Consequently, the user has the responsibility of clearing the pending flags before attempting to enter the HALT mode. The WKEN, WKPND and WKEDG are all read/write registers, and are cleared at reset.

#### PORT L INTERRUPTS

Port L provides the user with additional eight fully selectable, edge sensitive interrupts which are all vectored into the same service subroutine.

The interrupt from Port L shares logic with the wake up circuitry. The register WKEN allows interrupts from Port L to be individually enabled or disabled. The register WKEDG specifies the trigger condition to be either a positive or a negative edge. Finally, the register WKPND latches in the pending trigger conditions.

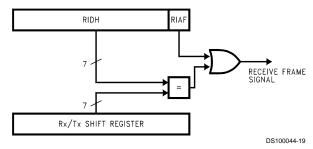

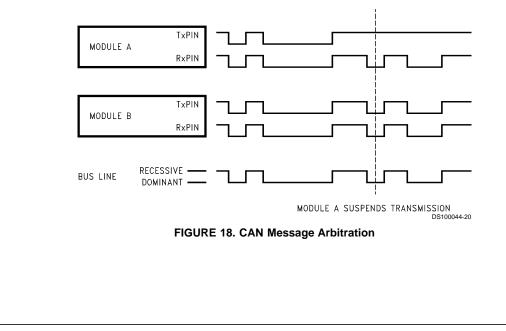

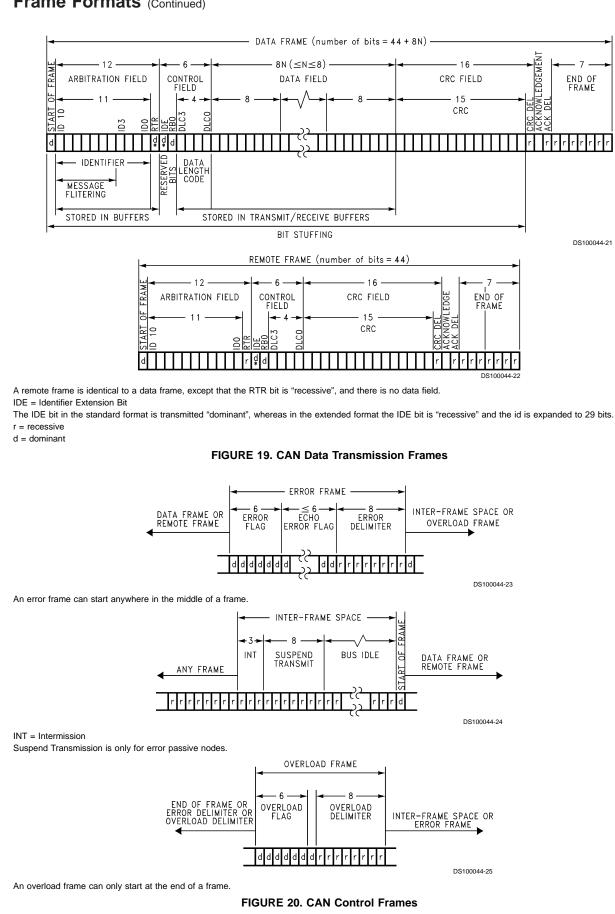

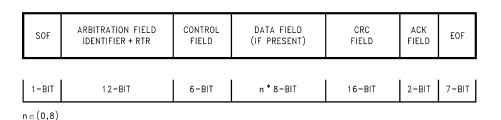

#### Multi-Input Wakeup (Continued)