# MC9S12UF32 System on a Chip Guide V01.05

Original Release Date: 17 JAN 2002 Revised: 03 Dec 2004

# TSPG - 8/16 Bit MCU Design, HKG Freescale Semiconductor, Inc.

This product has been designed for use in "Commercial" applications. Please see a description below.

Freescale's semiconductor products are classified into the following three tiers "Commercial", "Industrial", and "Automotive". A product should only be used in applications appropriate to its tier. The recommended applications for products in the different tiers are indicated below. For questions, please contact a Freescale sales representative.

Commercial: Typically 5 year applications - personal computers, PDA's, portable telecom products, consumer electronics, etc. Industrial: Typically 10 year applications - installed telecom equipment, work stations, servers, etc. These products can also be used for Commercial applications.

Automotive: Qualified per automotive industry standard methods.

# **Revision History**

| Release<br>Number | Date    | Author     | Summary of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------|---------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00.01             | 17JAN02 | Y.H. Cheng | Initial Version                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 00.02             | 19FEB02 | Y.H. Cheng | Modified SMRAM mapping to allow 1k byte 16-bit block mappable to Vector Space. Update spec with review feedback.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 00.03             | 26APR02 | Y.H. Cheng | Modified Device pinout to separate D+ D- for high speed and low speed operation. Remap Timer pins to Port R. Update BG references.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 00.04             | 16SEP02 | Y.H. Cheng | Modified Device pinout per IP requirement<br>Add SCI<br>Update Interrupt information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 00.05             | 25SEP02 | Y.H. Cheng | Change pin location for REF3V and VREGEN<br>minor update on module name references<br>remove references to pseudo stop and clock monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 00.06             | 03JUN03 | Y.H. Cheng | <ul> <li>Updated info for SMRAM3P5K2E in device memory map</li> <li>Updated EXTAL and XTAL supply rail information.</li> <li>Relocate SCI module base address from \$70 to \$C8</li> <li>Relocate ATA5HC module base address from \$240 to \$1C0</li> <li>Relocate PIM module base address from \$80 to \$240</li> <li>Relocate Interrupt Vectors</li> <li>Updated Phy evaluation pinout.</li> <li>Updated CFA00, CFA01 and CFA02 pin name to CFA0, CFA1 and CFA2 respectively.</li> <li>Removed ESD and Latchup section in Electrical.</li> <li>Update Block Guide References</li> <li>Miscellaneous Typo mistakes.</li> </ul> |

| 00.07             | 11JUN03 | Y.H. Cheng | <ul> <li>Update typo in interrupt vector table for Vector \$C2</li> <li>Update typo in pin order of IOC[7:4] in signal properties table</li> <li>Specify run and wait IDDs in Electrical Section</li> <li>Specify stop IDD at room temperature in Electrical Section</li> </ul>                                                                                                                                                                                                                                                                                                                                                 |

| 00.08             | 13JUL03 | Y.H. Cheng | - Change specification to include 64 pin option<br>- ROMCTL pin assigned to PJ2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Freescale Semiconductor reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Freescale Semiconductor does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death regarding the design or manufacture of the part. Freescale<sup>TM</sup> and the Freescale logo are registered trademarks of Freescale Semiconductor, Inc. Freescale Semiconductor, Inc. is an Equal Opportunity/Affirmative Action Employer.

© Freescale Semiconductor, Inc. 2004

#### Freescale Semiconductor

| Release<br>Number | Date    | Author     | Summary of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------|---------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01.00             | 21AUG03 | Y.H. Cheng | <ul> <li>Removed all references to XCLKS, since function is removed.</li> <li>typo - replaced PRU with RPU.</li> <li>typo - replaced ATAHC with ATA5HC</li> <li>Removed references to clock monitor, since function is not available.</li> <li>Update θ<sub>JA</sub> for 100-pin and 64-pin packages.</li> <li>Add footnotes on IRQ pin removal in 64-pin package</li> <li>Update Flash memory map out of reset.</li> <li>Add information on INITRM, INITRG, INITEE setting for example application memory map</li> <li>Update clock distribution diagram to make it more intelligible</li> <li>Change table 2-3, 2-5 description using general purpose port references instead of Functional module references.</li> <li>Stop IDD spec for -40C and 85C are removed</li> <li>Add other conditions for RUN Idd and Wait Idd.</li> </ul> |

| 01.01             | 28NOV03 | Wai-On Law | <ul> <li>Minor typo corrections.</li> <li>Corrected 'Background Debug Module' to 'HCS12 Breakpoint' at address \$0028-\$002F in table 1-1.</li> <li>Added detailed register map.</li> <li>Corrected the MSHC enable control in table 5-1.</li> <li>Added part ID \$6311 for mask 1L47S.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 01.02             | 23MAR04 | Y.H. Cheng | <ul> <li>Removed all references and description on USB Physical<br/>Endpoint 6</li> <li>Updated IDD, 3V and 5V I/O electricals and package thermal<br/>resistance information</li> <li>Include Commercial tier note</li> <li>Update and add note to detailed register map.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 01.03             | 20APR04 | Wai-On Law | - Added PIM reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 01.04             | 10MAY04 | Wai-On Law | - Added package information as appendix B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 01.05             | 03DEC04 | Wai-On Law | <ul> <li>Improved fig 1-1.</li> <li>Fixed consistency of 3.0v and 3.3v for VDD3X.</li> <li>Updated power dissipation formula.</li> <li>Added schematic and PCB layout recommendations.</li> <li>Added NVM, VREGU, CRGU electricals to appendix A.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

System on a Chip Guide — 9S12UF32DGV1/D V01.05

# **Table of Contents**

# **Section 1 Introduction**

| 1.1   | Overview              | 9          |

|-------|-----------------------|------------|

| 1.2   | Features              | 9          |

| 1.3   | Modes of Operation    | 22         |

| 1.4   | Block Diagram         | 23         |

| 1.5   | Device Memory Map     | <u>2</u> 4 |

| 1.5.1 | Detailed Register Map | 26         |

| 1.6   | Part ID Assignments   | 16         |

# **Section 2 Signal Description**

| 2.1    | Device Pinout                                                                  |

|--------|--------------------------------------------------------------------------------|

| 2.2    | Signal Properties Summary for 100-pin Package                                  |

| 2.3    | Signal Properties Summary for 64-pin Package                                   |

| 2.4    | Detailed Signal Descriptions for 100-pin package                               |

| 2.4.1  | EXTAL, XTAL — Oscillator Pins                                                  |

| 2.4.2  | RESET — External Reset Pin                                                     |

| 2.4.3  | TEST — Test Pin                                                                |

| 2.4.4  | VREGEN — Voltage Regulator Enable Pin                                          |

| 2.4.5  | BKGD / TAGHI / MODC — Background Debug, Tag High & Mode Pin57                  |

| 2.4.6  | RPU — USB D+ pull up resistor termination                                      |

| 2.4.7  | RREF — External bias resistor                                                  |

| 2.4.8  | DPF - USB Full Speed D+ data line                                              |

| 2.4.9  | DPH - USB High Speed D+ data line                                              |

| 2.4.10 | DMF - USB Full Speed D- data line                                              |

| 2.4.11 | DMH - USB High Speed D- data line                                              |

| 2.4.12 | PWROFF5V - power off 5V supply                                                 |

| 2.4.13 | PWROFF3V - power off 3V supply                                                 |

| 2.4.14 | REF3V - 3.3V reference for external regulator                                  |

| 2.4.15 | PA[7:0] / ADDR[15:8] / DATA[15:8] / CFD[15:8] / ATAD[15:8] — Port A I/O Pins58 |

| 2.4.16 | PB[7:0] / ADDR[7:0] / DATA[7:0] / CFD[7:0] / ATAD[7:0] — Port B I/O Pins       |

| 2.4.17 | PE7 / NOACC — Port E I/O Pin 7                                                 |

| 2.4.18 | PE6 / MODB / IPIPE1 — Port E I/O Pin 6                                         |

| 2.4.19 | PE5 / MODA / IPIPE0 — Port E I/O Pin 5                                         |

Freescale Semiconductor

| 2.4.20 | PE4 / ECLK— Port E I/O Pin 4 / E-Clock Output                       | .59 |

|--------|---------------------------------------------------------------------|-----|

| 2.4.21 | PE3 / LSTRB / TAGLO — Port E I/O Pin 3 / Low-Byte Strobe (LSTRB)    | .60 |

| 2.4.22 | PE2 / R/W — Port E I/O Pin 2 / Read/Write                           | .60 |

| 2.4.23 | PE1 / IRQ — Port E input Pin 1 / Maskable Interrupt Pin             | .60 |

| 2.4.24 | PE0 / XIRQ — Port E input Pin 0 / Non Maskable Interrupt Pin        | .60 |

| 2.4.25 | PJ2 / MSSCLK/ROMCTL - Port J I/O Pin 2                              | .60 |

| 2.4.26 | PJ1 / MSSDIO - Port J I/O Pin 1                                     | .61 |

| 2.4.27 | PJ0 / MSBS - Port J I/O Pin 0                                       | .61 |

| 2.4.28 | PM[5:2] / SDDATA[3:0] - Port M I/O Pin [5:2]                        | .61 |

| 2.4.29 | PM1 / SDCLK — Port M I/O Pin 1                                      | .61 |

| 2.4.30 | PM0 / SDCMD — Port M I/O Pin 0                                      | .61 |

| 2.4.31 | PP7 / SRE / ACFD15 / AATAD15— Port P I/O Pin 7                      | .61 |

| 2.4.32 | PP6 / SWE / ACFD14 / AATAD14— Port P I/O Pin 6                      | .62 |

| 2.4.33 | PP5 / SALE / ACFD13 / AATAD13— Port P I/O Pin 5                     | .62 |

| 2.4.34 | PP4 / SCLE / ACFD12 / AATAD12— Port P I/O Pin 4                     | .62 |

| 2.4.35 | PP3 / SWP / ACFD11 / AATAD11— Port P I/O Pin 3                      | .62 |

| 2.4.36 | PP2 / SCE / ACFD10 / AATAD10— Port P I/O Pin 2                      | .62 |

| 2.4.37 | PP1 / SCD / ACFD9 / AATAD9— Port P I/O Pin 1                        | .63 |

| 2.4.38 | PP0 / SBSY / ACFD8 / AATAD8— Port P I/O Pin 0                       | .63 |

| 2.4.39 | PQ[7:0] / SDAT[7:0] / ACFD[7:0] / AATAD[7:0]— Port Q I/O Pins [7:0] | .63 |

| 2.4.40 | PR[1:0] / CFA[4:3] — Port R I/O Pins [1:0]                          | .63 |

| 2.4.41 | PR[2] / CFA[5] / RXD — Port R I/O Pins [2]                          | .63 |

| 2.4.42 | PR[3] / CFA[6] / TXD — Port R I/O Pins [3]                          | .64 |

| 2.4.43 | PR[7:4] / CFA[10:7] / IOC[7:4] — Port R I/O Pins [7:4]              | .64 |

| 2.4.44 | PS7 / CFRDY(CFIREQ) / ATAINTQ — Port S I/O Pin 7                    | .64 |

| 2.4.45 | PS6 / CFWE / ATADMARQ — Port S I/O Pin 6                            | .64 |

| 2.4.46 | PS5 / CFIOWR / ATAIOWR — Port S I/O Pin 5                           | .64 |

| 2.4.47 | PS4 / CFIORD / ATAIORD — Port S I/O Pin 4                           | .65 |

| 2.4.48 | PS3 / CFCE2 / ATACS1 — Port S I/O Pin 3                             | .65 |

| 2.4.49 | PS2 / CFIOIS16 — Port S I/O Pin 2                                   | .65 |

| 2.4.50 | PS1 / CFOE — Port S I/O Pin 1                                       | .65 |

| 2.4.51 | PS0 / CFCE1 / ATACS0 — Port S I/O Pin 0                             | .65 |

| 2.4.52 | PT[3:0] / IOC[3:0]— Port T I/O Pins [3:0]                           | .66 |

| 2.4.53 | PU[5:3] / CFA[2:0] / ATADA[2:0] — Port U I/O Pins [5:3]             | .66 |

| 2.4.54 | PU2 / CFREG — Port U I/O Pin 2                                      | .66 |

| 2.4.55 | PU1 / CFINPACK / ATADMACK — Port U I/O Pin 1                        | .66 |

| 2.4.56       | PU0 / CFWAIT / ATAIORDY — Port U I/O Pin 0                                         | 66 |

|--------------|------------------------------------------------------------------------------------|----|

| 2.5 De       | etailed Signal Descriptions for 64-pin package                                     | 67 |

| 2.5.1        | EXTAL, XTAL — Oscillator Pins                                                      | 67 |

| 2.5.2        | RESET — External Reset Pin                                                         | 67 |

| 2.5.3        | TEST — Test Pin                                                                    | 67 |

| 2.5.4        | BKGD / TAGHI / MODC — Background Debug, Tag High & Mode Pin                        | 67 |

| 2.5.5        | RPU — USB D+ pull up resistor termination                                          | 67 |

| 2.5.6        | RREF — External bias resistor                                                      | 67 |

| 2.5.7        | DPF - USB Full Speed D+ data line                                                  | 67 |

| 2.5.8        | DPH - USB High Speed D+ data line                                                  | 68 |

| 2.5.9        | DMF - USB Full Speed D- data line                                                  | 68 |

| 2.5.10       | DMH - USB High Speed D- data line                                                  | 68 |

| 2.5.11       | REF3V - 3.3V reference for external regulator                                      | 68 |

| 2.5.12       | PA[5:0] / ADDR[13:8] / DATA[13:8] / CFD[13:8] / ATAD[13:8] — Port A I/O Pins       | 68 |

| 2.5.13       | PA[6] / ADDR[14] / DATA[14] / CFD[14] / ATAD[14] / MSBS— Port A I/O Pins           | 68 |

| 2.5.14       | PA[7] / ADDR[15] / DATA[15] / CFD[15] / ATAD[15] — Port A I/O Pins                 | 69 |

| 2.5.15<br>69 | PB[7:0] / ADDR[7:0] / DATA[7:0]/ CFD[7:0] / ATAD[7:0] / IOC[7:0] — Port B I/O Pine | Ξ. |

| 2.5.16       | PE7 / NOACC / CAF10— Port E I/O Pin 7                                              | 69 |

| 2.5.17       | PE6 / MODB / IPIPE1 / CFA9 — Port E I/O Pin 6                                      | 69 |

| 2.5.18       | PE5 / MODA / IPIPE0 / CFA8 — Port E I/O Pin 5                                      | 69 |

| 2.5.19       | PE4 / ECLK— Port E I/O Pin 4 / E-Clock Output                                      | 69 |

| 2.5.20       | PE3 / LSTRB / TAGLO / CFA3 — Port E I/O Pin 3 / Low-Byte Strobe (LSTRB)            | 70 |

| 2.5.21       | PE2 / R/W — Port E I/O Pin 2 / Read/Write                                          | 70 |

| 2.5.22       | PE0 / XIRQ — Port E input Pin 0 / Non Maskable Interrupt Pin                       | 70 |

| 2.5.23       | PJ2 / ATACS1 / SWP / CFCE2 / ROMCTL - Port J I/O Pin 2                             | 70 |

| 2.5.24       | PJ1 / ATACS0 / SCLE / CFCE1 - Port J I/O Pin 1                                     | 71 |

| 2.5.25       | PJ0 / ATAIOWR / SALE / CFIOWR - Port J I/O Pin 0                                   | 71 |

| 2.5.26       | PM4 / IOC3 / SDDATA2 / SBSY / CFIOIS16 — Port M I/O Pin 4                          | 71 |

| 2.5.27       | PM3 / IOC2 / SDDATA1 / SCE / CFINPACK — Port M I/O Pin 3                           | 71 |

| 2.5.28       | PQ7 / SDAT7 / CFA7 / IOC7 — Port Q I/O Pins 7                                      | 71 |

| 2.5.29       | PQ6 / SDAT6 / CFA6 / SDCLK / IOC6 — Port Q I/O Pins 6                              | 72 |

| 2.5.30       | PQ5 / SDAT5 / CFA5 / SDCMD / IOC5 — Port Q I/O Pins 5                              | 72 |

| 2.5.31       | PQ4 / SDAT4 / CFA4 / ATADMACK / IOC4 — Port Q I/O Pins 4                           | 72 |

| 2.5.32       | PQ3 / SDAT3 / CFIORD / ATAIORD — Port Q I/O Pins 3                                 | 72 |

| 2.5.33       | PQ[2:0] / SDAT[2:0] / CFA[2:0] / ATADA[2:0]— Port Q I/O Pins [2:0]                 | 72 |

System on a Chip Guide — 9S12UF32DGV1/D V01.05

| 2.5.34         | PS7 / CFRDY(CFIREQ) / ATAINTQ / MSSDIO — Port S I/O Pin 773                        |

|----------------|------------------------------------------------------------------------------------|

| 2.5.35         | PS6 / CFWE / ATADMARQ / MSCLK — Port S I/O Pin 6                                   |

| 2.5.36         | PS5 / TXD — Port S I/O Pin 5                                                       |

| 2.5.37         | PS4 / RXD — Port S I/O Pin 473                                                     |

| 2.5.38         | PT1 / IOC1 / SDDATA3 / SWE / CFOE — Port T I/O Pin 1                               |

| 2.5.39         | PT0 / IOC0 / SDDATA0 / SRE / CFREG — Port T I/O Pin 0                              |

| 2.5.40         | PU0 / CFWAIT / ATAIORDY / SCD — Port U I/O Pin 0                                   |

| 2.6            | Power Supply Pins                                                                  |

| 2.6.1<br>74    | VDDR, VSSR - Power & Ground Pins for I/O Drivers & for Internal Voltage Regulator. |

| ~ ~ ~          |                                                                                    |

| 2.6.2          | VDD - Core Power Pin                                                               |

| 2.6.2<br>2.6.3 | VDD - Core Power Pin                                                               |

|                |                                                                                    |

| 2.6.3          | VDDX, VSSX - Power & Ground Pins for I/O Drivers                                   |

# **Section 3 System Clock Description**

# **Section 4 Modes of Operation**

| 4.1   | Overview                                 |

|-------|------------------------------------------|

| 4.2   | Modes of Operation                       |

| 4.2.1 | Normal Operating Modes                   |

| 4.2.2 | Special Operating Modes                  |

| 4.3   | Internal Visibility                      |

| 4.4   | Security                                 |

| 4.4.1 | Securing the Microcontroller             |

| 4.4.2 | Operation of the Secured Microcontroller |

| 4.4.3 | Unsecuring the Microcontroller           |

| 4.5   | Low Power Modes                          |

| 4.5.1 | Stop                                     |

| 4.5.2 | Wait                                     |

| 4.5.3 | Run                                      |

# **Section 5 Resets and Interrupts**

| 5.1   | Overview     |

|-------|--------------|

| 5.2   | Vectors      |

| 5.2.1 | Vector Table |

| 5.3   | Resets       |

| 5.3.1 | Reset Summary Table | 87 |

|-------|---------------------|----|

| 5.3.2 | Effects of Reset    | 87 |

# Section 6 HCS12 Core Block Description

| 6.1  | CPU12 Block Description                                           |

|------|-------------------------------------------------------------------|

| 6.2  | HCS12 Background Debug Module (BDM) Block Description             |

| 6.3  | HCS12 Breakpoint (BKP) Block Description                          |

| 6.4  | HCS12 Interrupt (INT) Block Description                           |

| 6.5  | HCS12 Multiplexed External Bus Interface (MEBI) Block Description |

| 6.6  | HCS12 Module Mapping Control (MMC) Block Description              |

| Sect | ion 7 ATA5 Host Controller (ATA5HC) Block Description             |

| 7.1  | Device-specific information                                       |

| Sect | ion 8 Compact Flash Host Controller (CFHC) Block Description      |

| 8.1  | Device-specific information                                       |

| Sect | ion 9 Clock Reset Generator (CRG_U) Block Description             |

| 9.1  | Device-specific information                                       |

| Sect | ion 10 Flash EEPROM 32K (FTS32K) Block Description                |

| 10.1 | Device-specific information                                       |

| Sect | ion 11 Integrated Queue Controller (IQUE) Block Description       |

| 11.1 | Device-specific information                                       |

| Sect | ion 12 Memorystick Host Controller (MSHC) Block Description       |

| 12.1 | Device-specific information                                       |

| Sect | ion 13 Oscillator (OSC) Block Description                         |

| 13.1 | Device-specific information                                       |

| Sect | ion 14 Port Integration Module (PIM) Block Description            |

| 14.1 | Device-specific information                                       |

| Sect | ion 15 Serial Communication Interface (SCI) Block Description     |

| 15.1 | Device-specific information                                       |

| Secti  | on 16 Secured Digital Host Controller (SDHC) Block Description |

|--------|----------------------------------------------------------------|

| 16.1   | Device-specific information                                    |

| Secti  | on 17 Smartmedia Host Controller (SMHC) Block Description      |

| 17.1   | Device-specific information                                    |

| Secti  | on 18 Smartmedia RAM (SMRAM) Block Description                 |

| 18.1   | Device-specific information                                    |

| Secti  | on 19 Timer (TIM) Block Description                            |

| 19.1   | Device-specific information                                    |

| Secti  | on 20 USB2.0 Controller (USB20D6E2F) Block Description         |

| 20.1   | Device-specific information                                    |

| Secti  | on 21 Voltage Regulator (VREG_U) Block Description             |

| 21.1   | Device-specific information                                    |

| Secti  | on 22 Schematic and PCB Layout Design Recommendations          |

| 22.1   | Schematic Design with the MC9S12UF32 and a USB interface94     |

| 22.1.1 |                                                                |

|        | Clocking Notes                                                 |

| 22.2   | PCB Design Recommendation                                      |

| Appe   | endix A Electrical Characteristics                             |

| A.1    | General                                                        |

| A.1.1  | Parameter Classification                                       |

| A.1.2  | Power Supply                                                   |

| A.1.3  | Pins                                                           |

| A.1.4  | Current Injection                                              |

| A.1.5  | Absolute Maximum Ratings                                       |

| A.1.6  | ESD Protection and Latch-up Immunity                           |

| A.1.7  | Operating Conditions                                           |

| A.1.8  | Power Dissipation and Thermal Characteristics                  |

| A.1.9  | I/O Characteristics                                            |

| A.1.10 |                                                                |

| A.2    | NVM, Flash                                                     |

| A.2.1 | NVM timing                | 109 |

|-------|---------------------------|-----|

| A.2.2 | NVM Reliability           | 111 |

| A.3   | Voltage Regulator         | 113 |

| A.4   | Reset, Oscillator and PHY | 115 |

| A.4.1 | Startup                   | 115 |

| A.4.2 | Oscillator                | 117 |

| A.4.3 | USB PHY                   | 117 |

| A.5   | External Bus Timing       | 119 |

| A.5.1 | General Muxed Bus Timing  | 119 |

# Appendix B Package Information

| B.1 | General              | 123 |

|-----|----------------------|-----|

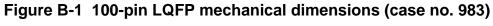

| B.2 | 100-pin LQFP Package | 124 |

| B.3 | 64-pin LQFP Package  | 125 |

System on a Chip Guide — 9S12UF32DGV1/D V01.05

# **List of Figures**

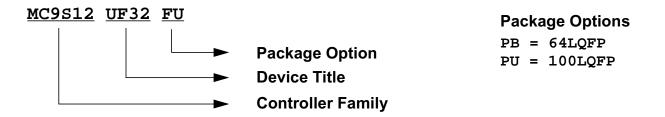

| Figure 0-1  | Order Part Number Coding18                           |

|-------------|------------------------------------------------------|

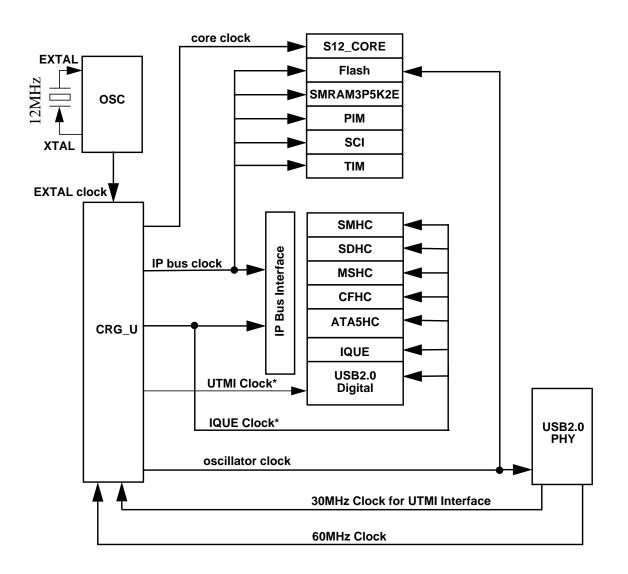

| Figure 1-1  | MC9S12UF32 Block Diagram                             |

| Figure 1-2  | MC9S12UF32 Memory Map (Application Example)          |

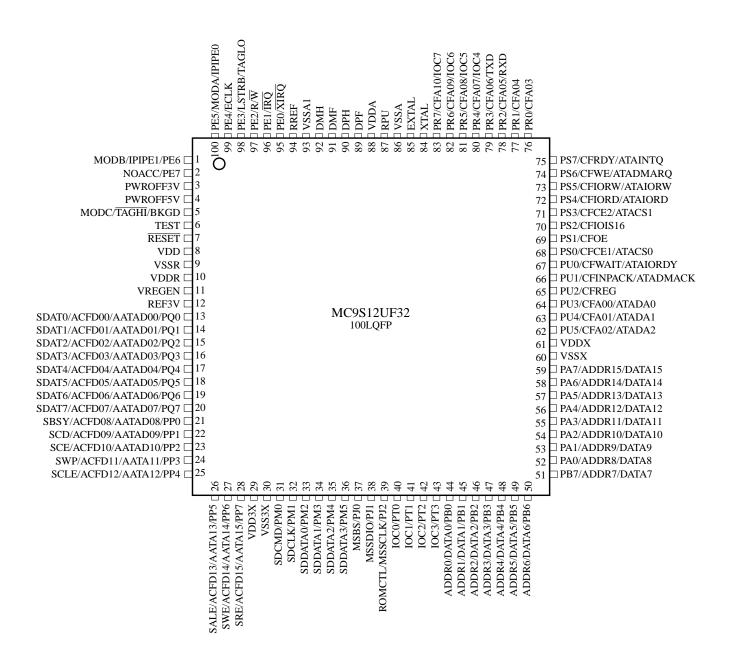

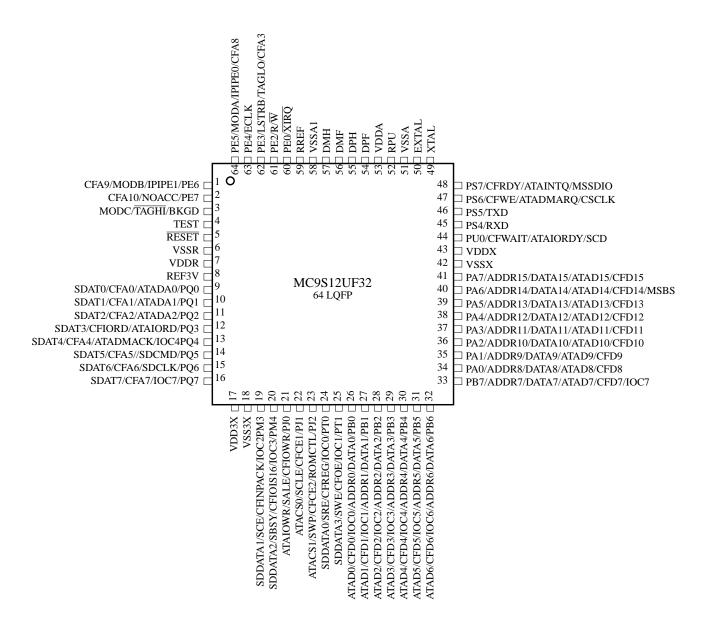

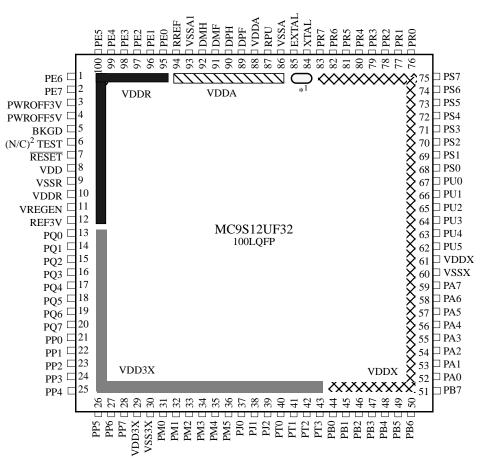

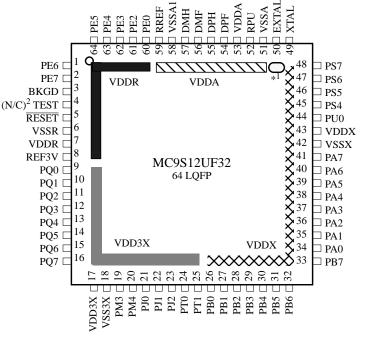

| Figure 2-1  | Pin Assignments in 100-pin LQFP49                    |

| Figure 2-2  | Pin Assignments in 64-pin LQFP50                     |

| Figure 2-3  | Supply rails for various I/O pins of 100-pin package |

| Figure 2-4  | Supply rails for various I/O pins of 64-pin package  |

| Figure 3-1  | Clock Connections                                    |

| Figure 13-1 | Pierce Oscillator Connections                        |

| Figure 22-1 | Sample schematic with 64-pin LQFP MC9S12UF3295       |

| Figure A-1  | General External Bus Timing 119                      |

| Figure B-1  | 100-pin LQFP mechanical dimensions (case no. 983)    |

| Figure B-2  | 64-pin LQFP mechanical dimensions (case no. 840F)    |

|             |                                                      |

System on a Chip Guide — 9S12UF32DGV1/D V01.05

# **List of Tables**

| Table 0-1  | Document References                                         | 17  |

|------------|-------------------------------------------------------------|-----|

| Table 0-2  | Part Number Coding                                          | 18  |

| Table 1-1  | Device Memory Map                                           | 24  |

| Table 1-2  | Assigned Part ID Numbers                                    | 46  |

| Table 1-3  | Memory size registers                                       | 46  |

| Table 2-1  | Configuration selection in 100-pin option                   | 47  |

| Table 2-2  | Configuration selection in 64-pin option                    | 48  |

| Table 2-3  | 100-pin Signal Properties                                   | 51  |

| Table 2-4  | 64-pin Signal Properties                                    | 54  |

| Table 2-5  | MC9S12UF32 Power and Ground Connection Summary              | 74  |

| Table 4-1  | Mode Selection                                              | 78  |

| Table 5-1  | Interrupt Vector Locations                                  | 85  |

| Table 5-2  | Reset Summary                                               | 87  |

| Table 11-1 | Queue Channel n Request Mapping                             | 90  |

| Table 22-1 | Recommended decoupling capacitor choice                     | 96  |

| Table A-1  | Absolute Maximum Ratings                                    | 99  |

| Table A-2  | ESD and Latch-up Test Conditions                            | 100 |

| Table A-3  | ESD and Latch-Up Protection Characteristics                 | 100 |

| Table A-4  | Operating Conditions                                        | 101 |

| Table A-5  | Thermal Package Characteristics                             | 102 |

| Table A-6  | 5V I/O Characteristics                                      | 104 |

| Table A-7  | 3.3V I/O Characteristics                                    | 106 |

| Table A-8  | Supply Current Characteristics                              | 108 |

| Table A-9  | NVM Timing Characteristics                                  | 110 |

| Table A-10 | NVM Reliability Characteristics                             | 111 |

| Table A-11 | Voltage Regulator Recommended Load Resistances/Capacitances | 113 |

| Table A-12 | Startup Characteristics.                                    | 115 |

| Table A-13 | Oscillator Characteristics                                  | 117 |

| Table A-15 | Expanded Bus Timing Characteristics                         | 120 |

System on a Chip Guide — 9S12UF32DGV1/D V01.05

# Preface

The SoC Guide provides information about the MC9S12UF32 device made up of standard HCS12 blocks and the HCS12 processor core.

This document is part of the customer documentation. A complete set of device manuals also includes the HCS12 Core User Guide and all the individual Block Guides of the implemented modules. In an effort to reduce redundancy all module specific information is located only in the respective Block Guide. If applicable, special implementation details of the module are given in the block description sections of this document.

See Table 0-1 for names and versions of the referenced documents throughout the Device Guide.

| User Guide                                                  | Version | Document Order<br>Number |

|-------------------------------------------------------------|---------|--------------------------|

| HCS12 CPU Reference Manual                                  | V02     | S12CPUV2/D               |

| HCS12 Breakpoint (BKP) Block Guide                          | V01     | S12BKPV1/D               |

| HCS12 Background Debug (BDM) Block Guide                    | V04     | S12BDMV4/D               |

| HCS12 Module Mapping Control (MMC) Block Guide              | V04     | S12MMCV4/D               |

| HCS12 Multiplexed External Bus Interface (MEBI) Block Guide | V03     | S12MEBIV3/D              |

| HCS12 Interrupt (INT) Block Guide                           | V01     | S12INTV1/D               |

| Clock and Reset Generator (CRG_U) Block Guide               | V01     | S12CRGUV1/D              |

| Timer: 16 bit, 8 channel (TIM_16B8C) Block Guide            | V01     | S12TIM16B8CV1/D          |

| Serial Communications Interface (SCI) Block Guide           | V04     | S12SCIV4/D               |

| 32Kbyte Flash EEPROM (FTS32K) Block Guide                   | V01     | S12FTS32KV1/D            |

| Voltage Regulator (VREG_U) Block Guide                      | V01     | S12VREGUV1/D             |

| Oscillator (OSC) Block Guide                                | V02     | S12OSCV2/D               |

| Port Integration Module (PIM_9UF32) Block Guide             | V02     | S12UF32PIMV2/D           |

| USB 2.0 Device Controller (USB20D6E2F) Block Guide          | V01     | S12USB20D6E2FV1/D        |

| Integrated Queue Controller (IQUE) Block Guide              | V01     | S12IQUEV1/D              |

| ATA5 Host Controller (ATA5HC) Block Guide                   | V01     | S12ATA5HCV1/D            |

| Smart Media Host Controller (SMHC) Block Guide              | V01     | S12SMHCV1/D              |

| Secure Digital Host Controller (SDHC) Block Guide           | V01     | S12SDHCV1/D              |

| Memory Stick Host Controller (MSHC) Block Guide             | V01     | S12MSHCV1/D              |

| Compact Flash Host Controller (CFHC) Block Guide            | V01     | S12CFHCV1/D              |

| SM RAM (SMRAM3P5K2E) Block Guide                            | V01     | S12SMRAM3P5K2EV1/D       |

Table 0-1

Document References

Since the device interfaces with several external industrial standards, please refer to the following for details about those interface standards:

- "Information Technology AT Attachment with Packet Interface 5 (ATA/ATAPI5)," T13/1321D rev 3, 29 February, 2000, ANSI.

- "CF+ and CompactFlash Specification," rev. 2.0 5/2003, CompactFlash Association.

- "Memory Stick Information for Developers," ver. 1.3, 2000, Sony Corp.

- "The MultiMediaCard system specification," ver. 3.0, 1/2001, MMCA Technical Committee.

- "SD Memory Card Specifications," ver. 1.0, March 2000, SD Group.

- "Smart Media Electrical Specifications," ver. 1.0, May 19, 1999, SSFDC Forum Technical Committee.

- "Universal Serial Bus Specification," rev. 2.0, 27 April 2000, Compaq, Hewlett-Packard, Intel, Lucent, Microsoft, NEC, Philips.

# **Part Number**

Figure 0-1 provides an ordering number example.

# Figure 0-1 Order Part Number Coding

**Table 0-2** lists the part number coding based on the package.

Table 0-2 Part Number Coding

| Part Number  | Package | Description |

|--------------|---------|-------------|

| MC9S12UF32PB | 64LQFP  | MC9S12UF32  |

| MC9S12UF32PU | 100LQFP | MC9S12UF32  |

# **Section 1 Introduction**

# 1.1 Overview

The MC9S12UF32 microcontroller unit (MCU) is USB2.0 device for memory card reader and ATA/ATAPI interface applications. This device is composed of standard on-chip modules including a 16-bit central processing unit (HCS12 CPU), 32k bytes of Flash EEPROM, 3.5k bytes of RAM, USB2.0 interface, Integrated Queue Controller (IQUE) block with 1.5k bytes RAM buffer for USB Bulk data transport, ATA5 interface, Compact Flash interface, SD/MMC interface, SmartMedia interface, Memorystick interface, a 16-bit 8-channel timer, Serial Communication Interface, 73 discrete digital I/O channels and 2 input only channels<sup>1</sup>. The MC9S12UF32 has full 16-bit internal data paths throughout.

# 1.2 Features

- HCS12 Core

- 16-bit HCS12 CPU

- i. Upward compatible with M68HC11 instruction set

- ii. Interrupt stacking and programmer's model identical to M68HC11

- iii. Instruction queue

- iv. Enhanced indexed addressing

- Multiplexed External Bus Interface (MEBI)

- Memory Mapping Control (MMC)

- Interrupt Control (INT)

- Single-wire Background Debug Mode (BDM)

- On-chip hardware Breakpoints (BKP)

- Clock and Reset Generator (CRG\_U)

- Clock Throttle to prescale the oscillator clock or 60Mhz clock from USB20D6E2F.

- COP watchdog

- Real Time Interrupt

- Memory

- 32K Flash EEPROM

- Internal program/erase voltage generation

- Security and Block Protect bits

- 3.5K byte RAM

### NOTES:

1. Not all functions are available simultaneously.

- Used as a contiguous 3.5k byte SRAM with misaligned access support

- Configurable to 1084 byte SRAM and 2000 x 10 bit SRAM for Smartmedia logical to physical address translation and parity generation/checking support.

- 1.5K byte Queue RAM

- SRAM used as USB endpoint buffer, access is arbitrated by IQUE module

- 8-channel Timer (TIM)

- Eight input capture/output compare channels

- Clock prescaling

- 16-bit counter

- 16-bit pulse accumulator

- Serial Interface

- Asynchronous serial communication interface (SCI)

- Internal Regulator (VREG\_U)

- Input voltage range from 4.25V to 5.5V

- Separate Regulation circuits

- 2.5V Regulator for Core Logic and memory

- 3.3V Regulator for USB2.0 physical layer interface

- 3.3V Regulator with off-chip NMOS driver for I/O and memory cards

- Power on Reset detection

- Integrated Queue Controller (IQUE)

- Provide block data transfer without CPU intervention

- Four independent queue channels for data transfer between Queue RAM and peripherals

- Unified Queue RAM Memory which can be allocated to different usb endpoints and storage interface module

- Programming model allows implementation of double buffering for maximum burst data throughput of 60M bytes per second between USB20D6E2F and one of the Storage Interfaces

- Universal Serial Bus 2.0 (USB20D6E2F)

- Intergrated USB2.0 Physical Layer Transceiver (USB20PHY) for High speed and Full Speed operations

- USB 2.0 Serial Interface Engine (USB20SIE) for High Speed and Full Speed operations compatible

- Endpoint 0 for Control IN and OUT operation

- Endpoint 2 and 3 are configurable for Bulk, ISO or Interrupt IN/OUT operation

- Endpoint buffer with programmable size residing in Queue RAM for endpoints 4 and 5

- Endpoint 0 IN, endpoint 0 OUT, endpoint 2 and endpoint 3 each has an independent 64 bytes fixed endpoint buffer.

- ATA5 Host Controller Interface (ATA5HC)

- Support PIO mode 0 to 4

- Support Multi-word DMA mode 0 to 2

- Support UDMA mode 0 to 4 (Up to 60M Bytes/sec at UDMA mode 4)

- Sector data can be transferred to and from USB endpoint buffer without CPU intervention using IQUE module

- Compact Flash Host Controller Interface (CFHC)

- Support Compact Flash memory and I/O mode access operations per CFA specification 1.4

- Sector data can be transferred to and from USB endpoint buffer without CPU intervention using IQUE module

- Secure Digital and Multimedia Card Host Controller Interface (SDHC)

- Compatible with the MMC System Specification Version 3.0

- Compatible with the SD Memory Card Specification 1.0

- Sector data can be transferred to and from USB endpoint buffer without CPU intervention using IQUE module

- Smartmedia Host Controller Interface (SMHC)

- Compatible with SmartMedia Specification 1.0

- Support SmartMedia with memory size of 4M Bytes to 128M Bytes

- Sector data can be transferred to and from USB endpoint buffer without CPU intervention using IQUE module

- Memorystick Host Controller Interface (MSHC)<sup>1</sup>

- Compatible with Memory Stick Standard 1.3

- Sector data can be transferred to and from USB endpoint buffer without CPU intervention using IQUE module

- Two Asynchronous External Interrupt pins

- XIRQ

- IRQ<sup>2</sup>

- 100-Pin LQFP package

- Up to 6 I/O pins with 5V only drive capability and 2 input only 5V pins.

- Up to 67 I/O pins with 3.3V/5V input and drive capability.

#### NOTES:

- 1. The Document for the Memory Stick Host Controller in the 912UF32 will be available to users who have obtained a formal license of Memory Stick from Sony. Memory Stick is a Sony technology.

- 2. IRQ is not available in 64 pin device.

- 64-Pin LQFP package

- User selectable subset of modules available.

- Up to 6 I/O pins with 5V only drive capability and 1 input only 5V pin.

- Up to 35 I/O pins with 3.3V/5V input and drive capability.

- Operating frequency

- Maximum 60MHz equivalent to 30MHz CPU Bus Speed for single chip modes.

- 60MHz operation for IQUE module and storage interface modules attached to IQUE.

# 1.3 Modes of Operation

- Normal modes

- Normal Single-Chip Mode

- Normal Expanded Wide Mode

- Normal Expanded Narrow Mode

- Emulation Expanded Wide Mode

- Emulation Expanded Narrow Mode

- Special Operating Modes

- Special Single-Chip Mode with active Background Debug Mode

- Special Test Mode (Freescale use only)

- Special Peripheral Mode (Freescale use only)

- Each of the above modes of operation can be configured for two Low power sub-modes

- Stop Mode

- Wait Mode

- Secure operation, preventing the unauthorized read and write of the flash memory contents.

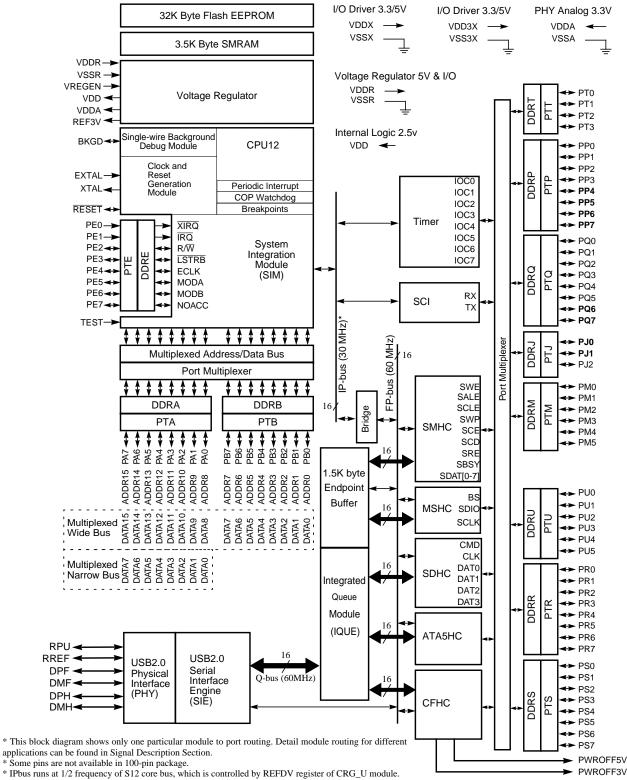

# **1.4 Block Diagram**

\*Qbus refers to the data transfer channels between IQUE and USB/ATA5HC/CFHC/MSHC/SDHC/SMHC.

### Figure 1-1 MC9S12UF32 Block Diagram

System on a Chip Guide — 9S12UF32DGV1/D V01.05

# 1.5 Device Memory Map

**Table 1-1** shows the device memory map of the MC9S12UF32 after reset.

| Address         | Module                                                                                                                                                                                                                                | Size<br>(Bytes) | Mapping<br>Register(s) |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------|

| \$0000 - \$000F | HCS12 Multiplexed External Bus Interface                                                                                                                                                                                              | 16              |                        |

| \$0010 - \$0014 | HCS12 Module Mapping Control                                                                                                                                                                                                          | 5               |                        |

| \$0015 - \$0016 | HCS12 Interrupt                                                                                                                                                                                                                       | 2               |                        |

| \$0017 - \$0018 | Reserved                                                                                                                                                                                                                              | 2               |                        |

| \$0019 - \$0019 | Voltage Regulator (VREG_U)                                                                                                                                                                                                            | 1               |                        |

| \$001A - \$001B | Device ID register (PARTID)                                                                                                                                                                                                           | 2               |                        |

| \$001C - \$001D | HCS12 Module Mapping Control                                                                                                                                                                                                          | 2               |                        |

| \$001E          | HCS12 Multiplexed External Bus Interface                                                                                                                                                                                              | 1               |                        |

| \$001F          | HCS12 Interrupt                                                                                                                                                                                                                       | 1               |                        |

| \$0020 - \$0027 | Reserved                                                                                                                                                                                                                              | 8               |                        |

| \$0028 - \$002F | HCS12 Breakpoint                                                                                                                                                                                                                      | 8               |                        |

| \$0030 - \$0033 | Reserved                                                                                                                                                                                                                              | 4               |                        |

| \$0034 - \$003F | Clock and Reset Generator (RTI, COP)                                                                                                                                                                                                  | 12              |                        |

| \$0040 - \$006F | Standard Timer 16-bit 8 channels (TIM)                                                                                                                                                                                                | 48              |                        |

| \$0070 - \$00C7 | Reserved                                                                                                                                                                                                                              | 88              |                        |

| \$00C8 - \$00CF | Serial Communication Interface (SCI)                                                                                                                                                                                                  | 8               | INITRG                 |

| \$00D0 - \$00FF | Reserved                                                                                                                                                                                                                              | 48              |                        |

| \$0100 - \$010F | Flash Control Register                                                                                                                                                                                                                | 16              |                        |

| \$0110 - \$011B | Reserved                                                                                                                                                                                                                              | 12              |                        |

| \$011C - \$011F | RAM Control Register (SMRAM)                                                                                                                                                                                                          | 4               |                        |

| \$0120 - \$01BF | Reserved                                                                                                                                                                                                                              | 160             |                        |

| \$01C0- \$01FF  | ATA Host Controller (ATA5HC)                                                                                                                                                                                                          | 64              |                        |

| \$0200 - \$023F | Integrated Queue 4 channels (IQUE)                                                                                                                                                                                                    | 64              |                        |

| \$0240 - \$027F | Port Integration Module (PIM)                                                                                                                                                                                                         | 64              |                        |

| \$0280 - \$029F | CompactFlash Host Controller (CFHC)                                                                                                                                                                                                   | 32              |                        |

| \$02A0 - \$02AF | MemoryStick Host Controller (MSHC)                                                                                                                                                                                                    | 16              |                        |

| \$02B0 - \$02BF | SmartMedia Host Controller (SMHC)                                                                                                                                                                                                     | 16              |                        |

| \$02C0 - \$02DF | Secure Digital Host Controller (SDHC)                                                                                                                                                                                                 | 32              |                        |

| \$02E0 - \$02FF | Reserved                                                                                                                                                                                                                              | 32              |                        |

| \$0300 - \$03FF | USB 2.0 (USB20D6E2F)                                                                                                                                                                                                                  | 256             |                        |

| \$0000 - \$07FF | QRAM array (IQUE)<br>1.5K-byte 16-bit SRAM in IQUE module \$0000 - \$05FF<br>0.5K-byte reserved \$0600-\$07FF                                                                                                                         | 2048            | INITEE <sup>1</sup>    |

| \$0800 - \$1BC3 | RAM array (SMRAM3P5K2E)<br>configurable as 2500-byte16-bit SRAM \$1200 - \$1BC3<br>or two 10-bit even byte aligned SRAM located at \$0800 -<br>\$0FCF and \$1000 - \$17CF<br>Unmapped locations in range \$0800 - \$1BC3 are reserved | 5060            | INITRM                 |

| \$1BC4 - \$1FFF | RAM array (SMRAM3P5K2E)<br>1084-byte 16-bit SRAM                                                                                                                                                                                      | 1084            |                        |

# Table 1-1 Device Memory Map

| \$1800 - \$3FFF | Reserved                                                                         | 10240 |        |

|-----------------|----------------------------------------------------------------------------------|-------|--------|

| \$4000 - \$7FFF | 16K-byte Flash EEPROM Array (addresses valid only when ROMHM=0 of register MISC) | 16384 | PPAGE, |

| \$8000 - \$BFFF | 16K-byte Paged Window                                                            | 16384 | MISC   |

| \$C000 - \$FFFF | 16K-byte Flash EEPROM Array                                                      | 16384 |        |

#### Table 1-1 Device Memory Map

NOTES:

QRAM starting address is controlled by INITEE register and QRAM has the same priority as EEPROM memory block. For details about signal priority, please refer to HCS12 MMC Block Guide.

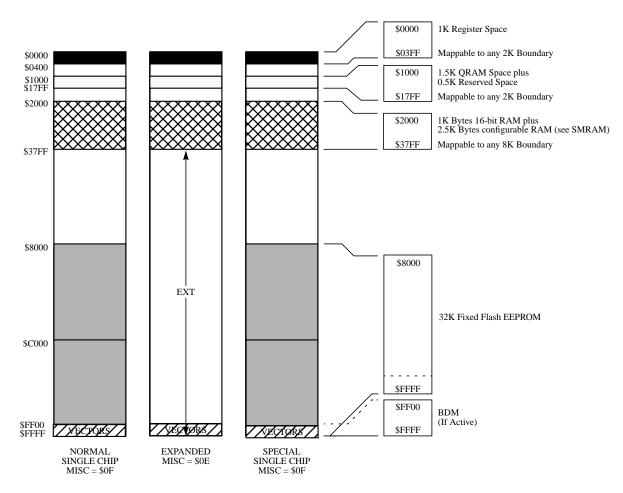

The figure shows an example of an application memory map with the following register setting. This is not the map out of reset.

$\begin{array}{l} INITRG = \$00\\ INITRM = \$20\\ INITEE = \$11\\ PPAGE = \$3E \end{array}$

# 1.5.1 Detailed Register Map

# \$0000 - \$000F

# MEBI map 1 of 3 (HCS12 Multiplexed External Bus Interface)

| Address         Name         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         Bit 0           \$0000         PORTA         Read:<br>Write:         Bit 7         6         5         4         3         2         1         Bit 0           \$0001         PORTB         Read:<br>Write:         Bit 7         6         5         4         3         2         1         Bit 0           \$0002         DDRA         Read:<br>Write:         Bit 7         6         5         4         3         2         1         Bit 0           \$0002         DDRA         Read:<br>Write:         Bit 7         6         5         4         3         2         1         Bit 0           \$0003         DDRB         Read:<br>Write:         Bit 7         6         5         4         3         2         1         Bit 0           \$0004 -<br>\$0007         Reserved         Read:<br>Write:         Bit 7         6         5         4         3         2         Bit 1         Bit 0           \$0008         PORTE         Read:<br>Write:         Bit 7         6         5         4         3         Bit 2         0         0 <th>\$0000<br/>\$0001<br/>\$0002</th> | \$0000<br>\$0001<br>\$0002 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| \$0000       PORIA       Write:       Bit 7       6       5       4       3       2       1       Bit 0         \$0001       PORTB       Read:       Write:       Bit 7       6       5       4       3       2       1       Bit 0         \$0002       DDRA       Read:       Write:       Bit 7       6       5       4       3       2       1       Bit 0         \$0002       DDRA       Read:       Write:       Bit 7       6       5       4       3       2       1       Bit 0         \$0003       DDRB       Read:       Bit 7       6       5       4       3       2       1       Bit 0         \$0004 -       Reserved       Read:       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0 <td>\$0001<br/>\$0002</td>                                                                                                                                                                              | \$0001<br>\$0002           |

| \$0001PORTBWrite:Bit 7654321Bit 0\$0002DDRARead:<br>Write:Bit 7654321Bit 0\$0003DDRBRead:<br>Write:Bit 7654321Bit 0\$0004 -<br>\$0007ReservedRead:<br>Write:00000000\$0008PORTERead:<br>Write:Bit 7654321Bit 0\$0008PORTERead:<br>Write:Bit 765432Eit 1Bit 0\$0009DDRERead:<br>Write:Bit 765432Eit 1Bit 0\$0000APEARRead:<br>Write:NOACCE0PIPOENECLKLSTRE<br>LSTRERDWE00\$000APEARRead:<br>Write:NOACCE0PIPOENECLKLSTRE<br>LSTRERDWE00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | \$0002                     |

| \$0002DDRAWrite:Bit 7654321Bit 0\$0003DDRBRead:<br>Write:Bit 7654321Bit 0\$0004 -<br>\$0007ReservedRead:<br>Write:00000000\$0008PORTERead:<br>Write:Bit 765432Bit 1Bit 0\$0009DDRERead:<br>Write:Bit 765432Eit 1Bit 0\$0009DDRERead:<br>Write:Bit 76543Bit 200\$000APEARRead:<br>Write:NOACCE0PIPOENECLKLSTRE<br>LSTRERDWE00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |

| \$0003DDRBWrite:Bit 7654321Bit 0\$0004 -<br>\$0007ReservedRead:<br>Write:00000000\$0008PORTERead:<br>Write:Bit 765432Bit 1Bit 0\$0009DDRERead:<br>Write:Bit 765432Dit 1Bit 0\$000APEARRead:<br>Write:NOACCE0PIPOENECLKLSTRE<br>LSTRERDWE00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | \$0003                     |

| \$0007ReservedWrite:Image: Constraint of the servedWrite:Image: Constraint of the servedImage: Constraint of the served\$0008PORTERead:<br>Write:Bit 765432Bit 1Bit 0\$0009DDRERead:<br>Write:Bit 76543Bit 200\$000APEARRead:<br>Write:NOACCE0PIPOENECLKLSTRE<br>LSTRERDWE00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |

| \$0007Write:Read:<br>Write:Bit 765432Bit 1Bit 0\$0008PORTERead:<br>Write:Bit 765432Bit 1Bit 0\$0009DDRERead:<br>Write:Bit 76543Bit 200\$000APEARRead:<br>Write:NOACCE0PIPOENECLKLSTRERDWE00\$000APEARRead:<br>Write:0000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | \$0004 -                   |

| \$0008     PORTE     Write:     Bit 7     6     5     4     3     2       \$0009     DDRE     Read:<br>Write:     Bit 7     6     5     4     3     2     0     0       \$0009     DDRE     Read:<br>Write:     Bit 7     6     5     4     3     Bit 2     0     0       \$000A     PEAR     Read:<br>Write:     NOACCE     0     PIPOE     NECLK     LSTRE     RDWE     0     0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | \$0007                     |

| Write:Read:<br>Write:Bit 76543Bit 200\$000APEARRead:<br>Write:NOACCE0PIPOENECLKLSTRERDWE00\$ead:Write:Read:<br>Write:0PIPOENECLKLSTRERDWE00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | \$0008                     |

| \$0009     DDRE     Write:     Bit 7     6     5     4     3     Bit 2       \$000A     PEAR     Read:<br>Write:     NOACCE     0     PIPOE     NECLK     LSTRE     RDWE     0     0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | φ0008                      |

| \$000A PEAR Write: NOACCE PIPOE NECLK LSTRE RDWE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | \$0009                     |

| Read: 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | \$000A                     |

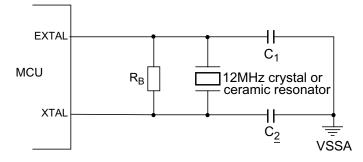

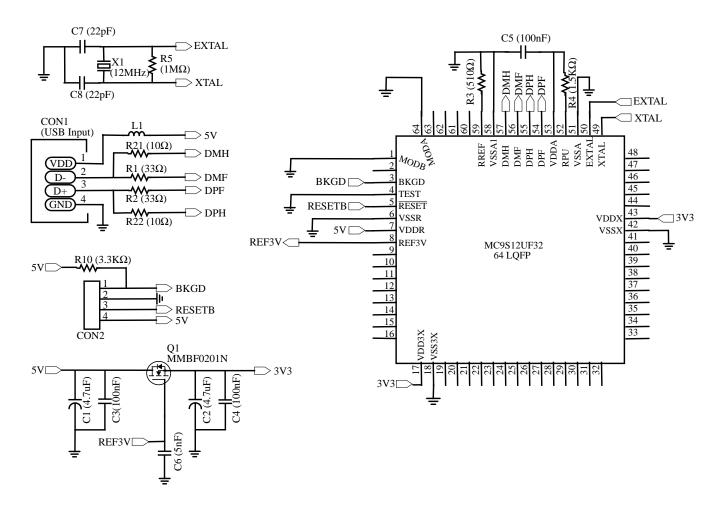

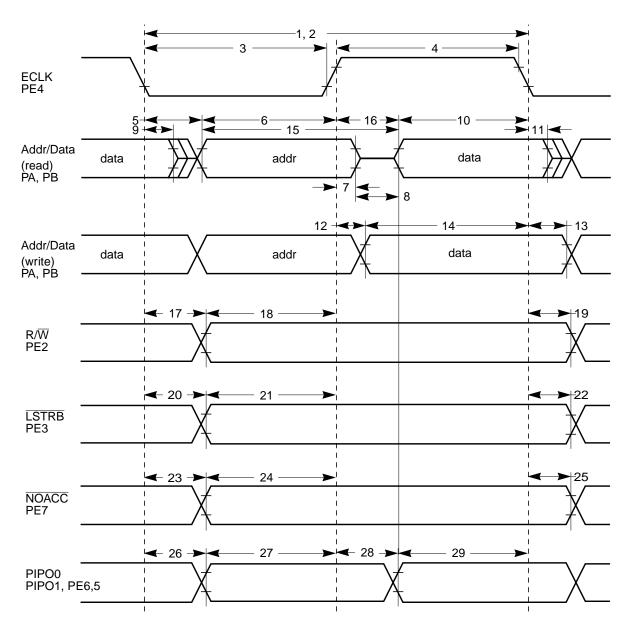

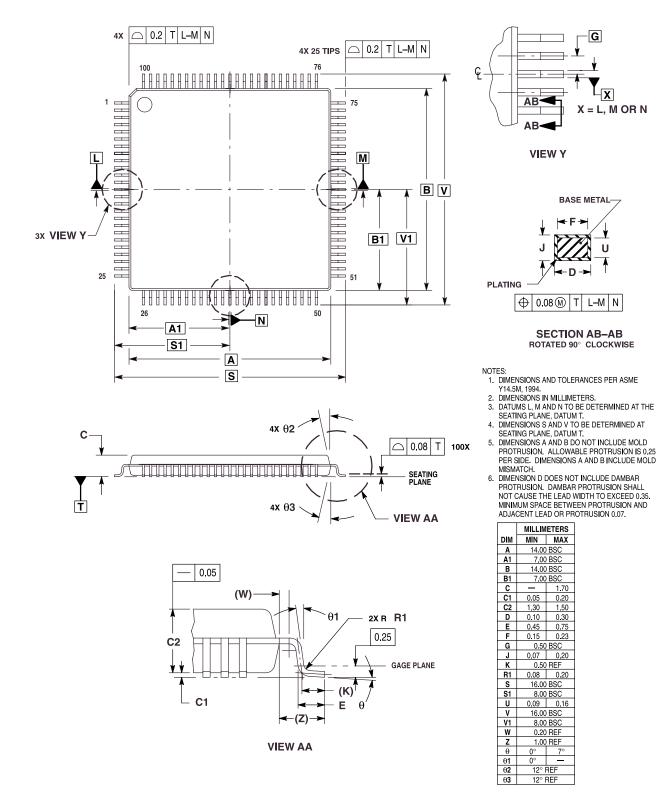

| SOOB MODE I MODE I MODE MODA — IVIS — IVIS — IMK I EME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>\$</b> \$\$\$ <b>\$</b> |