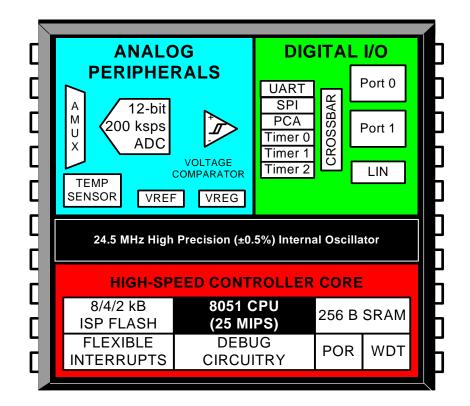

#### 8/4/2 kB ISP Flash MCU Family

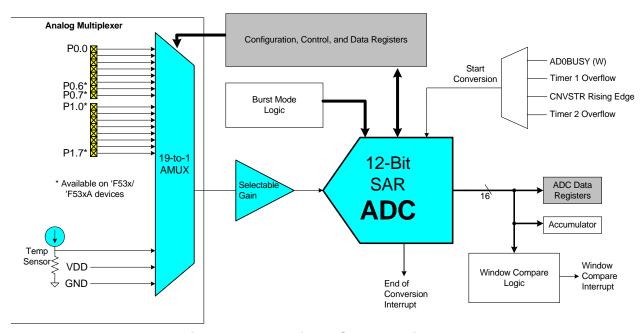

#### **Analog Peripherals**

- 12-Bit ADC

- ±1 LSB INL; no missing codes

- Programmable throughput up to 200 ksps

- Up to 6/16 external inputs

- Data dependent windowed interrupt generator

- Built-in temperature sensor

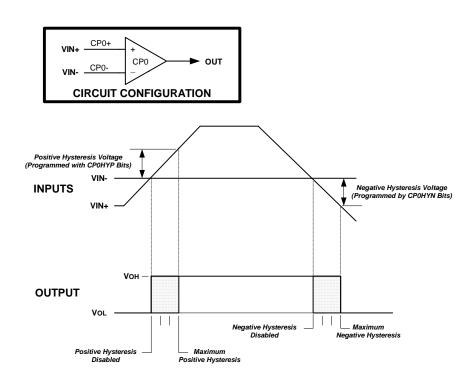

- Comparator

- Programmable hysteresis and response time

- Configurable as wake-up or reset source

- Low current

- POR/Brownout Detector

- Voltage Reference—1.5 and 2.2 V (programmable)

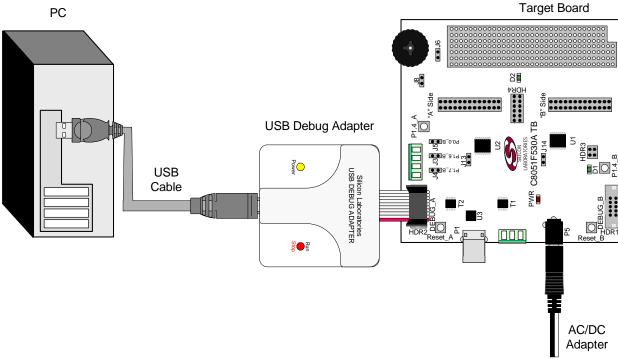

#### On-Chip Debug

- On-chip debug circuitry facilitates full-speed, nonintrusive in-system debug (No emulator required)

- Provides breakpoints, single stepping

- Inspect/modify memory and registers

- Complete development kit

#### Supply Voltage 1.8 to 5.25 V

Built-in LDO regulator

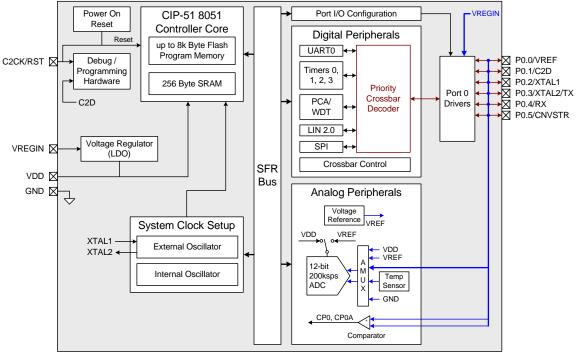

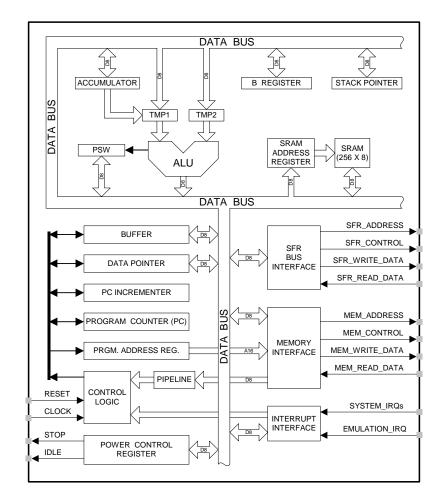

#### High Speed 8051 µC Core

- Pipelined instruction architecture; executes 70% of instructions in 1 or 2 system clocks

- Up to 25 MIPS throughput with 25 MHz system clock

- Expanded interrupt handler

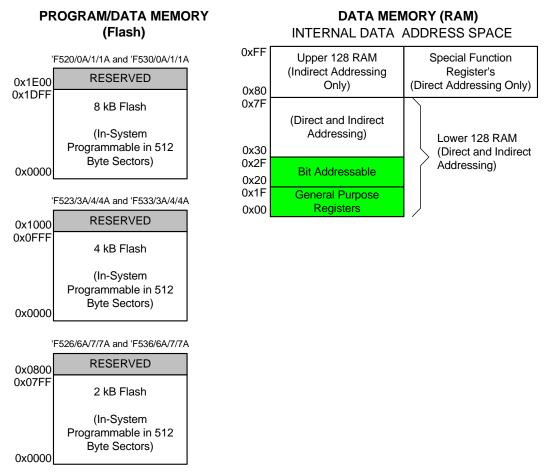

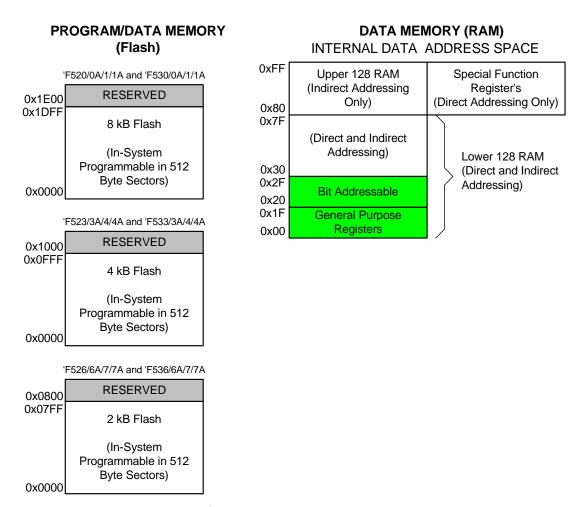

#### Memory

- 8/4/2 kB Flash; In-system byte programmable in 512 byte sectors

- 256 bytes internal data RAM

#### **Digital Peripherals**

- 16/6 port I/O; push-pull or open-drain, 5 V tolerant

- Hardware SPI™, and UART serial port

- Hardware LIN (both master and slave, compatible with V1.3 and V2.0)

- Three general purpose 16-bit counter/timers

- Programmable 16-bit counter/timer array with three capture/compare modules, WDT

#### **Clock Sources**

- Internal oscillators: 24.5 MHz ±0.5% accuracy supports UART and LIN-Master operation

- External oscillator: Crystal, RC, C, or Clock (1 or 2 pin modes)

- Can switch between clock sources on-the-fly

#### Packages:

- 10-Pin DFN (3 x 3 mm)

- 20-pin QFN (4 x 4 mm)

- 20-pin TSSOP

Temperature Range: -40 to +125 °C

**NOTES:**

# C8051F52x-53x

| 1. | System Overview                              | 15 |

|----|----------------------------------------------|----|

|    | 1.1. CIP-51™ Microcontroller                 |    |

|    | 1.1.1. Fully 8051 Compatible Instruction Set | 20 |

|    | 1.1.2. Improved Throughput                   |    |

|    | 1.1.3. Additional Features                   |    |

|    | 1.1.4. On-Chip Debug Circuitry               |    |

|    | 1.2. On-Chip Memory                          |    |

|    | 1.3. Operating Modes                         |    |

|    | 1.4. 12-Bit Analog to Digital Converter      | 24 |

|    | 1.5. Programmable Comparator                 |    |

|    | 1.6. Voltage Regulator                       |    |

|    | 1.7. Serial Port                             |    |

|    | 1.8. Port Input/Output                       |    |

| 2. | Absolute Maximum Ratings                     |    |

|    | Global DC Electrical Characteristics         |    |

|    | Pinout and Package Definitions               |    |

|    | 12-Bit ADC (ADC0)                            |    |

|    | 5.1. Analog Multiplexer                      |    |

|    | 5.2. Temperature Sensor                      |    |

|    | 5.3. ADC0 Operation                          |    |

|    | 5.3.1. Starting a Conversion                 |    |

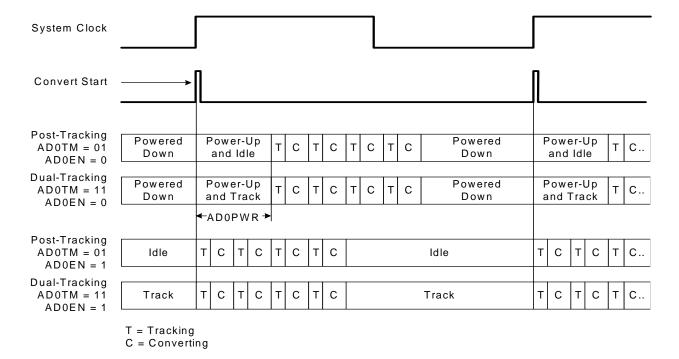

|    | 5.3.2. Tracking Modes                        |    |

|    | 5.3.3. Timing                                |    |

|    | 5.3.4. Burst Mode                            |    |

|    | 5.3.5. Output Conversion Code                | 53 |

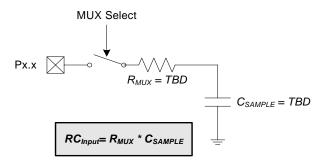

|    | 5.3.6. Settling Time Requirements            |    |

|    | 5.4. Selectable Gain                         |    |

|    | 5.4.1. Calculating the Gain Value            |    |

|    | 5.4.2. Setting the Gain Value                |    |

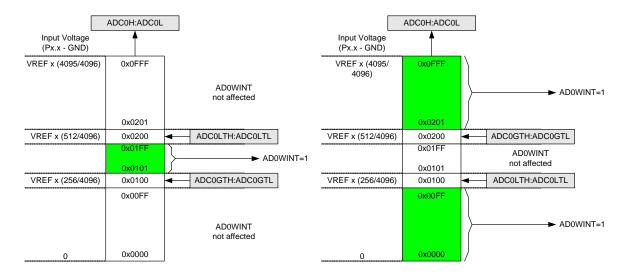

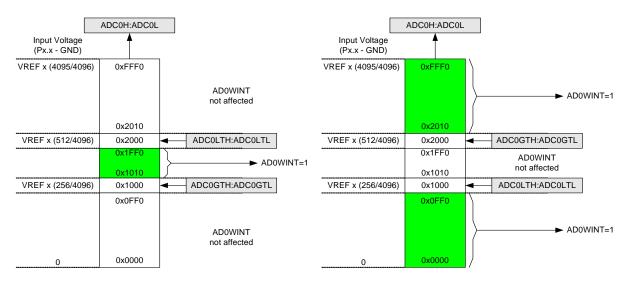

|    | 5.5. Programmable Window Detector            |    |

|    | 5.5.1. Window Detector In Single-Ended Mode  | 65 |

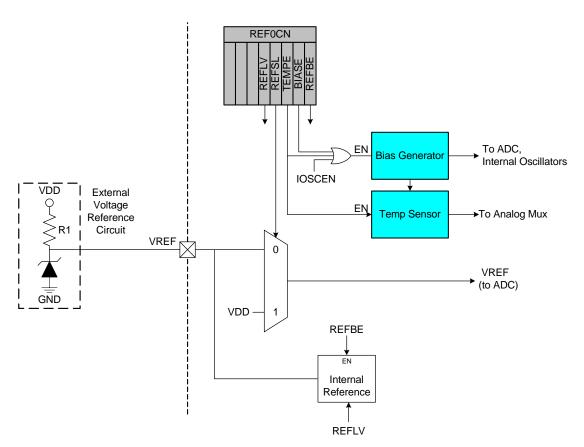

| 6. | Voltage Reference                            |    |

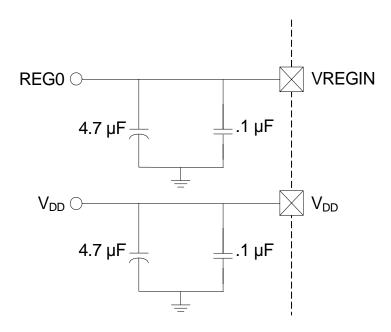

| 7. | Voltage Regulator (REG0)                     | 70 |

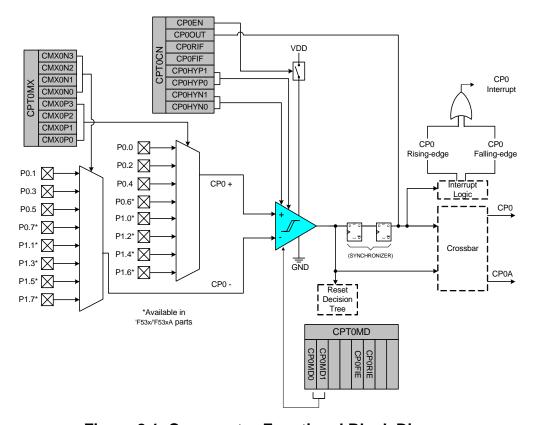

| 8. | Comparator                                   | 72 |

| 9. | CIP-51 Microcontroller                       | 78 |

|    | 9.1. Instruction Set                         | 79 |

|    | 9.1.1. Instruction and CPU Timing            | 79 |

|    | 9.1.2. MOVX Instruction and Program Memory   | 80 |

|    | 9.2. Register Descriptions                   | 83 |

|    | 9.3. Power Management Modes                  | 86 |

|    | 9.3.1. Idle Mode                             |    |

|    | 9.3.2. Stop Mode                             |    |

|    | 9.3.3. Suspend Mode                          |    |

| 10 | .Memory Organization and SFRs                |    |

|    | 10.1.Program Memory                          |    |

| 10.2.Data Memory                                                   | 90  |

|--------------------------------------------------------------------|-----|

| 10.3.General Purpose Registers                                     | 90  |

| 10.4.Bit Addressable Locations                                     |     |

| 10.5.Stack                                                         | 90  |

| 10.6.Special Function Registers                                    | 91  |

| 11. Interrupt Handler                                              |     |

| 11.1.MCU Interrupt Sources and Vectors                             |     |

| 11.2.Interrupt Priorities                                          |     |

| 11.3.Interrupt Latency                                             | 95  |

| 11.4.Interrupt Register Descriptions                               |     |

| 11.5.External Interrupts                                           | 101 |

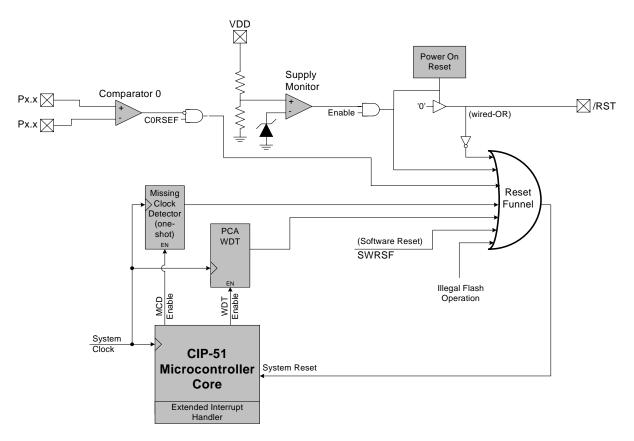

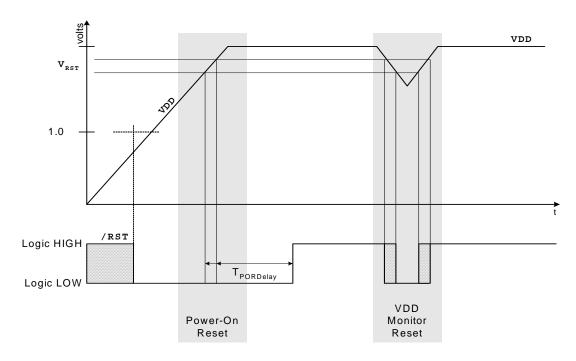

| 12. Reset Sources                                                  | 103 |

| 12.1.Power-On Reset                                                | 104 |

| 12.2.Power-Fail Reset / VDD Monitor                                | 105 |

| 12.3.External Reset                                                | 106 |

| 12.4.Missing Clock Detector Reset                                  | 106 |

| 12.5.Comparator Reset                                              | 106 |

| 12.6.PCA Watchdog Timer Reset                                      |     |

| 12.7.Flash Error Reset                                             | 107 |

| 12.8.Software Reset                                                | 107 |

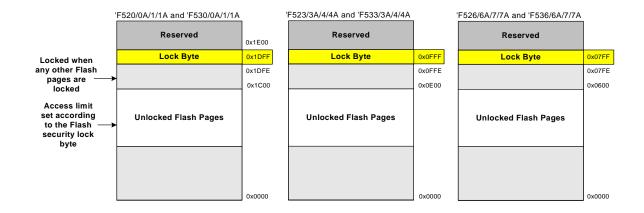

| 13. Flash Memory                                                   | 110 |

| 13.1.Programming The Flash Memory                                  | 110 |

| 13.1.1.Flash Lock and Key Functions                                | 110 |

| 13.1.2.Flash Erase Procedure                                       | 111 |

| 13.1.3.Flash Write Procedure                                       | 111 |

| 13.2.Flash Write and Erase Guidelines                              | 112 |

| 13.2.1.V <sub>DD</sub> Maintenance and the V <sub>DD</sub> monitor | 112 |

| 13.2.2.PSWE Maintenance                                            | 112 |

| 13.2.3.System Clock                                                | 113 |

| 13.3.Non-volatile Data Storage                                     | 114 |

| 13.4.Security Options                                              | 114 |

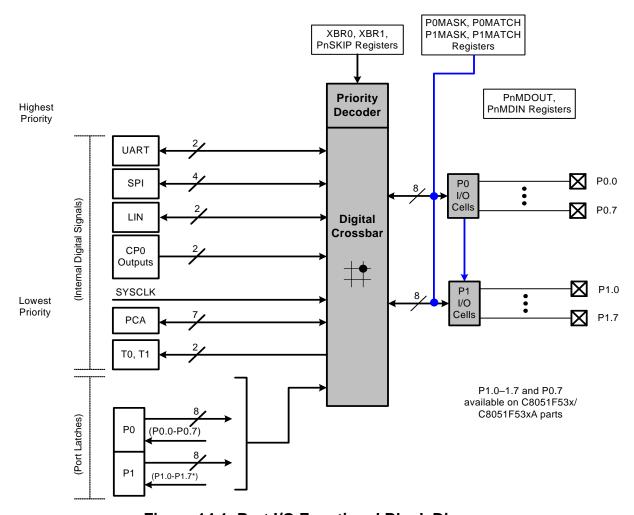

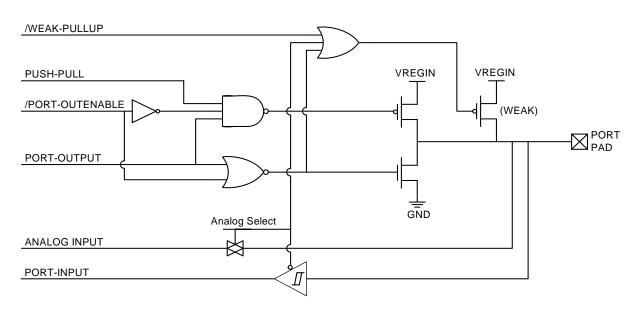

| 14. Port Input/Output                                              | 118 |

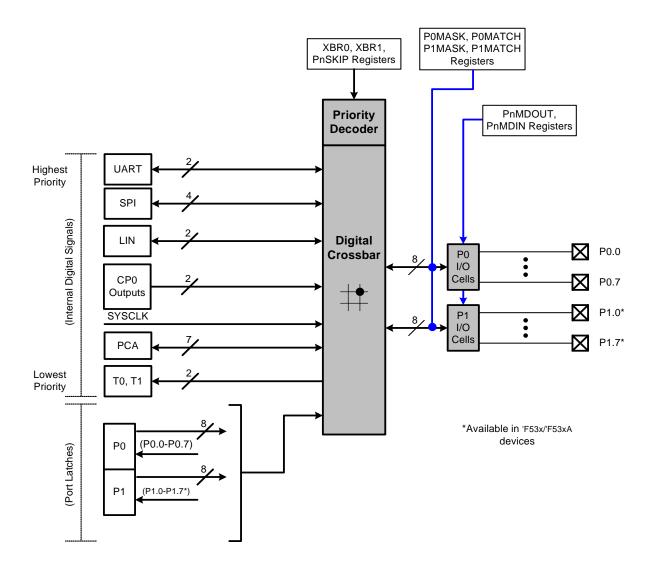

| 14.1.Priority Crossbar Decoder                                     | 120 |

| 14.2.Port I/O Initialization                                       |     |

| 14.3.General Purpose Port I/O                                      |     |

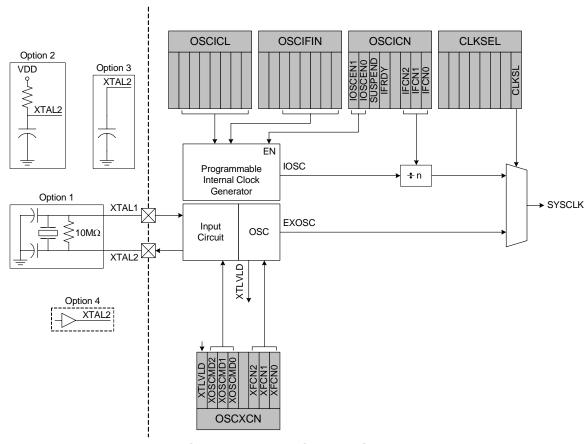

| 15. Oscillators                                                    | 135 |

| 15.1.Programmable Internal Oscillator                              | 135 |

| 15.1.1.Internal Oscillator Suspend Mode                            |     |

| 15.2.External Oscillator Drive Circuit                             |     |

| 15.2.1.Clocking Timers Directly Through the External Oscillator    |     |

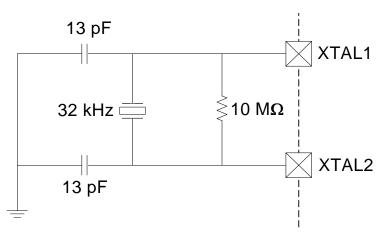

| 15.2.2.External Crystal Example                                    |     |

| 15.2.3.External RC Example                                         |     |

| 15.2.4.External Capacitor Example                                  |     |

| 15.3.System Clock Selection                                        |     |

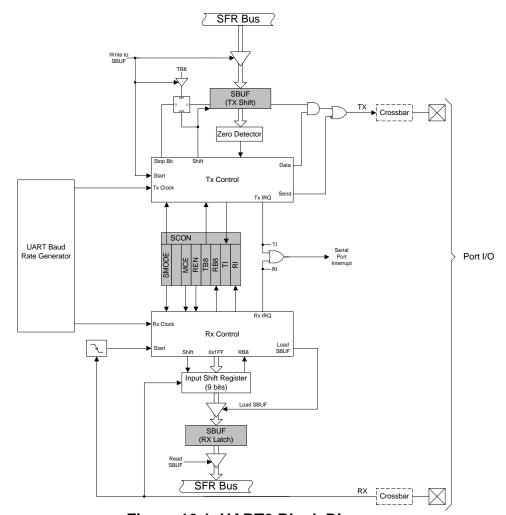

| 16. UART0                                                          | 146 |

# C8051F52x-53x

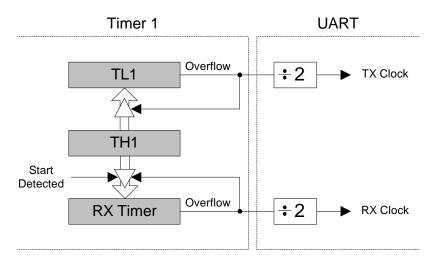

| 16.1.Enhanced Baud Rate Generation                          | 147 |

|-------------------------------------------------------------|-----|

| 16.2.Operational Modes                                      | 148 |

| 16.2.1.8-Bit UART                                           |     |

| 16.2.2.9-Bit UART                                           | 149 |

| 16.3.Multiprocessor Communications                          |     |

| 17. LIN (C8051F520/0A/3/3A/6/6A and C8051F530/0A/3/3A/6/6A) | 154 |

| 17.1. Software Interface with the LIN Peripheral            |     |

| 17.2.LIN Interface Setup and Operation                      |     |

| 17.2.1.Mode Definition                                      |     |

| 17.2.2.Baud Rate Options: Manual or Autobaud                | 155 |

| 17.2.3.Baud Rate Calculations - Manual Mode                 |     |

| 17.2.4.Baud Rate Calculations - Automatic Mode              |     |

| 17.3.LIN Master Mode Operation                              |     |

| 17.4.LIN Slave Mode Operation                               |     |

| 17.5.Sleep Mode and Wake-Up                                 |     |

| 17.6.Error Detection and Handling                           |     |

| 17.7.LIN Registers                                          |     |

| 17.7.1.LIN Direct Access SFR Registers Definition           | 161 |

| 17.7.2.LIN Indirect Access SFR Registers Definition         |     |

| 18. Enhanced Serial Peripheral Interface (SPI0)             |     |

| 18.1.Signal Descriptions                                    |     |

| 18.1.1.Master Out, Slave In (MOSI)                          | 172 |

| 18.1.2.Master In, Slave Out (MISO)                          | 172 |

| 18.1.3.Serial Clock (SCK)                                   |     |

| 18.1.4.Slave Select (NSS)                                   |     |

| 18.2.SPI0 Master Mode Operation                             | 173 |

| 18.3.SPI0 Slave Mode Operation                              | 174 |

| 18.4.SPI0 Interrupt Sources                                 | 175 |

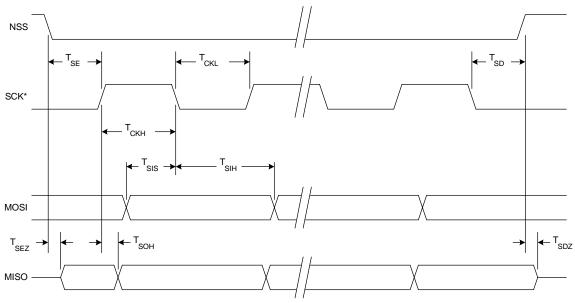

| 18.5.Serial Clock Timing                                    | 176 |

| 18.6.SPI Special Function Registers                         | 176 |

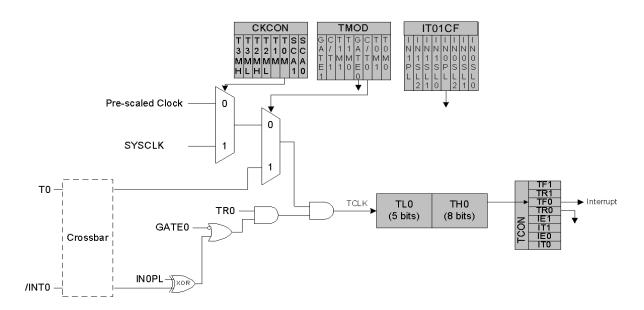

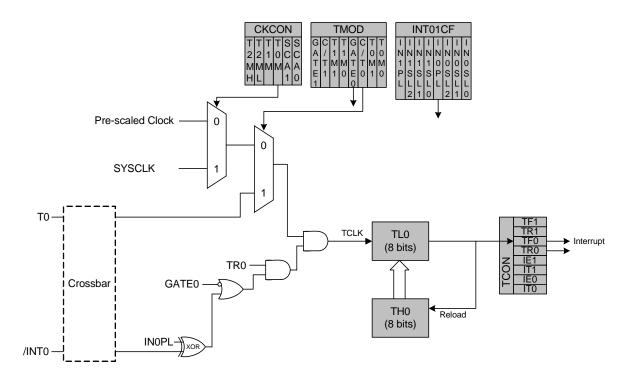

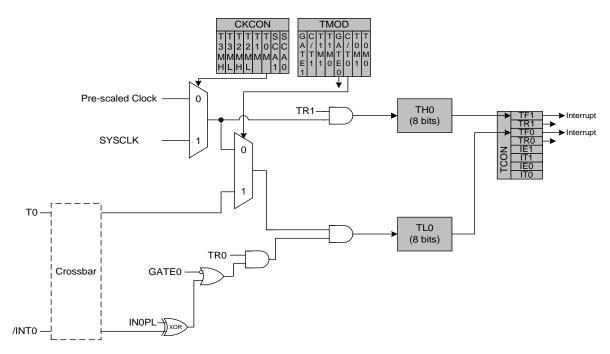

| 19. Timers                                                  | 184 |

| 19.1.Timer 0 and Timer 1                                    |     |

| 19.1.1.Mode 0: 13-bit Counter/Timer                         |     |

| 19.1.2.Mode 1: 16-bit Counter/Timer                         |     |

| 19.1.3.Mode 2: 8-bit Counter/Timer with Auto-Reload         |     |

| 19.1.4.Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)      |     |

| 19.2.Timer 2                                                |     |

| 19.2.1.16-bit Timer with Auto-Reload                        |     |

| 19.2.2.8-bit Timers with Auto-Reload                        |     |

| 19.2.3.External Capture Mode                                | 194 |

| 20. Programmable Counter Array (PCA0)                       |     |

| 20.1.PCA Counter/Timer                                      |     |

| 20.2.Capture/Compare Modules                                |     |

| 20.2.1.Edge-triggered Capture Mode                          |     |

| 20.2.2.Software Timer (Compare) Mode                        | 201 |

| 20.2.3.High Speed Output Mode                   | 202 |

|-------------------------------------------------|-----|

| 20.2.4.Frequency Output Mode                    |     |

| 20.2.5.8-Bit Pulse Width Modulator Mode         |     |

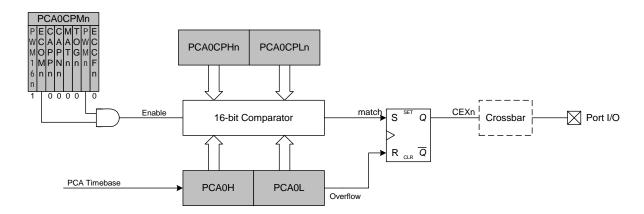

| 20.2.6.16-Bit Pulse Width Modulator Mode        |     |

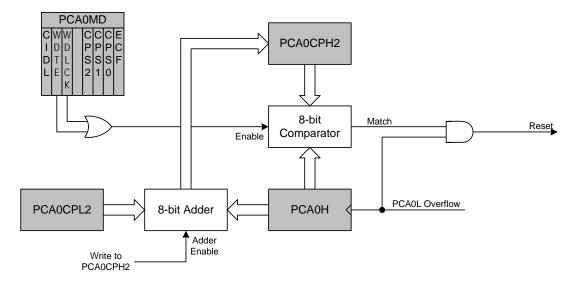

| 20.3.Watchdog Timer Mode                        | 205 |

| 20.3.1.Watchdog Timer Operation                 |     |

| 20.3.2.Watchdog Timer Usage                     |     |

| 20.4.Register Descriptions for PCA              | 209 |

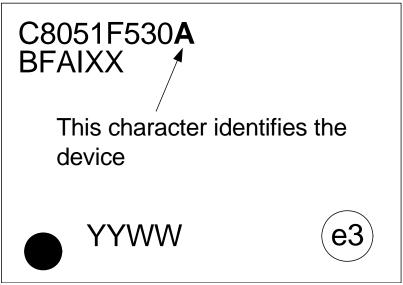

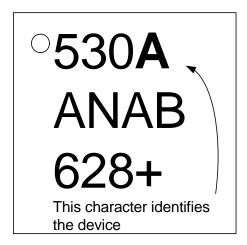

| 21. Device Specific Behavior                    |     |

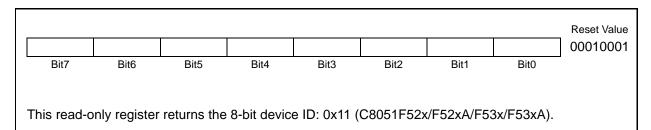

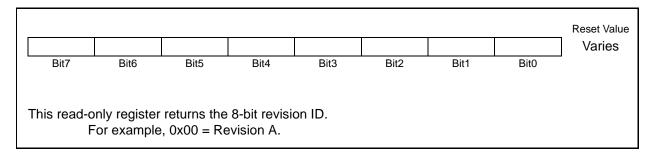

| 21.1.Device Identification                      |     |

| 21.2.Reset Pin Behavior                         | 214 |

| 21.3.Reset Time Delay                           | 214 |

| 21.4.UART Pins                                  |     |

| 21.5.LIN                                        | 215 |

| 21.5.1.Stop Bit Check                           |     |

| 21.5.2.Synch Break and Synch Field Length Check | 215 |

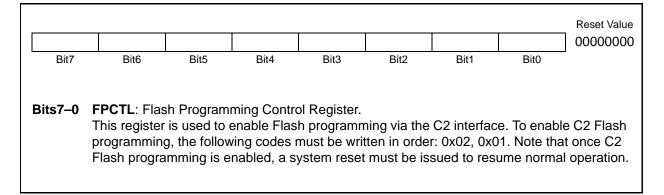

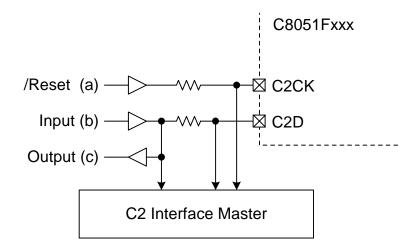

| 22. C2 Interface                                |     |

| 22.1.C2 Interface Registers                     |     |

| 22.2.C2 Pin Sharing                             | 218 |

| Document Change List                            |     |

| Contact Information                             | 220 |

# C8051F52x-53x

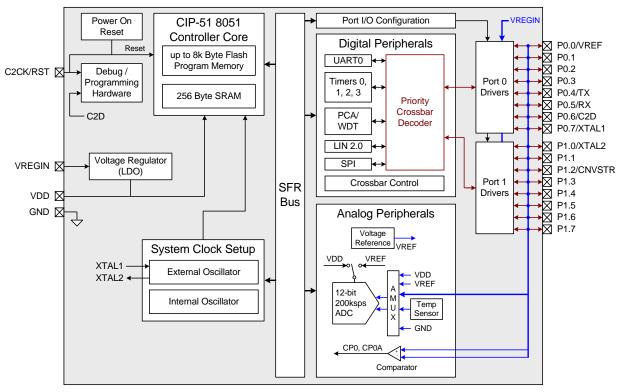

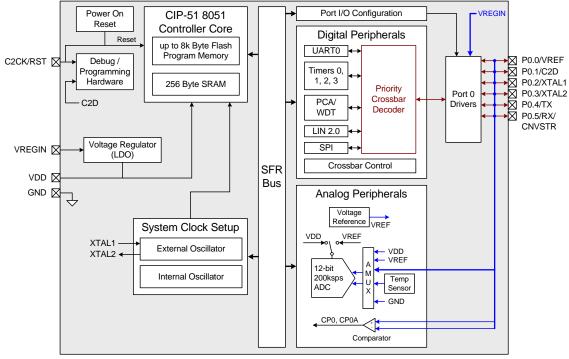

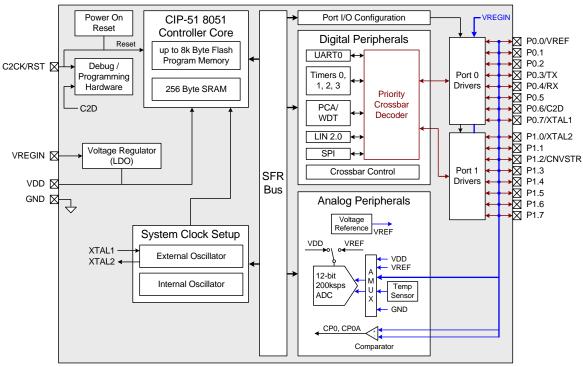

| 1. | System Overview                                                           |      |

|----|---------------------------------------------------------------------------|------|

|    | Figure 1.1. C8051F53xA Block Diagram                                      | . 18 |

|    | Figure 1.2. C8051F52xA Block Diagram                                      |      |

|    | Figure 1.3. C8051F53x Block Diagram                                       |      |

|    | Figure 1.4. C8051F52x Block Diagram                                       |      |

|    | Figure 1.5. Development/In-System Debug Diagram                           |      |

|    | Figure 1.6. Memory Map                                                    |      |

|    | Figure 1.7. 12-Bit ADC Block Diagram                                      |      |

|    |                                                                           |      |

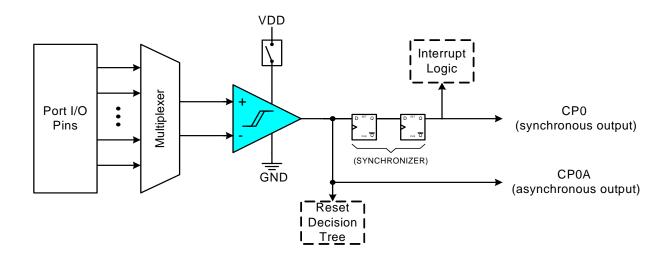

|    | Figure 1.8. Comparator Block Diagram                                      |      |

| 2  | Figure 1.9. Port I/O Functional Block Diagram                             | . 20 |

|    | Absolute Maximum Ratings Global DC Electrical Characteristics             |      |

|    |                                                                           |      |

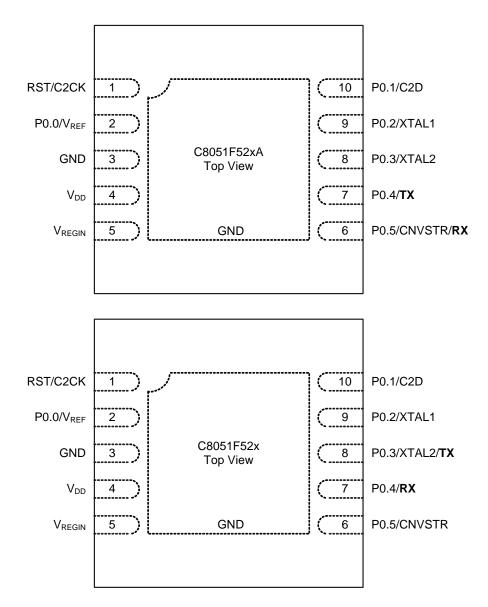

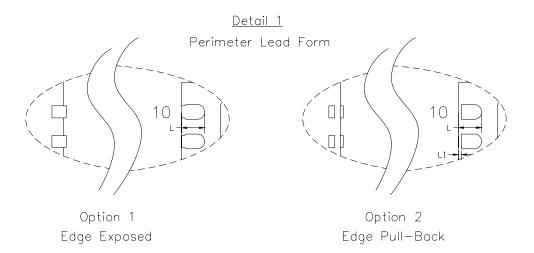

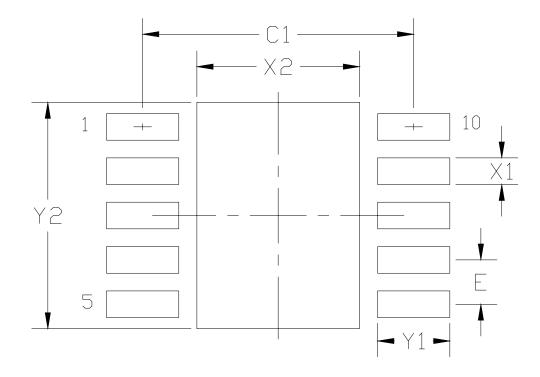

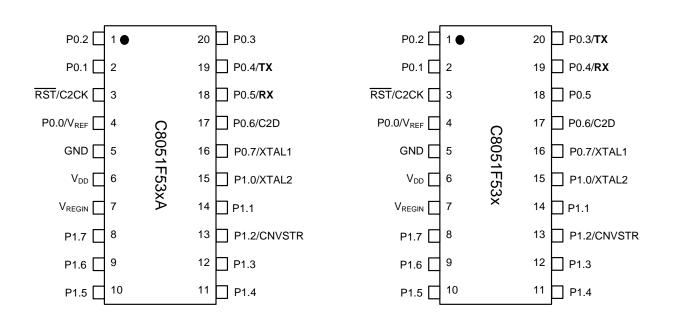

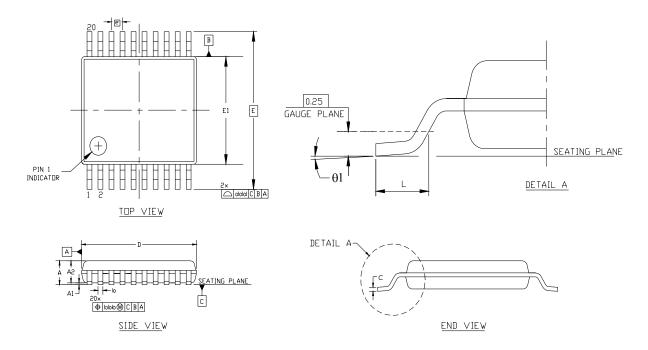

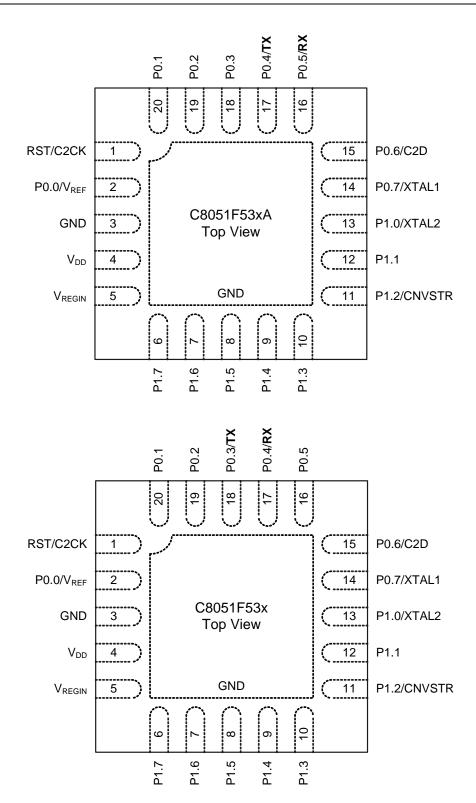

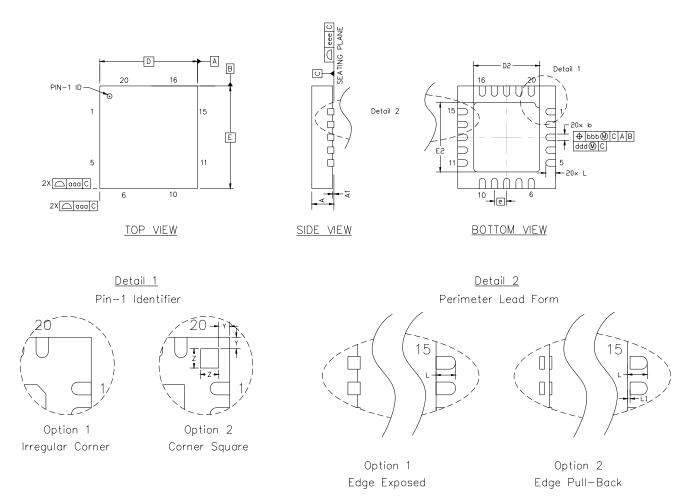

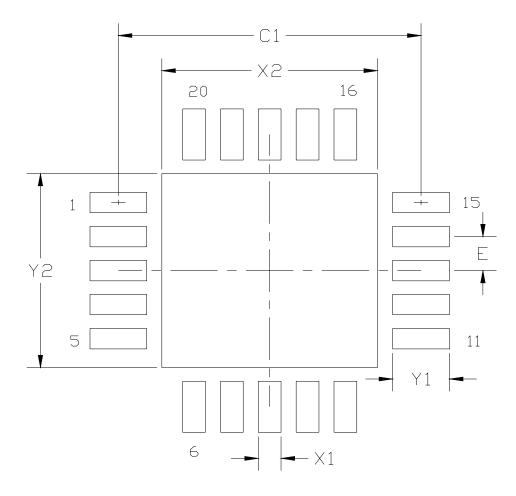

| 4. | Pinout and Package Definitions                                            | 20   |

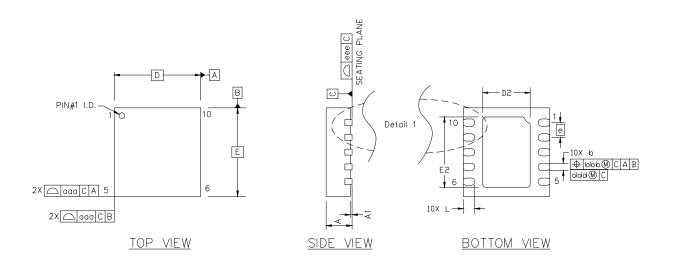

|    | Figure 4.1. DFN-10 Package Diagram*                                       |      |

|    | Figure 4.2. DFN-10 Landing Diagram                                        |      |

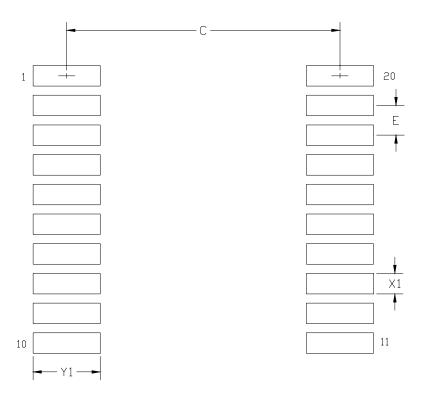

|    | Figure 4.3. TSSOP-20 Package Diagram                                      |      |

|    | Figure 4.4. TSSOP-20 Landing Diagram                                      | . 40 |

|    | Figure 4.5. QFN-20 Package Diagram*                                       |      |

| _  | Figure 4.6. QFN-20 Landing Diagram                                        | 46   |

| 5. | 12-Bit ADC (ADC0)                                                         |      |

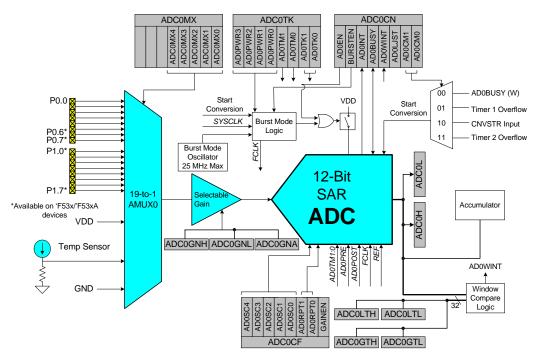

|    | Figure 5.1. ADC0 Functional Block Diagram                                 |      |

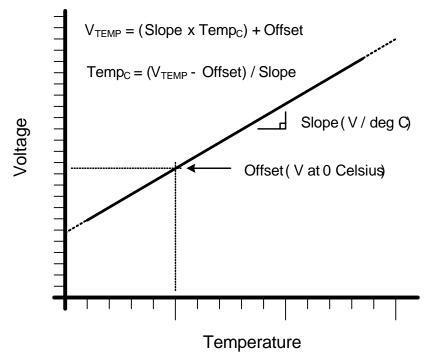

|    | Figure 5.2. Typical Temperature Sensor Transfer Function                  |      |

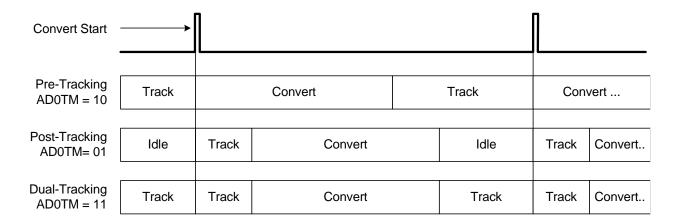

|    | Figure 5.3. ADC0 Tracking Modes                                           |      |

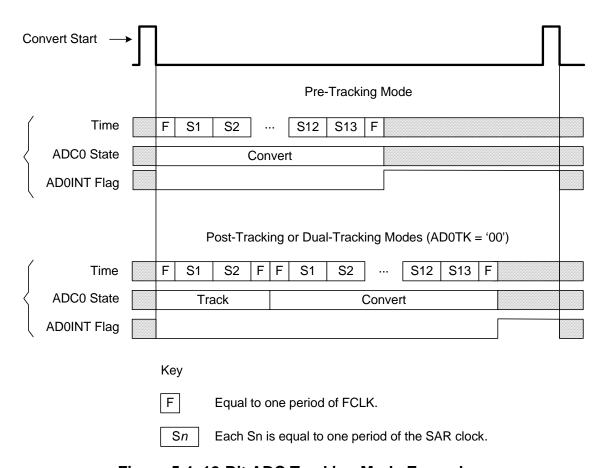

|    | Figure 5.4. 12-Bit ADC Tracking Mode Example                              |      |

|    | Figure 5.5. 12-Bit ADC Burst Mode Example with Repeat Count Set to 4      |      |

|    | Figure 5.6. ADC0 Equivalent Input Circuits                                |      |

|    | Figure 5.7. ADC Window Compare Example: Right-Justified Single-Ended Data |      |

|    | Figure 5.8. ADC Window Compare Example: Left-Justified Single-Ended Data  | . 65 |

| 6. | Voltage Reference                                                         |      |

|    | Figure 6.1. Voltage Reference Functional Block Diagram                    | . 67 |

| 7. | Voltage Regulator (REG0)                                                  |      |

|    | Figure 7.1. External Capacitors for Voltage Regulator Input/Output        | 70   |

| 8. | Comparator                                                                |      |

|    | Figure 8.1. Comparator Functional Block Diagram                           | . 72 |

|    | Figure 8.2. Comparator Hysteresis Plot                                    | . 73 |

| 9. | CIP-51 Microcontroller                                                    |      |

|    | Figure 9.1. CIP-51 Block Diagram                                          | . 78 |

| 10 | .Memory Organization and SFRs                                             |      |

|    | Figure 10.1. Memory Map                                                   | . 89 |

| 11 | .Interrupt Handler                                                        |      |

| 12 | Reset Sources                                                             |      |

|    | Figure 12.1. Reset Sources                                                | 103  |

|    | Figure 12.2. Power-On and V <sub>DD</sub> Monitor Reset Timing            |      |

| 13 | .Flash Memory                                                             |      |

|    | Figure 13.1. Flash Program Memory Map                                     | 114  |

| 14.1         | ort Input/Output                                                      |     |

|--------------|-----------------------------------------------------------------------|-----|

|              | igure 14.1. Port I/O Functional Block Diagram                         | 118 |

|              | igure 14.2. Port I/O Cell Block Diagram                               |     |

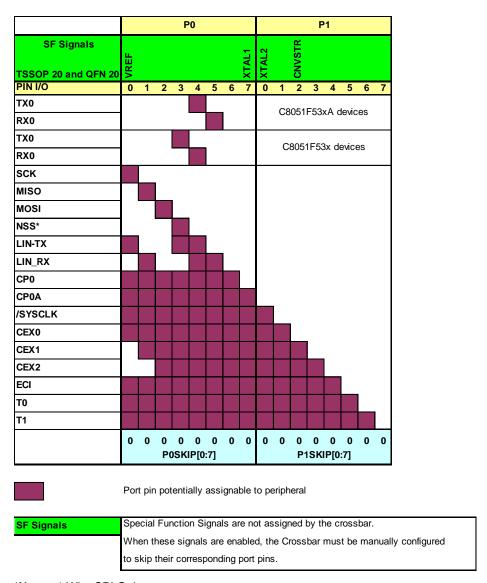

|              | igure 14.3. Crossbar Priority Decoder with No Pins Skipped            |     |

|              | (TSSOP 20 and QFN 20)120                                              |     |

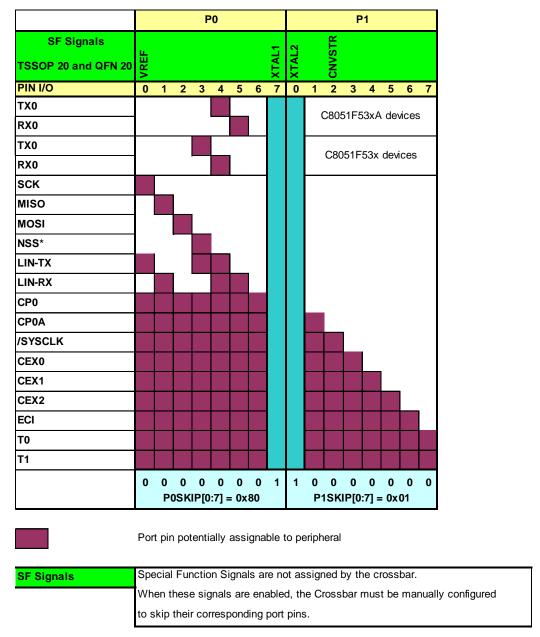

|              | igure 14.4. Crossbar Priority Decoder with Crystal Pins Skipped       |     |

|              | (TSSOP 20 and QFN 20)122                                              |     |

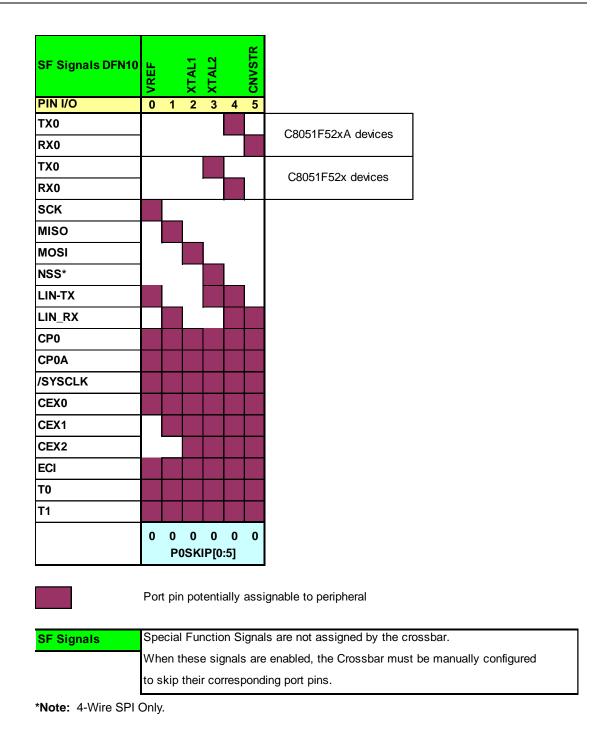

| I            | igure 14.5. Crossbar Priority Decoder with No Pins Skipped (DFN 10)   | 123 |

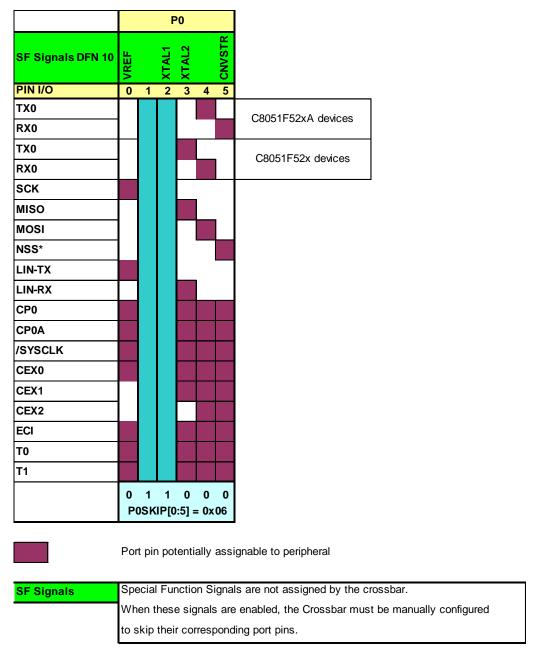

|              | igure 14.6. Crossbar Priority Decoder with Some Pins Skipped (DFN 10) |     |

|              | Oscillators ( )                                                       |     |

|              | igure 15.1. Oscillator Diagram                                        | 135 |

|              | igure 15.2. 32 kHz External Crystal Example                           |     |

|              | JÄRT0                                                                 |     |

|              | igure 16.1. UART0 Block Diagram                                       | 146 |

|              | igure 16.2. UART0 Baud Rate Logic                                     |     |

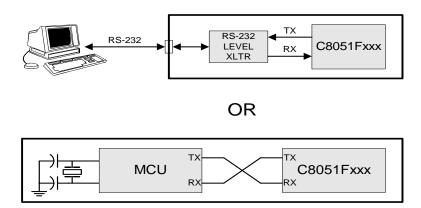

|              | igure 16.3. UART Interconnect Diagram                                 |     |

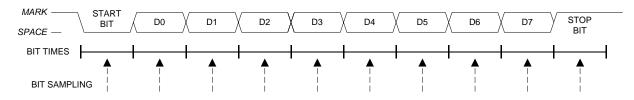

|              | igure 16.4. 8-Bit UART Timing Diagram                                 |     |

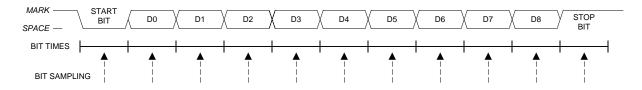

|              | igure 16.5. 9-Bit UART Timing Diagram                                 |     |

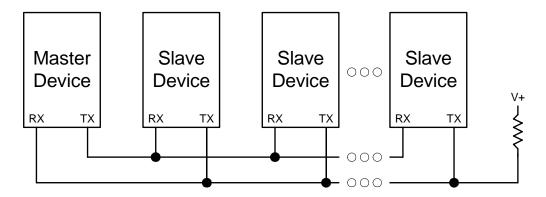

| I            | igure 16.6. UART Multi-Processor Mode Interconnect Diagram            | 150 |

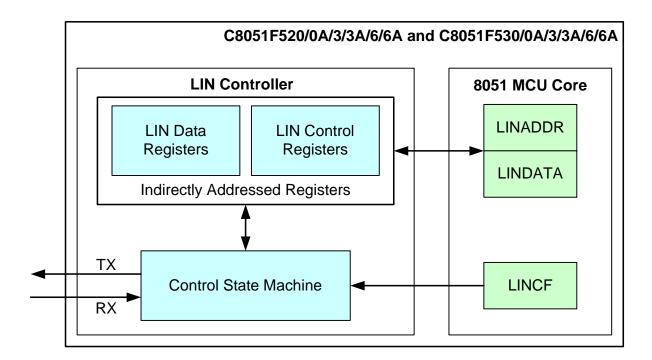

| <b>17.</b> l | IN (C8051F520/0A/3/3A/6/6A and C8051F530/0A/3/3A/6/6A)                |     |

| I            | igure 17.1. LIN Block Diagram                                         | 154 |

| 18.I         | nhanced Serial Peripheral Interface (SPI0)                            |     |

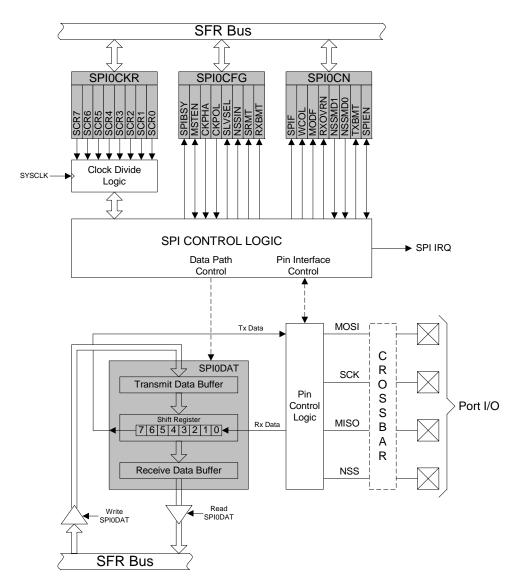

|              | igure 18.1. SPI Block Diagram                                         |     |

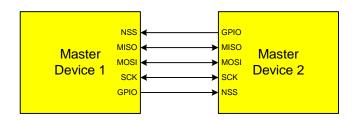

|              | igure 18.2. Multiple-Master Mode Connection Diagram                   |     |

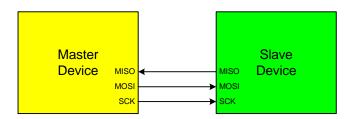

|              | igure 18.3. 3-Wire Single Master and Slave Mode Connection Diagram    |     |

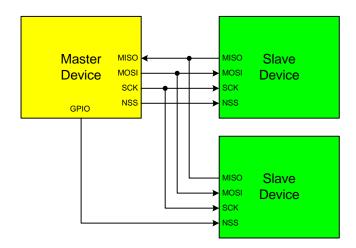

|              | igure 18.4. 4-Wire Single Master and Slave Mode Connection Diagram    | 174 |

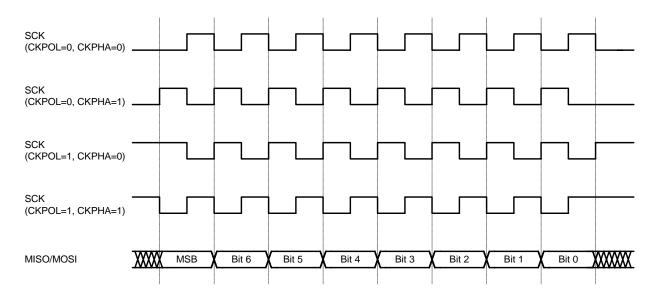

|              | igure 18.5. Data/Clock Timing Relationship                            | 176 |

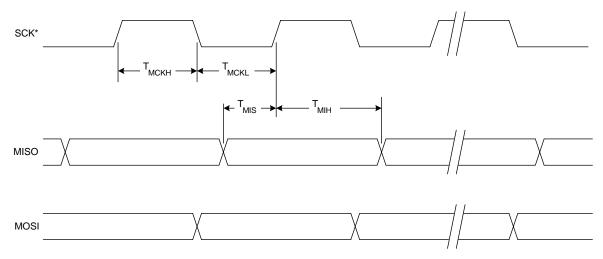

| I            | igure 18.6. SPI Master Timing (CKPHA = 0)                             | 181 |

|              | igure 18.7. SPI Master Timing (CKPHA = 1)                             |     |

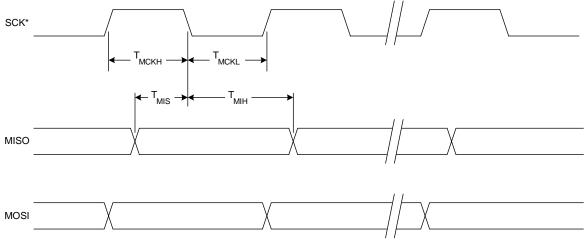

|              | igure 18.8. SPI Slave Timing (CKPHA = 0)                              | 182 |

|              | igure 18.9. SPI Slave Timing (CKPHA = 1)                              | 182 |

| 19.          | imers                                                                 |     |

|              | igure 19.1. T0 Mode 0 Block Diagram                                   | 185 |

|              | igure 19.2. T0 Mode 2 Block Diagram                                   | 186 |

|              | igure 19.3. T0 Mode 3 Block Diagram                                   |     |

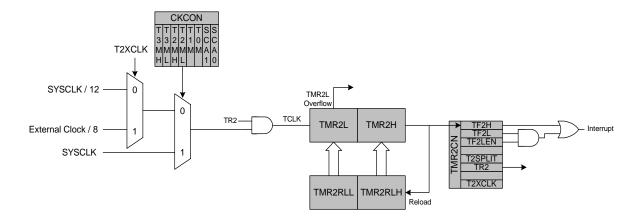

|              | igure 19.4. Timer 2 16-Bit Mode Block Diagram                         | 192 |

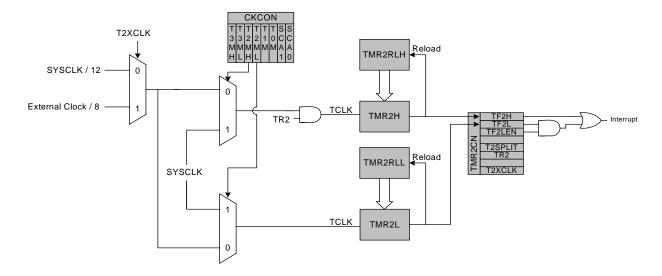

| I            | igure 19.5. Timer 2 8-Bit Mode Block Diagram                          | 193 |

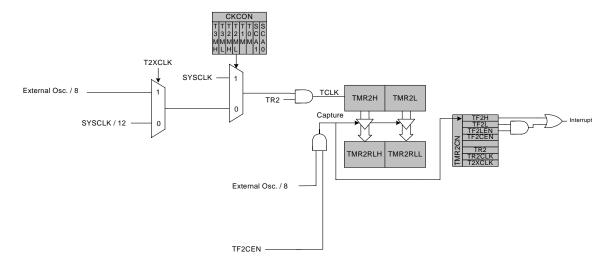

|              | igure 19.6. Timer 2 Capture Mode Block Diagram                        | 194 |

| <b>20.</b> l | rogrammable Counter Array (PCA0)                                      |     |

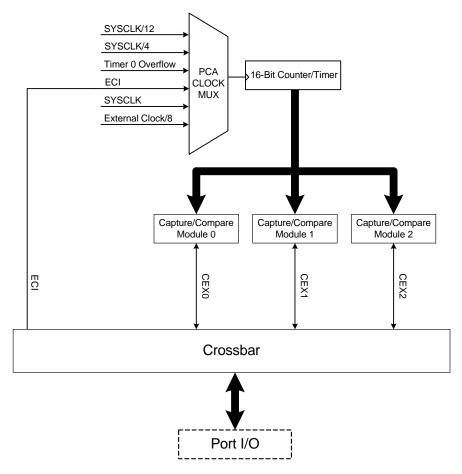

|              | igure 20.1. PCA Block Diagram                                         |     |

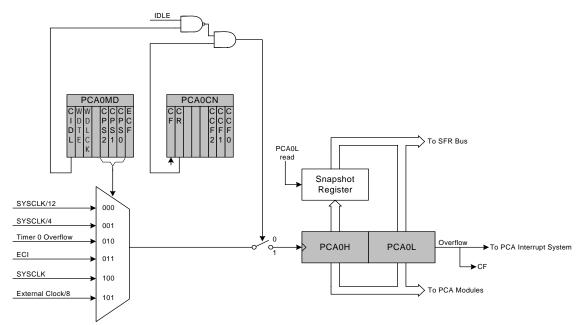

|              | igure 20.2. PCA Counter/Timer Block Diagram                           | 198 |

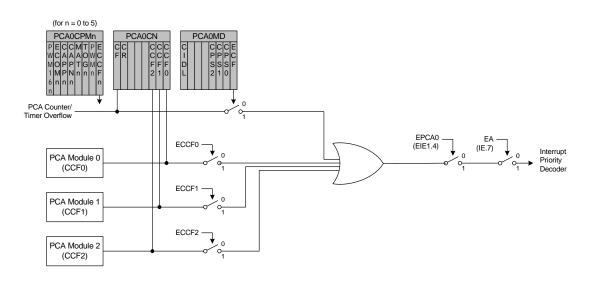

| I            | igure 20.3. PCA Interrupt Block Diagram                               | 199 |

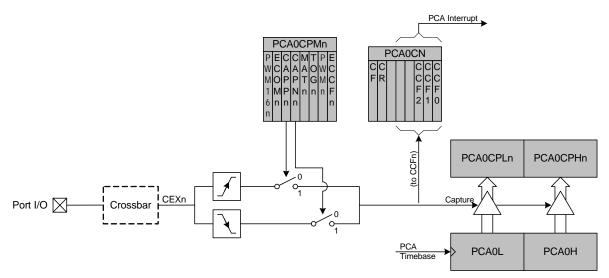

| I            | igure 20.4. PCA Capture Mode Diagram                                  | 200 |

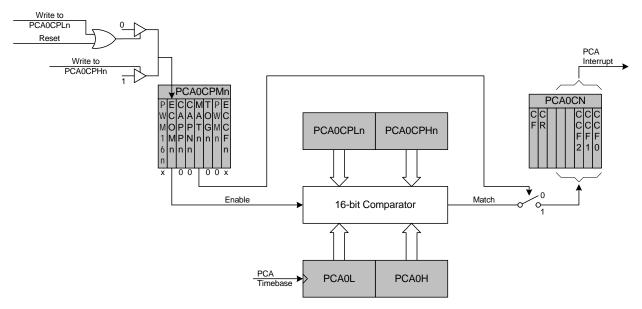

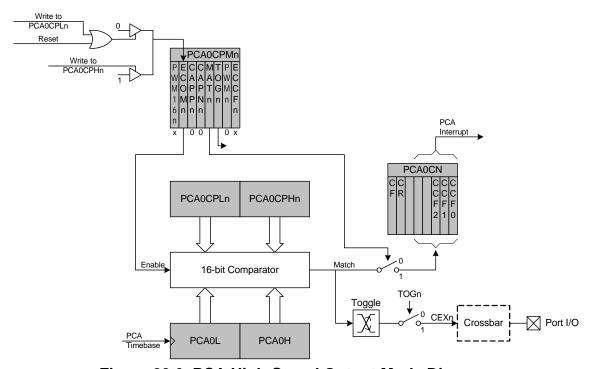

|              | igure 20.5. PCA Software Timer Mode Diagram                           |     |

|              | igure 20.6. PCA High-Speed Output Mode Diagram                        | 202 |

# C8051F52x-53x

| Figure 20.7. PCA Frequency Output Mode                 | 203 |

|--------------------------------------------------------|-----|

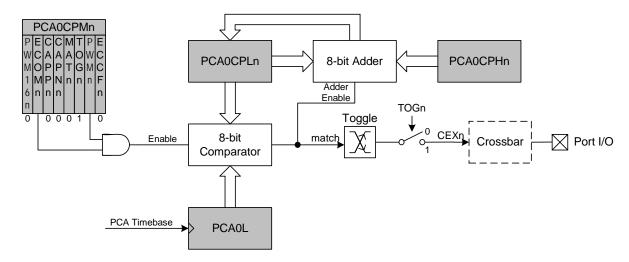

| Figure 20.8. PCA 8-Bit PWM Mode Diagram                |     |

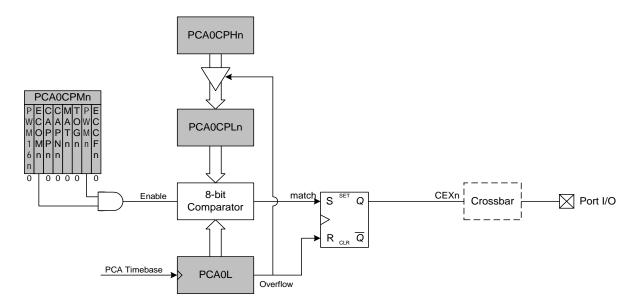

| Figure 20.9. PCA 16-Bit PWM Mode                       |     |

| Figure 20.10. PCA Module 2 with Watchdog Timer Enabled |     |

| 21. Device Specific Behavior                           |     |

| Figure 21.1. Device Package - TSSOP 20                 | 213 |

| Figure 21.2. Device Package - QFN 20                   |     |

| Figure 21.3. Device Package - DFN 10                   |     |

| 22. C2 Interface                                       |     |

| Figure 22.1. Typical C2 Pin Sharing                    | 218 |

| _   |                                                                       |      |

|-----|-----------------------------------------------------------------------|------|

| 1.  | System Overview                                                       |      |

|     | Table 1.1. Product Selection Guide                                    |      |

| _   | Table 1.2. Operating Modes Summary                                    | 23   |

| 2.  | Absolute Maximum Ratings                                              |      |

| _   | Table 2.1. Absolute Maximum Ratings                                   | 27   |

| 3.  | Global DC Electrical Characteristics                                  |      |

|     | Table 3.1. Global DC Electrical Characteristics                       | 28   |

| 4.  | Pinout and Package Definitions                                        |      |

|     | Table 4.1. Pin Definitions for the C8051F52x and C8051F52xA (DFN 10)  |      |

|     | Table 4.2. DFN-10 Package Diagram Dimensions                          |      |

|     | Table 4.3. DFN-10 Landing Diagram Dimensions                          |      |

|     | Table 4.4. Pin Definitions for the C8051F53x and C805153xA (TSSOP 20) |      |

|     | Table 4.5. TSSOP-20 Package Diagram Dimensions                        | 39   |

|     | Table 4.6. TSSOP-20 Landing Diagram Dimensions                        |      |

|     | Table 4.7. Pin Definitions for the C8051F53x and C805153xA (QFN 20)   | 42   |

|     | Table 4.8. QFN-20 Package Diagram Dimensions                          | 45   |

|     | Table 4.9. QFN-20 Landing Diagram Dimensions                          |      |

| 5.  | 12-Bit ADC (ADC0)                                                     |      |

|     | Table 5.1. ADC0 Electrical Characteristics                            | 66   |

| 6.  | Voltage Reference                                                     |      |

|     | Table 6.1. Voltage Reference Electrical Characteristics               | 69   |

| 7.  | Voltage Regulator (REG0)                                              |      |

|     | Table 7.1. Voltage Regulator Electrical Specifications                | 71   |

| 8.  | Comparator                                                            |      |

| •   | Table 8.1. Comparator Electrical Characteristics                      | 77   |

| 9_  | CIP-51 Microcontroller                                                |      |

| ٠.  | Table 9.1. CIP-51 Instruction Set Summary                             | 80   |

| 10  | Memory Organization and SFRs                                          |      |

|     | Table 10.1. Special Function Register (SFR) Memory Map                | 91   |

|     | Table 10.2. Special Function Registers                                |      |

| 11  | Interrupt Handler                                                     | 02   |

|     | Table 11.1. Interrupt Summary                                         | 96   |

| 12  | Reset Sources                                                         | 90   |

| 12  | Table 12.1. Reset Electrical Characteristics                          | 100  |

| 12  |                                                                       | 109  |

| 13  | Flash Memory                                                          | 115  |

|     | Table 13.1. Flash Security Summary                                    |      |

| 4.4 |                                                                       | 117  |

| 14. | Port Input/Output                                                     | 404  |

| 4 = | Table 14.1. Port I/O DC Electrical Characteristics                    | 134  |

| 15. | Oscillators                                                           | 4.45 |

| 4.0 | Table 15.1. Oscillator Electrical Characteristics                     | 145  |

| 16. | .UARTO                                                                |      |

|     | Table 16.1. Timer Settings for Standard Baud Rates                    | . –  |

|     | Using the Internal Oscillator                                         | 153  |

| 17. | LIN (C8051F520/0A/3/3A/6/6A and C8051F530/0A/3/3A/6/6A)               |      |

# C8051F52x-53x

| Table 17.1. Baud-Rate Calculation Variable Ranges                     | 156 |

|-----------------------------------------------------------------------|-----|

| Table 17.2. Manual Baud Rate Parameters Examples                      | 157 |

| Table 17.3. Autobaud Parameters Examples                              |     |

| Table 17.4. LIN Registers* (Indirectly Addressable)                   |     |

| 18. Enhanced Serial Peripheral Interface (SPI0)                       |     |

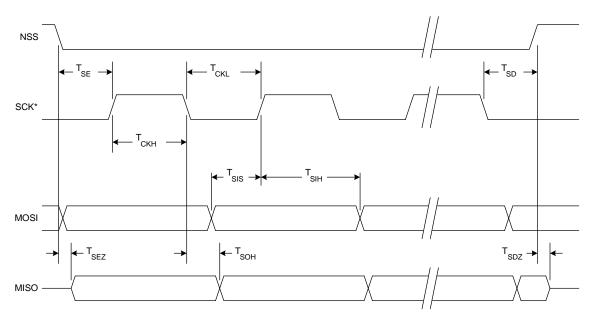

| Table 18.1. SPI Slave Timing Parameters                               | 183 |

| 19. Timers                                                            |     |

| 20. Programmable Counter Array (PCA0)                                 |     |

| Table 20.1. PCA Timebase Input Options                                | 198 |

| Table 20.2. PCA0CPM Register Settings for PCA Capture/Compare Modules | 199 |

| Table 20.3. Watchdog Timer Timeout Intervals1                         | 208 |

| 21. Device Specific Behavior                                          |     |

| 22. C2 Interface                                                      |     |

| SFR Definition 5.4. ADC0MX: ADC0 Channel Select                | 58  |

|----------------------------------------------------------------|-----|

| SFR Definition 5.5. ADC0CF: ADC0 Configuration                 | 59  |

| SFR Definition 5.6. ADC0H: ADC0 Data Word MSB                  |     |

| SFR Definition 5.7. ADC0L: ADC0 Data Word LSB                  |     |

| SFR Definition 5.8. ADC0CN: ADC0 Control                       |     |

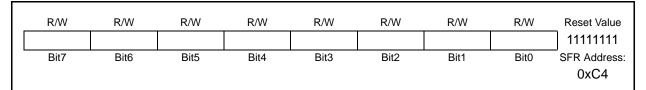

| SFR Definition 5.9. ADC0TK: ADC0 Tracking Mode Select          |     |

| SFR Definition 5.10. ADC0GTH: ADC0 Greater-Than Data High Byte |     |

| SFR Definition 5.11. ADC0GTL: ADC0 Greater-Than Data Low Byte  |     |

| SFR Definition 5.12. ADC0LTH: ADC0 Less-Than Data High Byte    |     |

| SFR Definition 5.13. ADC0LTL: ADC0 Less-Than Data Low Byte     |     |

| SFR Definition 6.1. REF0CN: Reference Control                  |     |

| SFR Definition 7.1. REG0CN: Regulator Control                  |     |

| SFR Definition 8.1. CPT0CN: Comparator0 Control                |     |

| SFR Definition 8.2. CPT0MX: Comparator0 MUX Selection          |     |

| SFR Definition 8.3. CPT0MD: Comparator0 Mode Selection         |     |

| SFR Definition 9.1. SP: Stack Pointer                          |     |

| SFR Definition 9.2. DPL: Data Pointer Low Byte                 |     |

| SFR Definition 9.3. DPH: Data Pointer High Byte                |     |

| SFR Definition 9.4. PSW: Program Status Word                   |     |

| SFR Definition 9.5. ACC: Accumulator                           | 86  |

| SFR Definition 9.6. B: B Register                              | 86  |

| SFR Definition 9.7. PCON: Power Control                        | 88  |

| SFR Definition 11.1. IE: Interrupt Enable                      | 97  |

| SFR Definition 11.2. IP: Interrupt Priority                    | 98  |

| SFR Definition 11.3. EIE1: Extended Interrupt Enable 1         |     |

| SFR Definition 11.4. EIP1: Extended Interrupt Priority 1       | 100 |

| SFR Definition 11.5. IT01CF: INT0/INT1 Configuration           | 102 |

| SFR Definition 12.1. VDDMON: VDD Monitor Control               | 106 |

| SFR Definition 12.2. RSTSRC: Reset Source                      |     |

| SFR Definition 13.1. PSCTL: Program Store R/W Control          | 116 |

| SFR Definition 13.2. FLKEY: Flash Lock and Key                 |     |

| SFR Definition 14.1. XBR0: Port I/O Crossbar Register 0        | 126 |

| SFR Definition 14.2. XBR1: Port I/O Crossbar Register 1        |     |

| SFR Definition 14.3. P0: Port0                                 | 128 |

| SFR Definition 14.4. P0MDIN: Port0 Input Mode                  | 128 |

| SFR Definition 14.5. P0MDOUT: Port0 Output Mode                | 129 |

| SFR Definition 14.6. P0SKIP: Port0 Skip                        |     |

| SFR Definition 14.7. P0MAT: Port0 Match                        | 130 |

| SFR Definition 14.8. P0MASK: Port0 Mask                        | 130 |

| SFR Definition 14.9. P1: Port1                                 | 131 |

| SFR Definition 14.10. P1MDIN: Port1 Input Mode                 |     |

| SFR Definition 14.11. P1MDOUT: Port1 Output Mode               | 132 |

| SFR Definition 14.12. P1SKIP: Port1 Skip                       |     |

| SFR Definition 14.13. P0SKIP: Port0 Skip                       | 133 |

| SFR Definition 14.14. P1MAT: Port1 Match                       |     |

# C8051F52x-53x

| SFR Definition 14.15. P1MASK: Port1 Mask                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 133 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| SFR Definition 15.1. OSCICN: Internal Oscillator Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 137 |

| SFR Definition 15.2. OSCICL: Internal Oscillator Calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 138 |

| SFR Definition 15.3. OSCIFIN: Internal Fine Oscillator Calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 138 |

| SFR Definition 15.4. OSCXCN: External Oscillator Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 143 |

| SFR Definition 15.5. CLKSEL: Clock Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| SFR Definition 16.1. SCON0: Serial Port 0 Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| SFR Definition 16.2. SBUF0: Serial (UART0) Port Data Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

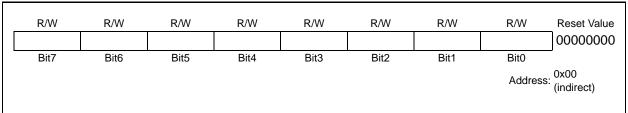

| SFR Definition 17.1. LINADDR: Indirect Address Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| SFR Definition 17.2. LINDATA: LIN Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

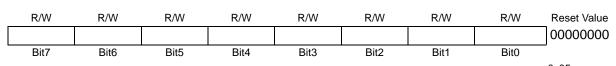

| SFR Definition 17.3. LINCF Control Mode Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| SFR Definition 17.4. LIN0DT1: LIN0 Data Byte 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| SFR Definition 17.5. LIN0DT2: LIN0 Data Byte 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| SFR Definition 17.6. LIN0DT3: LIN0 Data Byte 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| SFR Definition 17.7. LIN0DT4: LIN0 Data Byte 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| SFR Definition 17.8. LIN0DT5: LIN0 Data Byte 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| SFR Definition 17.9. LIN0DT6: LIN0 Data Byte 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| SFR Definition 17.10. LIN0DT7: LIN0 Data Byte 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| SFR Definition 17.11. LIN0DT8: LIN0 Data Byte 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| SFR Definition 17.12. LINOCTRL: LINO Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

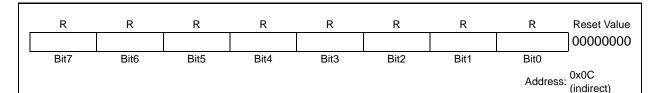

| SFR Definition 17.13. LINOST: LINO STATUS Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |