# STR750F

# ARM7TDMI-S™ 32-bit MCU with Flash, SMI, 3 std 16-bit timers, PWM timer, fast 10-bit ADC, I2C, UART, SSP, USB and CAN

#### ■ Core

- ARM7TDMI-S 32-bit RISC CPU

- 54 DMIPS @ 60 MHz

#### Memories

- Up to 256 KB Flash program memory (10k erase/write cycles, retention 20 yrs at 85°C)

- 16KB Read-While-Write Flash for data (100k erase/write cycles, retention 20 yrs@ 85°C)

- Flash Data Readout and Write Protection

- 16KBytes embedded high speed SRAM

- Memory mapped interface (SMI) to ext.

Serial Flash (64 MB) w. boot capability

### ■ Clock, Reset and Supply Management

- Single supply 3.3V  $\pm 10\%$  or 5V  $\pm 10\%$

- Embedded 1.8V Voltage Regulators with Low Power features

- Smart Clock Controller with flexible clock generation capability:

- Internal RC for fast start-up and backup clock mechanism

- Up to 60 MHz operation using internal PLL with 4 or 8 MHz crystal/ceramic osc.

- Smart Low Power Modes: SLOW, WFI, STOP and STANDBY with backup registers

- Real Time Clock, driven by low power internal RC or 32.768 kHz dedicated osc, for clock-calendar and Auto Wake-up

### ■ Nested interrupt controller

- Fast interrupt handling with 32 vectors

- 16 IRQ priorities, 2 maskable FIQ sources

- 16 external interrupt / wake-up Lines

### ■ DMA

- 4-channel DMA controller

- Circular buffer management

- Support for UART, SSP, Timers, ADC

### ■ 6 Timers

16-bit watchdog timer (WDG)

- 16-bit timer for system timebase functions

- 3 synchronizable timers each with up to 2 input captures and 2 output compare/PWMs.

- 16-bit 6-channel synchronizable PWM timer

- Dead time generation, edge/center-aligned waveforms and emergency stop

- Ideal for induction/brushless DC motors

### ■ 8 Communications Interfaces

- 1 I<sup>2</sup>C interface

- 3 HiSpeed UARTs w. Modem/LIN capability

- 2 SSP interfaces (SPI or SSI) up to 16 Mb/s

- 1 CAN interface (2.0B Active)

- 1 USB full-speed 12 Mb/s interface with 8 configurable endpoint sizes

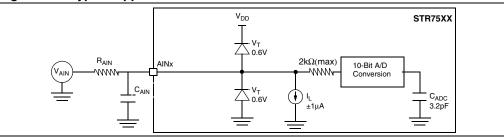

### ■ 10-bit A/D Converter

- 16/11 chan. with prog. Scan Mode & FIFO

- Programmable Analog Watchdog feature

- Conversion: min. 3.75  $\mu$ s, range: 0 to  $V_{DD\ IO}$

- Start conversion can be triggered by timers

### ■ Up to 72/38 I/O ports

- 72/38 GPIO lines with High Sink capabilities

- Atomic bit SET and RES operations

October 2006 Rev 2 1/71

Contents STR750F

# **Contents**

| 1    | Intro | duction   | 4                                                                        |

|------|-------|-----------|--------------------------------------------------------------------------|

|      | 1.1   | Overvi    | ew5                                                                      |

|      | 1.2   | Block [   | Diagram                                                                  |

| 2    | Pin [ | Descript  | ion11                                                                    |

|      |       | 2.0.1     | Pin Description Table                                                    |

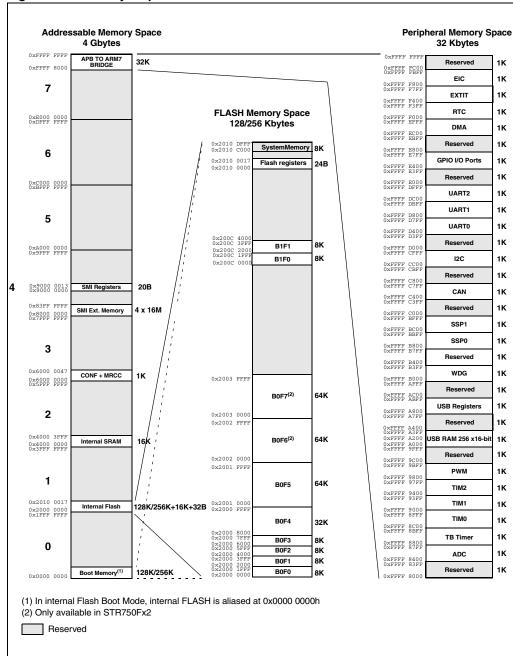

|      | 2.1   | Memor     | y map                                                                    |

| 3    | Elec  | trical pa | rameters 23                                                              |

|      | 3.1   | Parame    | eter conditions                                                          |

|      |       | 3.1.1     | Minimum and maximum values                                               |

|      |       | 3.1.2     | Typical values                                                           |

|      |       | 3.1.3     | Typical curves                                                           |

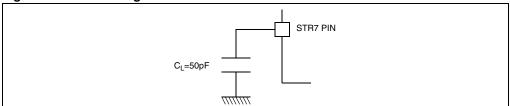

|      |       | 3.1.4     | Loading capacitor                                                        |

|      |       | 3.1.5     | Pin input voltage24                                                      |

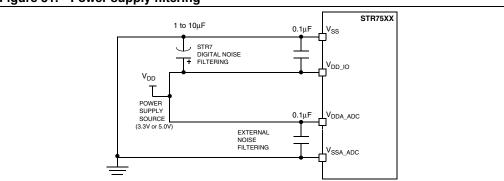

|      |       | 3.1.6     | Power Supply Schemes                                                     |

|      |       | 3.1.7     | I/O characteristics versus the various power schemes (3.3V or 5.0V) . 28 |

|      |       | 3.1.8     | Current Consumption Measurements                                         |

|      | 3.2   | Absolu    | te maximum ratings                                                       |

|      |       | 3.2.1     | Voltage characteristics                                                  |

|      |       | 3.2.2     | Current characteristics                                                  |

|      |       | 3.2.3     | Thermal characteristics                                                  |

|      | 3.3   | Operat    | ing conditions                                                           |

|      |       | 3.3.1     | General operating conditions                                             |

|      |       | 3.3.2     | Operating conditions at power-up / power-down                            |

|      |       | 3.3.3     | Embedded voltage regulators                                              |

|      |       | 3.3.4     | Supply current characteristics                                           |

|      |       | 3.3.5     | Clock and timing characteristics40                                       |

|      |       | 3.3.6     | Memory characteristics                                                   |

|      |       | 3.3.7     | EMC characteristics                                                      |

|      |       | 3.3.8     | I/O port pin characteristics                                             |

|      |       | 3.3.9     | TB and TIM timer characteristics                                         |

|      |       | 3.3.10    | Communication interface characteristics                                  |

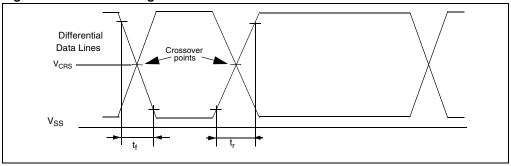

|      |       | 3.3.11    | USB characteristics                                                      |

| 2/76 |       |           |                                                                          |

|      |       |           | 7.2                                                                      |

| STR750F |      |          |             |            |           |   |      |      |      | ( | Cont | ents |

|---------|------|----------|-------------|------------|-----------|---|------|------|------|---|------|------|

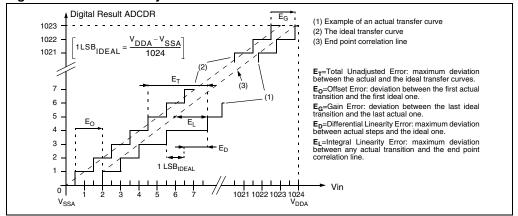

|         |      | 3.3.12   | 10-bit AD   | C charac   | cteristic | 3 | <br> | <br> | <br> |   |      | 61   |

| 4       | Pack | age cha  | racterist   | ics        |           |   | <br> | <br> | <br> |   |      | . 65 |

|         | 4.1  | Packag   | je mechan   | ical data  | a         |   | <br> | <br> | <br> |   |      | . 65 |

|         | 4.2  | Therma   | al characte | eristics . |           |   | <br> | <br> | <br> |   |      | . 67 |

| 5       | Orde | er codes |             |            |           |   | <br> | <br> | <br> |   |      | . 68 |

| 6       | Revi | sion his | torv        |            |           |   | <br> | <br> | <br> |   |      | . 69 |

**577**

Introduction STR750F

# 1 Introduction

This Datasheet contains the description of the STR750 family features, pinout, Electrical Characteristics, Mechanical Data and Ordering information.

For complete information on the Microcontroller memory, registers and peripherals. Please refer to the STR750 Reference Manual.

For information on the ARM7TDMI-S core please refer to the ARM7TDMI-S Technical Reference Manual available from Arm Ltd.

For information on programming, erasing and protection of the internal Flash memory please refer to the STR7 Flash Programming Reference Manual

For information on third-party development tools, please refer to the http://www.st.com/mcu website.

Table 1. Device summary

| Features               | STR755FRx                                           | STR751FRx                                | STR752FRx    | STR755FVx                     | STR750FVx                                                              |  |  |  |  |  |  |

|------------------------|-----------------------------------------------------|------------------------------------------|--------------|-------------------------------|------------------------------------------------------------------------|--|--|--|--|--|--|

| Flash - Bank 0 (bytes) |                                                     | 64                                       | 4K/128K/256K |                               |                                                                        |  |  |  |  |  |  |

| Flash - Bank 1 (bytes) |                                                     |                                          | 16K RWW      |                               |                                                                        |  |  |  |  |  |  |

| RAM (bytes)            |                                                     |                                          | 16K          |                               |                                                                        |  |  |  |  |  |  |

| Operating Temp.        | -40 to +85°C / -40 to +105°C (see <i>Table 44</i> ) |                                          |              |                               |                                                                        |  |  |  |  |  |  |

| Common Peripherals     | ,                                                   | Ps, 1 I2C, 3 timer<br>ake-up lines, 11 / | ,            | 3 timers 1 P\<br>I/Os 15 Wake | SSPs, 1 I <sup>2</sup> C,<br>VM timer, 72<br>e-up lines, 16<br>nannels |  |  |  |  |  |  |

| USB/CAN<br>peripherals | None                                                | USB                                      | CAN          | None                          | USB+CAN                                                                |  |  |  |  |  |  |

| Operating Voltage      | 3.3V or 5V                                          | 3.3V                                     |              | 3.3V or 5V                    |                                                                        |  |  |  |  |  |  |

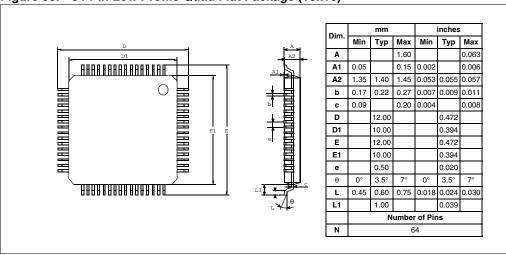

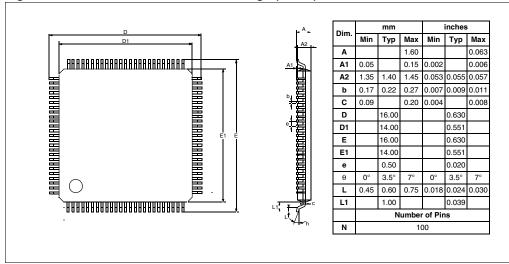

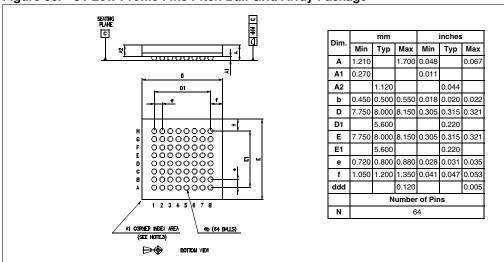

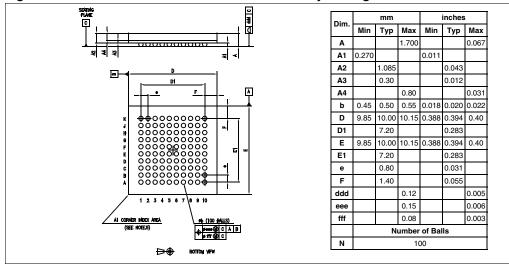

| Packages (x)           | <b>T</b> =LQFI                                      | P64 10x10, <b>H</b> =LF                  | FBGA64       | T=LQFP1<br>H=LFB              | 00 14x14,<br>GA100                                                     |  |  |  |  |  |  |

STR750F Introduction

### 1.1 Overview

The STR750 family includes devices in 2 package sizes: 64-pin and 100-pin. Both types have the following common features:

### ARM7TDMI-S™ core with embedded Flash & RAM

STR750 family has an embedded ARM core and is therefore compatible with all ARM tools and software. It combines the high performance ARM7TDMI-S™ CPU with an extensive range of peripheral functions and enhanced I/O capabilities. All devices have on-chip high-speed single voltage FLASH memory and high-speed RAM.

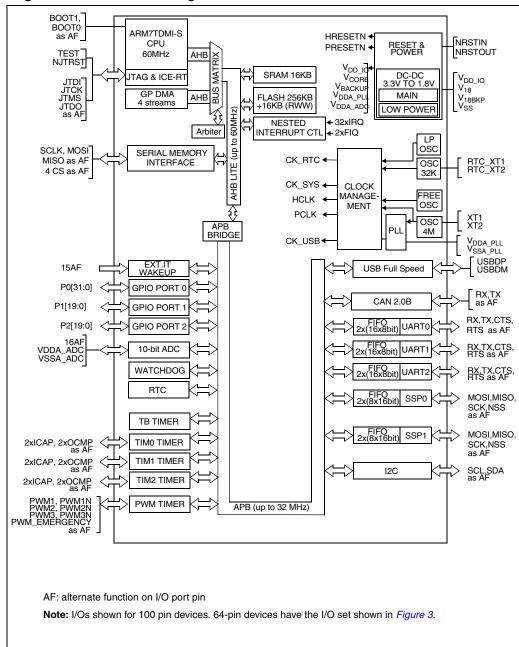

Figure 1 shows the general block diagram of the device family.

### **Embedded Flash Memory**

Up to 256 KBytes of embedded Flash is available in Bank 0 for storing programs and data. An additional Bank 1 provides 16 Kbytes of RWW (Read While Write) memory allowing it to be erased/programmed on-the-fly. This partitioning feature is ideal for storing application parameters.

- When configured in burst mode, access to Flash memory is performed at CPU clock speed with 0 wait states for sequential accesses and 1 wait state for random access (maximum 60 MHz).

- When not configured in burst mode, access to Flash memory is performed at CPU clock speed with 0 wait states (maximum 32 MHz)

### **Embedded SRAM**

16 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states.

### **Enhanced Interrupt Controller (EIC)**

In addition to the standard ARM interrupt controller, the STR750F embeds a nested interrupt controller able to handle up to 32 vectors and 16 priority levels. This additional hardware block provides flexible interrupt management features with minimal interrupt latency.

### **Serial Memory Interface (SMI)**

The Serial Memory interface is directly able to access up to 4 serial FLASH devices. It communicates at a speed of up to 48 MHz. It can be used to access data, execute code directly or boot the application from external memory. The memory is addressed as 4 banks of up to 16 Mbytes each.

### Clocks and start-up

After RESET or when exiting from Low Power Mode, the CPU is clocked immediately by an internal RC oscillator (FREEOSC) at a frequency centered around 5 MHz, so the application code can start executing without delay. In parallel, the 4/8 MHz Oscillator is enabled and its stabilization time is monitored using a dedicated counter.

An oscillator failure detection is implemented: when the clock disappears on the XT1 pin, the circuit automatically switches to the FREEOSC oscillator and an interrupt is generated.

In Run mode, the AHB and APB clock speeds can be set at a large number of different frequencies thanks to the PLL and various prescalers: up to 60 MHz for AHB and up to 32 MHz for APB when fetching from Flash (64 MHz and 32 MHz when fetching from SRAM).

577

Introduction STR750F

In SLOW mode, the AHB clock can be significantly decreased to reduce power consumption.

The built-in Clock Controller also provides the 48 MHz USB clock directly without any extra oscillators or PLL. For instance, starting from the 4 MHz crystal source, it is possible to obtain in parallel 60 MHz for the AHB clock, 48 MHz for the USB clock and 30 MHz for the APB peripherals.

#### **Boot modes**

At start-up, boot pins are used to select one of five boot options:

- Boot from internal flash

- Boot from external serial Flash memory

- Boot from internal boot loader

- Boot from internal SRAM

Booting from SMI memory allows booting from a serial flash. This way, a specific boot monitor can be implemented. Alternatively, the STR750F can boot from the internal boot loader that implements a boot from UART.

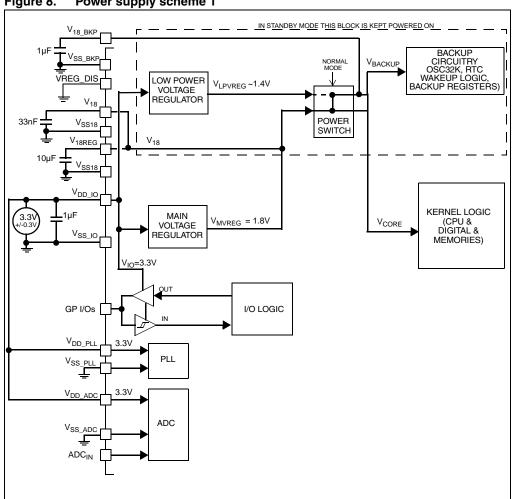

### **Power Supply Schemes**

You can connect the device in any of the following ways depending on your application.

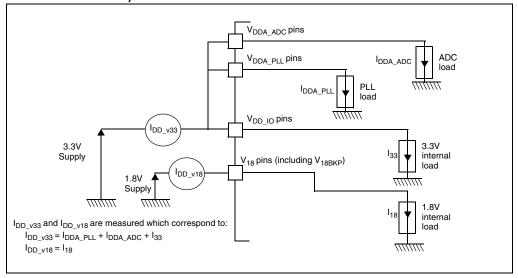

- Power Scheme 1: Single external 3.3V power source. In this configuration the

V<sub>CORE</sub> supply required for the internal logic is generated internally by the main voltage

regulator and the V<sub>BACKUP</sub> supply is generated internally by the low power voltage

regulator. This scheme has the advantage of requiring only one 3.3V power source.

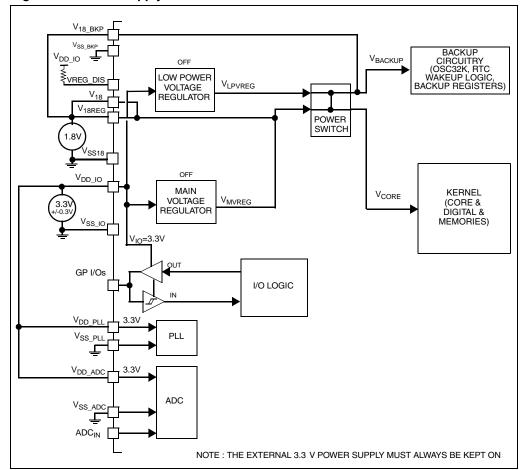

- Power Scheme 2: Dual external 3.3V and 1.8V power sources. In this configuration, the internal voltage regulators are switched off by forcing the VREG\_DIS pin to high level. V<sub>CORE</sub> is provided externally through the V<sub>18</sub> and V<sub>18REG</sub> power pins and V<sub>BACKUP</sub> through the V<sub>18\_BKP</sub> pin. This scheme is intended to save power consumption for applications which already provide an 1.8V power supply.

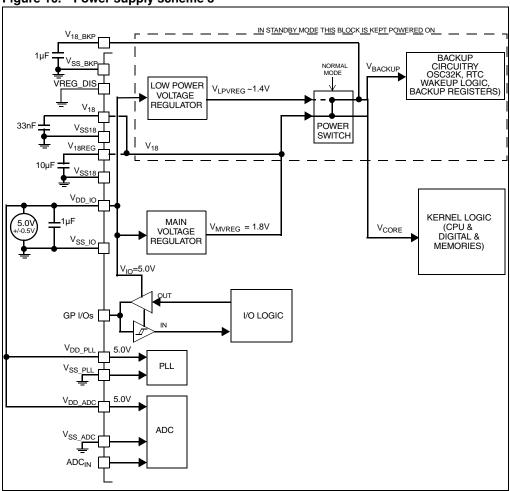

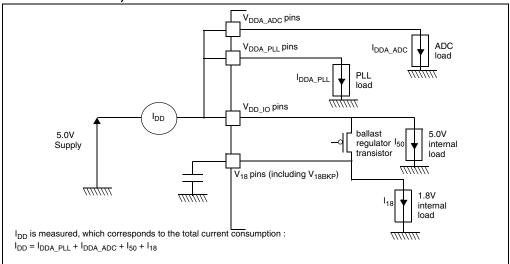

- Power Scheme 3: Single external 5.0V power source. In this configuration the

V<sub>CORE</sub> supply required for the internal logic is generated internally by the main voltage

regulator and the V<sub>BACKUP</sub> supply is generated internally by the low power voltage

regulator. This scheme has the advantage of requiring only one 5.0V power source.

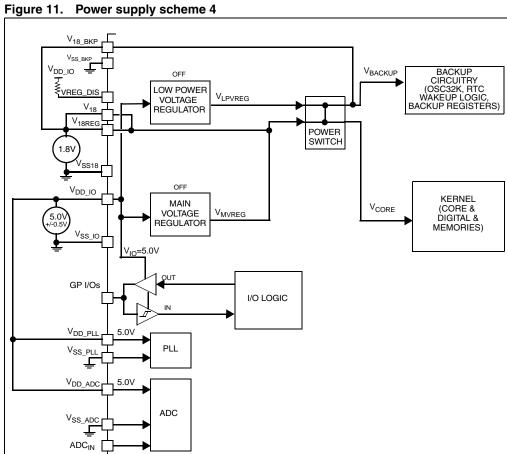

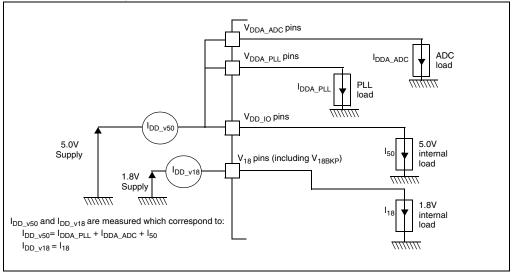

- Power Scheme 4: Dual external 5.0V and 1.8V power sources. In this configuration, the internal voltage regulators are switched off, by forcing the VREG\_DIS pin to high level. V<sub>CORE</sub> is provided externally through the V<sub>18</sub> and V<sub>18REG</sub> power pins and V<sub>BACKUP</sub> through the V<sub>18</sub> BKP pin. This scheme is intended to provide 5V I/O capability.

Caution: When powered by 5.0V, the USB peripheral cannot operate.

**577**

STR750F Introduction

#### Low Power modes

The STR750F supports 5 low power modes, SLOW, PCG, WFI, STOP and STANDBY.

SLOW MODE: the system clock speed is reduced. Alternatively, the PLL and the main oscillator can be stopped and the device is driven by a low power clock (f<sub>RTC</sub>). The clock is either an external 32.768 kHz oscillator or the internal low power RC oscillator.

- PCG MODE (Peripheral Clock Gating MODE): When the peripherals are not used, their APB clocks are gated to optimize the power consumption.

- WFI MODE (Wait For Interrupts): only the CPU clock is stopped, all peripherals continue to work and can wake-up the CPU when IRQs occur.

- STOP MODE: all clocks/peripherals are disabled. It is also possible to disable the oscillators and the Main Voltage Regulator (In this case the V<sub>CORE</sub> is entirely powered by V<sub>18\_BKP</sub>). This mode is intended to achieve the lowest power consumption with SRAM and registers contents retained. The system can be woken up by any of the external interrupts / wake-up lines or by the RTC timer which can optionally be kept running. The RTC can be clocked either by the 32.768 kHz Crystal or the Low Power RC Oscillator.

- Alternatively, STOP mode gives flexibility to keep the either main oscillator, or the Flash or the Main Voltage Regulator enabled when a fast start after wake-up is preferred (at the cost of some extra power consumption).

- STANDBY MODE: This mode (only available in single supply power schemes) is intended to achieve the lowest power consumption even when the temperature is increasing. The digital power supply (V<sub>CORE</sub>) is completely removed (no leakage even at high ambient temperature). SRAM and all register contents are lost. Only the RTC remains powered by V<sub>18\_BKP</sub> The STR750F can be switched back from STANDBY to RUN mode by a trigger event on the WKP\_STDBY pin or an alarm timeout on the RTC counter.

### Caution:

It is important to bear in mind that it is forbidden to remove power from the  $V_{DD\_IO}$  power supply in any of the Low Power Modes (even in STANDBY MODE).

#### **DMA**

The flexible 4-channel general-purpose DMA is able to manage memory to memory, peripheral to memory and memory to peripheral transfers. The DMA controller supports circular buffer management avoiding the generation of interrupts when the controller reaches the end of the buffer.

The DMA can be used with the main peripherals: UART0, SSP0, Motor control PWM timer (PWM), standard timer TIM0 and ADC.

### RTC (Real Time Clock)

The real time clock provides a set of continuously running counters which can be used with suitable software to provide a clock calendar function, and provides an alarm interrupt and a periodic interrupt. It is clocked by an external 32.768 kHz oscillator or the internal low power RC oscillator. The RC has a typical frequency of 300 kHz and can be calibrated.

### WDG (Watchdog Timer)

The watchdog timer is based on a 16-bit downcounter and 8-bit prescaler. It can be used as watchdog to reset the device when a problem occurs, or as free running timer for application time out management.

5//

Introduction STR750F

### **Timebase Timer (TB)**

The timebase timer is based on a 16-bit auto-reload counter and not connected to the I/O pins. It can be used for software triggering, or to implement the scheduler of a real time operating system.

### Synchronizable Standard Timers (TIM2:0)

The three standard timers are based on a 16-bit auto-reload counter and feature up to 2 input captures and 2 output compares (for external triggering or time base / time out management). They can work together with the PWM timer via the Timer Link feature for synchronization or event chaining. In reset state, timer Alternate Function I/Os are connected to the same

I/O ports in both 64-pin and 100-pin devices. To optimize timer functions in 64-pin devices, timer Alternate Function I/Os can be connected, or "remapped", to other I/O ports as summarized in *Table 2* and detailed in *Table 5*. This remapping is done by the application via a control register.

Table 2. Standard timer alternate function I/Os

|          |                      | Nun     | nber of Alternate Fur | nction I/Os |

|----------|----------------------|---------|-----------------------|-------------|

| Stand    | dard Timer Functions | 100-pin | 64-pin p              | oackage     |

|          |                      | package | Default mapping       | Remapped    |

| TIM 0    | Input Capture        | 2       | 1                     | 2           |

| I IIVI O | Output Compare/PWM   | 2       | 1                     | 2           |

| TIM 1    | Input Capture        | 2       | 1                     | 1           |

| I IIVI I | Output Compare/PWM   | 2       | 1                     | 1           |

| TIM 2    | Input Capture        | 2       | 2                     | 2           |

| 1 1101 2 | Output Compare/PWM   | 2       | 1                     | 2           |

Any of the standard timers can be used to generate PWM outputs. One timer (TIM0) is mapped to a DMA channel.

### **Motor Control PWM timer (PWM)**

The Motor Control PWM Timer (PWM) can be seen as a three-phase PWM multiplexed on 6 channels. The 16-bit PWM generator has full modulation capability (0...100%), edge or centre-aligned patterns and supports dead-time insertion. It has many features in common with the standard TIM timers which has the same architecture and it can work together with the TIM timers via the Timer Link feature for synchronization or event chaining. The PWM timer is mapped to a DMA channel.

### I<sup>2</sup>C bus

The I<sup>2</sup>C bus interface can operate in multi-master and slave mode. It can support standard and fast modes (up to 400KHz).

STR750F Introduction

### High Speed Universal Asynch. Receiver Transmitter (UART)

The three UART interfaces are able to communicate at speeds of up to 2 Mbit/s. They provide hardware management of the CTS and RTS signals and have LIN Master capability.

To optimize the data transfer between the processor and the peripheral, two FIFOs (receive/transmit) of 16 bytes each have been implemented.

One UART can be served by the DMA controller (UART0).

### Synchronous Serial Peripheral (SSP)

The two SSPs are able to communicate up to 8 Mbit/s (SSP1) or up to 16 Mbit/s (SSP0) in standard full duplex 4-pin interface mode as a master device or up to 2.66 Mbit/s as a slave device. To optimize the data transfer between the processor and the peripheral, two FIFOs (receive/transmit) of 8 x 16 bit words have been implemented. The SSPs support the Motorola SPI or TI SSI protocols.

One SSP can be served by the DMA controller (SSP0).

### **Controller Area Network (CAN)**

The CAN is compliant with the specification 2.0 part B (active) with a bit rate up to 1Mbit/s. It can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. Up to 32 message objects are handled through an internal RAM buffer. In LQFP64 devices, CAN and USB cannot be connected simultaneously.

### **Universal Serial Bus (USB)**

The STR750F embeds a USB device peripheral compatible with the USB Full speed 12Mbs. The USB interface implements a full speed (12 Mbit/s) function interface. It has software configurable endpoint setting and suspend/resume support. The dedicated 48 MHz clock source is generated from the internal main PLL. V<sub>DD</sub> must be in the range 3.3V±10% for USB operation.

### **ADC (Analog to Digital Converter)**

The 10-bit Analog to Digital Converter, converts up to 16 external channels (11 channels in 64-pin devices) in single-shot or scan modes. In scan mode, continuous conversion is performed on a selected group of analog inputs. The minimum conversion time is  $3.75 \,\mu s$  (including the sampling time).

The ADC can be served by the DMA controller.

An analog watchdog feature allows you to very precisely monitor the converted voltage of up to four channels. An IRQ is generated when the converted voltage is outside the programmed thresholds.

The events generated by TIM0, TIM2 and PWM timers can be internally connected to the ADC start trigger, injection trigger, and DMA trigger respectively, to allow the application to synchronize A/D conversion and timers.

### **GPIOs (General Purpose Input/Output)**

Each of the 72 GPIO pins (38 GPIOs in 64-pin devices) can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as Peripheral Alternate Function. Port 1.15 is an exception, it can be used as general-purpose input only or wake-up from STANDBY mode (WKP\_STDBY). Most of the GPIO pins are shared with digital or analog alternate functions.

Introduction STR750F

# 1.2 Block Diagram

Figure 1. STR750 block diagram

**STR750F Pin Description**

#### 2 **Pin Description**

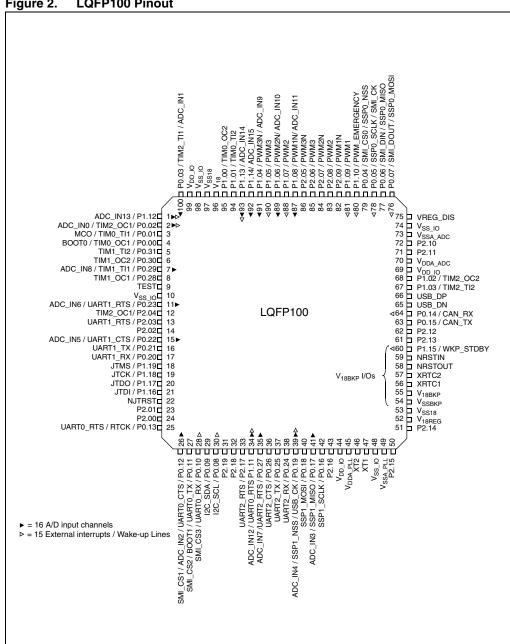

Figure 2. **LQFP100 Pinout**

Pin Description STR750F

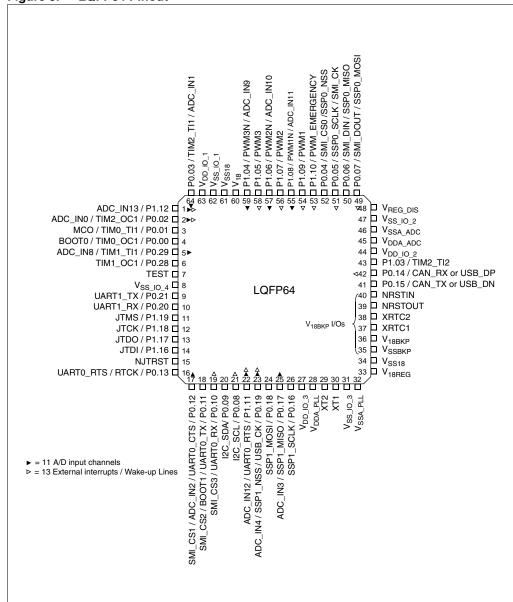

Figure 3. LQFP64 Pinout

STR750F Pin Description

Table 3. LFBGA100 ball connections

|   | 1      | 2     | 3                  | 4                  | 5     | 6     | 7                  | 8                    | 9                    | 10                   |

|---|--------|-------|--------------------|--------------------|-------|-------|--------------------|----------------------|----------------------|----------------------|

|   |        |       |                    |                    |       |       |                    |                      |                      |                      |

| A | P0.03  | P1.13 | P1.14              | P1.04              | P1.06 | P1.08 | P0.05              | P0.06                | P0.07                | P1.02                |

| В | P1.12  | P0.02 | P0.01              | P1.05              | P1.07 | P1.09 | P0.04              | P2.13                | P1.03                | P2.10                |

| С | P0.31  | P0.00 | $V_{DD\_IO}$       | V <sub>18</sub>    | P1.10 | P2.09 | V <sub>SS_IO</sub> | V <sub>SSA_ADC</sub> | P2.11                | USB_DP               |

| D | P0.29  | P0.30 | V <sub>SS_IO</sub> | V <sub>SS18</sub>  | P1.01 | P1.15 | $V_{DD\_IO}$       | V <sub>DDA_ADC</sub> | P2.12                | USB_DN               |

| E | P0.28  | P0.23 | P0.22              | V <sub>SS_IO</sub> | TEST  | P1.00 | NRSTOUT            | VREG_DIS             | NRSTIN               | P0.14                |

| F | P2.03  | P0.21 | P0.20              | P2.02              | P2.04 | P2.05 | P2.06              | V <sub>SS18</sub>    | V <sub>SSBKP</sub>   | P0.15                |

| G | NJTRST | P1.18 | P1.19              | P2.01              | P2.00 | P2.07 | 2.08               | V <sub>18REG</sub>   | V <sub>18BKP</sub>   | XRTC2                |

| Н | P0.13  | P1.16 | P1.17              | P2.19              | P2.18 | P2.17 | P0.24              | P2.14                | P2.16                | XRTC1                |

| J | P0.11  | P0.12 | P1.11              | P0.27              | P0.19 | P0.26 | P0.25              | P2.15                | V <sub>DD_IO</sub>   | V <sub>SS_IO</sub>   |

| K | P0.10  | P0.09 | P0.08              | P0.18              | P0.17 | P0.16 | XT1                | XT2                  | V <sub>DDA_PLL</sub> | V <sub>SSA_PLL</sub> |

Table 4. LFBGA64 ball connections

|   | 1     | 2                  | 3     | 4                  | 5                  | 6                    | 7                    | 8                    |

|---|-------|--------------------|-------|--------------------|--------------------|----------------------|----------------------|----------------------|

| Α | P0.03 | V <sub>SS_IO</sub> | P1.04 | P1.06              | P1.08              | P0.05                | P0.06                | P0.07                |

| В | P1.12 | $V_{DD\_IO}$       | P1.05 | P1.07              | P1.09              | P0.04                | P1.10                | P1.03                |

| С | P0.01 | P0.02              | P0.00 | V <sub>18</sub>    | V <sub>SS18</sub>  | V <sub>DD_IO</sub>   | V <sub>SS_IO</sub>   | P0.14                |

| D | P0.29 | P0.28              | TEST  | V <sub>SS_IO</sub> | VREG_DIS           | V <sub>DDA_ADC</sub> | V <sub>SSA_ADC</sub> | P0.15                |

| E | P1.18 | P1.19              | P0.20 | P0.21              | NRSTOUT            | NRSTIN               | V <sub>18BKP</sub>   | XRTC2                |

| F | P0.13 | NJTRST             | P1.16 | P1.17              | V <sub>18REG</sub> | V <sub>SS18</sub>    | V <sub>SSBKP</sub>   | XRTC1                |

| G | P0.11 | P0.12              | P1.11 | P0.19              | V <sub>DD_IO</sub> | V <sub>SS_IO</sub>   | V <sub>DDA_PLL</sub> | V <sub>SSA_PLL</sub> |

| н | P0.10 | P0.09              | P0.08 | P0.17              | P0.18              | P0.16                | XT2                  | XT1                  |

Pin Description STR750F

### 2.0.1 Pin Description Table

### Legend / Abbreviations for *Table 5*:

**Type:** I = input, O = output, S = supply,

Input Levels: All Inputs are LVTTL at  $V_{DD\_IO} = 3.3V + /-0.3V$  or TTL

at  $V_{DD\ IO} = 5V \pm 0.5V$ . In both cases,  $T_T$  means

$V_{ILmax} = 0.8V V_{IHmin} = 2.0V$

Inputs: All inputs can be configured as floating or with

internal weak pull-up or pull down (pu/pd)

Outputs: All Outputs can be configured as Open Drain (OD) or

Push-Pull (PP) (see also note 6 below *Table 5*). There are 3 different types of Output with different

drives and speed characteristics:

- O8:  $\rm f_{max}$  = 40 MHz on C<sub>L</sub>=50pF and 8 mA static drive capability for V<sub>OL</sub>=0.4V and up to 20 mA for V<sub>OL</sub>=1.3V (see Output driving current on page 54)

O4: f<sub>max</sub> = 20 MHz on C<sub>L</sub>=50pF and 4 mA static drive capability for V<sub>OL</sub>=0.4V (see Output driving

current on page 54)

O2: f<sub>max</sub> = 10 MHz on C<sub>L</sub>=50pF and 2 mA static drive capability of for V<sub>OL</sub>=0.4V (see Output driving

current on page 54)

External Interrupts/wake-up lines: EITx

STR750F Pin Description

#### **Port Reset State**

The reset state of the I/O ports is GPIO input floating. Exceptions are P1[19:16] and P0.13 which are configured as JTAG alternate functions:

- The JTAG inputs (JTDI, JTMS and JTDI) are configured as input floating and are ready to accept JTAG sequences.

- The JTAG output JTDO is configured as floating when idle (no JTAG operation) and is configured in output push-pull only when serial JTAG data must be output.

- The JTAG output RTCK is always configured as output push-pull. It outputs '0' level during the reset phase and then outputs the JTCK input signal resynchronized 3 times by the internal AHB clock.

- The GPIO\_PCx registers do not control JTAG AF selection, so the reset values of GPIO\_PCx for P1[19:16] and P0. 13 are the same as other ports. Refer to the GPIO section of the STR750 Reference Manual for the register description and reset values.

- P0.11 and P0.00 are sampled by the boot logic after reset, prior to fetching the first word of user code at address 0000 0000h.

- When booting from SMI (and only in this case), the reset state of the following GPIOs is "SMI alternate function output enabled":

- P0.07 (SMI\_DOUT)

- P0.05 (SMI\_CLK)

- P0.04 (SMI\_CS0)

- P0.06 (SMI\_DIN)

Note that the other SMI pins: SMI\_CS1,2,3 (P0.12, P0.11, P0.10) are not affected.

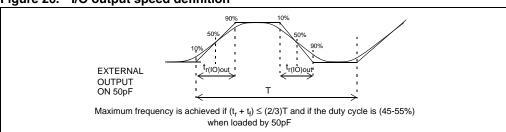

To avoid excess power consumption, unused I/O ports must be tied to ground.

Table 5. STR750F pin description

|          | Pin      | n°      |         |                                  |      |                | In       | put   |                   | C          | utpu   | ıt | 5                 |                                                  |                                                        |                      |

|----------|----------|---------|---------|----------------------------------|------|----------------|----------|-------|-------------------|------------|--------|----|-------------------|--------------------------------------------------|--------------------------------------------------------|----------------------|

| LQPFP100 | LFBGA100 | LQPFP64 | LFBGA64 | Pin Name                         | Type | Input Level    | floating | pd/nd | Ext. int /Wake-up | Capability | OD (1) | PP | Usable in Standby | Main<br>function<br>(after<br>reset)             | Alternate                                              | e function           |

| 1        | B1       | 1       | B1      | P1.12 /<br>ADC_IN13              | I/O  | T <sub>T</sub> | X        | Х     | EIT12             | 08         | Х      | Х  |                   | Port 1.12                                        | ADC: Analog input 13                                   |                      |

| 2        | B2       | 2       | C2      | P0.02 /<br>TIM2_OC1 /<br>ADC_IN0 | I/O  | T <sub>T</sub> | x        | X     | EIT0              | 08         | х      | х  |                   | Port 0.02                                        | TIM2: Output<br>Compare 1 <sup>(2)</sup>               | ADC: Analog input 0  |

| 3        | ВЗ       | 3       | C1      | P0.01 / TIM0_TI1<br>/ MCO        | I/O  | T <sub>T</sub> | x        | х     |                   | O8         | х      | х  |                   | Port 0.01                                        | TIM0: Input<br>Capture / trigger<br>/ external clock 1 | Main Clock<br>Output |

| 4        | C2       | 4       | C3      | P0.00 /<br>TIM0_OC1 /<br>BOOT0   | I/O  | T <sub>T</sub> | х        | х     |                   | O8         | х      | х  |                   | Port 0.00 /<br>Boot mode<br>selection<br>input 0 | TIM0: Output Compare 1                                 |                      |

| 5        | C1       |         |         | P0.31 / TIM1_TI2                 | I/O  | T <sub>T</sub> | х        | Х     |                   | 02         | х      | Х  |                   | Port 0.31                                        | TIM1: Input Capture / trigger / external clock 2       |                      |

| 6        | D2       |         |         | P0.30 /<br>TIM1_OC2              | I/O  | T <sub>T</sub> | х        | Х     |                   | O2         | х      | х  |                   | Port 0.30                                        | TIM1: Output Compare 2                                 |                      |

577

Pin Description STR750F

Table 5. STR750F pin description (continued)

| The company     |          | Pin      | n°      |         | H750F pill de |      |                |          | put   |                   | Ĺ          | utpu   | ıt | >                 |                                    |                                                                                       |                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|---------|---------|---------------|------|----------------|----------|-------|-------------------|------------|--------|----|-------------------|------------------------------------|---------------------------------------------------------------------------------------|------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | LQPFP100 | LFBGA100 | LQPFP64 | LFBGA64 | Pin Name      | Type | Input Level    | floating | pd/nd | Ext. int /Wake-up | Capability | OD (1) | PP | Usable in Standby | function<br>(after                 | Alternate                                                                             | e function                         |

| S   E1   6   D   TIMI_OC1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7        | D1       | 5       | D1      |               | I/O  | T <sub>T</sub> | х        | Х     |                   | 02         | Х      | х  |                   | Port 0.29                          |                                                                                       | ADC: Analog input 8                |

| 10   E4   8   D4   VSS_IO   S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8        | E1       | 6       | D2      |               | I/O  | T <sub>T</sub> | х        | Х     |                   | 02         | Х      | Х  |                   | Port 0.28                          | TIM1: Output Con                                                                      | npare 1                            |

| 11   E2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9        | E5       | 7       | D3      | TEST          | ı    |                |          |       |                   |            |        |    |                   | Reserved, mu                       | ust be tied to ground                                                                 | d                                  |

| 11   E2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10       | E4       | 8       | D4      | VSS_IO        | S    |                |          |       |                   |            |        |    |                   | Ground Voltage                     | ge for digital I/Os                                                                   |                                    |

| 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11       | E2       |         |         | UART1_RTS /   | I/O  | T <sub>T</sub> | х        | х     |                   | O2         | х      | х  |                   | Port 0.23                          | To Send                                                                               | ADC analog input                   |

| 13   F1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12       | F5       |         |         |               | I/O  | T <sub>T</sub> | х        | Х     |                   | 02         | Х      | Х  |                   | Port 2.04                          | TIM2: Output<br>Compare 1 <sup>(2)</sup>                                              |                                    |

| 15   E3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13       | F1       |         |         |               | I/O  | T <sub>T</sub> | х        | х     |                   | O2         | х      | х  |                   | Port 2.03                          | To Send                                                                               |                                    |

| 15   E3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 14       | F4       |         |         | P2.02         | I/O  | T <sub>T</sub> | Х        | Х     |                   | 02         | Х      | Х  |                   | Port 2.02                          |                                                                                       |                                    |

| 17   F3   10   E3   P0.20 / UART1_RX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 15       | E3       |         |         | UART1_CTS /   | I/O  | T <sub>T</sub> | х        | х     |                   | O2         | х      | х  |                   | Port 0.22                          |                                                                                       | ADC: Analog input 5                |

| 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 16       | F2       | 9       | E4      |               | 9    | T <sub>T</sub> | X        | Х     |                   | 02         | Х      | Х  |                   | Port 0.21                          |                                                                                       |                                    |

| 18   G3   11   E2   P1.19 / JTMS   I/O   T <sub>T</sub>   X   X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17       | F3       | 10      | E3      |               | I/O  | T <sub>T</sub> | х        | Х     |                   | 02         | Х      | Х  |                   | Port 0.20                          | UART1: Receive of (remappable to Po                                                   | data input<br>0.14) <sup>(2)</sup> |

| 19   G2   I2   E1   F1.16/JTCK   I/O   IT   X   X   O2   X   X   Input <sup>(4)</sup>   Folt 1.16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 18       | G3       | 11      | E2      | P1.19 / JTMS  | I/O  | T <sub>T</sub> | Х        | х     |                   | O2         | х      | х  |                   | selection                          | Port 1.19                                                                             |                                    |

| 20 H3 H3 H4 P1.17/3IDU WO TT X X O8 X X Output(4) Port 1.17  21 H2 14 F3 P1.16/JTDI WO TT X X O2 X X JTAG data input(4) Port 1.16  22 G1 15 F2 NJTRST I TT JTAG reset input(3)  23 G4 P2.01 WO TT X X O2 X X Port 2.01  24 G5 P2.00 WO TT X X O2 X X Port 2.00  25 H1 16 F1 P0.13/RTCK/ UARTO_RTS WO TT X X X O8 X X UARTO_RTS WO TT X X X O8 X X UARTO_RTS WO TT A DC: | 19       | G2       | 12      | E1      | P1.18 / JTCK  | I/O  | T <sub>T</sub> | Х        | Х     |                   | 02         | Х      | х  |                   | JTAG clock<br>input <sup>(4)</sup> | Port 1.18                                                                             |                                    |

| 21 H2 14 F3 P1.16/3IDI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20       | НЗ       | 13      | F4      | P1.17 / JTDO  | I/O  | T <sub>T</sub> | Х        | Х     |                   | 08         | Х      | х  |                   |                                    | Port 1.17                                                                             |                                    |

| 23 G4 P2.01 I/O T <sub>T</sub> X X O2 X X Port 2.01  24 G5 P2.00 I/O T <sub>T</sub> X X O2 X X Port 2.00  25 H1 16 F1 P0.13 / RTCK / UARTO_RTS I/O T <sub>T</sub> X X X O8 X X D4 Port 2.00  UARTO_RTS I/O T <sub>T</sub> X X X O8 X X D4 Port 2.00  UARTO: Ready To Send of Output (4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 21       | H2       | 14      | F3      | P1.16 / JTDI  | I/O  | T <sub>T</sub> | Х        | Х     |                   | 02         | Х      | Х  |                   |                                    | Port 1.16                                                                             |                                    |

| 24 G5 P2.00 I/O T <sub>T</sub> X X O2 X X Port 2.00  25 H1 16 F1 P0.13 / RTCK / UARTO_RTS I/O T <sub>T</sub> X X X O8 X X JTAG return clock output(4) UARTO: Ready To Send or UARTO: Ready To Send or UARTO: Clock To ADC: ADC: ADC: ADC: ADC: ADC: ADC: ADC:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 22       | G1       | 15      | F2      | NJTRST        | ı    | T <sub>T</sub> |          |       |                   |            |        |    |                   | JTAG reset in                      | put <sup>(3)</sup>                                                                    |                                    |

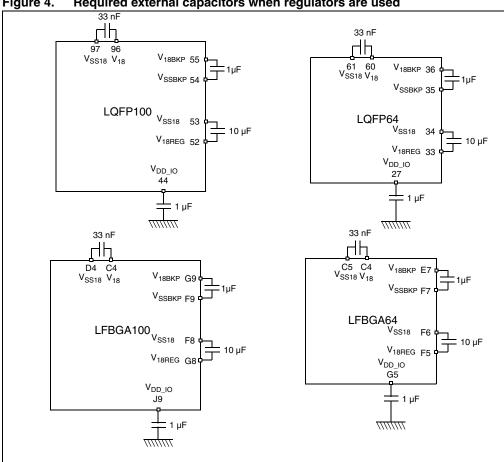

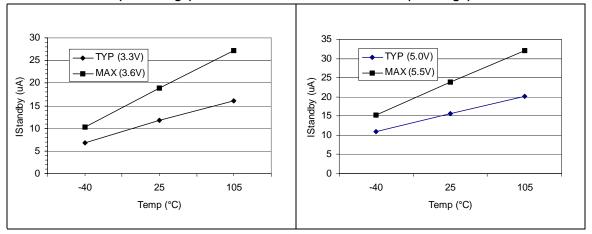

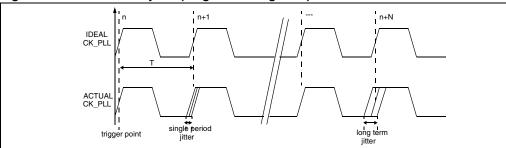

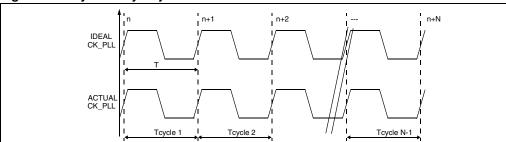

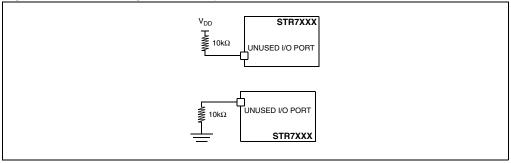

| 25 H1 16 F1 P0.13 / RTCK / UARTO_RTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 23       | G4       |         |         | P2.01         | I/O  | T <sub>T</sub> | х        | Х     |                   | 02         | Х      | Х  |                   | Port 2.01                          |                                                                                       |                                    |