# zilog

### **Crimzon<sup>®</sup> Infrared Microcontrollers**

## ZLF645 Series Flash MCUs with Learning Amplification

#### **Product Specification**

PS026407-0408

Copyright ©2008 by Zilog<sup>®</sup>, Inc. All rights reserved. www.zilog.com

#### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2008 by Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8 and Crimzon are registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

Zilog products are designed and manufactured under an ISO registered 9001:2000 Quality Management System. For more details, please visit www.zilog.com/quality.

## **Revision History**

Each instance in the revision history table reflects a change to this document from its previous revision. For more details, refer to the corresponding pages or appropriate links given in the table below.

| Date            | Version | Description                                                                                                                                     | Page<br>Number |

|-----------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| April<br>2008   | 07      | Updated Enabling The Flash Byte Programming Interface section                                                                                   | 76             |

| April<br>2008   | 06      | Deleted "Design Info" subsection and all of its associated text.                                                                                | All            |

|                 |         | Updated Flash Memory Overview section; updated Figure 19.                                                                                       | 64, 65         |

|                 |         | Updated Flash Frequency High and Low Byte Registers section.                                                                                    | 74             |

|                 |         | Updated Icc and Icc1 in Table 81.                                                                                                               | 160            |

|                 |         | Updated notes in Table 5 and Table 6.                                                                                                           | 9, 10          |

|                 |         | Removed "Preliminary" and "Precharacterization Product" notice.                                                                                 | All            |

|                 |         | Added 20-pin QFN package to Pin Description, Table 3,                                                                                           | 5, 6, 7,       |

|                 |         | Table 4, Packaging, Table 88, and Part Number                                                                                                   | 171,           |

|                 |         | Description.                                                                                                                                    | 180, 182       |

|                 |         | Change P31 to P32 at the beginning of Universal Asynchronous Receiver/Transmitter.                                                              | 79             |

| January<br>2008 | 05      | Updated Flash Operation Timing Using Flash Frequency<br>Registers and Flash Frequency High and Low Byte<br>Registers.                           | 68, 74         |

| January<br>2008 | 04      | Chapter Reset and Power Management: Updated Table 69.                                                                                           | 137            |

| January<br>2008 | 03      | Replaced Advance with Preliminary and added<br>Precharacterization Product section. Updated Table 81,<br>Table 82, and Table 83.                | All            |

| August<br>2007  | 02      | Updated Memory and Registers section; Added description to Stack.                                                                               | 42             |

|                 |         | Updated ICP Interface section; Table 30, Field for Bit 0 changed from RST to Reserved.                                                          | 61             |

|                 |         | Updated Reset and Power Management section;<br>Watchdog Timer, changed the Field for Bits 6 through Bits 4<br>from Reserved to Time-Out Select. | 136            |

|                 |         | Minor updates throughout the document.                                                                                                          | All            |

## **Table of Contents**

| Architectural Overview 1         |

|----------------------------------|

| Features                         |

| Interrupt Sources                |

| Additional Features 2            |

| Functional Block Diagram 4       |

| Pin Description                  |

| I/O Port Pin Functions           |

| RESET (Input, Active Low) 18     |

| Port 0                           |

| Port 1                           |

| Port 2                           |

| Port 3                           |

| Comparator Inputs 28             |

| Comparator Outputs 28            |

| Port 4                           |

| Port Configuration Register 30   |

| Port 0/1 Mode Register 31        |

| Port 0 Register                  |

| Port 1 Register                  |

| Port 2 Mode Register             |

| Port 2 Register                  |

| Port 3 Mode Register             |

| Port 3 Register                  |

| Port 4 Mode Register             |

| Port 4 Register                  |

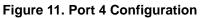

| Memory and Registers 41          |

| Flash Program/Constant Memory 41 |

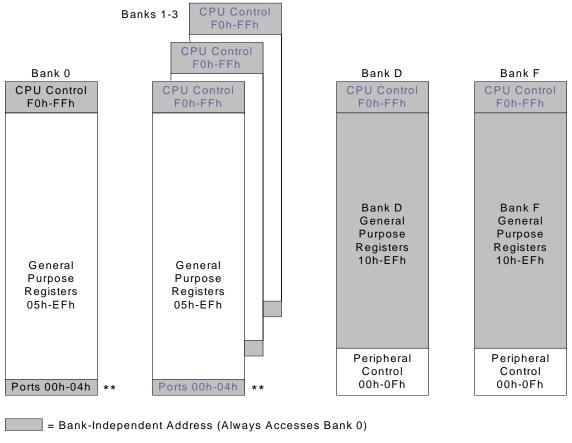

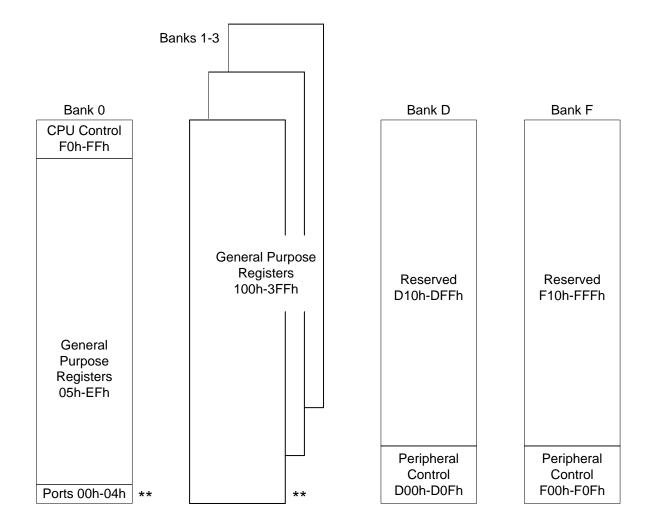

| Register File                    |

| Stack                            |

| Register Pointer Example 45      |

| Linear Memory Addressing 45      |

| Register Pointer Register 48     |

| Stack Pointer Register           |

| Register File Summary                                         | . 50 |

|---------------------------------------------------------------|------|

| ICP Interface                                                 | . 53 |

| Enabling ICP Mode                                             | . 53 |

| State of ZLF645 in ICP Mode                                   | . 53 |

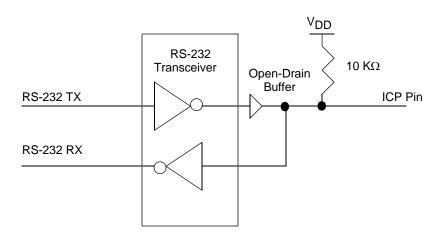

| Enabling Flash Accesses Through the ICP                       | . 54 |

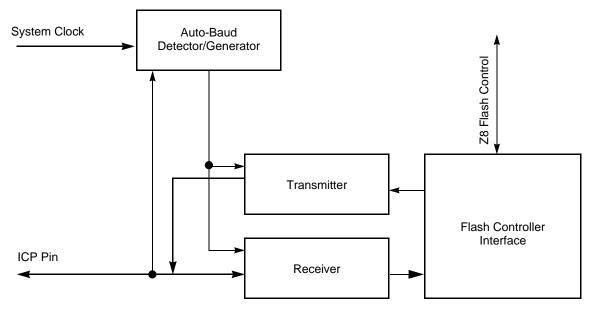

| ICP Interface Logic Architecture                              | . 54 |

| ICP Interface Operation                                       |      |

| ICP Data Format                                               |      |

| ICP Auto-Baud Detector/Generator                              |      |

| ICP In-Circuit Programming Commands                           |      |

| In-Circuit Programming Control Register Definitions           |      |

|                                                               |      |

| ICP Status Register                                           |      |

| TEST Mode Register                                            | . 63 |

| Exiting ICP Mode                                              | . 63 |

| Flash Controller                                              | . 64 |

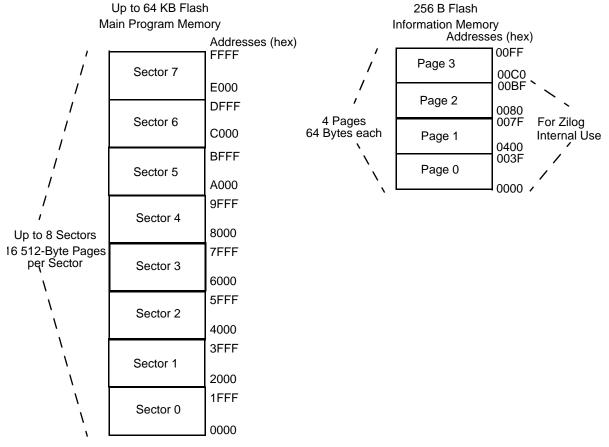

| Flash Memory Overview                                         | . 64 |

| Flash Information Block                                       | . 65 |

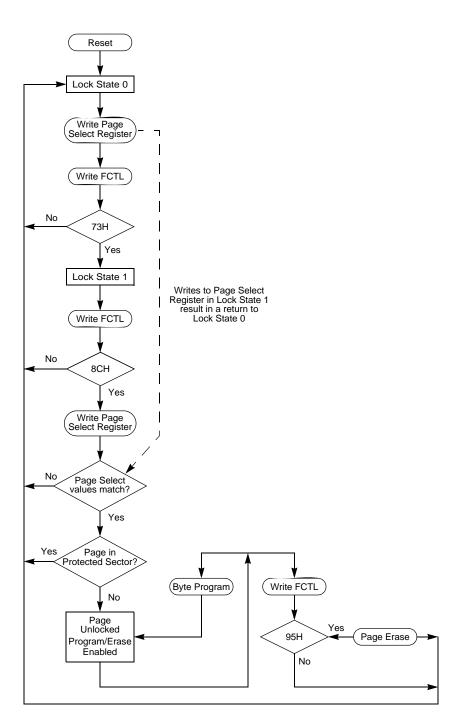

| Flash Controller Operation                                    |      |

| Flash Operation Timing Using Flash Frequency Registers        |      |

| Flash Code Protection Against External Access                 |      |

| Byte Programming                                              |      |

| Page Erase                                                    |      |

| Mass Erase                                                    | . 70 |

| Flash Control Register Definitions                            | . 71 |

| Flash Control Register                                        |      |

| Flash Status Register                                         |      |

| Flash Page Select Register      Flash Sector Protect Register |      |

| Flash Frequency High and Low Byte Registers                   |      |

| Flash Controller Functions Summary                            |      |

| Flash Byte Programming Interface                              | . 76 |

| Enabling The Flash Byte Programming Interface                 |      |

| Flash Byte Programming Interface Flash Access Restrictions    |      |

| Infrared Learning Amplifier                                   | . 78 |

|                                                               |      |

| Universal Asynchronous Receiver/Transmitter            | 79  |

|--------------------------------------------------------|-----|

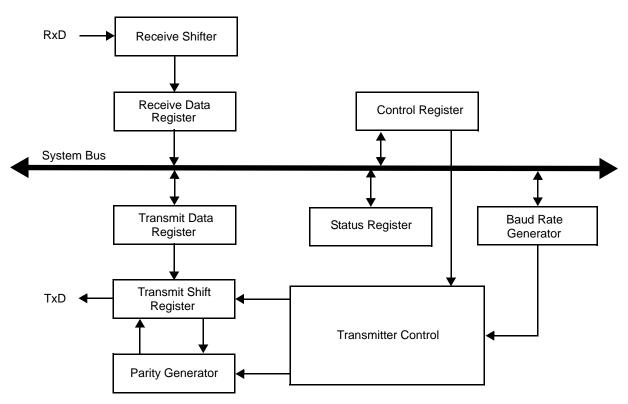

| Architecture                                           | 80  |

| Operation                                              | 80  |

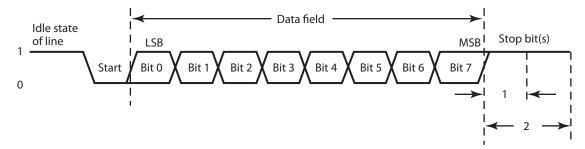

| Data Format                                            | 81  |

| Transmitting Data Using Polled Method                  | 81  |

| Transmitting Data Using Interrupt-Driven Method        | 82  |

| Receiving Data Using the Polled Method                 | 83  |

| Receiving Data Using the Interrupt-Driven Method       | 83  |

| UART Interrupts                                        |     |

| UART Baud Rate Generator                               | 87  |

| UART Receive Data Register/UART Transmit Data Register | 89  |

| UART Status Register                                   | 89  |

| UART Control Register                                  | 90  |

| UART Baud Rate Generator Constant Register             |     |

| Timers                                                 | 93  |

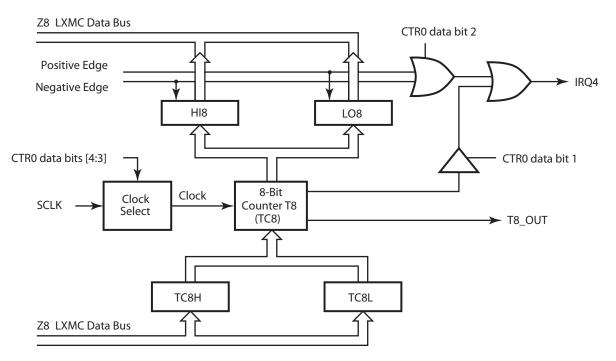

| Counter/Timer Functional Blocks                        | 94  |

| Input Circuit                                          | 94  |

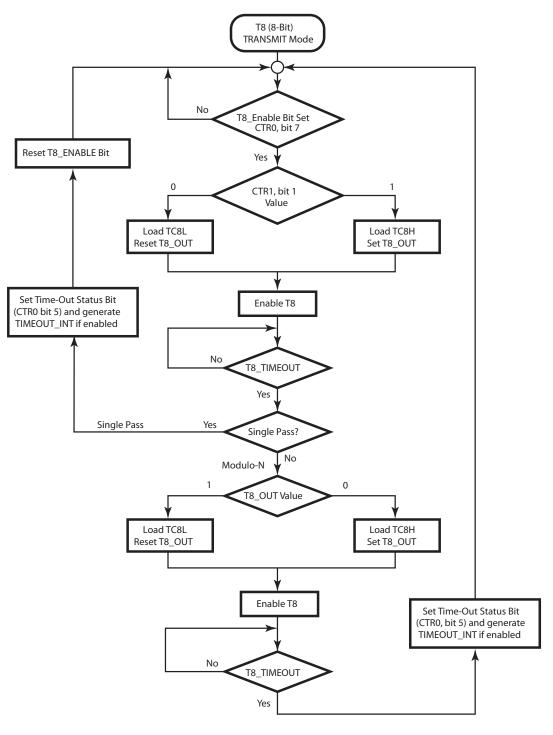

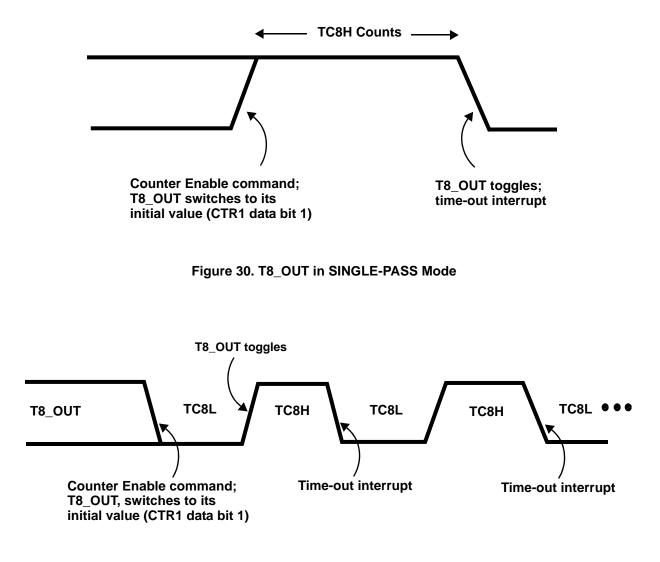

| T8 TRANSMIT Mode                                       | 95  |

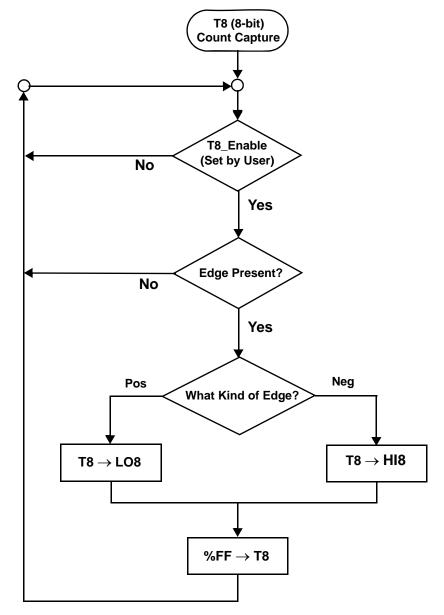

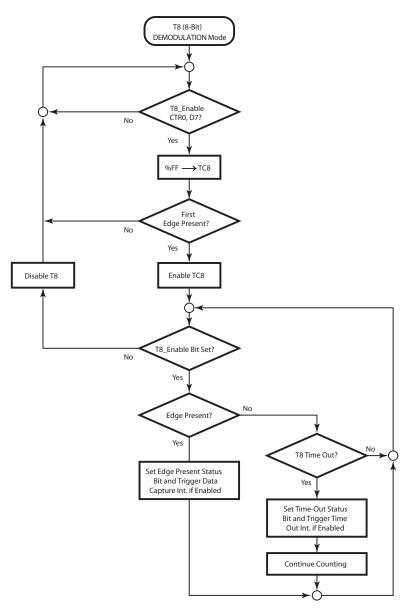

| T8 DEMODULATION Mode                                   | 99  |

| T16 TRANSMIT Mode                                      | 103 |

| T16 DEMODULATION Mode                                  | 104 |

| PING-PONG Mode                                         | 105 |

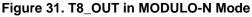

| Timer Output                                           | 106 |

| Counter/Timer Registers                                | 108 |

| Timer 8 Capture High Register                          | 108 |

| Timer 8 Capture Low Register                           | 108 |

| Timer 16 Capture High Register                         |     |

| Timer 16 Capture Low Register                          | 110 |

| Counter/Timer 16 High Hold Register                    | 110 |

| Counter/Timer 16 Low Hold Register                     |     |

| Counter/Timer 8 High Hold Register                     |     |

| Counter/Timer 8 Low Hold Register                      |     |

| Counter/Timer 8 Control Register                       |     |

| T8 and T16 Common Functions Register                   |     |

| Counter/Timer 16 Control Register                      |     |

| Timer 8/Timer 16 Control Register                      | 119 |

| Interrupts                                             |     |

| Interrupt Priority Register                            | 124 |

| Interrupt Request Register                             | 125 |

| Interrupt Mask Register                     | 127 |

|---------------------------------------------|-----|

|                                             | 128 |

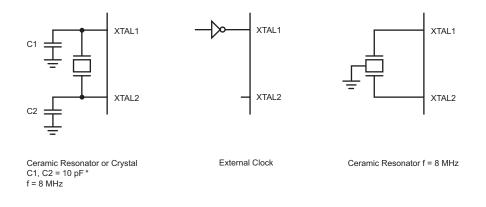

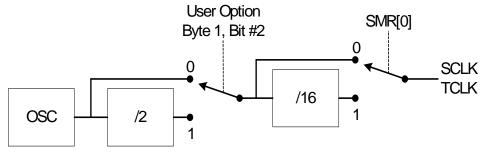

| Clock                                       | 129 |

| Crystal 1 Oscillator Pin (XTAL1)            | 130 |

| Crystal 2 Oscillator Pin (XTAL2)            | 130 |

| Internal Clock Signals (SCLK and TCLK)      | 130 |

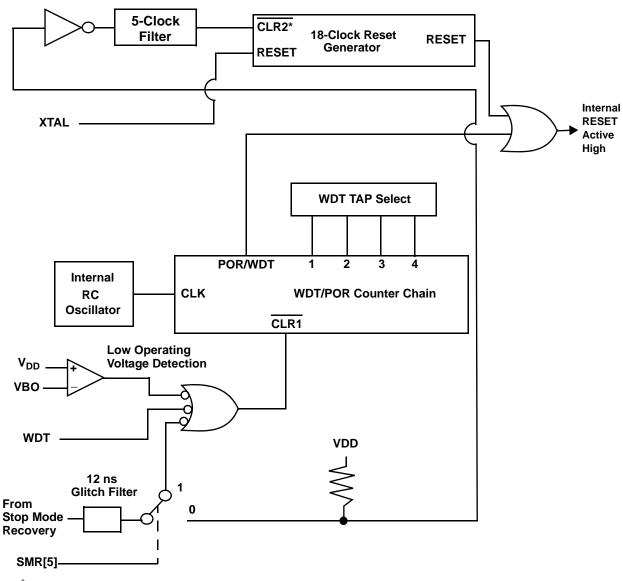

| Reset and Power Management                  | 132 |

| Voltage Brownout Standby                    | 134 |

| STOP Mode                                   | 134 |

| HALT Mode                                   | 134 |

| Voltage Detection                           | 135 |

| Power-On Reset Timer                        | 136 |

| Watchdog Timer                              | 136 |

| Reset/Stop Mode Recovery Status             | 137 |

| Fast Stop Mode Recovery                     |     |

| Stop Mode Recovery Interrupt                | 138 |

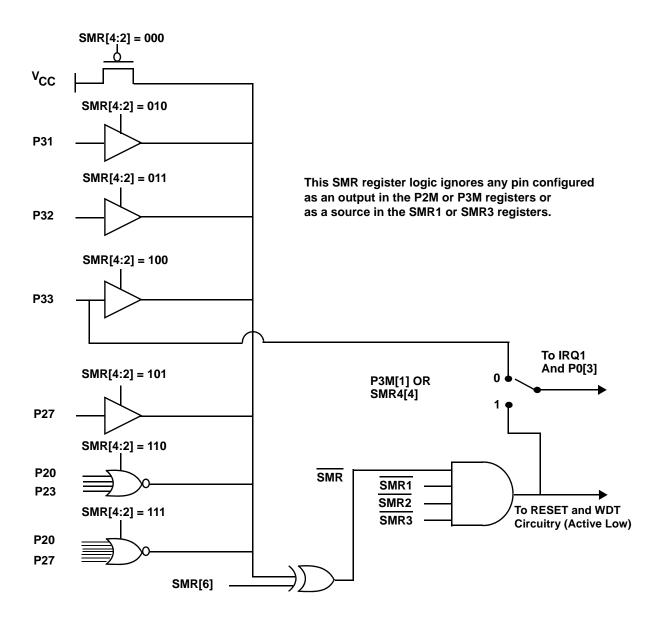

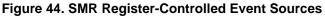

| Stop Mode Recovery Event Sources            | 138 |

| SMR Register Events                         |     |

| SMR1 Register Events                        |     |

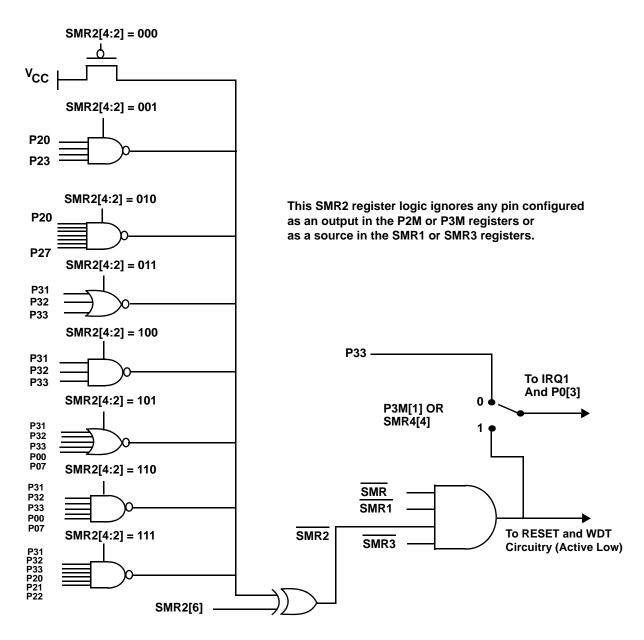

| SMR2 Register Events                        |     |

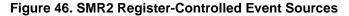

| SMR3 Register Events                        |     |

| Stop Mode Recovery Register 4               |     |

| Z8 LXMC CPU Programming Summary             | 152 |

| Addressing Notation                         | 152 |

| Flags Register                              | 155 |

| Condition Codes                             | 156 |

| Electrical Characteristics                  | 158 |

| Absolute Maximum Ratings                    | 158 |

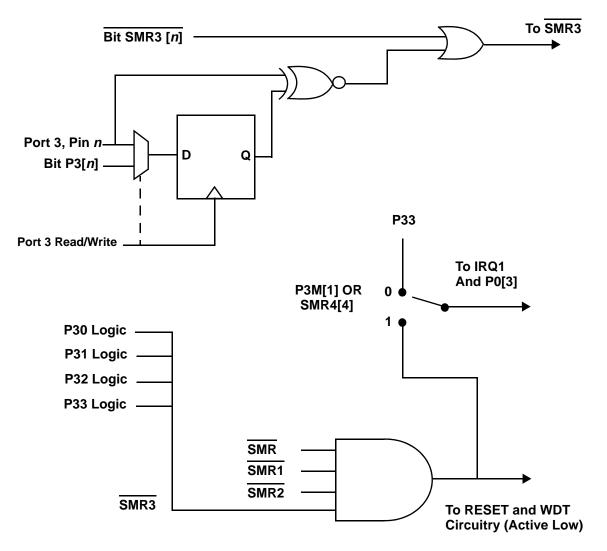

| Standard Test Conditions                    | 159 |

| Capacitance                                 | 159 |

| DC Characteristics                          | 160 |

| AC Characteristics                          | 163 |

| Flash Option Bits                           | 166 |

| Operation                                   | 166 |

| Option Bit Shadow Register Loading By Reset | 166 |

| User Option Bit Locations in Flash Memory   | 167 |

vii

| User Option Bit Shadow Register Access               | 167 |

|------------------------------------------------------|-----|

| User Option Byte 0 and Option Byte 0 Shadow          |     |

| Register Definitions                                 | 167 |

| User Option Byte 1 and Option Byte 1 Shadow Register |     |

| Definitions                                          | 168 |

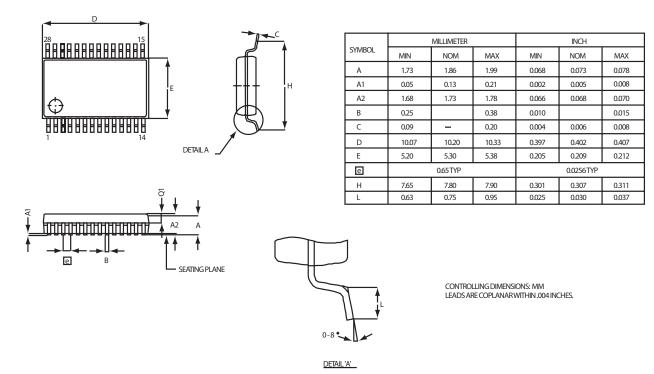

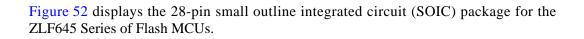

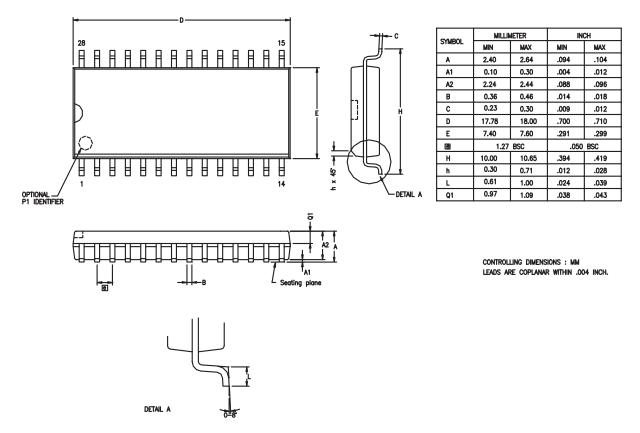

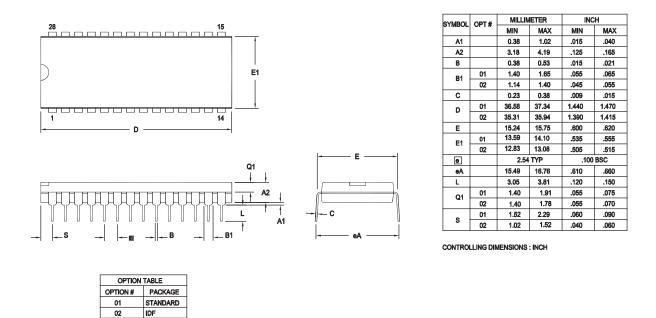

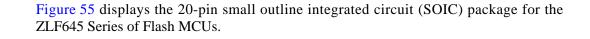

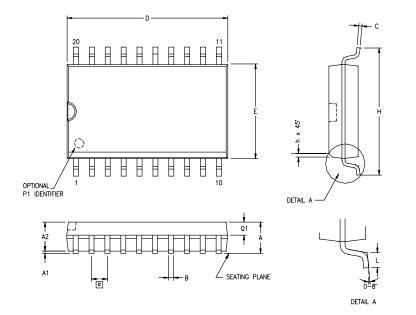

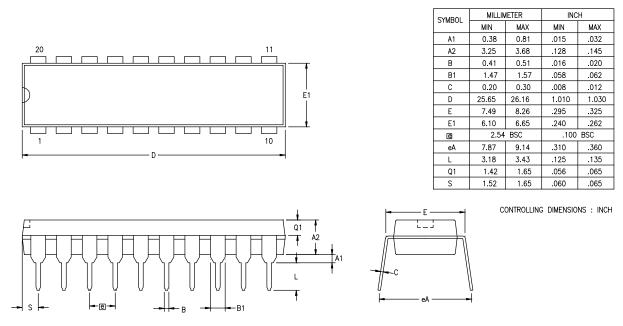

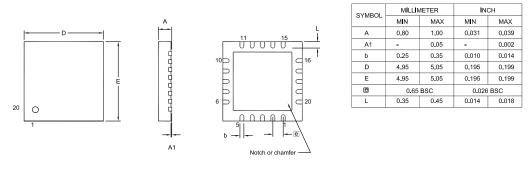

| Packaging                                            | 171 |

| Ordering Information                                 | 180 |

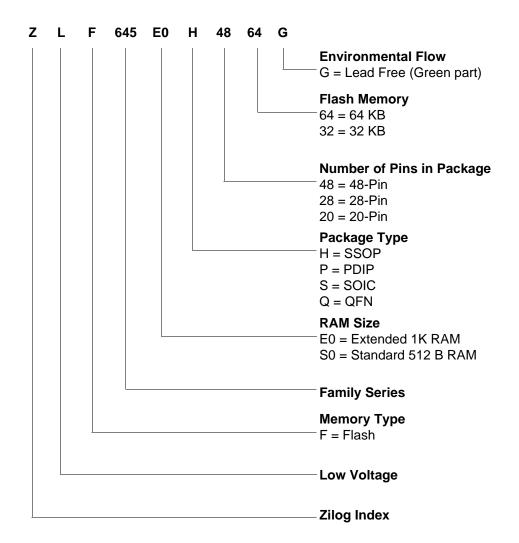

| Part Number Description                              | 182 |

| Index                                                | 183 |

| Customer Support                                     | 189 |

## **Architectural Overview**

Zilog's ZLF645 Series of Flash MCU's are members of the Crimzon<sup>®</sup> family of infrared microcontrollers. This series provides a directly-compatible code upgrade path to other Crimzon MCUs, offers a robust learning function, and features up to 64 KB Flash memory and 1K general-purpose Random Access Memory (RAM). Two timers allow the generation of complex signals while performing other counting operations.

A Universal Asynchronous Receiver/Transmitter (UART) allows the ZLF645 MCU to function as a slave/master database chip. When the UART is not in use, the Baud Rate Generator (BRG) can be used as a third timer. Enhanced Stop Mode Recovery features allow the ZLF645 MCU to recover from STOP mode on any change of logic and on any combination of the 12 SMR inputs. The SMR source can also be used as an interrupt source.

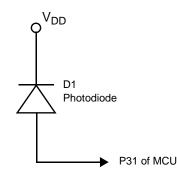

Many high-end remote control units offer a learning function. A learning function allows a replacement remote unit to learn infrared signals from the original remote unit and regenerate the signal. However, the amplifying circuits of many learning remotes are expensive and are not tuned well. The ZLF645 MCU is the first chip to offer a built-in tuned amplification circuit in a wide range of positions and battery voltages. The only external component required is a photodiode.

The ZLF645 MCU greatly reduces the system cost and improves learning function reliability. With all new features, the ZLF645 MCU is excellent for infrared remote control and other MCU applications.

#### Features

Table 1 lists the memory, I/O, and power features of the ZLF645 Flash MCU. Additional features are listed below the table.

| Device                                         | Flash (KB) | RAM*         | I/O Lines     | Voltage<br>Range |  |

|------------------------------------------------|------------|--------------|---------------|------------------|--|

| ZLF645 Flash<br>MCU                            | 32 or 64   | 512 B or 1 K | 16, 24, or 40 | 2.0 V-3.6 V      |  |

| *General-purpose registers implemented as RAM. |            |              |               |                  |  |

#### Table 1. ZLF645 Flash MCU Features

#### **Interrupt Sources**

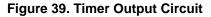

The ZLF645 MCU supports 23 interrupt sources with 6 interrupt vectors, as given below:

- Three external interrupts.

- Two from T8, T16 time-out and capture.

- Three from UART Tx, UART Rx, and UART BRG.

- One from LVD.

- Fourteen from SMR source P20-P27, P30-P33, P00, and P07:

- Any change in logic from P20-P27, P30-P33 can generate an interrupt or SMR

#### **Additional Features**

The additional features of ZLF645 MCU include:

- IR learning amplifier.

- Low power consumption—11 mW (typical).

- Three standby modes:

- STOP—1.7  $\mu$ A (typical)

- HALT-0.6 mA (typical)

- Low-voltage reset

- Intelligent counter/timer architecture to automate generation or reception and demodulation of complex waveform, and pulsed signals:

- One programmable 8-bit counter/timer with two capture registers and two load registers

- One programmable 16-bit counter/timer with one 16-bit capture register pair and one 16-bit load register pair

- Programmable input glitch filter for pulse reception

- The UART baud rate generator can be used as another 8-bit timer, when the UART is not in use

- Six priority interrupts:

- Three external/UART interrupts

- Two assigned to counter/timers

- One low-voltage detection interrupt

- 8-bit UART:

- R<sub>X</sub> and T<sub>X</sub> interrupts

- 4800, 9600, 19200, and 38400 baud rates

- Parity Odd/Even/None

- Stop bits 1/2

- ICP (In-circuit Flash Programming) interface multiplexed with one of the GPIO's.

- Intelligent Power-On Reset (POR) to provide reduced POR time on detection of stable clock from external crystal oscillator or resonator.

- Low-voltage and high-voltage detection flags.

- Programmable Watchdog Timer (WDT)/POR circuits.

- Two on-board analog comparators with independent reference voltages and programmable interrupt polarity.

- User-selectable options through option bit Flash coding (ON/OFF):

- Port 0 pins 0–3 pull-up transistors

- Port 0 pins 4–7 pull-up transistors

- Port 1 pins 0–3 pull-up transistors

- Port 1 pins 4–7 pull-up transistors

- Port 2 pins 0–7 pull-up transistors

- Port 3 pins 0–3 pull-up transistors

- Port 4 pins 0–7 pull-up transistors

- WDT enabled at Power-On Reset

- Flash lowest half main memory protect

- Flash entire main memory protect

- 16-bit addressability for stack pointer

- No division, divide by 2, divide by 16, or divide by 32 of external clock to system clock

**Note:** All signals with an overline, " $\overline{}$ ", are active Low. For example,  $\overline{B/W}$ , in which WORD is active Low, and  $\overline{B}/W$ , in which BYTE is active Low.

Power connections use the conventional descriptions listed in Table 2.

#### **Table 2. Power Connections**

| Connection | Device          |

|------------|-----------------|

| Power      | V <sub>DD</sub> |

| Ground     | V <sub>SS</sub> |

#### **Functional Block Diagram**

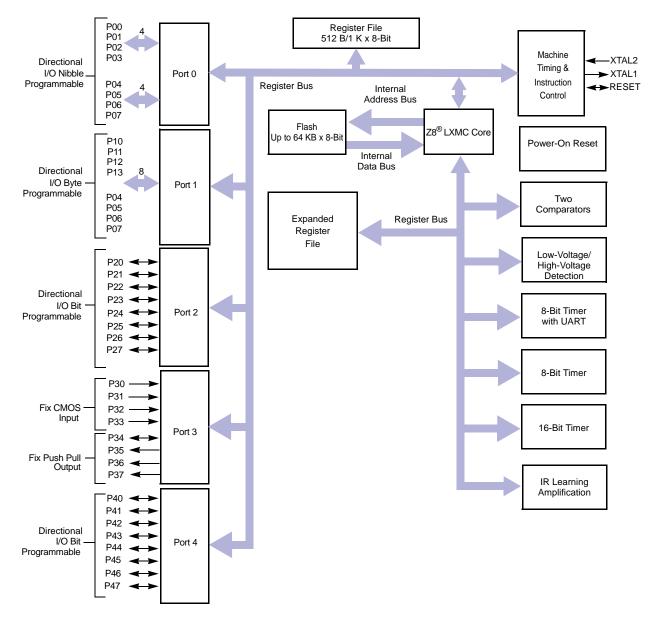

Figure 1 displays the functional blocks of the ZLF645 Flash MCU.

## **Pin Description**

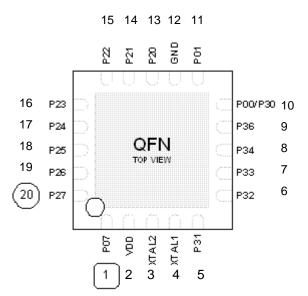

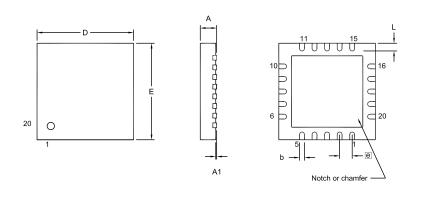

Figure 2 displays the pin configuration for ZLF645 MCU 20-pin QFN packages.

Figure 2. 20-Pin QFN Pin Configuration

Table 3 lists the function and signal directions of each pin within the 20-pin QFN package sequentially by pin number.

| Pin No | Symbol          | Function           | Signal Direction |

|--------|-----------------|--------------------|------------------|

| 1      | P07             | Port 0, bit 7      | Input/Output     |

| 2      | V <sub>DD</sub> | Power Supply       | Input            |

| 3      | XTAL2           | Crystal oscillator | Output           |

| 4      | XTAL1           | Crystal oscillator | Input            |

| 5      | P31             | Port 3, bit 1      | Input            |

| 6      | P32             | Port 3, bit 2      | Input            |

| 7      | P33             | Port 3, bit 3      | Input            |

| 8      | P34             | Port 3, bit 4      | Input/Output     |

| 9      | P36             | Port 3, bit 6      | Output           |

| 10     | P00             | Port 0, bit 0      | Input/Output     |

|        | P30             | Port 3, bit 0      | Input            |

| 11     | P01             | Port 0, bit 1      | Input/Output     |

| 12     | GND             | Ground             | Input            |

| 13     | P20             | Port 2, bit 0      | Input/Output     |

| 14     | P21             | Port 2, bit 1      | Input/Output     |

| 15     | P22             | Port 2, bit 2      | Input/Output     |

| 16     | P23             | Port 2, bit 3      | Input/Output     |

| 17     | P24             | Port 2, bit 4      | Input/Output     |

| 18     | P25             | Port 2, bit 5      | Input/Output     |

| 19     | P26             | Port 2, bit 6      | Input/Output     |

|        | P27             | Port 2, bit 7      | Input/Output     |

#### Table 3. 20-Pin QFN Sequential Pin Identification

Table 4 lists the function and signal direction of each pin within the 20-pin QFN package by function.

| Pin No | Symbol          | Function           | Signal Direction |

|--------|-----------------|--------------------|------------------|

| 10     | P00             | Port 0, bit 0      | Input/Output     |

|        | P30             | Port 3, bit 0      | Input            |

| 11     | P01             | Port 0, bit 1      | Input/Output     |

| 1      | P07             | Port 0, bit 7      | Input/Output     |

| 13     | P20             | Port 2, bit 0      | Input/Output     |

| 14     | P21             | Port 2, bit 1      | Input/Output     |

| 15     | P22             | Port 2, bit 2      | Input/Output     |

| 16     | P23             | Port 2, bit 3      | Input/Output     |

| 17     | P24             | Port 2, bit 4      | Input/Output     |

| 18     | P25             | Port 2, bit 5      | Input/Output     |

| 19     | P26             | Port 2, bit 6      | Input/Output     |

| 20     | P27             | Port 2, bit 7      | Input/Output     |

| 5      | P31             | Port 3, bit 1      | Input            |

| 6      | P32             | Port 3, bit 2      | Input            |

| 7      | P33             | Port 3, bit 3      | Input            |

| 8      | P34             | Port 3, bit 4      | Input/Output     |

| 9      | P36             | Port 3, bit 6      | Output           |

| 2      | V <sub>DD</sub> | Power Supply       | Input            |

| 12     | GND             | Ground             | Input            |

| 4      | XTAL1           | Crystal oscillator | Input            |

| 3      | XTAL2           | Crystal oscillator | Output           |

Table 4. 20-Pin QFN Functional Pin Identification

**Note:** When the Port 0 low-nibble pull-up option is enabled and the P30 input is Low, current flows through the pull-up to Ground.

8

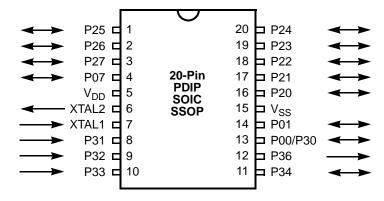

Figure 3 displays the pin configuration for ZLF645 MCU 20-pin PDIP, SOIC, and SSOP packages.

Figure 3. 20-Pin PDIP/SOIC/SSOP Pin Configuration

Table 5 lists the function and signal directions of each pin within the 20-pin PDIP, SOIC, and SSOP packages sequentially by pin number.

| Pin No | Symbol          | Function           | Signal Direction |

|--------|-----------------|--------------------|------------------|

| 1      | P25             | Port 2, bit 5      | Input/Output     |

| 2      | P26             | Port 2, bit 6      | Input/Output     |

| 3      | P27             | Port 2, bit 7      | Input/Output     |

| 4      | P07             | Port 0, bit 7      | Input/Output     |

| 5      | V <sub>DD</sub> | Power Supply       | Input            |

| 6      | XTAL2           | Crystal oscillator | Output           |

| 7      | XTAL1           | Crystal oscillator | Input            |

| 8      | P31             | Port 3, bit 1      | Input            |

| 9      | P32             | Port 3, bit 2      | Input            |

| 10     | P33             | Port 3, bit 3      | Input            |

| 11     | P34             | Port 3, bit 4      | Input/Output     |

| 12     | P36             | Port 3, bit 6      | Output           |

| 13     | P00             | Port 0, bit 0      | Input/Output     |

|        | P30             | Port 3, bit 0      | Input            |

| 14     | P01             | Port 0, bit 1      | Input/Output     |

| 15     | V <sub>SS</sub> | Ground             | Input            |

| 16     | P20             | Port 2, bit 0      | Input/Output     |

| 17     | P21             | Port 2, bit 1      | Input/Output     |

| 18     | P22             | Port 2, bit 2      | Input/Output     |

| 19     | P23             | Port 2, bit 3      | Input/Output     |

| 20     | P24             | Port 2, bit 4      | Input/Output     |

Table 6 lists the function and signal direction of each pin within the 20-pin PDIP, SOIC, and SSOP packages by function.

| Pin No | Symbol          | Function           | Signal Direction |  |

|--------|-----------------|--------------------|------------------|--|

| 13     | P00             | Port 0, bit 0      | Input/Output     |  |

|        | P30             | Port 3, bit 0      | Input            |  |

| 14     | P01             | Port 0, bit 1      | Input/Output     |  |

| 4      | P07             | Port 0, bit 7      | Input/Output     |  |

| 16     | P20             | Port 2, bit 0      | Input/Output     |  |

| 17     | P21             | Port 2, bit 1      | Input/Output     |  |

| 18     | P22             | Port 2, bit 2      | Input/Output     |  |

| 19     | P23             | Port 2, bit 3      | Input/Output     |  |

| 20     | P24             | Port 2, bit 4      | Input/Output     |  |

| 1      | P25             | Port 2, bit 5      | Input/Output     |  |

| 2      | P26             | Port 2, bit 6      | Input/Output     |  |

| 3      | P27             | Port 2, bit 7      | Input/Output     |  |

| 8      | P31             | Port 3, bit 1      | Input            |  |

| 9      | P32             | Port 3, bit 2      | Input            |  |

| 10     | P33             | Port 3, bit 3      | Input            |  |

| 11     | P34             | Port 3, bit 4      | Input/Output     |  |

| 12     | P36             | Port 3, bit 6      | Output           |  |

| 5      | V <sub>DD</sub> | Power Supply       | Input            |  |

| 15     | V <sub>SS</sub> | Ground             | Input            |  |

| 7      | XTAL1           | Crystal oscillator | Input            |  |

| 6      | XTAL2           | Crystal oscillator | Output           |  |

Table 6. 20-Pin PDIP/SOIC/SSOP Functional Pin Identification

**Note:** When the Port 0 low-nibble pull-up option is enabled and the P30 input is Low, current flows through the pull-up to Ground.

Figure 4 displays the pin configuration of the ZLF645 MCU within the 28-pin PDIP, SOIC, and SSOP packages.

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |  |

|-------------------------------------------------------|--|

|-------------------------------------------------------|--|

Figure 4. 28-Pin PDIP/SOIC/SSOP Pin Configuration

Table 7 lists the function and signal directions of each pin within the 28-pin PDIP, SOIC, and SSOP packages sequentially by pin number.

| Table 7. 28-Pin PDIP/SOIC/SSOP Sequential Pin Identification |  |

|--------------------------------------------------------------|--|

|                                                              |  |

| Pin No | Symbol          | Function                                  | Signal Direction |

|--------|-----------------|-------------------------------------------|------------------|

| 1      | P25             | Port 2, bit 5                             | Input/Output     |

| 2      | P26             | Port 2, bit 6                             | Input/Output     |

| 3      | P27             | Port 2, bit 7                             | Input/Output     |

| 4      | P04             | Port 0, bit 4                             | Input/Output     |

| 5      | P05             | Port 0, bit 5                             | Input/Output     |

| 6      | P06             | Port 0, bit 6                             | Input/Output     |

| 7      | P07             | Port 0, bit 7                             | Input/Output     |

| 8      | V <sub>DD</sub> | Power supply                              | Input            |

| 9      | XTAL2           | Crystal oscillator                        | Output           |

| 10     | XTAL1           | Crystal oscillator                        | Input            |

| 11     | P31             | Port 3, bit 1                             | Input            |

| 12     | P32             | Port 3, bit 2                             | Input            |

| 13     | P33             | Port 3, bit 3                             | Input            |

| 14     | P34             | Port 3, bit 4                             | Input/Output     |

| 15     | P35             | Port 3, bit 5                             | Output           |

| 16     | P37             | Port 3, bit 7                             | Output           |

| 17     | P36             | Port 3, bit 6                             | Output           |

| 18     | P30             | Port 3, bit 0; connect to VDD if not used | Input            |

| 19     | P00             | Port 0, bit 0                             | Input/Output     |

| 20     | P01             | Port 0, bit 1                             | Input/Output     |

| 21     | P02             | Port 0, bit 2                             | Input/Output     |

| 22     | V <sub>SS</sub> | Ground                                    | Input            |

| 23     | P03             | Port 0, bit 3                             | Input/Output     |

| 24     | P20             | Port 2, bit 0                             | Input/Output     |

| 25     | P21             | Port 2, bit 1                             | Input/Output     |

| 26     | P22             | Port 2, bit 2                             | Input/Output     |

| 27     | P23             | Port 2, bit 3                             | Input/Output     |

| 28     | P24             | Port 2, bit 4                             | Input/Output     |

Table 8 lists the functions and signal directions of each pin within the 28-pin PDIP, SOIC, and SSOP packages by function.

| Pin No | Symbol          | Function                                  | Signal Direction |  |

|--------|-----------------|-------------------------------------------|------------------|--|

| 19     | P00             | Port 0, bit 0                             | Input/Output     |  |

| 20     | P01             | Port 0, bit 1 Input/Output                |                  |  |

| 21     | P02             | Port 0, bit 2                             | Input/Output     |  |

| 23     | P03             | Port 0, bit 3                             | Input/Output     |  |

| 4      | P04             | Port 0, bit 4                             | Input/Output     |  |

| 5      | P05             | Port 0, bit 5                             | Input/Output     |  |

| 6      | P06             | Port 0, bit 6                             | Input/Output     |  |

| 7      | P07             | Port 0, bit 7                             | Input/Output     |  |

| 24     | P20             | Port 2, bit 0                             | Input/Output     |  |

| 25     | P21             | Port 2, bit 1                             | Input/Output     |  |

| 26     | P22             | Port 2, bit 2                             | Input/Output     |  |

| 27     | P23             | Port 2, bit 3                             | Input/Output     |  |

| 28     | P24             | Port 2, bit 4                             | Input/Output     |  |

| 1      | P25             | Port 2, bit 5                             | Input/Output     |  |

| 2      | P26             | Port 2, bit 6                             | Input/Output     |  |

| 3      | P27             | Port 2, bit 7                             | Input/Output     |  |

| 18     | P30             | Port 3, bit 0; connect to VDD if not used | Input            |  |

| 11     | P31             | Port 3, bit 1                             | Input            |  |

| 12     | P32             | Port 3, bit 2                             | Input            |  |

| 13     | P33             | Port 3, bit 3                             | Input            |  |

| 14     | P34             | Port 3, bit 4                             | Input/Output     |  |

| 15     | P35             | Port 3, bit 5                             | Output           |  |

| 17     | P36             | Port 3, bit 6                             | Output           |  |

| 16     | P37             | Port 3, bit 7                             | Output           |  |

| 8      | V <sub>DD</sub> | Power supply                              | Input            |  |

| 22     | V <sub>SS</sub> | Ground                                    | Input            |  |

| 10     | XTAL1           | Crystal oscillator                        | Input            |  |

| 9      | XTAL2           | Crystal oscillator                        | Output           |  |

Table 8. 28-Pin PDIP/SOIC/SSOP Functional Pin Identification

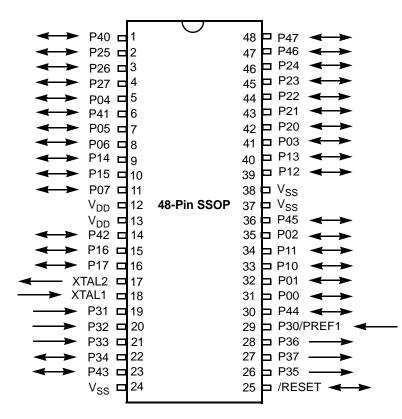

Figure 5 displays the pin configuration of the ZLF645 MCU within the 48-pin SSOP package.

Figure 5. 48-Pin SSOP Pin Configuration

Table 9 lists the functions and signal directions of each pin within the 48-pin SSOP package sequentially by pin number.

| Pin No | Symbol | Function      | Signal Direction |

|--------|--------|---------------|------------------|

| 1      | P40    | Port 4, bit 0 | Input/Output     |

| 2      | P25    | Port 2, bit 5 | Input/Output     |

| 3      | P26    | Port 2, bit 6 | Input/Output     |

| 4      | P27    | Port 2, bit 7 | Input/Output     |

| 5      | P04    | Port 0, bit 4 | Input/Output     |

| 6      | P41    | Port 4, bit 1 | Input/Output     |

| 7      | P05    | Port 0, bit 5 | Input/Output     |

Table 9. 48-Pin SSOP Sequential Pin Identification

| Pin No | Symbol               | Function                   | Signal Direction |  |

|--------|----------------------|----------------------------|------------------|--|

| 8      | P06 Port 0, bit 6 In |                            | Input/Output     |  |

| 9      | P14                  | Port 1, bit 4              | Input/Output     |  |

| 10     | P15                  | Port 1, bit 5              | Input/Output     |  |

| 11     | P07                  | Port 0, bit 7              | Input/Output     |  |

| 12     | V <sub>DD</sub>      | Power Supply               | Input            |  |

| 13     | V <sub>DD</sub>      | Power Supply               | Input            |  |

| 14     | P42                  | Port 4, bit 2              | Input/Output     |  |

| 15     | P16                  | Port 1, bit 6              | Input/Output     |  |

| 16     | P17                  | Port 1, bit 7              | Input/Output     |  |

| 17     | XTAL2                | Crystal oscillator         | Output           |  |

| 18     | XTAL1                | Crystal oscillator         | Input            |  |

| 19     | P31                  | Port 3, bit 1              | Input            |  |

| 20     | P32                  | Port 3, bit 2              | Input            |  |

| 21     | P33                  | Port 3, bit 3              | Input            |  |

| 22     | P34                  | Port 3, bit 4              | Input/Output     |  |

| 23     | P43                  | Port 4, bit 3              | Input/Output     |  |

| 24     | V <sub>SS</sub>      | Ground                     | Input            |  |

| 25     | /RESET               | Bidirectional reset signal | Input/Output     |  |

| 26     | P35                  | Port 3, bit 5              | Output           |  |

| 27     | P37                  | Port 3, bit 7              | Output           |  |

| 28     | P36                  | Port 3, bit 6              | Output           |  |

| 29     | P30/PREF1            | Port 3, bit 0              | Input            |  |

| 30     | P44                  | Port 4, bit 4              | Input/Output     |  |

| 31     | P00                  | Port 0, bit 0              | Input/Output     |  |

| 32     | P01                  | Port 0, bit 1              | Input/Output     |  |

| 33     | P10                  | Port 1, bit 0              | Input/Output     |  |

| 34     | P11                  | Port 1, bit 1              | Input/Output     |  |

| 35     | P02                  | Port 0, bit 2              | Input/Output     |  |

| 36     | P45                  | Port 4, bit 5              | Input/Output     |  |

| 37     | V <sub>SS</sub>      | Ground                     | Input            |  |

| 38     | V <sub>SS</sub>      | Ground                     | Input            |  |

| 39     | P12                  | Port 1, bit 2              | Input/Output     |  |

| 40     | P13                  | Port 1, bit 3              | Input/Output     |  |

#### Table 9. 48-Pin SSOP Sequential Pin Identification (Continued)

PS026407-0408

Pin Description

15

| Pin No | Symbol | Function      | Signal Direction |

|--------|--------|---------------|------------------|

| 41     | P03    | Port 0, bit 3 | Input/Output     |

| 42     | P20    | Port 2, bit 0 | Input/Output     |

| 43     | P21    | Port 2, bit 1 | Input/Output     |

| 44     | P22    | Port 2, bit 2 | Input/Output     |

| 45     | P23    | Port 2, bit 3 | Input/Output     |

| 46     | P24    | Port 2, bit 4 | Input/Output     |

| 47     | P46    | Port 4, bit 6 | Input/Output     |

| 48     | P47    | Port 4, bit 7 | Input/Output     |

#### Table 9. 48-Pin SSOP Sequential Pin Identification (Continued)

Table 10 lists the functions and signal directions of each pin within the 48-pin SSOP package by function.

| Pin No | Symbol | Function      | Signal Direction |  |

|--------|--------|---------------|------------------|--|

| 31     | P00    | Port 0, bit 0 | Input/Output     |  |

| 32     | P01    | Port 0, bit 1 | Input/Output     |  |

| 35     | P02    | Port 0, bit 2 | Input/Output     |  |

| 41     | P03    | Port 0, bit 3 | Input/Output     |  |

| 5      | P04    | Port 0, bit 4 | Input/Output     |  |

| 7      | P05    | Port 0, bit 5 | Input/Output     |  |

| 8      | P06    | Port 0, bit 6 | Input/Output     |  |

| 11     | P07    | Port 0, bit 7 | Input/Output     |  |

| 33     | P10    | Port 1, bit 0 | Input/Output     |  |

| 34     | P11    | Port 1, bit 1 | Input/Output     |  |

| 39     | P12    | Port 1, bit 2 | Input/Output     |  |

| 40     | P13    | Port 1, bit 3 | Input/Output     |  |

| 9      | P14    | Port 1, bit 4 | Input/Output     |  |

| 10     | P15    | Port 1, bit 5 | Input/Output     |  |

| 15     | P16    | Port 1, bit 6 | Input/Output     |  |

| 16     | P17    | Port 1, bit 7 | Input/Output     |  |

| 42     | P20    | Port 2, bit 0 | Input/Output     |  |

| 43     | P21    | Port 2, bit 1 | Input/Output     |  |

| 44     | P22    | Port 2, bit 2 | Input/Output     |  |

#### Table 10. 48-Pin SSOP Functional Pin Identification

| Pin No | Symbol          | Function                                  | Signal Direction |

|--------|-----------------|-------------------------------------------|------------------|

| 45     | P23             | Port 2, bit 3                             | Input/Output     |

| 46     | P24             | Port 2, bit 4                             | Input/Output     |

| 2      | P25             | Port 2, bit 5                             | Input/Output     |

| 3      | P26             | Port 2, bit 6                             | Input/Output     |

| 4      | P27             | Port 2, bit 7                             | Input/Output     |

| 29     | P30             | Port 3, bit 0; connect to VDD if not used | Input            |

| 19     | P31             | Port 3, bit 1                             | Input            |

| 20     | P32             | Port 3, bit 2                             | Input            |

| 21     | P33             | Port 3, bit 3                             | Input            |

| 22     | P34             | Port 3, bit 4                             | Input/Output     |

| 26     | P35             | Port 3, bit 5                             | Output           |

| 28     | P36             | Port 3, bit 6                             | Output           |

| 27     | P37             | Port 3, bit 7                             | Output           |

| 1      | P40             | Port 4, bit 0                             | Input/Output     |

| 6      | P41             | Port 4, bit 1                             | Input/Output     |

| 14     | P42             | Port 4, bit 2                             | Input/Output     |

| 23     | P43             | Port 4, bit 3                             | Input/Output     |

| 30     | P44             | Port 4, bit 4                             | Input/Output     |

| 36     | P45             | Port 4, bit 5                             | Input/Output     |

| 47     | P46             | Port 4, bit 6                             | Input/Output     |

| 48     | P47             | Port 4, bit 7                             | Input/Output     |

| 12     | V <sub>DD</sub> | Power Supply                              | Input            |

| 13     | V <sub>DD</sub> | Power Supply                              | Input            |

| 24     | V <sub>SS</sub> | Ground                                    | Input            |

| 37     | V <sub>SS</sub> | Ground                                    | Input            |

| 38     | V <sub>SS</sub> | Ground                                    | Input            |

| 18     | XTAL1           | Crystal oscillator                        | Input            |

| 17     | XTAL2           | Crystal oscillator                        | Output           |

| 25     | /RESET          | Bidirectional reset signal                | Input/Output     |

#### Table 10. 48-Pin SSOP Functional Pin Identification (Continued)

## **I/O Port Pin Functions**

The ZLF645 MCU features up to five 8-bit ports which are described below:

- 1. Port 0 is nibble-programmable as either input or output.

- 2. Port 1 is byte-programmable as either input or output.

- 3. Port 2 is bit-programmable as either input or output.

- 4. Port 3 features four inputs on the lower nibble and four outputs on the upper nibble.

- 5. Port 4 is bit-programmable as either input or output.

**Note:** *Port 0, Port 1, Port 2, and Port 4 internal pull-ups are disabled on any pin or group of pins when programmed into output mode.*

**Caution:** The CMOS input buffer for each Port 0, Port 1, Port 2, or Port 4 pin are always connected to the pin, even when the pin is configured as an output. If the pin is configured as an open-drain output and no external signal is applied, a High output state can cause the CMOS input buffer to float. This may lead to excessive leakage current of more than 100 μA. To prevent this leakage, connect the pin to an external signal with a defined logic level or ensure that its output state is Low, especially during STOP mode.

Port 0, Port 1, Port 2, and Port 4 have both input and output capability. The input logic is always present no matter whether the port is configured as input or output. When executing a READ instruction, the MCU reads the actual value at the input logic but not from the

output buffer. In addition, the instructions of OR, AND, and XOR have the Read-Modify-Write sequence. The MCU first reads the port, then modifies the value, and loads back to the port.

Precaution must be taken, if the port is configured as an open-drain output or if the port is driving any circuit that makes the voltage different from the appropriate output logic. If it is configured as open-drain output with output logic as ONE, it is a floating port and reads back as ZERO. The following instruction sets P00–P07 all Low:

AND P0,#%F0

#### **RESET (Input, Active Low)**

Reset initializes the MCU and is accomplished either through Power-On Reset (POR), Watchdog Timer (WDT), Stop Mode Recovery, Low-Voltage detection, or through the external reset pin in the case of 48-pin packaged products.

During POR and WDT Reset, the internally generated reset drives the reset pin Low for the POR time. Any device driving the external reset line must be open-drain to avoid damage from a possible conflict during reset conditions. A pull-up is provided internally for the reset pin, if available. When the ZLF645 MCU asserts (Low) the RESET pin, the internal pull-up is disabled. The ZLF645 MCU does not assert the RESET pin when the VDD voltage is below the VBO trip point level (for more details, see Reset and Power Management on page 132).

**Note:** *The external reset does not initiate an exit from STOP mode.*

Table 11 lists the registers used to control I/O ports. Some port pin functions can also be affected by control registers for other peripheral functions.

| Α      | ddress (He | ex)   |                             |          |            |         |

|--------|------------|-------|-----------------------------|----------|------------|---------|

| 12-Bit | Bank       | 8-Bit | Register Description        | Mnemonic | Reset      | Page No |

| 000    | 0–3        | 00    | Port 0 Register             | P0       | XXh        | 32      |

| 001    | 0–3        | 01    | Port 1 Register             | P1       | XXh        | 33      |

| 002    | 0–3        | 02    | Port 2 Register             | P2       | XXh        | 35      |

| 003    | 0–3        | 03    | Port 3 Register             | P3       | 0Xh        | 37      |

| F08    | 0–3        | 08    | Port 4 Register             | P4       | XXh        | 40      |

| F09    | F          | 09    | Port 4 Mode Register        | P4M      | FFh        | 39      |

| 0F6    | All        | F6    | Port 2 Mode Register        | P2M      | FFh        | 34      |

| 0F7    | All        | F7    | Port 3 Mode Register        | P3M      | XXXX_X000b | 36      |

| 0F8    | All        | F8    | Port 0/1 Mode Register      | P01M     | X1XX_XXX1b | 31      |

| F00    | F          | 00    | Port Configuration Register | PCON     | XXXX_1110b | 30      |

|        | Г          | 00    | For Configuration Register  | FCON     |            |         |

#### Table 11. I/O Port Control Registers

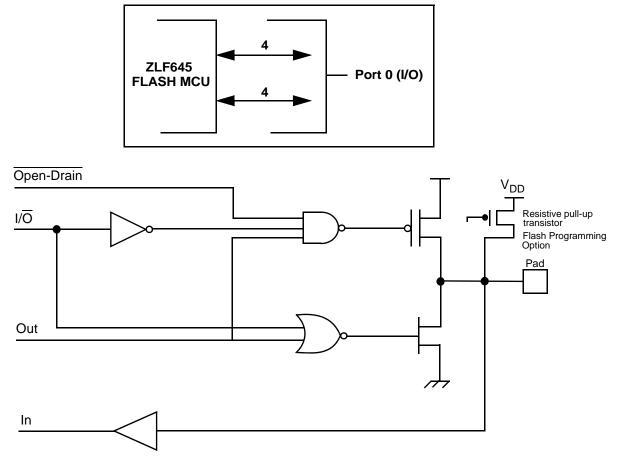

#### Port 0

Port 0 is an 8-bit bidirectional CMOS-compatible port. Its eight I/O lines are configured under software control to create a nibble I/O port. The output drivers are push/pull or open-drain, controlled by bit 2 of the Port Configuration Register.

If one or both nibbles are required for I/O operation, they must be configured by writing to the Port 0/1 Mode Register. After a hardware reset or a Stop Mode Recovery, Port 0 is configured as an input port.

Port 0, bit 7 is used as the transmit output of the UART when UART Tx is enabled. The I/O function of Port 0, bit 7 is overridden by the UART serial output (TxD) when UART Tx is enabled (UCTL[7] = 1). The pin must be configured as an output for TxD data to reach the pin (P01M[6] = 0).

An optional pull-up transistor is available as an user-selectable flash programming option on all Port 0 bits with nibble select. Figure 6 displays the Port 0 configuration.

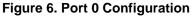

#### Port 1

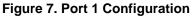

Port 1 is an 8-bit bidirectional CMOS-compatible I/O port. It can be configured under software control as inputs or outputs. A flash programming option bit is available to connect eight pull-up transistors on this port. Bits programmed as output are globally programmed as either push/pull or open-drain. The power-on reset function resets with the eight bits of Port 1 [P17:10] configured as inputs. Figure 7 displays the Port 1 configuration.

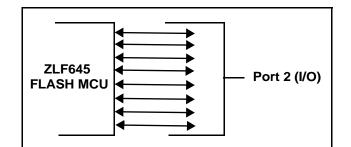

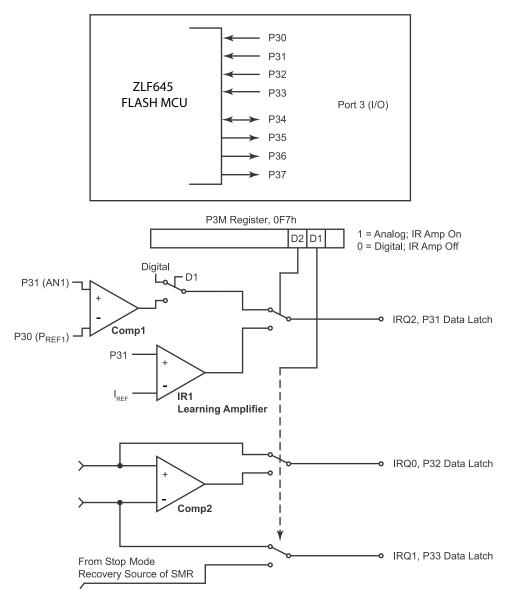

#### Port 2

Port 2 is an 8-bit bidirectional CMOS-compatible I/O port. Its eight I/O lines can be independently configured under software control as inputs or outputs. Port 2 is always available for I/O operation. A flash programming option bit is available to connect eight pull-up transistors on this port. Bits programmed as outputs are globally programmed as either push/pull or open-drain. The Power-On Reset function resets with the eight bits of Port 2 [P27:20] configured as inputs.

Port 2 also has an 8-bit input OR and AND gate and edge detection circuitry, which can be used to recover from the STOP mode. P20 can be programmed to access the edge-detection circuitry in DEMODULATION mode. Figure 8 displays the Port 2 configuration.

Figure 8. Port 2 Configuration

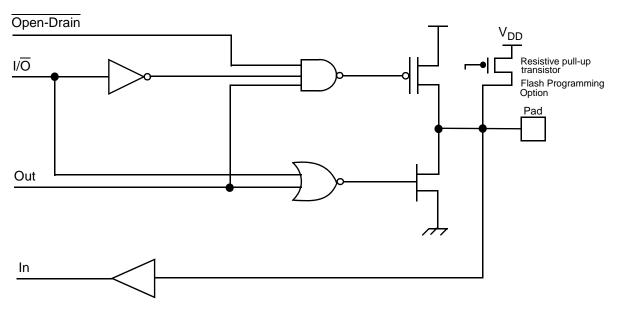

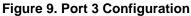

#### Port 3

Port 3 is an 8-bit CMOS-compatible I/O port. Port 3 consists of four fixed inputs (P33:P30), three fixed outputs (P37:P36:P35), and one multi-functioned pin (P34) that can function as an output only or as a bidirectional open-drain I/O depending on whether the ZLF645 MCU is in ICP mode.

P30, P31, P32, and P33 are standard CMOS inputs with option enabled pull-up transistors and can be configured under software as interrupts, as received data input to the UART block, as input to comparator circuits, or as input to the IR learning amplifier.

P37, P36, and P35 are push/pull outputs and can be configured as outputs from counter/timers and/or comparator circuits.

During the ZLF645's POR time, P34 is configured as an input pin with pull-up enabled. If after completing it's POR period, the ZLF645 has not detected this pin LOW and been put into ICP mode, this pin will revert back to being a push/pull output only. For more details on the function of pin P34, see ICP Interface on page 53.

24

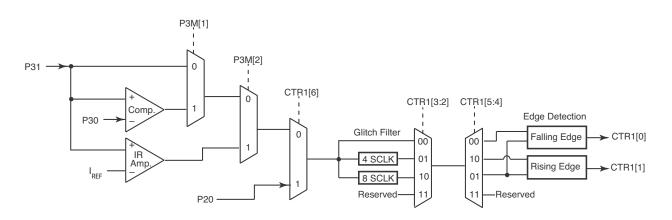

Figure 9 displays the Port 3 configuration.

P31 can be used as an interrupt, analog comparator input, infrared learning amplifier input, normal digital input pin, and as a Stop Mode Recovery source. When bit 2 of the Port 3 Mode register (P3M) is set, P31 is used as the infrared learning amplifier, IR1. The reference source for IR1 is GND. The infrared learning amplifier is disabled during STOP mode. When bit 1 of P3M is set, the part is in ANALOG mode and the analog comparator,

zilog

COMP1 is used. The reference voltage for COMP1 is P30 ( $P_{REF1}$ ). When in ANALOG mode, P30 cannot be read as a digital input when the CPU reads bit 0 of the Port 3 register; such reads always return a value of 1.

Also, when in ANALOG mode, P31 cannot be used as a Stop Mode Recovery source, as in STOP mode the comparator is disabled and its output will not toggle. The programming of bit 2 of the P3M register takes precedence over the programming of Bit 1 in determining the function of P31. If both bits are set, P31 functions as an IR learning amplifier instead of an analog comparator. As displayed in Figure 9 the output of the function selected for P31 can be used as a source for IRQ2 interrupt assertion. The IRQ2 interrupt can be configured based upon detecting a rising, falling, or edge-triggered input change using Bits 6 and 7 of the IRQ register. The P31 output stage signal also goes to the Counter/Timer edge detection circuitry in the same way that P20 does.

P32 can be used as an interrupt, analog comparator, UART receiver, normal digital input and as Stop Mode Recovery source. When bit 6 of UCTL register is set, P32 functions as a receive input for the UART. When bit 1 of the P3M register is set, thereby placing Port 3 into ANALOG mode, P32 functions as an analog comparator, COMP2. The reference voltage for COMP2 is P33 ( $P_{REF2}$ ). P32 can be used as a rising, falling or edge-triggered interrupt, IRQ0, using IRQ register bits 6 and 7. If UART receiver interrupts are not enabled, the UART receive interrupt is used as the source of interrupts for IRQ0 instead of P32. When in ANALOG mode P32 cannot be used as SMR source because the comparators are turned OFF in STOP mode.

When in ANALOG mode, P33 cannot be read by the CPU as a digital input through bit 3 of the Port 3 register. In this case, a read of bit 3 of the Port 3 register indicates whether Stop Mode Recovery condition exists. Reading a value of 0 indicates an SMR condition; if the ZLF645 MCU is in STOP mode, it will exit STOP mode. Reading a value of 1 indicates that no condition exists to exit the ZLF645 MCU from STOP mode.

Additionally, when in ANALOG mode, P33 cannot be used as an interrupt source. Instead, the existence of a SMR condition can generate an interrupt, if enabled. P33 can be used as a falling-edge interrupt, IRQ1, when not in ANALOG mode. IRQ1 is also used as the UART  $T_X$  interrupt and the UART BRG interrupt. Only one source is active at a time. If bit 7 and bit 5 of UCTL are set to 1, IRQ1 will transmit an interrupt when the Transmit Shift register is empty. If bits 0 and 5 of UCTL are set to 1 and bit 6 of UCTL is cleared to 0, the BRG interrupts will activate IRQ1.

#### **Note:** *Comparators and the IR amplifier are powered down by entering STOP mode.*

For P30:P33 to be used as a Stop Mode Recovery source during STOP mode, these inputs must be placed into DIGITAL mode. When in ANALOG mode, do not configure any Port 3 input as a SMR source. The configuration of these inputs must be re-initialized after Stop Mode Recovery or POR.

26

| Pin | I/O    | In-Circuit<br>Programmer | Counter/Timers | Comparator | Interrupt | IRAMP | UART    |

|-----|--------|--------------------------|----------------|------------|-----------|-------|---------|

| P30 | IN     | -                        |                | REF1       | -         |       |         |

| P31 | IN     |                          | IN             | AN1        | IRQ2      | IR1   |         |

| P32 | IN     |                          |                | AN2        | IRQ0      |       | UART Rx |

| P33 | IN     |                          |                | REF2       | IRQ1      |       |         |

| P34 | IN/OUT | ICP                      | Т8             | AO1        |           | IROUT |         |

| P35 | OUT    |                          | T16            |            |           |       |         |

| P36 | OUT    |                          | T8/T16         |            |           |       |         |

| P37 | OUT    |                          |                | AO2        |           |       |         |

#### Table 12. Summary of Port 3 Pin Functions

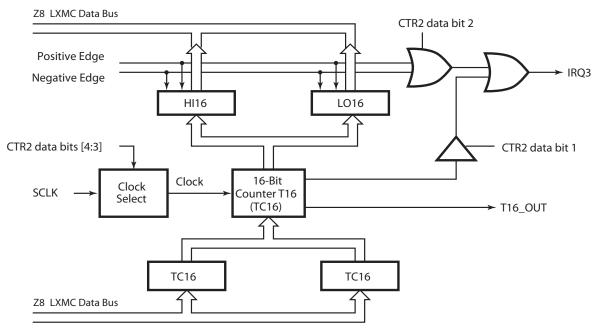

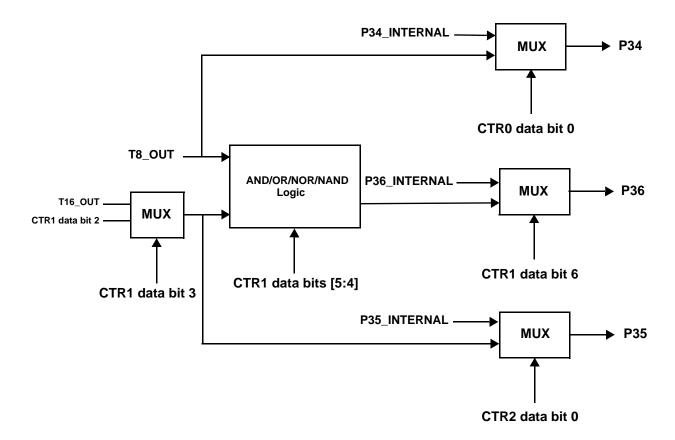

Port 3 also provides output for each of the counter/timers and AND/OR Logic (see Figure 10). Control is performed by programming CTR1 bit 5 and bit 4, CTR0 bit 0, and CTR2 bit 0.

Figure 10. Port 3 Counter/Timer Output Configuration

#### **Comparator Inputs**

In ANALOG mode, P31 and P32 have a comparator front end. The comparator reference is supplied by P33 and  $P_{REF1}$ . In ANALOG mode, the P33 internal data latch and its corresponding IRQ1 are diverted to the Stop Mode Recovery sources (excluding P31, P32, and P33) as displayed in Figure 9 on page 24. In DIGITAL mode, P33 is used as bit 3 of the Port 3 input register, which then generates IRQ1.

**Note:** *Comparators are powered down by entering STOP mode. For P30:P33 to be used as an SMR source, these inputs must be placed into DIGITAL mode.*

#### **Comparator Outputs**

The comparators can be programmed to output on P34 and P37 by setting bit 0 of the PCON register.

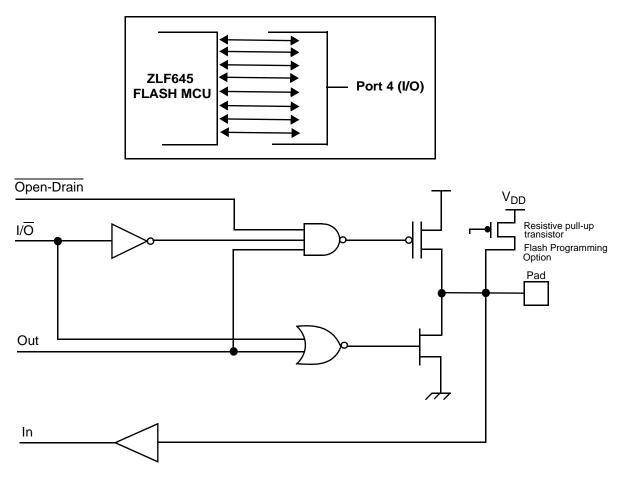

#### Port 4

Port 4 is an 8-bit bidirectional CMOS-compatible I/O port. Its eight I/O lines can be independently configured under software control as inputs or outputs. Port 4 is always available for I/O operation. A flash programming option bit is available to connect eight pull-up transistors on this port. Bits programmed as outputs are globally programmed as either push/pull or open-drain. The POR function resets with the eight bits of Port 4 [P47:40] configured as inputs. Figure 11 on page 29 displays the Port 4 configuration.

# **Port Configuration Register**

The Port Configuration register (see Table 13) configures the Port 0 output mode and the comparator output on Port 3. The PCON register is located in expanded register Bank F, address 00h.

#### Table 13. Port Configuration Register (PCON)

| Bit     | 7 | 6                         | 5 | 4 | 3 | 2 | 1                     | 0                            |  |  |

|---------|---|---------------------------|---|---|---|---|-----------------------|------------------------------|--|--|

| Field   |   | Reserved                  |   |   |   |   | Port 1<br>Output Mode | Comp/IR Amp<br>Output Port 3 |  |  |

| Reset   | Х | Х                         | Х | Х | 1 | 1 | 1                     | 0                            |  |  |

| R/W     | _ |                           |   |   | W | W | W                     | W                            |  |  |

| Address |   | Bank F: 00h; Linear: F00h |   |   |   |   |                       |                              |  |  |

| Bit Position | Value | Description                                                             |

|--------------|-------|-------------------------------------------------------------------------|

| [7:4]        |       | Reserved—Must be written to 1; reads 11111b.                            |

| [3]          |       | Port 4 Output Mode—Controls the output mode of Port 4.                  |

|              | 0     | Open-drain                                                              |

|              | 1     | Push/pull                                                               |

| [2]          |       | Port 0 Output Mode—Controls the output mode of Port 0.                  |

|              |       | Write only; read returns 1.                                             |

|              | 0     | Open-drain                                                              |

|              | 1     | Push/pull                                                               |

| [1]          |       | Port 1 Output Mode—Controls the output mode of Port 1.                  |

|              |       | Write only; read returns 1                                              |

|              | 0     | Open-drain                                                              |

|              | 1     | Push/pull                                                               |

| [0]          |       | Comparator or IR Amplifier Output Port 3—Select digital outputs or      |

|              |       | comparator, and IR amplifier outputs on P34 and P37.                    |

|              |       | Write only; read returns 1.                                             |

|              | 0     | P34 and P37 outputs are digital.                                        |

|              | 1     | P34 is Comparator 1 or IR Amplifier output, P37 is Comparator 2 output. |

**Note:** *PCON register is not reset after a Stop Mode Recovery. Also, for package types other than the 48-pin package, writes to bit 3 and bit 1 have no effect.*

PS026407-0408

>

# Port 0/1 Mode Register

The Port 0/1 Mode register (see Table 14) determines the I/O direction of Port 0 and Port 1. The Port 0 direction is nibble-programmable. Bit 6 controls the upper nibble of Port 0, bits [7:4]. Bit 0 controls the lower nibble of Port 0, bits [3:0]. The Port 1 direction is byte programmable.

Table 14. Port 0/1 Mode Register (P01M)

| Bit     | 7        | 6                                   | 5    | 4    | 3           | 2    | 1     | 0            |  |  |

|---------|----------|-------------------------------------|------|------|-------------|------|-------|--------------|--|--|

| Field   | Reserved | P07:P04 Mode                        | Rese | rved | Port 1 Mode | Rese | erved | P03:P00 Mode |  |  |

| Reset   | Х        | 1                                   | Х    | Х    | 1           | Х    | Х     | 1            |  |  |

| R/W     | _        | W                                   | _    |      | W           |      | _     | W            |  |  |

| Address |          | Bank Independent: F8h; Linear: 0F8h |      |      |             |      |       |              |  |  |

| <b>Bit Position</b> | Value | Description                               |

|---------------------|-------|-------------------------------------------|

| [7]                 | 0     | Reserved—Must be written to 1. Reads 1b.  |

| [6]                 |       | P07:P04 Mode                              |

|                     | 0     | Output                                    |

|                     | 1     | Input                                     |

| [5:4]*              | _     | Reserved—Must be written to 1. Reads 1's. |

| [3] <sup>*</sup>    |       | Port 1 Mode                               |

|                     | 0     | Output                                    |

|                     | 1     | Input                                     |

| [0]                 |       | P00:P03 Mode                              |

|                     | 0     | Output                                    |

|                     | 1     | Input                                     |

<sup>\*</sup>For package types other than the 48-pin package, writes to bit 3 have no effect.

**Note:** Only P00, P01, and P07 are available for ZLF645 Flash MCU 20-pin configuration.

# Port 0 Register

The Port 0 register (see Table 15) allows read and write access to the Port 0 pins.

### Table 15. Port 0 Register (P0)

| Bit     | 7   | 6   | 5   | 4            | 3             | 2   | 1   | 0   |

|---------|-----|-----|-----|--------------|---------------|-----|-----|-----|

| Field   | P07 | P06 | P05 | P04          | P03           | P02 | P01 | P00 |

| Reset   | Х   | Х   | Х   | Х            | Х             | Х   | Х   | Х   |

| R/W     | R/W | R/W | R/W | R/W          | R/W           | R/W | R/W | R/W |

| Address |     |     | Ba  | ink 0–3: 00h | i; Linear: 00 | 0h  |     |     |

| <b>Bit Position</b> | R/W   | Description                                                                              |

|---------------------|-------|------------------------------------------------------------------------------------------|

| [7]                 |       | Port 0 Pin 7—Available for I/O if UART Tx is disabled.                                   |

|                     | Read  | Pin configured as input or output in P01M register.                                      |

|                     | 0     | Pin level is Low.                                                                        |

|                     | 1     | Pin level is High.                                                                       |

|                     | Write | Pin configured as output in P01M register, UCTL[7]=0.                                    |

|                     | 0     | Assert pin Low.                                                                          |

|                     | 1     | Assert pin High if configured as push-pull; make pin high-impedance if it is open-drain. |

| [6:0]               |       | Port 0 Pins 6–0—Each bit provides access to the corresponding Port 0 pin                 |

|                     | Read  | Pin configured as input or output in P01M register.                                      |

|                     | 0     | Pin level is Low.                                                                        |

|                     | 1     | Pin level is High.                                                                       |

|                     | Write | Pin configured as output in P01M register.                                               |

|                     | 0     | Assert pin Low.                                                                          |

|                     | 1     | Assert pin High if configured as push-pull; make pin high-impedance if it is open-drain. |

**Note:** *Only P00, P01, and P07 are available for ZLF645 Flash MCU 20-pin configuration.*

# Port 1 Register

The Port 1 register (see Table 16) allows read and write access to the Port 1 pins.

### Table 16. Port 1 Register (P1)

| Bit            | 7                           | 6              | 5             | 4              | 3               | 2             | 1             | 0        |

|----------------|-----------------------------|----------------|---------------|----------------|-----------------|---------------|---------------|----------|

| Field          | P17                         | P16            | P15           | P14            | P13             | P12           | P11           | P10      |

| Reset          | Х                           | Х              | Х             | Х              | Х               | Х             | Х             | Х        |

| R/W            | R/W                         | R/W            | R/W           | R/W            | R/W             | R/W           | R/W           | R/W      |

| Address        | Bank 0–3: 01h; Linear: 001h |                |               |                |                 |               |               |          |

| Note: For page | ckage types o               | other than the | e 48-pin pack | age, this regi | ster is availat | ole as a gene | ral-purpose r | egister. |

| Bit Position | Value | Description                                                                               |

|--------------|-------|-------------------------------------------------------------------------------------------|

| [7:0]        |       | Port 1 Pins 7–0—Each bit provides access to the corresponding Port 1 pin                  |

|              | Read  | Pin configured as input or output in P01M register.                                       |

|              | 0     | Pin level is Low.                                                                         |

|              | 1     | Pin level is High.                                                                        |

|              | Write | Pin configured as output in P01M register.                                                |

|              | 0     | Assert pin Low.                                                                           |

|              | 1     | Assert pin High, if configured as push-pull; make pin high-impedance if it is open-drain. |

Note: For packages other than 48-pin package, this register is available as general-purpose register.

# Port 2 Mode Register

The Port 2 Mode register (see Table 17) determines the I/O direction of each bit on Port 2. Bit 0 of the Port 3 Mode register determines whether the output drive is push/pull or open-drain.

Table 17. Port 2 Mode Register (P2M)

| Bit     | 7                     | 6                     | 5                     | 4                     | 3                     | 2                     | 1                     | 0                     |

|---------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| Field   | P27 I/O<br>Definition | P26 I/O<br>Definition | P25 I/O<br>Definition | P24 I/O<br>Definition | P23 I/O<br>Definition | P22 I/O<br>Definition | P21 I/O<br>Definition | P20 I/O<br>Definition |

| Reset   | 1                     | 1                     | 1                     | 1                     | 1                     | 1                     | 1                     | 1                     |

| R/W     | W                     | W                     | W                     | W                     | W                     | W                     | W                     | W                     |

| Address |                       |                       | Bank Ir               | ndependent            | F6h; Linea            | r: 0F6h               |                       |                       |

| Bit Position | Value | Description            |

|--------------|-------|------------------------|

| [7]          | 0     | Defines P27 as output. |

|              | 1     | Defines P27 as input.  |

| [6]          | 0     | Defines P26 as output. |

|              | 1     | Defines P26 as input.  |

| [5]          | 0     | Defines P25 as output. |

|              | 1     | Defines P25 as input.  |

| [4]          | 0     | Defines P24 as output. |

|              | 1     | Defines P24 as input.  |

| [3]          | 0     | Defines P23 as output. |

|              | 1     | Defines P23 as input.  |

| [2]          | 0     | Defines P22 as output. |

|              | 1     | Defines P22 as input.  |

| [1]          | 0     | Defines P21 as output. |

|              | 1     | Defines P21 as input.  |

| [0]          | 0     | Defines P20 as output. |

|              | 1     | Defines P20 as input.  |

**Note:** *Port 2 Mode register is not reset after a Stop Mode Recovery.*

# Port 2 Register

The Port 2 register (see Table 18) allows read and write access to the Port 2 pins.

### Table 18. Port 2 Register (P2)

| Bit     | 7   | 6   | 5   | 4            | 3             | 2   | 1   | 0   |

|---------|-----|-----|-----|--------------|---------------|-----|-----|-----|

| Field   | P27 | P26 | P25 | P24          | P23           | P22 | P21 | P20 |

| Reset   | Х   | Х   | Х   | Х            | Х             | Х   | Х   | Х   |

| R/W     | R/W | R/W | R/W | R/W          | R/W           | R/W | R/W | R/W |

| Address |     |     | Ba  | ink 0–3: 02h | i; Linear: 00 | 2h  |     |     |

| <b>Bit Position</b> | Value | Description                                                                              |

|---------------------|-------|------------------------------------------------------------------------------------------|

| [7:0]               |       | <b>Port 2 Pins 7–0</b> —Each bit provides access to the corresponding Port 2 pin.        |

|                     | Read  | Pin configured as input or output in P2M register.                                       |

|                     | 0     | Pin level is Low.                                                                        |

|                     | 1     | Pin level is High.                                                                       |

|                     | Write | Pin configured as output in P2M register.                                                |

|                     | 0     | Assert pin Low.                                                                          |

|                     | 1     | Assert pin High if configured as push-pull; make pin high-impedance if it is open-drain. |

# Port 3 Mode Register

The Port 3 Mode register (see Table 20) is used to configure the functionality of Port 3 inputs and the output mode of Port 2. When bit 2 is set, the IR Learning Amplifier is used instead of the COMP1 comparator, regardless of the value of bit 1.

| Bit          | 7     | 6                                   | 5        | 4                   | 3        | 2                                       | 1                  | 0                    |  |

|--------------|-------|-------------------------------------|----------|---------------------|----------|-----------------------------------------|--------------------|----------------------|--|

|              |       |                                     | Reserved | ł                   |          | IR Learning<br>Amplifier                | DIGITAL/<br>ANALOG | Port 2<br>Open-Drain |  |

| Field        |       |                                     |          |                     |          |                                         | Mode               |                      |  |

| Reset        | Х     | Х                                   | Х        | X                   | X        | 0                                       | 0                  | 0                    |  |

| R/W          | —     | —                                   | _        | _                   | _        | W                                       | W                  | W                    |  |

| Address      |       | Bank Independent: F7h; Linear: 0F7h |          |                     |          |                                         |                    |                      |  |

| Bit Position | n R/W | Va                                  | alue D   | escriptio           | on       |                                         |                    |                      |  |

| [7:3]        | _     |                                     | — R      | eserved-            | —Must be | e written to 1. Re                      | ads return 1111    | 1b.                  |  |

| [2]          | W     |                                     |          |                     |          | er disabled.                            |                    |                      |  |

|              |       |                                     |          | R Learning          |          | er enabled with F                       | '31 configured a   | IS                   |  |

| [1]          | W     |                                     |          | IGITAL/A            |          |                                         |                    |                      |  |

|              |       |                                     |          |                     |          | are digital input                       |                    | 0.004.444            |  |

|              |       |                                     |          |                     |          | are comparator i<br>trator input. If P3 |                    |                      |  |

|              |       |                                     |          | inction as<br>iput. | a compa  | iator input. Il Fo                      | ivi[∠]=1, F31 IS1  |                      |  |

| [0]          | W     | W 0 Port 2 open-drain.              |          |                     |          |                                         |                    |                      |  |

|              |       |                                     | 1 P      | ort 2 pusl          | h/pull.  |                                         |                    |                      |  |

#### Table 20. Port 3 Mode Register (P3M)

**Note:** *Port 3 Mode register is not reset after a Stop Mode Recovery.*

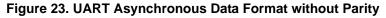

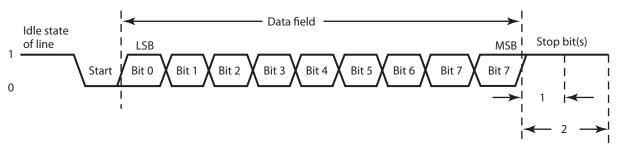

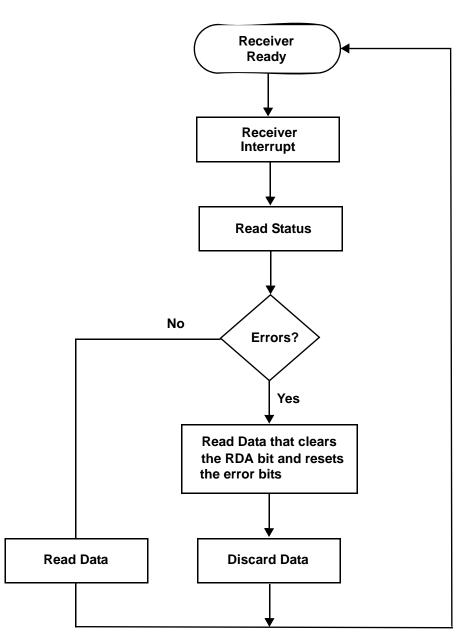

# Port 3 Register