# Datasheet

Single Chip CMOS Imager with Integrated Image Signal Processor and JPEG Codec

Version 1.8

21 November 2005

Products and specifications discussed herein are for evaluation and reference purposes only and are subject to change by TransChip without notice. The information in this document is not a warranty, does not form part of any quotation or contract and does not convey a license under intellectual property rights.

Copyright © TransChip Israel Research Center, Ltd., 2005.

## **Table of Contents**

| 1. IN | VTRODUCTION                          | 1    |

|-------|--------------------------------------|------|

| 1.1   | Features                             | 1    |

| 1.2   | SPECIFICATIONS                       | 3    |

| 1.3   | COMPACT 24-PIN CAMERA MODULE         | 4    |

| 2. FI | UNCTIONAL DESCRIPTION                | 5    |

|       |                                      |      |

| 2.1   | CONT                                 |      |

| 2.2   | RCLK                                 |      |

| 2.3   | IMGA                                 |      |

| 2.4   | YUVR                                 |      |

| 2.5   | JPEG                                 |      |

| 2.6   | PVI AND SVI                          |      |

| 2.7   | IMAGER AND ADDRESS GENERATOR         |      |

| 2.8   | PIXEL ARRAY CONFIGURATION            |      |

| 2.9   | BAYER GRID CONFIGURATION             |      |

| 2.10  | RESOLUTIONS AND FRAME RATES          |      |

| 2.11  | ANALOG PROCESSING                    |      |

| 2.12  | ON-CHIP MICRO CONTROLLER             |      |

| 2.13  | BAYER TO YUV TRANSLATION UNIT (YUVR) |      |

| 2.14  | JPEG COMPRESSION UNIT (JCOR)         | 9    |

| 3. R  | ESET AND CLOCK                       | . 11 |

| 3.1   | Low Power Modes                      | 11   |

|       | 1.1 Startup                          |      |

|       | 1.1 Startup<br>1.2 Bypass            |      |

|       | 1.2 <i>Bypass</i>                    |      |

| 3.2   | PLL CONFIGURATIONS                   |      |

| 3.2   | Device Initialization Sequence       |      |

|       |                                      |      |

| 4. To | C5747MF24L INTERFACES                | 13   |

| 4.1   | I <sup>2</sup> C Serial Interface    | 13   |

| 4.    | 1.1 Overview                         | 13   |

| 4.    | 1.2 Mode of Operation                | 14   |

| 4.2   | PARALLEL VIDEO INTERFACE (PVI)       | 17   |

| 4.1   | 2.1 Parallel Mode of Operation       | 17   |

| 4.    | 2.2 External Chip-Select             |      |

|       | 2.3 Qualified Clock Mode             |      |

|       | 2.4 VALIDH Configured as WR#         |      |

|       | 2.5 Frame-Rate Control               |      |

|       | 2.6 Data                             |      |

|       | 2.7 Data Markers                     |      |

|       | 2.8 Ancillary Data Format            |      |

|       | 2.9 Serial Output Mode               |      |

|       | SERIAL VIDEO INTERFACE               |      |

| 5. 1        | HIGH LEVEL API PROGRAMMING                                       |    |

|-------------|------------------------------------------------------------------|----|

| 5.1         | FIRMWARE LOADING                                                 |    |

| 6.          | AC/DC SPECIFICATIONS                                             | 30 |

| 6.1         | ABSOLUTE MAXIMUM RATINGS                                         |    |

| 6.2         | RECOMMENDED OPERATING CONDITIONS                                 |    |

| 6.3         | B DC ELECTRICAL CHARACTERISTICS                                  |    |

| 6.4         | PARALLEL VIDEO OUTPUT CLOCK QUALIFIED MODE AC CHARACTERISTICS    |    |

| 6.5         | 5 PARALLEL VIDEO OUTPUT CAMERA INTERFACE MODE AC CHARACTERISTICS |    |

| 6.6         | PARALLEL VIDEO OUTPUT INTERFACE AC CHARACTERISTICS               |    |

| 6.7         | SERIAL VIDEO OUTPUT INTERFACE AC CHARACTERISTICS                 |    |

| 6.8         | ······                                                           |    |

| 6.9         |                                                                  |    |

| 6.1         | 0 I <sup>2</sup> C-Compatible Interface AC Characteristics       |    |

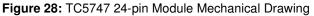

| <b>7.</b> 1 | MECHANICAL AND ELECTRICAL DRAWINGS                               |    |

| 7.1         | TC5747MF24L 24-PIN PACKAGE                                       |    |

| 7.2         | LENS SPECIFICATION                                               |    |

# List of Figures

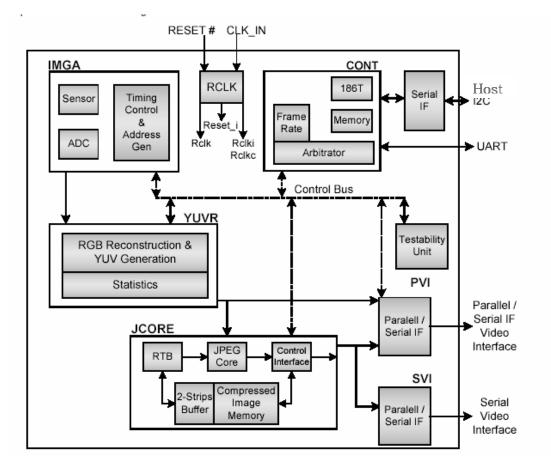

| FIGURE 1: TC5747 FUNCTIONAL BLOCK DIAGRAM                      | 5  |

|----------------------------------------------------------------|----|

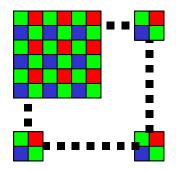

| FIGURE 2: BAYER GRID CONFIGURATION                             | 7  |

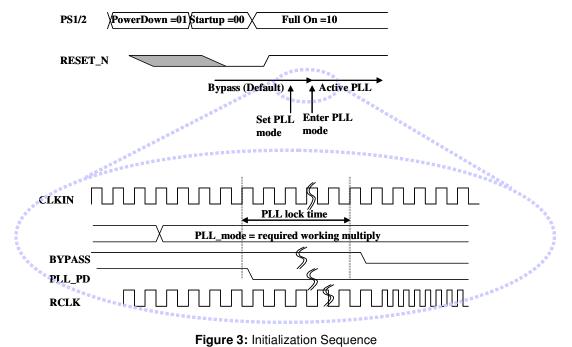

| FIGURE 3: INITIALIZATION SEQUENCE                              | 12 |

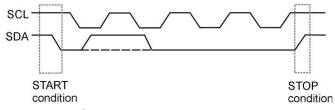

| FIGURE 4: I <sup>2</sup> C INTERFACE START AND STOP CONDITIONS | 14 |

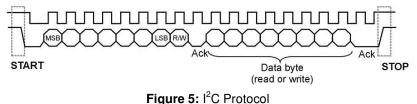

| FIGURE 5: I <sup>2</sup> C Protocol                            | 14 |

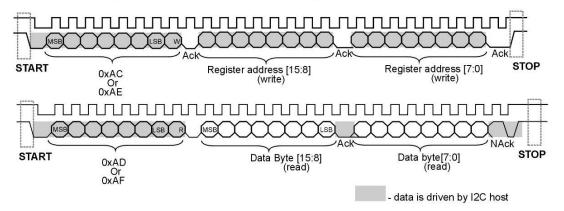

| FIGURE 6: I <sup>2</sup> C Host-Write Access                   | 15 |

| FIGURE 7: I <sup>2</sup> C Host-Read Access                    | 15 |

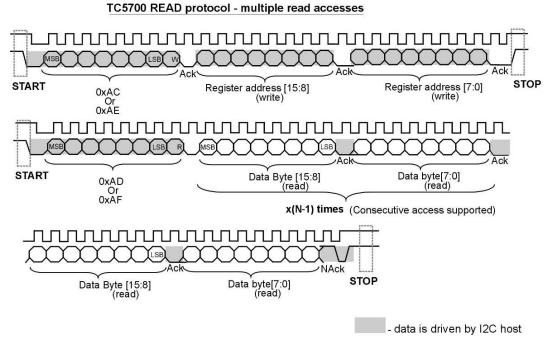

| FIGURE 8: I <sup>2</sup> C Host-Read Multiple (N) Accesses     | 16 |

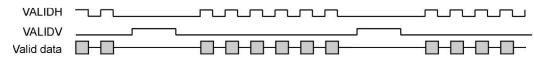

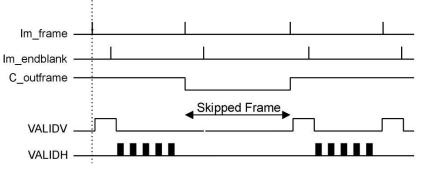

| FIGURE 9: PVI QUALIFICATION SIGNAL TIMING                      | 17 |

| FIGURE 10: VERTICAL AND HORIZONTAL QUALIFY SIGNALS             | 17 |

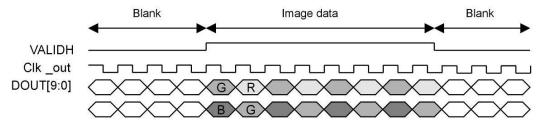

| FIGURE 11: PVI BAYER OUTPUT FORMAT                             | 18 |

| FIGURE 12: PVI YUV OUTPUT FORMAT                               | 19 |

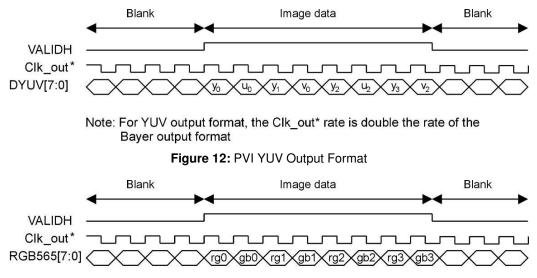

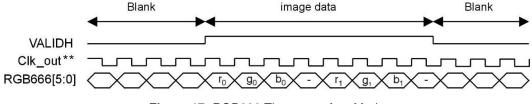

| FIGURE 13: RGB 565 OUTPUT ON PARALLEL VIDEO OUTPUT INTERFACE   | 19 |

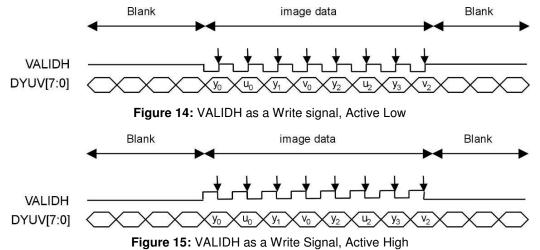

| FIGURE 14: VALIDH AS A WRITE SIGNAL, ACTIVE LOW                | 20 |

| FIGURE 15: VALIDH AS A WRITE SIGNAL, ACTIVE HIGH               | 20 |

| FIGURE 16: FRAME RATE CONTROL                                  | 20 |

| FIGURE 17: RGB666 THREE-TRANSFERS MODE                         | 22 |

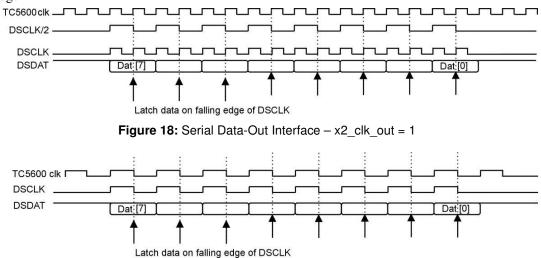

| FIGURE 18: SERIAL DATA-OUT INTERFACE – X2_CLK_OUT = 1          | 26 |

| FIGURE 19: SERIAL DATA-OUT INTERFACE – X2_CLK_OUT = 0          | 26 |

| FIGURE 20: SINGLE BYTE TRANSFER MODE                           | 27 |

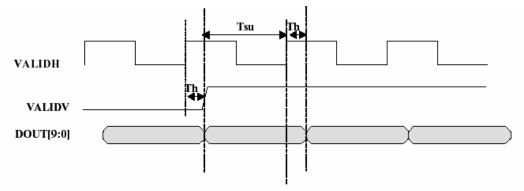

| FIGURE 21: PARALLEL VIDEO OUTPUT CLOCK QUALIFIED MODE          | 31 |

| FIGURE 22: PARALLEL VIDEO OUTPUT CAMERA INTERFACE MODE         | 31 |

| FIGURE 23: PARALLEL VIDEO OUTPUT INTERFACE SIGNALS             | 32 |

| FIGURE 24: SERIAL VIDEO OUTPUT INTERFACE SIGNALS               | 32 |

| FIGURE 25: SERIAL VIDEO OUTPUT CLOCK QUALIFIED MODE AC         | 33 |

| FIGURE 26: SERIAL VIDEO OUTPUT SSI MODE                        | 33 |

| FIGURE 27: I <sup>2</sup> C-COMPATIBLE INTERFACE               | 34 |

| FIGURE 28: TC5747 24-PIN MODULE MECHANICAL DRAWING             | 36 |

| FIGURE 29: TC5747 24-PIN MODULE MECHANICAL DRAWING CONTINUED   | 37 |

# List of Tables

| TABLE 1: TC5747 Specifications                                           |    |

|--------------------------------------------------------------------------|----|

| TABLE 2: 24-PIN MODULE PIN LIST                                          | 4  |

| TABLE 3: ANALOG CLOCK RATE MODES                                         |    |

| TABLE 4: TRANSCHIP MARKERS                                               |    |

| TABLE 5: ITU 656 MARKERS.                                                |    |

| TABLE 6: ABSOLUTE MAXIMUM RATINGS                                        |    |

| TABLE 7: RECOMMENDED OPERATING CONDITIONS                                |    |

| TABLE 8: DC ELECTRICAL CHARACTERISTICS                                   |    |

| TABLE 9: PARALLEL VIDEO OUTPUT CLOCK QUALIFIED MODE AC CHARACTERISTICS   |    |

| TABLE 10: PARALLEL VIDEO OUTPUT CAMERA INTERFACE MODE AC CHARACTERISTICS |    |

| TABLE 11: PARALLEL VIDEO OUTPUT INTERFACE AC CHARACTERISTICS             |    |

| TABLE 12: SERIAL VIDEO OUTPUT CLOCK QUALIFIED MODE AC CHARACTERISTICS    | 33 |

| TABLE 13: SERIAL VIDEO OUTPUT SSI MODE AC CHARACTERISTICS                | 33 |

| TABLE 14: I <sup>2</sup> C-COMPATIBLE INTERFACE AC CHARACTERISTICS       |    |

| TABLE 15: LENS SPECIFICATIONS                                            |    |

|                                                                          |    |

## 1. Introduction

The TC5747 is a single chip VGA (640 lines over 480 pixels) color CMOS sensor with an integrated color processing and JPEG codec. It is designed to meet the requirements of cellular devices with low power consumption and miniature size. An embedded programmable core with dedicated hardware performs the extensive color processing. An embedded real-time JPEG encoder and compressed frames SRAM store JPEG images on chip. The TC5747 has flexible interfaces and supports multiple video output formats for easy integration into cellular phones. It supports a 16-bit host interface for fast data access and control.

### 1.1 Features

The TC5747 features a state-of-the-art architecture, allowing extremely low power consumption and miniature size. The following are the product highlights.

- Sensor Array

- 1/4" optical format

- VGA resolution 640x480

- 5µm x 5µm square pixels

- Integrated 10 Bit ADC

- RGB mosaic with micro-lens for high sensitivity

- Double sampling for fixed pattern noise reduction

- Separate gains for R, G and B

- Programmable frame rate up to 20 fps VGA and 40 fps QVGA

- Programmable window size and filtered-option sub-sampling

- Image processing

- Embedded Image Signal Processor (ISP)

- Embedded micro controller with program memory

- Faulty pixel mechanism

- Loadable gamma correction tables

- Automatic white balance

- Automatic exposure control

- Despeckle function

- Enhanced dynamic range for backlight illumination

- Programmable 3x3 color correction matrix

- Programmable 3x3 sharpening or blurring matrix

- Anti flicker for 50Hz and 60 Hz

- Horizontal and vertical inversion

- Digital zoom of 4X, 2X

- Color adjustments such as: brightness, contrast, saturation

- Digital effects, such as monochrome, negative, sepia

- Frame or stamp overlay on the captured image (up to 320x240)

- Down sampling by 2x, 3x, 4x, 5x, 6x, 7x, 8x

- JPEG Codec

- Real-time JPEG encoder and decoder for still images and M-JPEG for motion video

- Compression of up to VGA YUV 422 format images

- Decompression of up to VGA resolution, 4:2:2, 4:1:1, 4:2:0 format images

- Programmable compression ratio, up to 1.8 bits/pixel for VGA image

- JPEG compression is done in parallel with preview of the video on the LCD

- Thumbnail image support

- Portrait images for phone book

- Compression and decompression from the internal memory

- Compression can be done after scaling and overlay of frame and stamp data

- Decompressed image can be resized and re-compressed

- On screen display

- On screen display overlay of up to QVGA (320x240) resolution, 4-bit OSD data color table

- Support of up to two layers of OSD data. The first layer can be used to add frame of stamp to the captured image. The second layer can be composed of one or two non-overlapping regions of OSD for switching messages and icons. Each OSD window has its own 4-bit color table.

- Support of 32x32 pixel cursor with 4-bit color table

- Rotation of JPEG images display by  $90^{\circ}$  or  $270^{\circ}$

- Video Interface

- Flexible output formats including: Bayer, RGB (666, 565, 444), YUV/YCrCb 4:2:2 and JPEG

- 18 bits direct interface to LCD: supports 8/9/16/18 bit output

- Chip select for two LCD (main and sub)

- Camera standby mode for host access to the LCD

- Optional configuration of 8 bits camera interface

- Horizontal and vertical sync signals

- CCIR656 compatible signaling markers

- Optional high-speed bi-directional serial interface

- Support of two simultaneous video output streams

- Host Interface

- 8/16bit bi-directional I80 and M68 access types host interface

- Optional I<sup>2</sup>C or UART interface for programming and control

- Easy to use software API

- Input clock frequency: 3.6MHz to 32MHz

- Power consumption, VGA@ 15 FPS is 85 mW.

- Power management to support low power modes

- Operation voltage 2.8 +/- 10%

- Technology: 0.25 um s

- Operation temperature: -10 to 60 degrees Celsius

- Packaging types: module with lens. Module can have either flex cable or board-to-board connector. Several pin-out options will be supported to provide selected interface functionality.

## 1.2 Specifications

| Feature                | Description                                                                                                                                    |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Array format           | VGA - 656x524 physical pixel, 648x492 active pixels for 1/4" optics                                                                            |

| Capture size           | Configurable window size                                                                                                                       |

| Pixel size             | 5μ x 5μ                                                                                                                                        |

| Color filter           | RGB Mosaic with micro lens                                                                                                                     |

| Supply Voltage         | 2.8V ±10%, internal regulators for digital and analog supplies                                                                                 |

| Power consumption      | 85mW at 15 fps (including color processing)                                                                                                    |

| Power save modes       | Sleep mode with maximum of 100 $\mu A$ current and wake up of less than 100msec.                                                               |

|                        | Power down mode with up to 10µA current.                                                                                                       |

| Input clock frequency  | Internal PLL supports input clocks of 3.6MHz – 32MHz.                                                                                          |

| A/D converter          | 10 bit ADC                                                                                                                                     |

| Down sampling          | Down sampling with filter by 2X to 8X in both dimensions.                                                                                      |

| Video output format    | YCrCb422 / YUV422 / RGB444 / RGB565 / RGB666 / Raw / JPEG;                                                                                     |

| Video output interface | 8/9/10-bit parallel camera interface or 8/9/16/18 LCD controller data interface                                                                |

| Video synchronization  | Horizontal and vertical sync signals and/or CCIR656 header                                                                                     |

| Control interface      | <ul> <li>6-bit host bus interface</li> <li>I<sup>2</sup>C compatible interface</li> <li>UART</li> <li>Used also to read JPEG images</li> </ul> |

| Frame rate             | Variable up to 20 fps for VGA or 40 fps for QVGA                                                                                               |

| JPEG                   | HW JPEG encoder/decoder acceleration                                                                                                           |

| JPEG frames memory     | On-chip 64Kbyte SRAM to store compressed images                                                                                                |

| Program memory         | On-chip 48Kbyte SRAM to store firmware for the ISP                                                                                             |

| Readout control        | Progressive readout; vertical and horizontal inversion options                                                                                 |

| Exposure control       | From one line to one frame duration with 250ns granularity.                                                                                    |

| AGC                    | Separate gain for each of the three color components R,G and B                                                                                 |

| Dynamic range control  | Enhanced dynamic range                                                                                                                         |

| Image enhancement      | Black level, faulty pixel correction, color correction, auto white balance, auto exposure, anti-flicker, gamma correction, color suppression.  |

| Anti shading           | Lens shading correction                                                                                                                        |

| Zoom                   | Digital zoom by 2X, 4X.                                                                                                                        |

| Image controls         | Contrast, brightness, saturation, sharpening, windowing, lookup table                                                                          |

| Camera module          | Camera module package with lens, optional flex cable or board-to-<br>board connector                                                           |

| Sensitivity            | 4V/lux-sec (including gain)                                                                                                                    |

Table 1: TC5747 Specifications

### 1.3 Compact 24-pin Camera Module

| Pin Name           | #  | I/O | Description                                                                                   |  |  |

|--------------------|----|-----|-----------------------------------------------------------------------------------------------|--|--|

| SCLK               | 1  | Ι   | I <sup>2</sup> C-compatible input clock signal generated by the I <sup>2</sup> C master.      |  |  |

| AGND               | 2  | Ι   | Analog circuits ground.                                                                       |  |  |

| AVDD28             | 3  | I   | 2.8V supply for analog circuits.                                                              |  |  |

| RESET#             | 4  | I   | Asynchronous reset input signal; active low                                                   |  |  |

| CLK_IN             | 5  | Ι   | 16-32 MHz clock input or crystal input                                                        |  |  |

| DGND               | 6  | I   | Digital circuits ground.                                                                      |  |  |

| DOUT[1]/CSDAT# (*) | 7  | I/O | 9 <sup>th</sup> bit data /External Chip Select for data bus; active low                       |  |  |

| DYUV[0]            | 8  |     | Output video data                                                                             |  |  |

| DYUV[1]            | 9  | I/O | Output video data                                                                             |  |  |

| DYUV[2]            | 10 | I/O | Output video data                                                                             |  |  |

| DYUV[3]            | 11 | I/O | Output video data                                                                             |  |  |

| DYUV[4]            | 12 | I/O | Output video data                                                                             |  |  |

| DYUV[5]            | 13 |     | Output video data / i2c_toggle - Selects between two I <sup>2</sup> C addresses during RESET# |  |  |

| DYUV[6]            | 14 | I/O | Output video data                                                                             |  |  |

| DYUV[7] /          | 15 | I/O | Output video data / Serial Output Data signal                                                 |  |  |

| DSDAT              |    |     |                                                                                               |  |  |

| VCLKOUT/ DSCLK     | 16 | 0   | Parallel video interface clock output/ Serial output clock                                    |  |  |

| VALIDH / WR# /     | 17 | 0   | Horizontal VALID output / Write to LCD – active low                                           |  |  |

| DSFRM              |    |     | Serial Output Frame signal                                                                    |  |  |

| VALIDV             | 18 | 0   | Vertical VALID output signal or interrupt output on Frame start                               |  |  |

| DVDD28             | 19 | I   | 2.8V for digital circuits                                                                     |  |  |

| SDIN               | 20 | I/O | I <sup>2</sup> C -compatible bi-directional data signal. Open-drain type.                     |  |  |

| PS1                | 21 | I   | Chip operation modes [PS1, PS2]:                                                              |  |  |

| PS2                | 22 | Ι   | 00 – Reset<br>01 – Full operation<br>11 – Reserved<br>10 – Reserved                           |  |  |

| Reserved           | 23 | -   | Module noise shield                                                                           |  |  |

| LED control        | 24 | 0   | GPO pin, Activates the white LED for low light condition                                      |  |  |

The 24-pin camera module option uses  $I^2C$  and an 8/9-bit parallel video interface.

(\*) 9<sup>th</sup> bit output or chip select options are selected through wire bonding

Table 2: 24-pin Module Pin List

## 2. Functional Description

The figure below shows the main functional blocks of the TC5747 and the basic signal flow.

Figure 1: TC5747 Functional Block Diagram

### 2.1 CONT

The **CONT** unit controls the TC5747 units via a central programming bus. Its operation is synchronized with the frame image sequence through several interrupt sources. It is directly accessed by the serial interfaces

### 2.2 RCLK

The RCLK unit generates the RESET and CLOCK signals to the various units.

### 2.3 IMGA

The **IMGA** unit controls the image array and the analog processing unit. It produces the various timing controls, performs the "Mirror" transformations and the "Fixed Pattern Noise" corrections. After receiving the array pixels (the **ADC** output) and performing the required corrections and offsets, the data is sent to the **YUVR** unit for processing, or to the **PVI** or **SVI** unit for Bayer output.

### 2.4 YUVR

The **YUVR** unit transforms the Bayer data received from the **IMGA** unit into **YUV** or **RGB** data by applying several image reconstruction and correction algorithms. Demosaicing, dynamic range enhancement, digital gain, filter downscaling, sharpening or blurring, color correction, gamma correction, **RGB** to **YUV** conversion, **YUV**-to-**RGB** conversion and cropping for display are all performed in the **YUVR** unit. Resizing of the image can be done by 2X - 8X to achieve target LCD screen size with full field of view.

### 2.5 JPEG

The JPEG unit performs encoding or decoding of JPEG images. In encode mode it receives YUV 4:2:2 data, and compresses the image into a JPEG stream. The JPEG compressed image is stored in RAM that is accessible to the CONT unit core and to the  $I^2C$  interface. The JPEG unit can also be configured to send out the RAM content to one of the output units, with optional ancillary data header and checksum.

In decode mode, the compressed code is written to the Code memory, and the JPEG unit decodes it into YUV 4:2:2, 4:2:0 or 4:1:1 data.

**4:2:0** and **4:1:1** formats are interpolated into **4:2:2** format. **YUV** data are then sent to the **YUVR** unit for resizing and cropping. From the **YUVR** unit the decoded image is sent to the Parallel Video Interface unit for display.

Compression of a display ready image, after scaling and overlay of screen bitmap is also supported.

The **JPEG** unit can also output a thumbnail image.

### 2.6 PVI and SVI

The Parallel Video Interface (**PVI**) and Serial Video Interface (**SVI**) units are the output interfaces of the TC5747 device. Each interface can be configured to output one of several streams (**Bayer**, **YUV 4:2:2**, **RGB**, **JPEG**). The **PVI** can be configured as a parallel video interface or as a serial output interface.

### 2.7 Imager and Address Generator

The imager includes a VGA size pixel array, gain, double sampling, black pixel and readout circuits and ADC. The address generator receives timing signals from the control unit and produces the sequence signals to the pixel array for exposure control, read and reset operations. There are several modes of reading the array content, enabling various image resolutions by windowing and by down sampling. At different modes, various modes of power saving are used. VGA sized images can be read at a rate of up to 20 frames per second. For smaller images at higher frame-rates, several working modes are implemented.

### 2.8 Pixel Array Configuration

The pixel array is 648 by 487 active pixels, surrounded by four black columns on each side and 13 black lines above and 14 black lines below the active image array. This results in a total of 656 by 514 pixels.

### 2.9 Bayer Grid Configuration

Each pixel in the array is covered by a color filter, to create a Bayer grid format:

The sensor operates in rolling mode, in which the exposure and readout processes are linked. The sampling of each row data is performed at the end of the integration time. After sampling the selected-row data, the row is reset. The row is sampled again after the reset for the double-sampling procedure. The integration of that row starts again according to the exposure parameters.

A set of registers defines the total size of the frame and the size of the array that is read out and sent to the **YUVR** unit for further processing. Another set of registers defines the exposure time that is required for the array.

Figure 2: Bayer Grid Configuration

### 2.10 Resolutions and Frame Rates

The following table summarizes the possible resolutions and frame rates that the TC5747 can produce. The calculation for modes 1, 2 and 3 assume an input and color-processing clock of 32MHz. For mode 4, a 16MHz clock is assumed. The analog clock rate varies according to mode.

|                                 | MODE 1<br>(Full resolution) | MODE 2<br>(MODE1with<br>window) | MODE 3<br>(down-sample, only 1<br>ADC is used) | MODE 4<br>(down-sample with<br>speed-up) |

|---------------------------------|-----------------------------|---------------------------------|------------------------------------------------|------------------------------------------|

|                                 | 32MHz rclk                  | 32MHz rclk                      | 32MHz rclk                                     | 16MHz <b>rclk</b>                        |

|                                 | 8MHz pixel<br>clock         | 8MHz pixel clock                | 8MHz pixel clock                               | 4MHz pixel clock                         |

|                                 | 8 rclk cycles/pix           | 8 rclk cycles/pix               | 8 rclk cycles/pix                              | 4 rclk cycles/pix                        |

|                                 | Full power                  | Full power                      | Slightly reduced power                         | Significantly reduced power              |

| VGA                             | 20 fps                      |                                 |                                                |                                          |

| <b>QVGA</b> – no<br>down sample |                             | 40 fps (reduced field of view)  | 40 fps (full field of view)                    | 40 fps (reduced field of view)           |

| <b>QVGA</b> –down sample        | 20 fps                      |                                 |                                                |                                          |

Table 3: Analog Clock Rate Modes

### 2.11 Analog Processing

Analog processing includes a separate gain control for each color filtered pixel, dark pixel correction for each color separately, dark and black-offset correction, faulty pixel replacement and 10-bit ADC.

### 2.12 On-chip Micro Controller

The TC5747 is fully controlled by the embedded microcontroller. Once the firmware, which is supplied by TransChip, is loaded, the embedded microcontroller sets the appropriate registers, and runs the automatic image processing algorithms. An external host does not need to access TC5747 registers and set values, nor does it need to run any algorithm. An easy to use API (Application Programming Interface) is provided to set or adjust various camera controls. The API is performed via a small set of host commands, which are sent over the serial interface (I<sup>2</sup>C or UART), and are interpreted by the embedded microcontroller, to perform specific camera control, or any other defined internal task.

The set of host commands include:

- Color adjustments (Brightness, contrast, saturation, etc)

- Image Format (size, mirror x and y, etc)

- Automatic algorithm enable and parameters (Auto Exposure, AWB, Auto Flicker detection and cancellation)

The concept of host commands makes it very useful, as it is going to be forward compatible with any of TransChip sensor, since it is not hardware dependent (namely no need to use specific hardware registers.

TransChip supplies sample C code, which shows how to upload the firmware and use the host commands (software API). The sample includes all the needed C header files. The supplied firmware comes with preset default values for the various controls. Thus even if no single host commands is performed the firmware ensures that the sensor is running properly according to a preset default set.

TransChip also supplies a released version of the firmware.

The host commands are fully detailed in a separate document.

### 2.13 Bayer to YUV Translation Unit (YUVR)

The **YUVR** is the color-processing unit. The unit's parameters and mode registers are loaded through the control bus. The Bayer image is received from the **IMGA** unit, processed by the **YUVR** unit, and transferred to the PVI unit for output out of the device. While processing the image, statistics are calculated by the **YUVR** unit. After completing the processing of an image, the **YUVR** unit produces an interrupt to the **CONT** unit. The **YUVR** thus signifies to the **CONT** that the statistics for the current image are ready, and the **CONT** may read the results through the main control bus.

The **YUVR** unit receives the **Bayer** grid as input. For each pixel, two color values are missing and need to be reconstructed. The input accuracy is 10 bits. The **YUVR** unit reconstructs the **RGB** per pixel, performs correction algorithms and generates the **YUV** representation of the image.

Digital color processing includes: demosaicing, dynamic range enhancement, digital gain, filter downscaling, sharpening or blurring, flicker detection and removal, color and white balance correction, gamma correction, color suppression, zoom by 2X or 4X, **RGB** to **YUV** conversion, **YUV**-to-**RGB** conversion, down sample and cropping of **RGB** for display, **RGB** formatting (6:6:6, 5:6:5, 4:4:4) are all performed in the **YUVR** unit.

Zoom is performed by creating a full resolution image from a small region in the center of the image. The small region is blown up by 2X or by 4X to the target image size. The missing pixels are interpolated from the original pixels using a filter to provide a smooth appearance.

### 2.14 JPEG Compression Unit (JCOR)

The **JPEG** unit receives the **YUV 4:2:2** image data from the **YUVR** unit, and performs real-time **JPEG** compression. A 25K Byte memory is used for the **JPEG** compression process. The memory is divided into a Raster-to-Block operation buffer and a **JPEG**-code memory section. The 64K Bytes of memory can hold a full VGA-sized compressed image at a compression ratio of up to 1.7 bits per pixel.

The partition of the memory is fully configurable.

- When a higher compression ratio is used, several images can be stored in the memory. For example, when capturing a VGA-sized image, three compressed images of 0.5 bits per pixel can be stored in the 64K Byte JPEG-code memory section.

- When capturing a smaller image, a smaller buffer is required for the Raster-to-Block operation. Therefore a larger JPEG-code memory section can be allocated for support of a lower compression ratio.

The **JPEG**-compressed image can be transmitted either on the parallel video output interface or on the serial video output interface. Alternatively, the host can read the **JPEG**-compressed image from the on-chip **JPEG**-code memory via the  $I^2C$  interface.

The JPEG unit can optionally create also a thumbnail image for the full resolution compressed image.

The **JPEG** unit can also be configured to send out RAM contents to one of the output units, with optional ancillary data header and checksum.

The **JPEG** unit can also be activated in decompression mode. The compressed code is written to the Code memory, and the **JPEG** unit decodes it into **YUV 4:2:2** data. The **YUV** data is then sent to the **YUVR** unit for resizing and cropping. From the **YUVR** unit the decoded image is sent to the Parallel Video Interface unit for display.

## 3. Reset and Clock

### 3.1 Low Power Modes

The chip operation is controlled by two bits [**PS1**, **PS2**]:

Chip operation modes [PS1, PS2]:

- **00** Startup

- 01 Full operation

- **11** Sleep

- **10** Power down

#### 3.1.1 Startup

The camera powers up at start up mode "00". Then it moves to full operation mode "01".

#### 3.1.2 Bypass

To enter bypass mode, send a host command for power save, then provide standby mode "11" or switch off the input clock. Bypass mode power consumption is  $60\mu$ A. This minimum power is consumed by a minimal power-supply digital regulator. Contents of memories and registers are maintained. The host can access the LCD during bypass mode.

To return to full operation from standby mode, switch on the input clock and wait for clock stability, then send a host command for full operation.

#### 3.1.3 Power Down

To enter power down mode, send a host command for power down, and then provide power down mode "10". Power down mode consumes less than  $10\mu$ A.

To return to full operation from power down mode: provide full operation mode "**01**", wait for clock stability, then send a host command for full operation and load the camera program.

### 3.2 PLL Configurations

An on-chip PLL is configured to supply the internal working clock signal in several modes:

- Bypass mode internal clock is identical in frequency to input clock.

- PLL mode, for support of an internal clock in the range of 24-36MHx

- 8x internal clock is 8x the input clock, for support of low frequency input (3-4MHz input)

- 4x internal clock is 4x the input clock, for support of low frequency input (8-9MHz input)

- 2x internal clock is 2x the input clock, for support of medium frequency input (13-16MHz input)

- 1.5x internal clock is 1.5x the input clock, for support of high frequency input (20-24MHz input)

Each of the two output units, the **PVI** and **SVI** have a serial clock whose frequency is a multiple of the input clock. Each clock, **rclkp** and **rclks** is configured separately.

### 3.3 Device Initialization Sequence

The Initialization sequence includes the following steps:

- 1 After system power-up, the Power Save pins should be put into Startup mode.

- 2 Clock input and **RESET\_N** should be activated.

- 3 After the Regulators' wake up time, the Power Save pins should be put into Full-on mode.

- **4 RESET\_N** is deactivated.

- **5 PLL** mode should be set.

- 6 After PLL lock time, Bypass mode may be deactivated.

When working in Bypass mode, steps 5 and 6 may be skipped.

## 4. TC5747MF24L Interfaces

The TC5747MF24L chip has the following interfaces:

- I<sup>2</sup>C or UART control interface

- Parallel Video Interface (PVI)

- Serial Video Interface (SVI)

### 4.1 I<sup>2</sup>C Serial Interface

#### 4.1.1 Overview

The I<sup>2</sup>C interface is a two-wire bi-directional serial bus. The TC5747 can operate as a slave device only.

Both wires (**SCL** and **SDA**) are connected to a positive supply via a pull-up resistor, and when the bus is free both lines are high. The output stage of the device must have an open-drain or open collector type IO cell so that a wired-AND function between all devices that are connected on the bus can be performed.

Each device is recognized by a unique 7-bit address. The address allocated to TC5747-B0 is **0x47**. When performing write operations, add 0 to the LSB to get **0x8E**. For a Read operation add **1** to the LSB to get **0x8F**.

To summarize:

| Address | I <sup>2</sup> C Write | I <sup>2</sup> C Read |

|---------|------------------------|-----------------------|

| 0x47    | 0x8E                   | 0x8F                  |

**Note:** Some operating systems automatically add the 1 or 0 bit to the 7 bit address. The address for the TC5747-A0 is **0x47**.

A control of the byte order in I<sup>2</sup>C transactions is provided through setting a register.

### 4.1.2 Mode of Operation

The bus master, typically the host **DSP**, initiates an access to the TC5747 device. The bus master activates a START condition, and passes the address of the requested device along with the type of access (read or write bit – the MSB or the start byte). The requested device replies with an acknowledge (ACK). The host can then perform as many transactions as it wishes, until the host activates a STOP condition. The bus is considered free after the STOP condition.

The data on the **SDA** pin must be stable during the high period of the clock (**SCL**) as shown in the figure below. Only the host may change the data while **SCL** is high. A high-to-low transition marks a START condition, and a low-to-high a STOP condition.

**Figure 4:** I<sup>2</sup>C Interface START and STOP Conditions

The master device activates a **START** condition, and sends the first byte of data that contains the 7-bit address, and a direction bit ( $\mathbf{R}/\mathbf{W}$ #, 1 for read, 0 for write). The addressed device answers by pulling down the SDA line as acknowledge procedure.

The TC5747 expects the first two bytes after the address byte to be the register address of the first register that is to be read or written by the host. Programming is done in host commands level which is translated into a series of register level commands.

When writing registers to the TC5747, the following bytes are data bytes. The data for each READ or WRITE access is two bytes long. The TC5747 performs auto increment until the STOP condition is identified. Auto increment is not performed when the initial address is in the address space that is allocated to the On-Chip-Memories. This address space is reserved for tables, where multiple bytes are written to a single address.

When reading registers from the TC5747, the register address (2 bytes) should be followed by a repeated START condition, device address, and  $\mathbf{R}/\mathbf{W}$  bit equal to 1, to change mode from write (address) to read (data).

The sequence of loading or reading registers is described in the figure below.

- The colored boxes represent host-to-slave data transfer.

- The clear boxes represent slave-to-host data transfer.

TC5700 WRITE protocol ппп ЛГ W ASE Ack Ack /Ack START Register address [15:8] Register address [7:0] 0xAC Or 0xAE (write) (write) Ack Ack STOP Data byte[7:0] (write) Data Byte [15:8] (write) - data is driven by I2C host xN times (Consecutive access supported)

Figure 6: I<sup>2</sup>C Host-Write Access

TC5700 READ protocol - single access

Figure 7: I<sup>2</sup>C Host-Read Access

Figure 8: I<sup>2</sup>C Host-Read Multiple (N) Accesses

The host should activate the STOP condition if a direction change is needed.

### 4.2 Parallel Video Interface (PVI)

The PVI generates the video output of the TC5747. The interface consists of a vertical frame-start signal and a 10-bit parallel data bus with clock and qualify signals. It supports parallel and serial modes of operation.

#### 4.2.1 Parallel Mode of Operation

The PVI produces a clock signal (the **CLK\_OUT** pin), a 10-bit data bus, **DOUT[9:0]** and qualifying signals that are synchronous to that clock. On each determining edge of **CLK\_OUT**, a single data byte is transferred on the data bus, if qualified by the **VALIDH** signal.

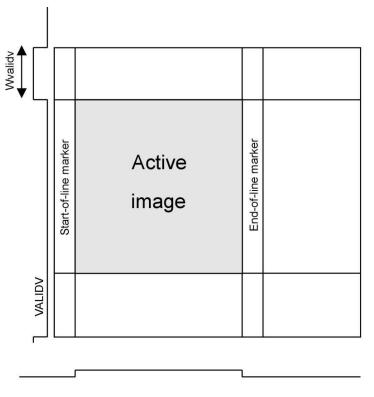

Note: VALIDH is active during the shaded region

Figure 9: PVI Qualification Signal Timing

Valid data are qualified by the **VALIDH** signal. The **VALIDH** signal is activated only when image data is sent out on the parallel interface. It is inactive when dark lines are read, or during the vertical blank period. The **VALIDH** signal can be configured to qualify only the valid image data, or to qualify optional Start-of-line and End-of-line markers.

Note: Duration and polarity of VALIDV signal is programmable

Figure 10: Vertical and Horizontal Qualify Signals

TransChip © 17

The DOUT[9:0] bus carries either the Bayer grid data, the YUV 4:2:2 output data, the RGB data (RGB565, RGB666 or RGB444) or JPEG code according to the TCIF\_OUTPUT\_FORMAT host command.

- Bayer Grid data is left-justified.

- 10-bit Bayer resides on **DOUT[9:0]**

- 9-bit Bayer resides on **DOUT[9:1]**

- 8-bit Bayer resides on DOUT[9:2]

- The 8-bit YUV data resides on the **DOUT[9:2]** output pads, annotated **DYUV[7:0]**.

- The 8-bit **RGB565** or **RGB444** data resides on the **DOUT[9:2]** output pads.

- The 9-bit **RGB666** data resides on the **DOUT[9:1]** output pads.

RGB666 can also be transmitted using 3 clock cycles on the DOUT bus

- The 6-bit **RGB666** (3-word mode) data resides on the **DOUT[9:4]** output pads.

- The 8-bit JPEG data resides on the **DOUT[9:2]** output pads.

For 2-word output formats, **RGB444**, **565** and **666**, the data is packed into 2 words:

| • | RGB444: | {Blue[3:0], 0x0}        |            | {Red[3:0],Green[3:0]} |

|---|---------|-------------------------|------------|-----------------------|

| • | RGB565: | {Green[2:0], Blue[4:0]} | {Red[4:0], | Green[5:3]}           |

| • | RGB666: | {Green[2:0], Blue[5:0]} | {Red[5:0], | Green[5:3]}           |

For 3-word RGB 666 output formats, the data is sent out as 3 words:

• RGB666: Red[5:0], Green[5:0]

Blue[5:0]

The active line timing is depicted in the diagrams below. The diagram below shows the active data line where the optional Start-of-line and End-of-line markers are omitted:

Figure 11: PVI Bayer Output Format

Figure 13: RGB 565 Output on Parallel Video Output Interface

The output clock rate for **YUV** or 2-word RGB output is double the output clock rate for Bayer output. The output clock rate for 3-word **RGB666** is double the output clock rate for **YUV** output.

When sending out the data in Bayer-grid format, a "RED" line will always be the first line in the frame.

#### 4.2.2 External Chip-Select

A mode may be selected where the data bus may be floated or driven according to an external chip-select input controlled by the CSDAT# pin. The CSDAT# pin is active-low, i.e. when low the DOUT[9:1] or DYUV[7:0] bus pins are driven, and when CSDAT# is high these outputs are put in a tri-state position. The VALIDH, VALIDV and VCLKOUT pins are not affected by the CSDAT# pin.

#### 4.2.3 Qualified Clock Mode

The TC5747 supports a mode where the **VCLKOUT** pin is not active when there is no active data on the parallel interface.

### 4.2.4 VALIDH Configured as WR#

The VALIDH pin may be configured to work as a WRITE signal for applications requiring that the video data is being written into a device. The polarity is programmable. The data is marked as valid only when the VALIDV pin is active. The data should be sampled on the trailing edge of the VALIDH pin.

#### 4.2.5 Frame-Rate Control

The CONT unit uses the **c\_outframe** signal to control the frame rate. It enables or disables the output of a full frame. When output is disabled, the **VALIDH** and **VALIDV** output signals are stuck at an inactive state. The data output bus holds the background value throughout the disabled frame time.

Figure 16: Frame Rate Control

The **c\_outframe** signal changes on **im\_frame**. The decision if to send or skip the new frame is made on the clock cycle that follows the **im\_frame signal**.

#### 4.2.6 Data

#### 4.2.6.1 General

The type of data (**Bayer, RGB, YCrCb 4:2:2** or **JPEG**) output from the TC5747 is programmable through the TC5747 programming registers, using host commands. The type of data also defines the frequency of the TC5747's output clock signal.

#### 4.2.6.2 Bayer Output

When **Bayer** output is selected, the data volume is one byte per pixel.

If Data-Markers are added, 8 more bytes per line must be taken into consideration in the image buffer that is allocated for the application.

There are two types of **Bayer** data lines:

- "RED" lines lines that carry Green and Red Bayer components. The Green and Red data bytes are interleaved. The even numbered bytes (0, 2 to 2n) are Green, the odd numbered bytes (1,3 to 2n+1) are Red.

- "BLUE" lines lines that carry Blue and Green Bayer components. The Green and Blue data bytes are interleaved. The even numbered bytes (0, 2 to 2n) are Blue, the odd numbered bytes (1,3 to 2n+1) are Green.

When sending out the data in **Bayer**-grid format, a "RED" line will always be the first line in the frame.

#### 4.2.6.3 YCrCb 4:2:2 Output

When **YCrCb 4:2:2** output is selected, the data volume is two bytes per pixel. If Data-Markers are added, 8 more bytes per line must be taken into consideration in the image buffer that is allocated for the application.

The data in the **YCrCb 4:2:2** output format is ordered in several configurations, according to the setting in the **Color\_order** bits in the video output control registers:

#### 4.2.6.4 RGB565 Output

When **RGB565** output is selected, the data volume is two bytes per pixel. Output data are transmitted in the same manner and frequency as the **YCrCb 4:2:2** output format, on **DOUT[9:2]**. The first byte of each pixel carries 5 bits of the Red color component, and the 3 MSB of the Green. The second byte carries the 3 LSB of the Green color component, and the 5 bits of the Blue color component.

#### 4.2.6.5 RGB666 Output

When **RGB666** output is selected, the data volume is two 9-bit "words" per pixel. Two modes can be selected for **RGB666** data.

#### Two-transfers Mode

When **RGB666** output is selected, the data volume is two 9-bit "words" per pixel. No extra pixels are required beyond the **VGA/QVGA** size.

The output data is transmitted in the same manner and frequency as the **YCrCb 4:2:2** output format, on **DOUT[9:1]**. The first byte of each pixel carries 6 bits of the Red color component, and the 3 MSB of the Green. The second byte carries the 3 LSB of the Green color component, and the 6 bits of the Blue color component.

#### Three-transfers Mode

When three-transfer **RGB666** output is selected, the data volume is three 6-bit "words" per pixel. No extra pixels are required beyond the **VGA/QVGA** size.

The output data is transmitted on **DOUT[9:4]**. The order of transmission is Red, Green and Blue.

The output data is transmitted in the double the frequency as the **YCrCb 4:2:2** output format, 3 consecutive clock cycles carry valid data, and the fourth clock cycle is skipped. No valid data is active on this clock cycle, and **VALIDH** is inactive.

#### 4.2.6.6 RGB444 Output

When **RGB444** output is selected, the data volume is two bytes per pixel. The output data is transmitted in the same manner and frequency as the **YCrCb 4:2:2** output format, on **DOUT[9:2]**. The first byte of each pixel carries 4 bits of the Red color component, and the 4 bits of the Green. The second byte carries the 4 bits of the Blue color component on **DOUT[9:6]**, and is padded by 6 zeros on **DOUT[5:0]**.

#### 4.2.6.7 JPEG Output

When JPEG output is selected, the compressed code is sent out on the parallel data bus, qualified by VALIDH. To support ancillary data format as defined in the ITU 656 and ITU 1364 standards, an optional ancillary data packet header may be added before each consecutive packet of bytes of JPEG code. A Checksum byte may be added following the data bytes. The last "packet" of JPEG code may contain less than packet number of bytes, and the "payload byte" in the packet header reflects the actual size.

#### 4.2.7 Data Markers

Extra optional data markers are inserted at the beginning and end of each image line. The user may select between TransChip-specific markers, and markers that conform to the **ITU 656** standard.

#### 4.2.7.1 TransChip Markers

A "Timing signal" or Marker is defined in the **ITU 656** standard as a sequence of four bytes, the first three bytes holding reserved values of **FF 00 00**, and the fourth byte composed of a collection of bits whose function is defined in the standard. The TransChip markers utilize the format of the markers as defined in the standard, but redefines two bits in the last marker byte.

There are four types of markers:

- Start of First Line marker This marker precedes the data of the first line in a frame.

- Start of Line Marker This marker precedes the data of each line in a frame, except for the first line. When Bayer output mode is selected, bit #5 of the marker content differentiates between a "red" line and a "blue" line (0 and 1 respectively).

- End of Last Line Marker This marker immediately follows the data of the last line in a frame.

- End of Line Marker This marker immediately follows the data of each line in a frame, except for the last line.

All markers are 4 bytes long. The first 3 bytes of all markers are identical, and annotate the marker header. The marker content is "**FF 00 00 xy**", where xy is different for each marker type.

| Marker                     | Marker Header |      |      | Marker content<br>DOUT[9:2] / DYUV[7:0] |

|----------------------------|---------------|------|------|-----------------------------------------|

| SOFL                       | 0xFF          | 0x00 | 0x00 | 0xC7                                    |

| SOLR (YCrCb or "red" line) | 0xFF          | 0x00 | 0x00 | 0x80                                    |

| SOLB ("blue" line)         | 0xFF          | 0x00 | 0x00 | 0xAB                                    |

| EOLL                       | 0xFF          | 0x00 | 0x00 | 0xDA                                    |

| EOL                        | 0xFF          | 0x00 | 0x00 | 0x9D                                    |

#### Table 4: TransChip Markers

Bits [7:4] of the Marker-content byte carry the marker information:

- Bit [7] Always 1 to avoid 0x00 code

- Bit [6] Special frame markers (start-first-line/end-last-line)

- Bit [5] For Bayer line "color" (0 for Red, 1 for Blue)

- Bit [4] End/Start bit, 0 for Start-of-line marker, 1 for End-of-line

Bits [3:0] of the Marker-content byte provide parity check capability, allowing for one-bit errors to be corrected, and two-bit errors to be detected, according to ITU-656-4 Standard.

#### 4.2.7.2 ITU 656 Markers

A "Timing signal" or Marker is defined in the **ITU 656** standard as a sequence of four bytes, the first three bytes holding reserved values of **FF 00 00**, and the fourth byte composed of a collection of bits whose function is defined in the standard.

Bits [7:4] of the Marker-content byte carry the marker information:

- Bit [7] Always 1 to avoid 0x00 code

- Bit [6] F field 0 or field 1

- Bit [5] V blank or active video line indication (0 for active, 1 for blank)

- Bit [4] H End/Start bit, 0 for Start-of-line marker, 1 for End-of-line

Bits [3:0] of the Marker-content byte provide parity check capability, allowing for one-bit errors to be corrected, and two-bit errors to be detected, according to **ITU-656-4** Standard.

When adhering to the bit-definition of the **ITU-656** standard, there is a need to distinguish between consecutive frames, either by inserting markers on at least one blank line between frames, or by toggling the field bit on every frame start.

The **PVI** supports the following options.

| Marker       | Field | Marker Header |      |      | Marker content<br>DOUT[9:2] / DYUV[7:0] |

|--------------|-------|---------------|------|------|-----------------------------------------|

| SAV - active | 0     | 0xFF          | 0x00 | 0x00 |                                         |

| SAV - blank  | 0     | 0xFF          | 0x00 | 0x00 |                                         |

| EAV - active | 0     | 0xFF          | 0x00 | 0x00 |                                         |

| EAV - blank  | 0     | 0xFF          | 0x00 | 0x00 |                                         |

| SAV - active | 1     | 0xFF          | 0x00 | 0x00 |                                         |

| SAV - blank  | 1     | 0xFF          | 0x00 | 0x00 |                                         |

| EAV - active | 1     | 0xFF          | 0x00 | 0x00 |                                         |

| EAV - blank  | 1     | 0xFF          | 0x00 | 0x00 |                                         |

Table 5: ITU 656 Markers

#### 4.2.7.3 Avoiding Marker Emulation

When the Send-Markers mode is enabled, care has to be taken to avoid marker-emulation inside the data itself.

- When YCrCb 4:2:2 output mode is selected, there is no contention between marker header contents and the transmitted data, because the Y data values are limited to the range of 16-235, and the Cr and Cb data values are limited to the 16-240 range. 0x00 and 0xFF values never occur inside the image data values.

- When Bayer output is selected, the data has to be modified, so that 0xFF and **0x00** values are removed from the data content, and replaced by their nearest allowed values (0xFE and **0x01** respectively).

- When **RGB565** output is selected, the data has to be modified, as in the case of the Bayer output. **0xFF** and **0x00** values are removed from the data content, and replaced by their nearest allowed values.

- The first byte of **RGB565** is replaced by **0xF7** or **0x08**.

- The second byte of **RGB565** is replaced by **0xFE** or **0x01**.

- When **RGB666** output is selected, the data has to be modified, as in the case of the Bayer output. **0xFF** and **0x00** values are removed from the data content, and replaced by their nearest allowed values.

- TBD

- When **RGB444** output is selected, the data has to be modified, as in the case of the Bayer output. **0xFF** and 0x00 values are removed from the data content, and replaced by their nearest allowed values.

- The first byte of **RGB444** is replaced by **0xEF** or **0x10**.

- The second byte of **RGB444** is replaced by **0xF0** or **0x01**.

- JPEG code cannot be modified. However, there is no need for any modification if Ancillary format is used for JPEG transmission.

#### 4.2.8 Ancillary Data Format

The **ITU-1364** defines the ancillary data format that may be transmitted during blank lines of video, as defined in the **ITU 656** standard.

Immediately following a blank line "Timing signal", an ancillary data packet may be added. If an ancillary data header is detected instead of the blank video data, as defined by the standard (a sequence of 0x80 0x10), ancillary data can be extracted.

An ancillary data header is defined as a sequence of 6 bytes:

#### 0x00 0xFF 0xFF ID1 ID2 Data-SIZE/4

The header is followed by data (4 to 252 bytes).

A Check-sum byte follows the data as the last byte of the packet.

The ancillary header and checksum are optionally produced by the JPEG unit. The **PVI** does not differentiate between header and JPEG code.

#### 4.2.9 Serial Output Mode

The Transmitted data size for Serial output mode is 8 bits per transmitted "word". Bayer output provides 8 bits per pixel, and **YUV** and **RGB** output provides 16 bits per pixel. The bytes are sent with the MSB first, LSB last. During continuous transfer, the MSB of byte N immediately follows the LSB of byte (N-1).

The TC5747 serial output interface can be configured to work in two different modes:

- Clock-qualify mode A two wire interface with clock and output data signals. The TC5747 acts as a

master of the interface. It activates the serial clock signal when there is valid data to be sent out.

- **SSI** mode A three wire interface, with clock, output data and frame signals. The TC5747 acts as a master of the interface, producing all three signals.

#### 4.2.9.1 Clock-Qualify Mode

The serial interface consists of two pins:

- DSCLK Data Serial Clock output pin –1X or 2X the rate of the data output TC5747 generates DSCLK signal from its general clock input signal.

- **DSDAT** Serial Data output pin.

The TC5747 acts as a master of the interface. It activates the serial clock signal when there are valid data to be sent out.

- Serial Clock Polarity Clock is inactive at zero

- Serial Clock Phase Drive data on positive edge of Serial clock signal (DSCLK/2), latch on negative edge

#### 4.2.9.2 SSI Mode

The serial interface consists of three pins:

- **DSCLK** Data Serial Clock output pin

- **DSDAT** Serial Data output pin.

- **DSFRM** Frame signal in early-frame mode

The TC5747 acts as a master of the interface. It activates the Frame signal one clock period before there is valid data to be sent out. Transfer datum size configurable. There are three options:

- Transfer datum size is a single byte.

- Transfer datum size is a single line (size is according to output image size and output mode).

- Transfer datum size is a single image. This configuration can be used only in a mode that combines the **SSI**-mode with the clock-qualify mode.

#### **DSFRM Signal**

The **DSFRM** signal notifies of a transfer of a complete data unit. There are three configurations, as described below.

#### Single Byte Transfer Mode

The 8 bits of the transfer byte are sent out on the eight following effective edges of the **DSCLK** signal. When the last bit of the byte is sent out, the **DSFRM** signal may be active again. If it is active, the following byte transfer begins on the next effective edge of **DSCLK**.

Figure 20: Single Byte Transfer Mode

#### Image-line Transfer Mode

In this mode, **DSFRM** is activated one clock before the continuous transfer of a complete image line. Transfer size should be configured on the receiving side according to the image line size, taking into consideration the **SAV** and **EAV** markers, if used.

#### Frame Transfer Mode

In this mode, the **DSFRM** signal is activated once in a frame, one clock cycle before the first byte of the image is transferred out.

The **DSFRM** signal duration is also configurable, to be of one clock cycle duration, or to be active until the last byte of data in the transfer is transmitted. The second mode can be used to generate an interrupt inside the receiving device, once the complete data has been transferred.

#### DSCLK Output

The **DSCLK** output can be configured to be continuous or gated. The gated option should be used when **DSFRM** is in the Frame-transfer mode.

### 4.3 Serial Video Interface

The TC5747 Serial Video interface unit is identical to the PVI unit described above, with two exceptions:

- Supports only serial interface

- Support also **SSI** input of data. The data input is controlled through the I<sup>2</sup>C. The addition of input direction provides a high speed input serial interface for decompression of JPEG images.

## 5. High Level API Programming

All TC5747 series products come with a flexible software API (Applications Program Interface) for integration of the product and interfacing it to a wide range of hosts. The API is based on a set of defined host commands.

The TC5747 is controlled by an embedded microcontroller. The microcontroller runs the firmware that is supplied by TransChip. The microcontroller receives the host commands, and executes them to perform various camera control functions.

### 5.1 Firmware Loading

The microcontroller firmware (program) may be loaded through the host interface. (When using I2C or UART for control, firmware is loaded either using the  $I^2C$  interface or the UART interface). Once the program is loaded, the microcontroller sets the registers and controls the entire chip according to the firmware preset defaults and according to host commands which the microcontroller receives through the control interfaces.

## 6. AC/DC Specifications

The TC5747 chip excels in low power consumption

### 6.1 Absolute Maximum Ratings

| Symbol          | Parameter           | Min | Max  |

|-----------------|---------------------|-----|------|

| V <sub>DD</sub> | DC supply Voltage   |     | 4.0V |

| TA              | Storage Temperature | -30 | 70°C |

Table 6: Absolute Maximum Ratings

### 6.2 Recommended Operating Conditions

| Symbol          | Parameter                        |      | Max   |

|-----------------|----------------------------------|------|-------|

| V <sub>DD</sub> | DC supply Voltage – 2.8V nominal | 2.52 | 3.08V |

| TA              | Operating Temperature            | -10  | 60°C  |

Table 7: Recommended Operating Conditions

### 6.3 DC Electrical Characteristics

| Symbol           | Characteristic                            | Condition             | Specifications |          |          |  |

|------------------|-------------------------------------------|-----------------------|----------------|----------|----------|--|

|                  |                                           |                       | Min            | Тур      | Max      |  |

| VIH <sup>1</sup> | Input Hi-Volt                             | VDD=2.8V;Temp=25⁰C    | 2.0V           |          |          |  |

| VIH <sup>2</sup> | Input Hi-Volt                             | VDD=2.8V;Temp=25⁰C    |                |          |          |  |

| VIL <sup>1</sup> | Input Low-Volt                            | VDD=2.8V;Temp=25⁰C    |                |          | 0.8V     |  |

| VIL <sup>2</sup> | Input Low-Volt                            | VDD=2.8V;Temp=25⁰C    |                |          |          |  |

| VOH              | Input Hi-Volt                             | VDD=2.8V;Temp=25⁰C    | 2.4V           |          |          |  |

| VOL              | Input Low-Volt                            | VDD=2.8V;Temp=25⁰C    |                |          | 0.4V     |  |

| IOL              |                                           | VOL=0.5*VDD;Temp=25ºC |                | 13.3mA   |          |  |

| IOH              |                                           | VOH=0.5*VDD;Temp=25°C |                | 19.4mA   |          |  |

| IDDmax           | Supply current in working conditions      | VDD=2.8V;Temp=25ºC    |                | 15mA TBD |          |  |

|                  |                                           | VGA mode, 15 fps      |                |          |          |  |

| ll/loz           | Input leakage/<br>Output tristate leakage |                       |                | +/- 1uA  | +/- 10uA |  |

Table 8: DC Electrical Characteristics

1 - All pins except clk\_in

2 - clk\_in

### 6.4 Parallel Video Output Clock Qualified Mode AC Characteristics

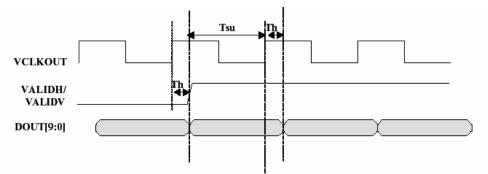

Figure 21: Parallel Video Output Clock Qualified Mode

| Parameter | Description                                | Specifications |     | Units |

|-----------|--------------------------------------------|----------------|-----|-------|

|           |                                            | Min            | Мах |       |

| Tsu       | Data setup before effective edge of VALIDH | 150            | -   | ns    |

| Th        |                                            | 25             | -   | ns    |

Table 9: Parallel Video Output Clock Qualified Mode AC Characteristics

$^{*}$  Results depend on device frequency and mode. The results in this table are for 32MHz, PVI CLK = clk\_in.

### 6.5 Parallel Video Output Camera Interface Mode AC Characteristics

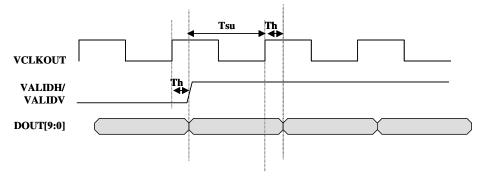

Figure 22: Parallel Video Output Camera Interface Mode

| Parameter | Description                                 | Specifications |     | Units |

|-----------|---------------------------------------------|----------------|-----|-------|

|           |                                             | Min            | Max |       |

| Tsu       | Data setup before effective edge of VCLKOUT | 150            | -   | ns    |

| Th        |                                             | 25             | -   | ns    |

Table 10: Parallel Video Output Camera Interface Mode AC Characteristics

\* Results depend on device frequency and mode. The results in this table are for 32MHz, **PVI CLK = clk\_in.**

### 6.6 Parallel Video Output Interface AC Characteristics

Figure 23: Parallel Video Output Interface Signals

| Parameter | Description                                 | Min | Max | Units |

|-----------|---------------------------------------------|-----|-----|-------|

| Tsu       | Data setup before effective edge of VCLKOUT | 150 | -   | nsec  |

| Th        |                                             | 25  | -   | nsec  |

Table 11: Parallel Video Output Interface AC Characteristics

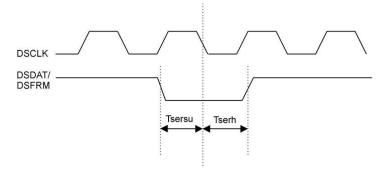

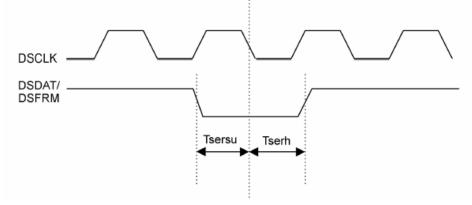

### 6.7 Serial Video Output Interface AC Characteristics

Figure 24: Serial Video Output Interface Signals

| Parameter | Description                                                 | Min | Max | Units |

|-----------|-------------------------------------------------------------|-----|-----|-------|

| Tsersu    | Data setup (DSDAT and DSFRM) before negative edge of DSCLK. | 5   | -   | nsec  |

| Tserh     | Data hold (DSDAT and DSFRM) before negative edge of DSCLK.  | 5   | -   | nsec  |

### 6.8 Serial Video Output Clock Qualified mode AC Characteristics

#### Figure 25: Serial Video Output Clock Qualified mode AC

| Parameter | Description                                                | Specifications |     | Units |

|-----------|------------------------------------------------------------|----------------|-----|-------|

|           |                                                            | Min            | Max |       |

| Tsersu    | Data setup (DSDAT and DSFRM) before negative edge of DSCLK | 5              | -   | ns    |

| Tserh     | Data hold (DSDAT and DSFRM) before negative edge of DSCLK. | 5              | -   | ns    |

Table 12: Serial Video Output Clock Qualified mode AC Characteristics

\* Results depend on device frequency and mode. The results in this table are for 32MHz, SVI CLK = clk\_in.

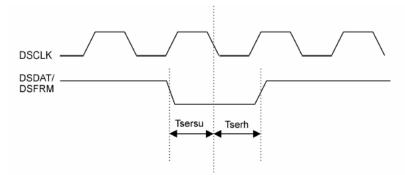

### 6.9 Serial Video Output SSI mode AC Characteristics

#### Figure 26: Serial Video Output SSI mode

| Param  | Description                                                |     | Specifications |    |

|--------|------------------------------------------------------------|-----|----------------|----|

|        |                                                            | Min | Max            |    |

| Tsersu | Data setup (DSDAT and DSFRM) before negative edge of DSCLK | 5   | -              | ns |

| Tserh  | Data hold (DSDAT and DSFRM) before negative edge of DSCLK  | 5   | -              | ns |

Table 13: Serial Video Output SSI mode AC Characteristics

\* Results depend on device frequency and mode. The results in this table are for 32MHz, SVI CLK = clk\_in.

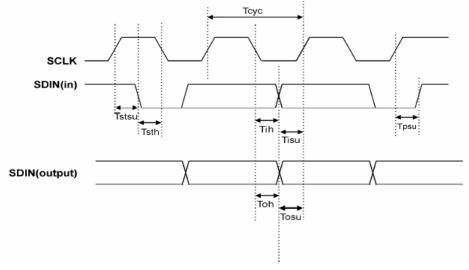

## 6.10 I<sup>2</sup>C-Compatible Interface AC Characteristics

| Parameter | Description                                 | Specifications |     | Units |

|-----------|---------------------------------------------|----------------|-----|-------|

|           |                                             | Min            | Max |       |

| Fmax      | Maximum SCLK frequency                      |                | 400 | KHz   |

| Тсус      | SCLK cycle duration                         | 2500           |     | ns    |

| Tstsu     | Start condition SCLK setup time             | 125            |     | ns    |

| Tsth      | Start condition SCLK hold time              | 250            |     | ns    |

| Tih       | SDIN input hold time 125 ns                 |                | ns  |       |

| Tisu      | isu SDIN input setup time 250               |                |     | ns    |

| Tpsu      | Tpsu         Stop condition SCLK setup time |                |     | ns    |

| Toh       | SDIN output hold time                       | 125            |     | ns    |

| Tosu      | SDIN output setup time                      | 250            |     | ns    |

Table 14: I<sup>2</sup>C-Compatible Interface AC Characteristics

**Note:** Data entered is calculated for 400KHz **SCLK** frequency.

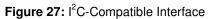

## 7. Mechanical and Electrical Drawings

### 7.1 TC5747MF24L 24-pin Package

Following is a mechanical drawing of the TC5747MF24L 24-pin module.

TransChip © 36

Figure 29: TC5747 24-pin Module Mechanical Drawing Continued

TransChip © 37

## 7.2 Lens Specification

| Characteristic           | 1/4 " Lens module                         |  |

|--------------------------|-------------------------------------------|--|

| Material                 | Heat resistant plastic                    |  |

| Structure                | Three element (one glass and two plastic) |  |

| Effective Focal Length   | 3.72 mm                                   |  |

| Focal Range              | 40cm - infinity                           |  |

| F Number                 | 2.4                                       |  |

| Angle of View (FOV)      | 55° Diagonal                              |  |

|                          | 45° Horizontal                            |  |

|                          | 35° Vertical                              |  |

| Focus                    | Factory fixed focused                     |  |

| IR Filter                | Included                                  |  |

| Resolution (MTF) for RGB | 0.47 @ 45 cy/mm on-axis                   |  |

|                          | 0.40 @ 45 cy/mm Vertical                  |  |

|                          | 0.30 @ 45 cy/mm Horizontal                |  |

|                          | 0.27 @ 45 cy/mm Diagonal                  |  |

| Relative Illumination    | 100% On-Axis                              |  |

|                          | 75% Vertical                              |  |

|                          | 65% Horizontal                            |  |

|                          | 55% Diagonal                              |  |

| TV Distortion            | <1%                                       |  |

| Module Height            | 5.5 mm +0.1 mm/ -0.2mm                    |  |

Table 15: Lens Specifications