## ICL8052A/ICL71C03, ICL8068A/ICL71C03

May 2001 File Number 3081.2

# Precision 4<sup>1</sup>/<sub>2</sub> Digit, A/D Converter

The ICL8052A or ICL8068A/ICL71C03 chip pairs with their multiplexed BCD output and digit drivers are ideally suited for the visual display DVM/DPM market. The outstanding  $4^{1}/_{2}$  digit accuracy, 200.00mV to 2.0000V full scale capability, auto-zero and auto-polarity combine with true ratiometric operation, almost ideal differential linearity and time-proven dual slope conversion. Use of these chip pairs eliminates clock feedthrough problems, and avoids the critical board layout usually required to minimize charge injection.

When only 2000 counts of resolution are required, the 71C03 can be wired for  $3^{1}/_{2}$  digits and give up to 30 readings/sec., making it ideally suited for a wide variety of applications.

The ICL71C03 is an improved CMOS plug-in replacement for the ICL7103 and should be used in all new designs.

## Part Number Information

| PART NUMBER  | TEMP.<br>RANGE ( <sup>o</sup> C) | PACKAGE      | PKG.<br>NO. |

|--------------|----------------------------------|--------------|-------------|

| ICL8052ACPD  | 0 to 70                          | 14 Ld PDIP   | E14.3       |

| ICL8068ACDD  | 0 to 70                          | 14 Ld CERDIP | F14.3       |

| ICL8068ACJD  | 0 to 70                          | 14 Ld CERDIP | F14.3       |

| ICL71C03ACPI | 0 to 70                          | 28 Ld PDIP   | E28.6       |

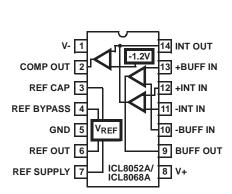

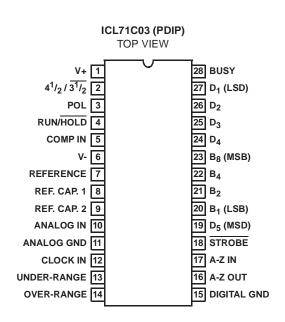

ICL8052A/ICL8068A

(CERDIP, PDIP) TOP VIEW

## **Pinouts**

## Features

- Typically Less Than  $2\mu V_{\mbox{P-P}}$  Noise (200.00mV Full Scale, ICL8068A

- Accuracy Guaranteed to ±1 Count Over Entire ±20,000 Counts (2.0000V Full Scale)

- Guaranteed Zero Reading for 0V Input

- True Polarity at Zero Count for Precise Null Detection

- Single Reference Voltage Required

- Over-Range and Under-Range Signals Available for Auto-Ranging Capability

- All Outputs TTL Compatible

- Medium Quality Reference, 40ppm (Typ) on Board

- Blinking Display Gives Visual Indication of Over Range

- Six Auxiliary Inputs/Outputs are Available for Interfacing to UARTs, Microprocessors or Other Complex Circuitry

- 5pA Input Current (Typ) (8052A)

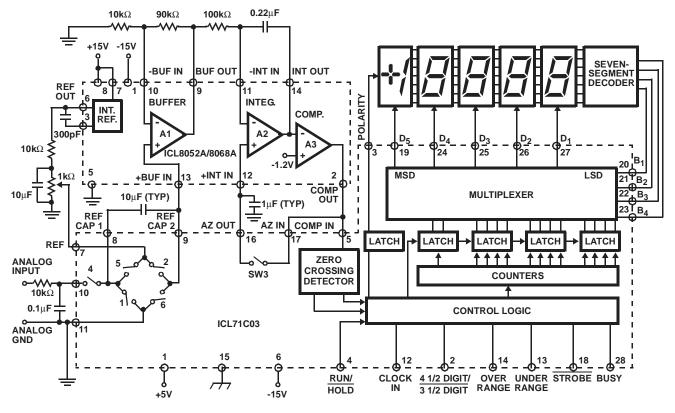

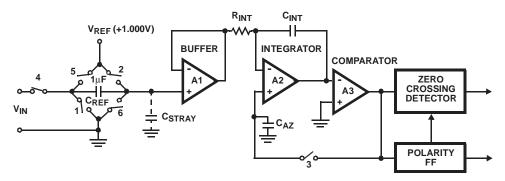

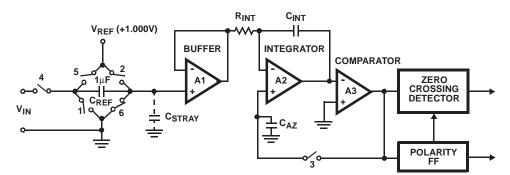

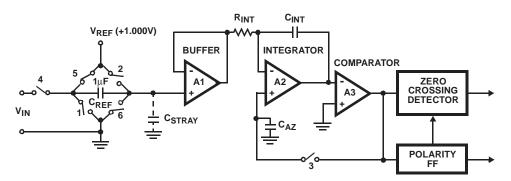

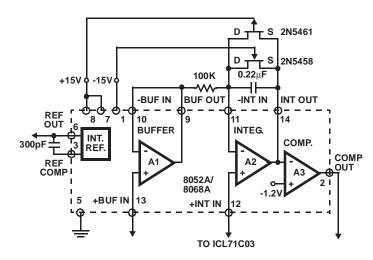

## Functional Block Diagram

FIGURE 1.

intersil

#### **Absolute Maximum Ratings**

#### ICL8052A, ICL8068A

#### **Thermal Information**

| Thermal Resistance (Typical, Note 5) | θ <sub>JA</sub> ( <sup>o</sup> C/W) | θ <sub>JC</sub> ( <sup>o</sup> C/W)      |

|--------------------------------------|-------------------------------------|------------------------------------------|

| CERDIP Package                       | 75                                  | 20                                       |

| 14 Ld PDIP Package                   |                                     | N/A                                      |

| 28 Ld PDIP Package                   | 65                                  | N/A                                      |

| Maximum Storage Temperature          |                                     | -65 <sup>0</sup> C to 150 <sup>0</sup> C |

| Maximum Lead Temperature (Solderin   | ıg, 10s)                            |                                          |

#### **Operating Conditions**

Temperature Range......0°C to 70°C

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

- 1. θ<sub>JA</sub> is measured with the component mounted on a low effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

- 2. For supply voltages less than ±15V, the absolute maximum input voltage is equal to the supply voltage.

- 3. Short circuit may be to ground or either supply. Rating applies to 70°C ambient temperature.

- 4. Input voltages may exceed the supply voltages provided the input current is limited to ±100μA.

- 5. Connecting any digital inputs or outputs to voltages greater then V+ or less than GND may cause destructive device latchup. For this reason it is recommended that the power supply to the ICL71C03 be established before any inputs from sources not on that supply are applied.

- 6.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

#### **Electrical Specifications**

| PARAMETER                                                                                                                                              | SYMBOL              | TEST<br>CONDITIONS      | MIN | ТҮР  | МАХ  | UNITS |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------|-----|------|------|-------|

| Clock In, Run/Hold, 4 1/2 / 3 1/2                                                                                                                      | I <sub>INL</sub>    | V <sub>IN</sub> = 0     | -   | 0.2  | 0.6  | mA    |

|                                                                                                                                                        | I <sub>INH</sub>    | V <sub>IN</sub> = +5V   | -   | 0.1  | 10   | μA    |

| Comp. In Current                                                                                                                                       | I <sub>INL</sub>    | V <sub>IN</sub> = 0     | -   | 0.1  | 10   | μA    |

|                                                                                                                                                        | I <sub>INH</sub>    | V <sub>IN</sub> = +5V   | -   | 0.1  | 10   | μA    |

| Threshold Voltage                                                                                                                                      | VINTH               |                         | -   | 2.5  | -    | V     |

| All Outputs                                                                                                                                            | V <sub>OL</sub>     | I <sub>OL</sub> = 1.6mA | -   | 0.25 | 0.40 | V     |

| B <sub>1</sub> , B <sub>2</sub> , B <sub>4</sub> , B <sub>8</sub> , D <sub>1</sub> , D <sub>2</sub> , D <sub>3</sub> , D <sub>4</sub> , D <sub>5</sub> | V <sub>OH</sub>     | I <sub>OH</sub> = -1mA  | 2.4 | 4.2  | -    | V     |

| Busy, Strobe, Over-Range, Under-Range Polarity                                                                                                         | V <sub>OH</sub>     | I <sub>OH</sub> = -10μA | 4.9 | 4.99 | -    | V     |

| Switches 1, 3, 4, 5, 6                                                                                                                                 | rDS(ON)             |                         | -   | 400  | -    | Ω     |

| Switch 2                                                                                                                                               | rDS(ON)             |                         | -   | 1200 | -    | Ω     |

| Switch Leakage (All)                                                                                                                                   | I <sub>D(OFF)</sub> |                         | -   | 2    | -    | pА    |

| +5V Supply Range                                                                                                                                       | V+                  |                         | 4   | 5    | 6    | V     |

| -15V Supply Range                                                                                                                                      | V-                  |                         | -5  | -15  | -18  | V     |

| +5V Supply Current                                                                                                                                     | l+                  | f <sub>CLK</sub> = 0    | -   | 1.1  | 3    | mA    |

| -15V Supply Current                                                                                                                                    | l-                  | f <sub>CLK</sub> = 0    | -   | 0.8  | 3    | mA    |

| Power Dissipation Capacitance                                                                                                                          | C <sub>PD</sub>     | vs Clock Frequency      | -   | 40   | -    | pF    |

| Clock Frequency (Note 6)                                                                                                                               |                     |                         | DC  | 2000 | 1200 | kHz   |

NOTE:

7. This specification relates to the clock frequency range over which the ICL71C03A will correctly perform its various functions. See the "Max Clock Frequency" section under Component Value Selection for limitations on the clock frequency range in a system.

<u>intersil</u>

## ICL8068A Electrical Specifications $V_{SUPPLY} = \pm 15V$ , $T_A = 25^{\circ}C$ , Unless Otherwise Specified

| PARAMETER                                                       | SYMBOL           | TEST<br>CONDITIONS | MIN    | ТҮР  | МАХ  | UNITS               |

|-----------------------------------------------------------------|------------------|--------------------|--------|------|------|---------------------|

| EACH OPERATIONAL AMPLIFIER                                      |                  |                    |        |      |      |                     |

| Input Offset Voltage                                            | V <sub>OS</sub>  | $V_{CM} = 0V$      | -      | 20   | 65   | mV                  |

| Input Current (Either Input) (Note 7)                           | I <sub>IN</sub>  | $V_{CM} = 0V$      | -      | 80   | 150  | рА                  |

| Common-Mode Rejection Ratio                                     | CMRR             | $V_{CM} = \pm 10V$ | 70     | 90   | -    | dB                  |

| Non-Linear Component of Common-Mode Rejection<br>Ratio (Note 8) |                  | $V_{CM} = \pm 2V$  | -      | 110  | -    | dB                  |

| Large Signal Voltage Gain                                       | A <sub>V</sub>   | $R_L = 50k\Omega$  | 20,000 | -    | -    | V/V                 |

| Slew Rate                                                       | SR               |                    | -      | 6    | -    | V/µs                |

| Unity Gain Bandwidth                                            | GBW              |                    | -      | 2    | -    | MHz                 |

| Output Short-Circuit Current                                    | Isc              |                    | -      | 5    | -    | mA                  |

| COMPARATOR AMPLIFIER                                            |                  |                    | 1      |      | 1    |                     |

| Small-Signal Voltage Gain                                       | A <sub>VOL</sub> | $R_L = 30k\Omega$  | -      | -    | -    | V/V                 |

| Positive Output Voltage Swing                                   | +VO              |                    | 12     | 13   | -    | V                   |

| Negative Output Voltage Swing                                   | -V <sub>O</sub>  |                    | -2.0   | -2.6 | -    | V                   |

| VOLTAGE REFERENCE                                               |                  |                    | 1      |      | 1    |                     |

| Output Voltage                                                  | Vo               |                    | 1.60   | 1.75 | 1.90 | V                   |

| Output Resistance                                               | R <sub>O</sub>   |                    | -      | 5    | -    | Ω                   |

| Temperature Coefficient                                         | TC               |                    | -      | 40   | -    | ppm/ <sup>o</sup> C |

| Supply Voltage (V++ -V-)                                        | VSUPPLY          |                    | ±10    | -    | ±16  | V                   |

| Supply Current Total                                            | ISUPPLY          |                    | -      | 8    | 14   | mA                  |

## ICL8052A Electrical Specifications $V_{SUPPLY} = \pm 15V$ , $T_A = 25^{\circ}C$ , Unless Otherwise Specified

| PARAMETER                                                       | SYMBOL           | TEST<br>CONDITIONS | MIN    | ТҮР  | МАХ  | UNITS |

|-----------------------------------------------------------------|------------------|--------------------|--------|------|------|-------|

| EACH OPERATIONAL AMPLIFIER                                      |                  |                    | -      |      |      | 1     |

| Input Offset Voltage                                            | V <sub>OS</sub>  | $V_{CM} = 0V$      | -      | 20   | 75   | mV    |

| Input Current (Either Input) (Note 7)                           | I <sub>IN</sub>  | $V_{CM} = 0V$      | -      | 2    | 10   | pА    |

| Common-Mode Rejection Ratio                                     | CMRR             | $V_{CM} = \pm 10V$ | 70     | 90   | -    | dB    |

| Non-Linear Component of Common-Mode Rejection<br>Ratio (Note 8) |                  | $V_{CM} = \pm 2V$  | -      | 110  | -    | dB    |

| Large Signal Voltage Gain                                       | A <sub>V</sub>   | $R_L = 50k\Omega$  | 20,000 | -    | -    | V/V   |

| Slew Rate                                                       | SR               |                    | -      | 6    | -    | V/µs  |

| Unity Gain Bandwidth                                            | GBW              |                    | -      | 1    | -    | MHz   |

| Output Short-Circuit Current                                    | Isc              |                    | -      | 20   | -    | mA    |

| COMPARATOR AMPLIFIER                                            |                  |                    |        |      |      |       |

| Small-Signal Voltage Gain                                       | A <sub>VOL</sub> | $R_L = 30k\Omega$  | -      | -    | -    | V/V   |

| Positive Output Voltage Swing                                   | +V <sub>O</sub>  |                    | 12     | 13   | -    | V     |

| Negative Output Voltage Swing                                   | -V <sub>O</sub>  |                    | -2.0   | -2.6 | -    | V     |

| VOLTAGE REFERENCE                                               |                  |                    |        |      |      |       |

| Output Voltage                                                  | V <sub>O</sub>   |                    | 1.60   | 1.75 | 1.90 | V     |

| Output Resistance                                               | R <sub>O</sub>   |                    | -      | 5    | -    | Ω     |

<u>intersil</u>

#### ICL8052A Electrical Specifications $V_{SUPPLY} = \pm 15V$ , $T_A = 25^{\circ}C$ , Unless Otherwise Specified (Continued)

| PARAMETER                | SYMBOL              | TEST<br>CONDITIONS | MIN | ТҮР | МАХ | UNITS               |

|--------------------------|---------------------|--------------------|-----|-----|-----|---------------------|

| Temperature Coefficient  | тс                  |                    | -   | 40  | -   | ppm/ <sup>o</sup> C |

| Supply Voltage (V++ -V-) | V <sub>SUPPLY</sub> |                    | ±10 | -   | ±16 | V                   |

| Supply Current Total     | ISUPPLY             |                    | -   | 6   | 14  | mA                  |

NOTES:

8. The input bias currents are junction leakage currents which approximately double for every  $10^{\circ}$ C increase in the junction temperature, T<sub>J</sub>. Due to limited production test time, the input bias currents are measured with junctions at ambient temperature. In normal operation the junction temperature rises above the ambient temperature as a result of internal power dissipation, P<sub>D</sub>. T<sub>J</sub> = T<sub>A</sub> + R<sub>θJA</sub>P<sub>D</sub>, where R<sub>θJA</sub> is the thermal resistance from junction to ambient. A heat sink can be used to reduce temperature rise.

9. This is the only component that causes error in dual-slope converter.

#### System Electrical Specifications: ICL8068A/ICL71C03

V++ = +15V, V+ = +5V, V- = -15V,  $T_A = 25^{\circ}C$ , f<sub>CLK</sub> Set for 3 Readings/Sec.

|                                                                                                     | TEST                                                                                                                   | ICL8   | ICL8068A/ICL71C03<br>(NOTE 9) |        |        | ICL8068A/ICL71C03<br>(NOTE 10) |        |                     |

|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------|-------------------------------|--------|--------|--------------------------------|--------|---------------------|

| PARAMETER                                                                                           | CONDITIONS                                                                                                             | MIN    | ТҮР                           | MAX    | MIN    | TYP                            | MAX    | UNITS               |

| Zero Input Reading                                                                                  | V <sub>IN</sub> = 0V,<br>Full Scale = 200mV                                                                            | -000.0 | ±000.0                        | +000.0 | -000.0 | ±000.0                         | 000.0  | Digital<br>Reading  |

| Ratiometric Error (Note 11)                                                                         | V <sub>IN</sub> = V <sub>REF</sub><br>Full Scale = 2V                                                                  | 0.999  | 1.000                         | 1.001  | 0.9999 | 1.0000                         | 1.0001 | Digital<br>Reading  |

| Linearity Over $\pm$ Full Scale (Error of Reading from Best Straight Line)                          | $-2V \le V_{IN} \le +2V$                                                                                               | -      | 0.2                           | 1      | -      | 0.5                            | 1      | Counts              |

| Differential Linearity (Difference between<br>Worst Case Step of Adjacent Counts and<br>Ideal Step) | $-2V \le V_{IN} \le +2V$                                                                                               | -      | 0.01                          | -      | -      | 0.01                           | -      | Counts              |

| Rollover Error (Difference in Reading for<br>Equal Positive & Negative Voltage Near<br>Full Scale)  | $-V_{IN} \cong +V_{IN} \approx 2V$                                                                                     | -      | 0.2                           | 1      | -      | 0.5                            | 1      | Counts              |

| Noise (P-P Value Not Exceeded 95% of Time)                                                          | V <sub>IN</sub> = 0V,<br>Full Scale = 200mV                                                                            | -      | 3                             | -      | -      | 2                              | -      | μV                  |

| Leakage Current at Input                                                                            | V <sub>IN</sub> = 0V                                                                                                   | -      | 200                           | 300    | -      | 100                            | 200    | pА                  |

| Zero Reading Drift (Note 12)                                                                        | $ \begin{array}{l} V_{IN} = 0V, \\ 0^{0}C \leq T_{A} \leq 50^{0}C \end{array} \end{array} $                            | -      | 1                             | 5      | -      | 0.5                            | 2      | μV/ <sup>o</sup> C  |

| Scale Factor Temperature Coefficient<br>(Note 12)                                                   | $\label{eq:VIN} \begin{array}{l} V_{IN} = 2V, \\ 0^o C \leq T_A \leq 50^o C \\ \text{Ext. Ref. 0ppm/}^o C \end{array}$ | -      | 3                             | 15     | -      | 2                              | 5      | ppm/ <sup>o</sup> C |

#### System Electrical Specifications: ICL8052A/ICL71C03

V++ = +15V, V+ = +5V, V- = -15V,  $T_A = 25^{\circ}C$ , f<sub>CLK</sub> Set for 3 Reading/Sec.

|                                                                        | TEST ICL8052A/ICL71C03<br>(NOTE 9)                    |        |        | ICL80  |        |        |        |                    |

|------------------------------------------------------------------------|-------------------------------------------------------|--------|--------|--------|--------|--------|--------|--------------------|

| PARAMETER                                                              | CONDITIONS                                            | MIN    | TYP    | MAX    | MIN    | TYP    | MAX    | UNITS              |

| Zero Input Reading                                                     | V <sub>IN</sub> = 0V,<br>Full Scale = 2V              | -0.000 | ±0.000 | +0.000 | -0.000 | ±0.000 | 0.000  | Digital<br>Reading |

| Ratiometric Error (Note 11)                                            | V <sub>IN</sub> = V <sub>REF</sub><br>Full Scale = 2V | 0.999  | 1.000  | 1.001  | 0.9999 | 1.0000 | 1.0001 | Digital<br>Reading |

| Linearity Over ± Full Scale (Error of Reading from Best Straight Line) | $-2V \le V_{IN} \le +2V$                              | -      | 0.2    | 1      | -      | 0.5    | 1      | Counts             |

intersil

#### System Electrical Specifications: ICL8052A/ICL71C03

V++ = +15V, V+ = +5V, V- = -15V,  $T_A = 25^{\circ}C$ , f<sub>CLK</sub> Set for 3 Reading/Sec. (Continued)

|                                                                                                     | TEST                                                                                              | ICL8052A/ICL71C03<br>(NOTE 9) |          | ICL8052A/A/ICL71C03<br>(NOTE 10) |     |      |     |                     |

|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------|----------|----------------------------------|-----|------|-----|---------------------|

| PARAMETER                                                                                           | CONDITIONS                                                                                        | MIN                           | ТҮР      | MAX                              | MIN | ТҮР  | MAX | UNITS               |

| Differential Linearity (Difference between<br>Worst Case Step of Adjacent Counts and<br>Ideal Step) | $-2V \le V_{IN} \le +2V$                                                                          | -                             | 0.01     | -                                | -   | 0.01 | -   | Counts              |

| Rollover Error (Difference in Reading for<br>Equal Positive & Negative Voltage Near<br>Full Scale)  | $\text{-V}_{IN}\cong\text{+V}_{IN}\approx2\text{V}$                                               | -                             | 0.2      | 1                                | -   | 0.5  | 1   | Counts              |

| Noise (Peak-To-Peak Value Not<br>Exceeded 95% of Time)                                              | $V_{IN} = 0V,$<br>Full Scale = 200mV,<br>Full Scale = 2V                                          | -                             | 20<br>50 | -                                | -   | 30   |     | μV                  |

| Leakage Current at Input                                                                            | V <sub>IN</sub> = 0V                                                                              | -                             | 5        | 30                               | -   | 3    | 10  | pА                  |

| Zero Reading Drift                                                                                  | V <sub>IN</sub> = 0V,<br>0 <sup>o</sup> C To 70 <sup>o</sup> C                                    | -                             | 1        | 5                                | -   | 0.5  | 2   | μV/ <sup>o</sup> C  |

| Scale Factor Temperature Coefficient                                                                | V <sub>IN</sub> = 2V,<br>0 <sup>o</sup> C To 70 <sup>o</sup> C,<br>Ext. Ref. 0ppm/ <sup>o</sup> C | -                             | 3        | 15                               | -   | 2    | 5   | ppm/ <sup>o</sup> C |

NOTES:

10. Tested in 3<sup>1</sup>/<sub>2</sub> digit (2,000 count) circuit shown in Figure 5, clock frequency 12kHz. Pin 2 71C03 connected to GND.

11. Tested in 4<sup>1</sup>/<sub>2</sub> digit (20,000 count) circuit shown in Figure 5, clock frequency 120kHz. Pin 2 71C03A open.

12. Tested with a low dielectric absorption integrating capacitor. See Component Selection Section.

13. The temperature range can be extended to 70<sup>o</sup>C and beyond if the Auto-Zero and Reference capacitors are increased to absorb the high temperature leakage of the 8068A.

## **Detailed Description**

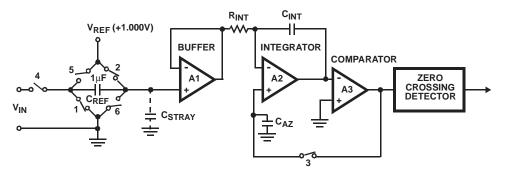

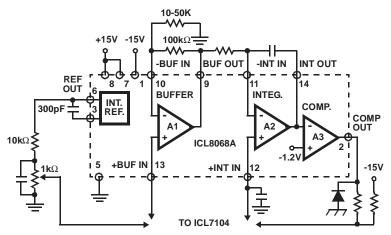

#### **Analog Section**

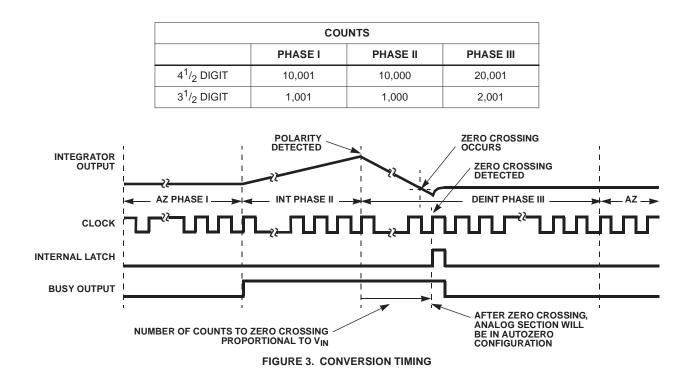

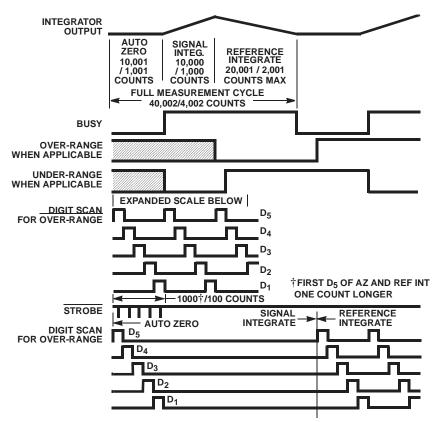

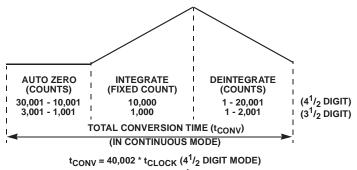

Figure 2 shows the equivalent Circuit of the Analog Section of both the ICL71C03/8052A and the ICL71C03/8068A in the 3 different phases of operation. IF the RUN/HOLD pin is left open or tied to V+, the system will perform conversions at a rate determined by the clock frequency: 40,0002 at  $4^{1}/_{2}$  digit and 4002 at  $3^{1}/_{2}$  digit clock periods per cycle (see Figure 3 for details of conversion timing).

#### Auto-Zero Phase I (Figure 2A)

During the Auto-Zero, the input of the buffer is connected to  $V_{REF}$  through switch 2, and switch 3 closes a loop around the integrator and comparator, the purpose of which is to charge the auto-zero capacitor until the integrator output does not change with time. Also, switches 1 and 2 recharge the reference capacitor to  $V_{REF}$ .

#### Input Integrate Phase II (Figure 2B)

During Input Integrate the auto-zero loop is opened and the ANALOG INPUT is connected to the BUFFER INPUT through switch 4 and  $C_{REF}$ . If the input signal is zero, the buffer, integrator and comparator will see the same voltage that existed in the previous state (Auto-Zero). Thus, the integrator output will not change but will remain stationary during the entire Input Integrate cycle. If V<sub>IN</sub> is not equal to zero, and unbalanced condition exists compared to the Auto

Zero phase, and the integrator will generate a ramp whose slope is proportional to  $V_{IN}$ . At the end of this phase, the sign of the ramp is latched into the polarity F/F.

#### Deintegrate Phase II (Figures 2C and 2D)

During the Deintegrate phase, the switch drive logic uses the output of the polarity F/F in determining whether to close switch 6 or 5. If the input signal is positive, switch 6 is closed and a voltage which is  $V_{REF}$  more negative than during Auto-Zero is impressed on the BUFFER INPUT. Negative Inputs will cause +2( $V_{REF}$ ) to be applied to the BUFFER INPUT via switch 5. Thus, the reference capacitor generates the equivalent of a (+) or (-) reference from the single reference voltage with negligible error. The reference voltage returns the output of the integrator to the zero-crossing point established in Phase I. The time, or number of counts, required to do this is proportional to the input voltage. Since the Deintegrate phase can be twice as long as the Input Integrate Phase, the input voltage required to give a full scale reading is  $2V_{REF}$ .

FIGURE 2B. PHASE II INTEGRATE INPUT

FIGURE 2C. PHASE III + DEINTEGRATE

FIGURE 2D. PHASE III - DEINTEGRATE FIGURE 2. ANALOG SECTION OF EITHER ICL8052A OR ICL8068A WITH ICL71C03

intersil

#### Zero-Crossing Flip-Flop

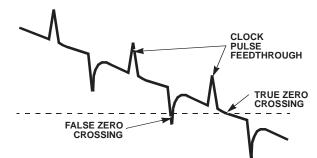

Figure 4 shows the problem that the zero-crossing F/F is designated to solve.

The integrator output is approaching the zero-crossing point where the count will be latched and the reading displayed. For a 20,000 count instrument, the ramp is changing approximately 0.50mV per clock pulse (10V Max integrator output divided by 20,000 counts). The clock pulse feedthrough superimposed upon this ramp would have to be less than 100mV peak to avoid causing significant errors.

The flip-flop interrogates the data once every clock pulse after the transients of the previous clock pulse and half-clock pulse have died down. False zero-crossings caused by clock pulses are not recognized. Of course, the flip-flop delays the true zero-crossing by one count in every instance, and if a correction were not made, the display would always be one count too high. Therefore, the counter is disabled for one clock pulse at the beginning of phase 3. This one count delay compensates for the delay of the zero crossing flipflop, and allows the correct number to be latched into the display. Similarly, a one count delay at the beginning of phase 1 gives an overload display of 0000 instead of 0001. No delay occurs during phase 2, so that true ratiometric readings result.

FIGURE 4. INTEGRATOR OUTPUT NEAR ZERO-CROSSING

## **Detailed Description**

#### **Digital Section**

The 71C03 includes several pins which allow it to operate conveniently in more sophisticated systems. These include:

#### 4-1/2 / 3-1/2 (PIN 2)

When high (or open) the internal counter operates as a full  $4^{1}/_{2}$  decade counter, with a complete measurement cycle requiring 40,002 counts. When held low, the least significant decade is cleared and the clock is fed directly into the next decade. A measurement cycle now requires only 4,0002 clock pulses. All 5 digit drivers are active in either case, with each digit lasting 200 counts with Pin 2 high  $(4^{1}/_{2} \text{ digit})$  and 20 counts for Pin 2 low  $(3^{1}/_{2} \text{ digit})$ .

### RUN/HOLD (PIN 4)

When high (or open) the A/D will free-run with equally spaced measurement cycles every 40,0002/4,002 clock pulses. If taken low, the converter will continue the full measurement cycle that it is doing and then hold this reading as long as Pin 4 is held low. A short positive pulse (greater then 300ns) will now initiate a new measurement cycle beginning with up to 10,001/1,001 counts of auto zero. Of course if the pulse occurs before the full measurement cycle (40,002/4,002 counts) is completed, it will not be recognized and the converter will simply complete the measurement it is doing. An external indication that full measurement cycle has been completed is that the first STROBE pulse (see below) will occur 101/11 counts after the end of this cycle. Thus, if RUN/HOLD is low and has been low for at least 101/11 counts, converter is holding and ready to start a new measurement when pulsed high.

### STROBE (PIN 18)

This is a negative-going output pulse that aids in transferring the BCD data to external latches, UARTs or microprocessors. There are 5 negative-going STROBE pulses that occur once and only once for each measurement cycle starting 101/11 pulses after the end of the full measurement cycle. Digit 5 (MSD) goes high at the end of the measurement cycle and stays on for 201/21 counts. In the center of this digit pulse (to avoid race conditions between changing BCD and digit drives) the first STROBE pulse goes negative for 1/2 clock pulse width. Similarly, after Digit 5, Digit 4 goes high (for 200/20 clock pulses) and 100/10 pulses later the STROBE goes negative for the second time. This continues through Digit 1 (LSD) when the fifth and last STROBE pulse is sent. The digit drive will continue to scan (unless the previous signal was over-range) but no additional STROBE pulses will be sent until a new measurement is available.

#### BUSY (PIN 28)

BUSY goes high at the beginning of signal integrate and stays high until the first clock pulse after zero-crossing (or after end of measurement in the case of an OVER-RANGE). The internal latches are enabled (i.e., loaded) during the first clock pulse after BUSY and are latched at the end of this clock pulse. The circuit automatically reverts to auto-zero when not BUSY so it may also be considered an A-Z signal. A very simple means for transmitting the data down a single wire pair from a remote location would be to AND BUSY with clock and subtract 10,001/1,001 counts from the number of pulses received - as mentioned previously there is one "NO-count" pulse in each Reference Integrate cycle.

#### **OVER-RANGE (PIN 4)**

This pin goes positive when the input signal exceeds the range (20,000/2,000) of the converter. The output F-F is set at the end of BUSY and is reset to zero at the beginning of Reference Integrate in the next measurement cycle.

#### UNDER-RANGE (PIN 13)

This pin goes positive when the reading is 9% of range or less. The output F-F is set at the end of BUSY (if the new reading is 1800/180 or less) and is reset a the beginning of Signal Integrate of the next reading.

#### POLARITY (PIN 3)

This pin is positive for a positive input signal. It is valid even for a zero reading. In other words, +0000 means the signal is positive but less than the least significant bit. The converter can be used as null detector by forcing equal (+) and (-) readings. The null at this point should be less than 0.1 LSB. This output becomes valid at the beginning of Reference Integrate and remains correct until it is revalidated for the next measurement.

#### DIGIT DRIVES (PINS 19, 24, 25, 26, AND 27)

Each digit drive is a positive-going signal which lasts for 200/20 clock pulses. The scan sequence is  $D_5$ (MSD),  $D_4$ ,  $D_3$ ,  $D_2$ , and  $D_1$  (LSD). All five digits are scanned even when operating in the  $3^{1}/_{2}$  digit mode, and this scan is continuous unless and OVER-RANGE occurs. Then all Digit drives are blanked from the end of the STROBE sequence until the beginning of Reference Integrate, at which time  $D_5$  will start the scan again. This gives a blinking display as a visual indication of OVER-RANGE.

#### BCD (PINS 20, 21, 22 AND 23)

The Binary coded decimal bit  $B_8$ ,  $B_4$ ,  $B_2$ , and  $B_1$  are positive logic signals that go on simultaneously with the Digit driver.

FIGURE 5. TIMING DIAGRAM FOR OUTPUTS

#### **Component Value Selection**

For optimum performance of the analog section, care must be taken in the selection of values for the integrator capacitor and resistor, auto-zero capacitor, reference voltage, and conversion rate. These values must be chosen to suit the particular application.

#### Integrating Resistor

The integrating resistor is determined by the full scale input voltage and the output current of the buffer used to charge the integrator capacitor. This current should be small compared to the output short circuit current such that thermal effects are kept to a minimum and linearity is not affected. Values of  $5\mu$ A to  $40\mu$ A give good results with a nominal of  $20\mu$ A. The exact value may be chosen by:

$$R_{INT} = \frac{Full Scale Voltage (See Note)}{20 \mu A}$$

NOTE: If gain is used in the buffer amplifier, then:

$$R_{INT} = \frac{(BufferGain) (Full Scale Voltage)}{20 \mu A}$$

#### Integrating Capacitor

The product of integrating resistor and capacitor is selected to give 9V swing for full scale inputs. This is a compromise between possibly saturating the integrator (at +14V) due to tolerance buildup between the resistor, capacitor and clock and the errors a lower voltage swing could induce due to offsets referred to the output of the comparator. In general, the value of  $C_{INT}$  is given by:

10

$$C_{INT} = \frac{\begin{bmatrix} 10,000(4-1/2 \text{ Digit}) \times \text{Clock Period} \end{bmatrix} \times (20\mu\text{A})}{\begin{bmatrix} 1000(3-1/2 \text{ Digit}) \\ \text{Integrates Output} \end{bmatrix} \times (20\mu\text{A})}$$

A very important characteristic of the integrating capacitor is that it has low dielectric absorption to prevent roll-over or ratiometric errors. A good test for dielectric absorption is to use the capacitor with the input tied to the reference.

This ratiometric condition should be read half scale 1.0000, and any deviation is probably due to dielectric absorption. Polypropylene capacitors give undetectable errors at reasonable cost. Polystyrene and polycarbonate capacitors may be used in less critical applications.

#### Auto-Zero and Reference Capacitor

The size of the auto-zero capacitor has some influence on the noise of the system, with a larger value capacitor giving less noise. The reference capacitor should be large enough such that stray capacitance to ground from its nodes is negligible.

When gain is used in the buffer amplifier the reference capacitor should be substantially larger than the auto-zero capacitor. As a rule of thumb, the reference capacitor should be approximately the gain times the value of the auto-zero capacitor. The dielectric absorption of the reference cap and auto-zero cap are only important at power-on or when the circuit is recovering from an overload. Thus, smaller or cheaper caps can be used here if accurate readings are not required for the first few seconds of recovery.

FIGURE 6. ADDING BUFFER GAIN TO ICL8068A

#### **Reference Voltage**

The analog input required to generate a full scale output is:  $V_{IN} = 2V_{REF}$ .

The stability of the reference voltage is a major factor in the overall absolute accuracy of the converter. For this reason, it is recommended that an external high quality reference be used where ambient temperature is not controlled or where high-accuracy absolute measurements are being made.

#### Buffer Gain

At the end of the auto-zero interval, the instantaneous noise voltage on the auto-zero capacitor is stored and subtracted from the input voltage while adding to the reference voltage during the next cycle. The result of this is that the noise voltage is effectively somewhat greater than the input noise voltage of the buffer itself during integration. By introducing some voltage gain into the buffer, the effect of the auto-zero noise (referred to the input) can be reduced to the level of the inherent buffer noise. This generally occurs with a buffer gain of between 3 and 10. Further increase in buffer gain merely increases the total offset to be handled by the auto-zero loop, and reduces the available buffer and integrator swings, without improving the noise performance of the system. The circuit recommended for doing this with the ICL8068A/ICL71C03 is shown in Figure 6.

#### ICL8052A vs ICL8068A

The ICL8052A offers significantly lower input leakage currents than the ICL8068A, and may be found preferable in systems with high input impedances. However, the ICL8068A has substantially lower noise voltage, and is the device of choice for systems where noise is a limiting factor, particularly in low signal level conditions.

#### Max Clock Frequency

The maximum conversion rate of most dual-slope A/D converters is limited by frequency response of the comparator. The comparator in this circuit is no exception, even though it is entirely NPN with an open-loop, gain-

11

bandwidth product of 300MHz. The comparator output follows the integrator ramp with a 3µs delay, and at a clock frequency of 160kHz (6µs period) half of the first reference integrate clock period is lost in delay. This means that the meter reading will change from 0 to 1 with 50µV input, 1 to 2 with 150µV, 2 to 3 at 250µV, etc. This transition at midpoint is considered desirable by most users. However, if the clock frequency is increased appreciably above 160kHz, the instrument will flash "1" on noise peaks even when the input is shorted.

For many dedicated applications where the input signal is always on one polarity, the dealy of the comparator need not be limitation. Since the non-linearity and noise do not increase substantially with frequency, clock rates of up to approximately 1MHz may be used. For a fixed clock frequency, the extra count or counts caused by comparator delay will be a constant and can be subtracted out digitally.

The minimum clock frequency is established by leakage on the auto-zero and reference caps. With most devices, measurement cycles as long as 10 seconds give no measurable leakage error.

To achieve maximum rejection of 60Hz pickup, the signal integrate cycle should be a multiple of 60Hz. Oscillator frequencies of 300kHz, 200kHz, 150kHz, 120kHz, 100kHz, 40kHz,  $33^{1}/_{3}$ kHz, etc, should be selected. For 50Hz rejection, oscillator frequencies of 250kHz,  $166^{2}/_{3}$ kHz, 125kHz, 100kHz, etc. would be suitable. Note that 100kHz (2.5 readings/second) will reject both 50Hz and 60Hz.

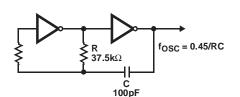

The clock used should be free from significant phase or frequency jitter. A simple two-gate oscillator and one based on CMOS 7555 timer are shown in the Applications section. The multiplexed output means that if the display takes significant current from the logic supply, the clock should have good PSRR.

## Applications

# Specific Circuits Using the 8068A/71C03 8052A/A71C03

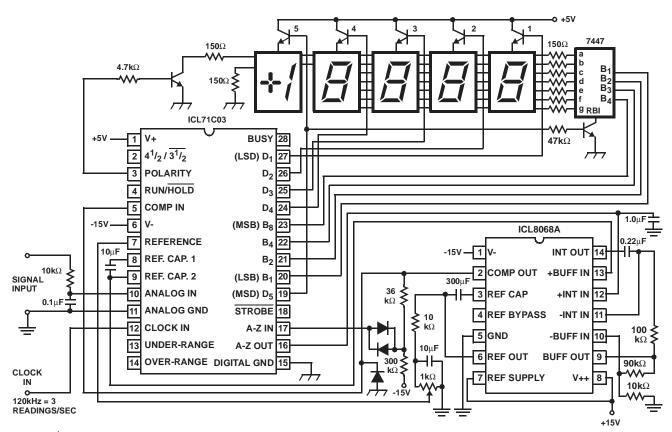

Figure 7 shows the complete circuit for a  $\pm 4^{1}/_{2}$  digit ( $\pm 200$ mV full scale) A/D converter with LED readout using the internal reference of the 8068A/52A. If an external reference is used, the reference supply (pin 7) should be connected to ground and the 300pF reference cap deleted. The circuit also shows a typical RC input filter. Depending on the application, the time-constant of this filter can be made faster, slower, or the filter deleted completely. The  $1/_{2}$  digit LED is driven from the 7-segment decoder, with a zero reading blanked by connecting a D<sub>5</sub> signal to RBI input of the decoder.

A voltage translation network is connected between the comparator output of the 8068A/52A and the auto-zero input of the 71C03. The purpose of this network is to assure that, during auto-zero, the output of the comparator is at or near the threshold of the 71C03 logic (+2.5V) while the auto-zero capacitor is being charged to V<sub>REF</sub> (+100mV for a 200mV instrument). Otherwise, even with 0V in, some reference integrate period would be required to drive the comparator output to the threshold level. This would show up as an equivalent offset error. Once the divider network has been selected, the unit-to-unit variation should contribute less than a tenth of a count error. A second feature is the back-to-back diodes, used to lower the noise. In the normal operating mode they offer a high impedance and long integrating time constant to any noise pulses charging the auto-zero cap. At startup or recovery from an overload, their impedance is low to large signals so that the cap can be charged up in one auto-zero cycle. The buffer gain does not have to be set precisely at 10 since the gain is used in both the integrate and deintegrate phase. For scale factors other then 200mV the gain of the buffer should be changed to give a ±2V buffer output. For 2.0000V full scale this means unity gain and for 20,000mV (1µV resolution) a gain of 100 is necessary. Not all 8068As can operate properly at a gain of 100 since their offset should be less than 10mV in order to accommodate the autozero circuitry. However, for devices selected with less than 10mV offset, the noise performance is reasonable with approximately 1.5µV near full scale. On all scales less than 200mV, the voltage translation network should be made adjustable as an offset trim.

The auto-zero cap should be  $1\mu$ F for all scales and the reference capacitor should be  $1\mu$ F times the gain of the buffer amplifier. At this value if the input leakages of the 8052A/8068A are equal, the droop effects will cancel giving zero offset. This is especially important at high temperature. Some typical component values are shown in Table 1. For  $3^{1}/_{2}$  digit conversion, use 12kHz clock.

| V++ = +15V, V+ = 5V, V- = -15V                                                  |

|---------------------------------------------------------------------------------|

| Clock Freq. = $120$ kHz ( $4^{1}/_{2}$ Digit) or $12$ kHz ( $3^{1}/_{2}$ Digit) |

|                      | VALUE                                                  |                                                                                                                                                                            |                                                                                                                                                                                                                                                            |  |  |  |

|----------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 20                   | 200                                                    | 2000                                                                                                                                                                       | mV                                                                                                                                                                                                                                                         |  |  |  |

| 100<br>(See<br>Note) | 10                                                     | 1                                                                                                                                                                          | V/V                                                                                                                                                                                                                                                        |  |  |  |

| 100                  | 100                                                    | 100                                                                                                                                                                        | kΩ                                                                                                                                                                                                                                                         |  |  |  |

| 0.22                 | 0.22                                                   | 0.22                                                                                                                                                                       | μF                                                                                                                                                                                                                                                         |  |  |  |

| 1.0                  | 1.0                                                    | 1.0                                                                                                                                                                        | μF                                                                                                                                                                                                                                                         |  |  |  |

| 10                   | 10                                                     | 1.0                                                                                                                                                                        | μF                                                                                                                                                                                                                                                         |  |  |  |

| 10                   | 100                                                    | 1000                                                                                                                                                                       | mV                                                                                                                                                                                                                                                         |  |  |  |

| 1                    | 10                                                     | 100                                                                                                                                                                        | μV                                                                                                                                                                                                                                                         |  |  |  |

|                      | 100<br>(See<br>Note)<br>100<br>0.22<br>1.0<br>10<br>10 | 20      200        100      10        (See      10        Note)      100        100      100        0.22      0.22        1.0      1.0        10      10        10      10 | 20      200      2000        100      10      1        (See      100      100        100      100      100        100      100      100        0.22      0.22      0.22        1.0      1.0      1.0        10      10      1.0        10      10      1.0 |  |  |  |

TABLE 1.

NOTE: Comment on offset limitations above. Buffer gain does not improve ICL8052A noise performance adequately.

## ICL8052A/ICL71C03, ICL8068A/ICL71C03

NOTE: For  $3^{1}/_{2}$  digit, tie pin 2 low and change clock to 12kHz.

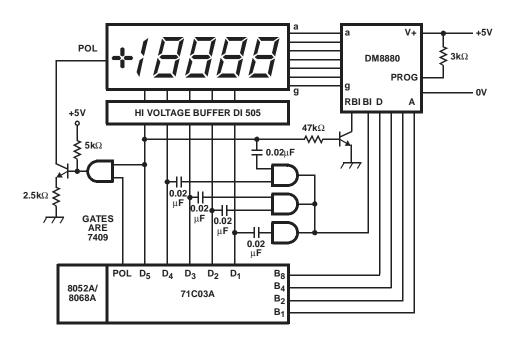

FIGURE 8. ICL8052A-8068A/71C03A PLASMA DISPLAY CIRCUIT

A suitable circuit for driving a plasma-type display is shown in Figure 8. The high voltage anode driver buffer is made by Dionics. The 3 AND gates and caps driving "BI" are needed for interdigit blanking of multiple-digit display elements, and can be omitted if not needed. The 2K and 3K resistors set the current levels in the display. A similar arrangement can be used with "Nixie®" tubes.

Nixie® is a registered trademark of Burroughs Corporation.

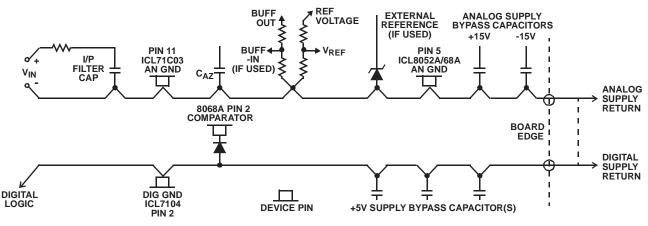

## Analog and Digital Grounds

Extreme care must be taken to avoid ground loops in the layout of 8068A or 8052A/71C03A circuits, especially in high sensitivity circuits. It is most important that return currents from digital loads are not fed into the analog ground line. Both of the above circuits have considerable current flowing in the digital ground returns from drivers, etc. A recommended connection sequence for the ground lines is shown in Figure 9.

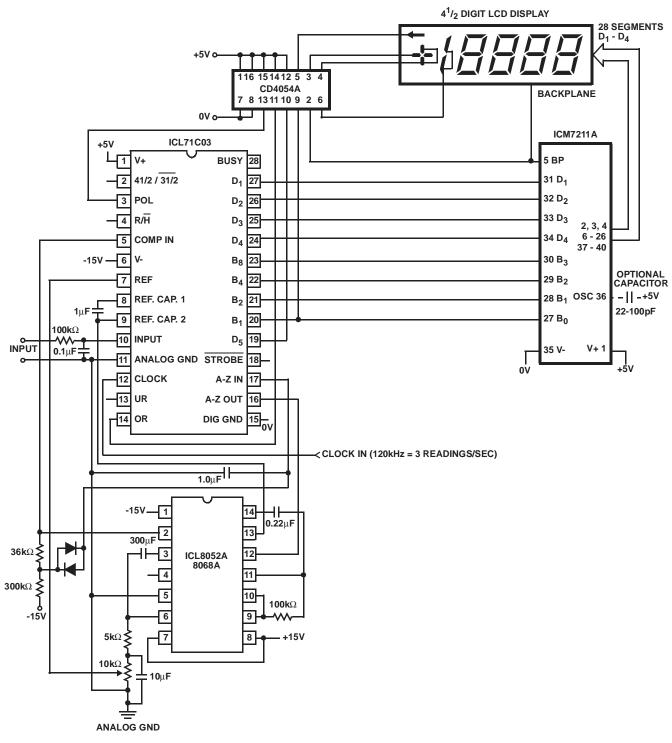

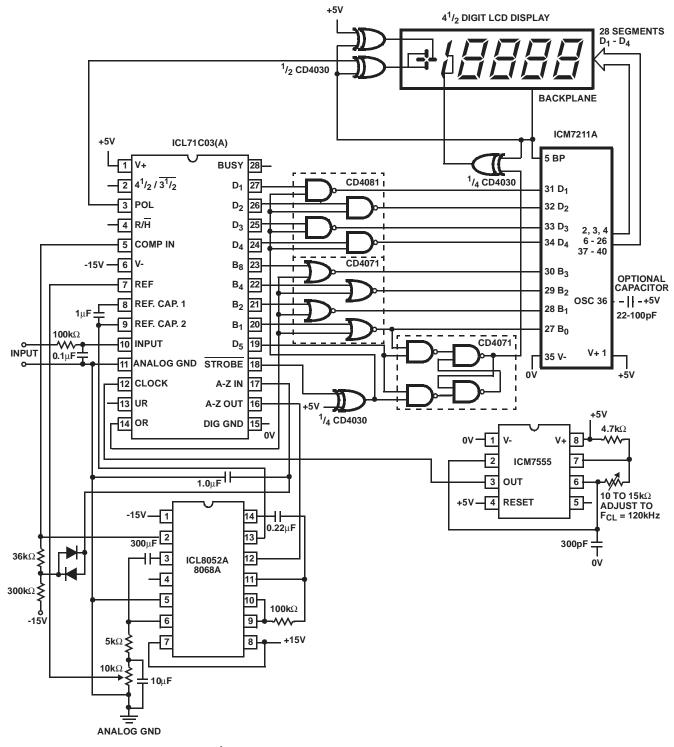

#### Other Circuits for Display Applications

Popular LCD displays can be interfaced to the Output of the ICL71C03 with suitable display drivers, such as the ICM7211A as shown in Figure 10. A standard CMOS 4000 series LCD driver circuit is used for displaying the  $1/_2$  digit, the polarity, and the "over-range" flag. A similar circuit can be used with the ICM7212A LED driver. Of course, another full

driver circuit could be ganged to the one shown if required. This would be useful if additional annunciators were needed.

Figure 10 shows the complete circuit for a  $4^{1}/2$  digit (±2.000V) A/D, again using the internal reference of the 8052A/8068A.

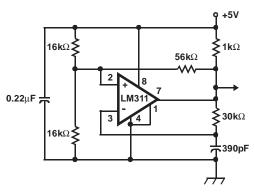

Figure 11 shows a more complicated circuit for driving LCD displays. Here the data is latched into the ICM7211 by the STROBE signal and "Overrange" is indicated by blanking the 4 digits. A clock oscillator circuit using the ICM7555 CMOS timer is shown. Some other suitable clock circuits are suggested in Figures 12 and 13. The 2-gate circuit should use CMOS gates to maintain good power supply rejection.

A problem sometimes encountered with the 8052A/68A/71C03 A/D is that of gross over-voltage applied in the input. Voltage in excess of ±2.000V may cause the integrator output to saturate. When this occurs, the integrator can no longer source (or sink) the current required to hold the summing junction (Pin 11) at the voltage stored on the auto zero capacitor. As a result, the voltage across the integrator capacitor decreases sufficiently to give a false voltage reading. This problem can also show up as large-signal instability on overrange conditions. A simple solution to this problem is to use junction FET transistors across the integrator capacitor to source (or sink) current into the summing junction and prevent the integrator amplifier from saturating, as shown in Figure 14.

FIGURE 9. GROUNDING SEQUENCE

intersil

FIGURE 10. DRIVING LCD DISPLAYS

intersil

FIGURE 11. 4<sup>1</sup>/<sub>2</sub> DIGIT LCD DPM WITH DIGIT BLANKING ON OVERRANGE

intersil

FIGURE 12. CMOS OSCILLATOR

FIGURE 13. LM311 OSCILLATOR

FIGURE 14. GROSS OVERVOLTAGE PROTECTION CIRCUIT

## Interfacing with UARTs and Microprocessors

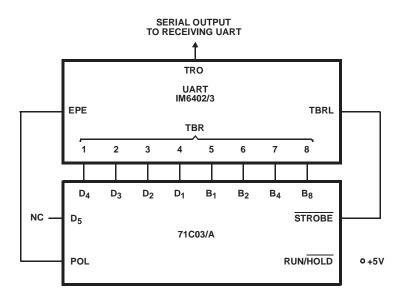

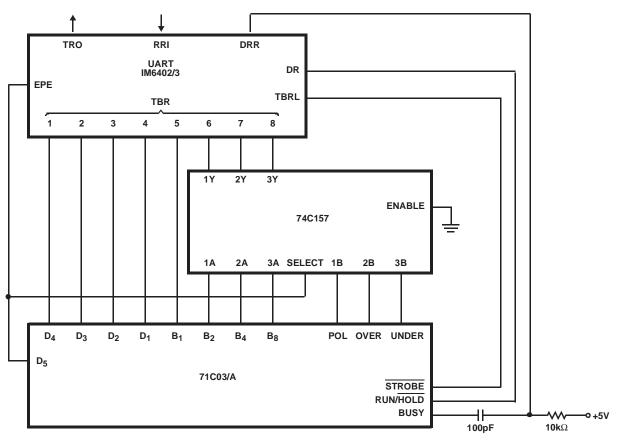

Figure 15 shows a very simple interface between a freerunning 8068A/8052A/71C03A and a UART. The five STROBE pulses start the transmission of the five data words. The digit 5 word is 0000XXXX, digit 4 is 1000XXXX, digit 3 is 0100XXXX, etc. Also, the polarity is transmitted indirectly by using it to drive the Even Parity Enable Pin (EPE). If EPE of the receiver is held low, a parity flag at the receiver can be decoded as a positive signal, no flag as negative. A complex arrangement is shown in Figure 14. Here the UART can instruct the A/D to begin a measurement sequence by a word on RRI. The Busy signal resets the Data Ready Reset (DRR). Again STROBE starts the transmit sequence. A quad 2 input multiplexer is used to superimpose polarity, over-range, and under-range onto the D<sub>5</sub> word since in this instance it is known that B<sub>2</sub> = B<sub>4</sub> = B<sub>8</sub> = 0.

For correct operation it is important that the UART clock be fast enough that each word is transmitted before the next STROBE pulse arrives. Parity is locked into the UART at load time but does not change in this connection during an output stream.

17

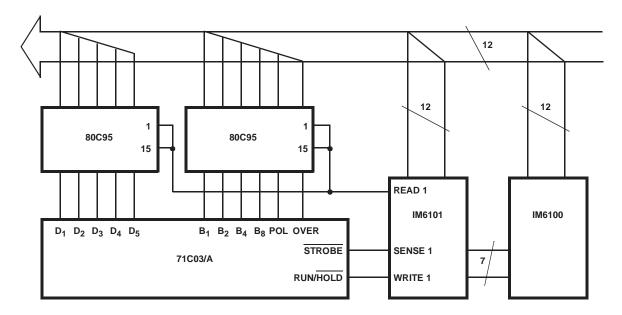

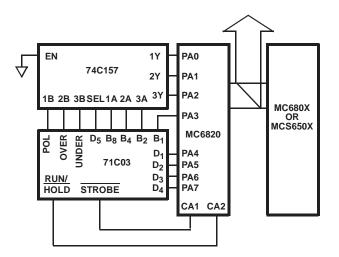

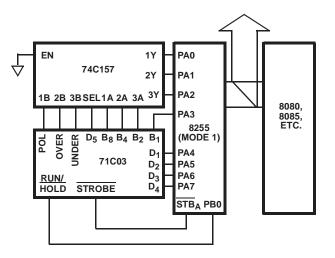

Circuits to interface the 71C03(A) directly with three popular microprocessors are shown in Figures 17, 18 and 19. The main differences in the circuits are that the IM6100 with its 12-bit word capability can accept polarity, over-range, underrange, 4 bits of BCD and 5 digits simultaneously where the 8080/8048 and the MC6800 groups with 8-bit words need to have polarity, over-range and under-range multiplexed onto the Digit 5 word - as in the UART circuits. In each case the microprocessor can instruct the A/D when to begin a measurement and when to hold this measurement.

## **Application Notes**

| NOTE # | DESCRIPTION                                                                            |  |  |

|--------|----------------------------------------------------------------------------------------|--|--|

| AN016  | "Selecting A/D Converters"                                                             |  |  |

| AN017  | "The Integrating A/D Converter"                                                        |  |  |

| AN018  | "Do's and Don'ts of Applying A/D Converters"                                           |  |  |

| AN023  | "Low Cost Digital Panel Meter Designs"                                                 |  |  |

| AN028  | "Build an Auto-Ranging DMM Using the 8052A/7103A<br>A/D Converter Pair," by Larry Goff |  |  |

FIGURE 15. SIMPLE ICL71C03/71C03A TO UART INTERFACE

FIGURE 16. COMPLEX ICL71C03/7103A TO UART INTERFACE

FIGURE 17. IM6100 TO ICL71C03A/71C03A INTERFACE

FIGURE 18. ICL71C03 TO MC6800, MCS650X INTERFACE

FIGURE 19. ICL71C03 TO MCS-48, -80, -85 INTERFACE

## ICL71C03 with ICL8052A/8068A Integrating A/D Converter Equations

The ICL71C03 does not have an internal crystal or RC oscillator. It has a clock input only.

#### Integration Period

$$\begin{split} t_{\text{INT}} &= \frac{10,000}{f_{\text{CLOCK}}}(4\text{-}1/2 \text{ Digit}) \\ t_{\text{INT}} &= \frac{1,000}{f_{\text{CLOCK}}}(3\text{-}1/2 \text{ Digit}) \end{split}$$

#### Integration Clock Period

$t_{CLOCK} = 1/f_{CLOCK}$

#### 60/50Hz Rejection Criterion

t<sub>INT</sub>/t<sub>60Hz</sub> or t<sub>INT</sub>/t<sub>50Hz</sub> = Integer

#### **Optimum Integration Current**

$I_{INT} = 20\mu A$

#### Full Scale Analog Input Voltage

$V_{INFS}$  (Typ) = 200mV to 2.0V = 2 $V_{REF}$

#### Integrate Resistor

$\mathsf{R}_{\mathsf{INT}} = \frac{(\mathsf{BufferGain}) \times \mathsf{V}_{\mathsf{INFS}}}{\mathsf{I}_{\mathsf{INT}}}$

#### Integrate Capacitor

$C_{INT} = \frac{(t_{INT})(l_{INT})}{V_{INT}}$

#### Integrator Output Voltage

$$V_{INT} = \frac{(t_{INT})(I_{INT})}{C_{INT}}$$

$V_{INT}$  (Typ) = 9V

#### Output Count

$$Count = 10,000 \times \frac{v_{IN}}{V_{REF}}$$

(4-1/2 Digit)

$$Count = 1,000 \times \frac{V_{IN}}{V_{REF}} (3-1/2 \text{ Digit})$$

NOTE: The  $4^{1}/_{2}$  digit mode's LSD will be output as a zero in the  $3^{1}/_{2}$  digit mode.

#### **Output Type:**

4 Nibbles BCD with Polarity and Over-range.

#### Power Supply: ±15V, +5V

V++ = +15V V- = -15V V+ = +5V V<sub>REF</sub> ≅ 1.75V If V<sub>REF</sub> not used, float output pin.

#### Auto Zero Capacitor Values

$0.01 \mu F < C_{AZ} < 1 \mu F$

#### Reference Capacitor Value

C<sub>REF</sub> = (Buffer Gain) x C<sub>AZ</sub>

$t_{CONV} = 4,002 * t_{CLOCK} (3^{1}/_{2} \text{ DIGIT MODE})$

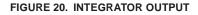

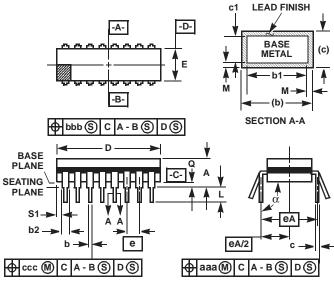

## Dual-In-Line Plastic Packages (PDIP)

#### NOTES:

- 1. Controlling Dimensions: INCH. In case of conflict between English and Metric dimensions, the inch dimensions control.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- 3. Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication No. 95.

- 4. Dimensions A, A1 and L are measured with the package seated in JEDEC seating plane gauge GS-3.

- D, D1, and E1 dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

- 6. E and e<sub>A</sub> are measured with the leads constrained to be perpendicular to datum -C-.

- 7.  $e_B$  and  $e_C$  are measured at the lead tips with the leads unconstrained.  $e_C$  must be zero or greater.

- 8. B1 maximum dimensions do not include dambar protrusions. Dambar protrusions shall not exceed 0.010 inch (0.25mm).

- 9. N is the maximum number of terminal positions.

- Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3, E42.6 will have a B1 dimension of 0.030 - 0.045 inch (0.76 -1.14mm).

#### E14.3 (JEDEC MS-001-AA ISSUE D) 14 LEAD DUAL-IN-LINE PLASTIC PACKAGE

|                | INCHES    |       | MILLIMETERS |       |       |

|----------------|-----------|-------|-------------|-------|-------|

| SYMBOL         | MIN       | MAX   | MIN         | MAX   | NOTES |

| А              | -         | 0.210 | -           | 5.33  | 4     |

| A1             | 0.015     | -     | 0.39        | -     | 4     |

| A2             | 0.115     | 0.195 | 2.93        | 4.95  | -     |

| В              | 0.014     | 0.022 | 0.356       | 0.558 | -     |

| B1             | 0.045     | 0.070 | 1.15        | 1.77  | 8     |

| С              | 0.008     | 0.014 | 0.204       | 0.355 | -     |

| D              | 0.735     | 0.775 | 18.66       | 19.68 | 5     |

| D1             | 0.005     | -     | 0.13        | -     | 5     |

| E              | 0.300     | 0.325 | 7.62        | 8.25  | 6     |

| E1             | 0.240     | 0.280 | 6.10        | 7.11  | 5     |

| е              | 0.100 BSC |       | 2.54        | BSC   | -     |

| e <sub>A</sub> | 0.300 BSC |       | 7.62 BSC    |       | 6     |

| е <sub>В</sub> | -         | 0.430 | -           | 10.92 | 7     |

| L              | 0.115     | 0.150 | 2.93        | 3.81  | 4     |

| N              | 14        |       | 14          |       | 9     |

Rev. 0 12/93

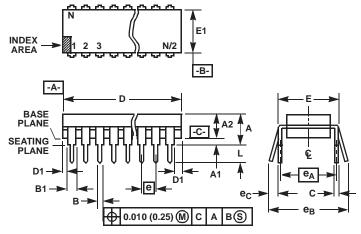

## Dual-In-Line Plastic Packages (PDIP)

#### NOTES:

- 1. Controlling Dimensions: INCH. In case of conflict between English and Metric dimensions, the inch dimensions control.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- 3. Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication No. 95.

- 4. Dimensions A, A1 and L are measured with the package seated in JEDEC seating plane gauge GS-3.

- 5. D, D1, and E1 dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

- 6. E and e<sub>A</sub> are measured with the leads constrained to be perpendicular to datum -C-.

- e<sub>B</sub> and e<sub>C</sub> are measured at the lead tips with the leads unconstrained.

e<sub>C</sub> must be zero or greater.

- 8. B1 maximum dimensions do not include dambar protrusions. Dambar protrusions shall not exceed 0.010 inch (0.25mm).

- 9. N is the maximum number of terminal positions.

- 10. Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3, E42.6 will have a B1 dimension of 0.030 0.045 inch (0.76 1.14mm).

#### E28.6 (JEDEC MS-011-AB ISSUE B) 28 LEAD DUAL-IN-LINE PLASTIC PACKAGE

|                | INCHES    |       | MILLIMETERS |       |       |

|----------------|-----------|-------|-------------|-------|-------|

| SYMBOL         | MIN       | MAX   | MIN         | MAX   | NOTES |

| A              | -         | 0.250 | -           | 6.35  | 4     |

| A1             | 0.015     | -     | 0.39        | -     | 4     |

| A2             | 0.125     | 0.195 | 3.18        | 4.95  | -     |

| В              | 0.014     | 0.022 | 0.356       | 0.558 | -     |

| B1             | 0.030     | 0.070 | 0.77        | 1.77  | 8     |

| С              | 0.008     | 0.015 | 0.204       | 0.381 | -     |

| D              | 1.380     | 1.565 | 35.1        | 39.7  | 5     |

| D1             | 0.005     | -     | 0.13        | -     | 5     |

| E              | 0.600     | 0.625 | 15.24       | 15.87 | 6     |

| E1             | 0.485     | 0.580 | 12.32       | 14.73 | 5     |

| е              | 0.100 BSC |       | 2.54 BSC    |       | -     |

| e <sub>A</sub> | 0.600 BSC |       | 15.24 BSC   |       | 6     |

| е <sub>В</sub> | -         | 0.700 | -           | 17.78 | 7     |

| L              | 0.115     | 0.200 | 2.93        | 5.08  | 4     |

| N              | 28        |       | 28          |       | 9     |

Rev. 1 12/00

## Ceramic Dual-In-Line Frit Seal Packages (CERDIP)

NOTES:

- 1. Index area: A notch or a pin one identification mark shall be located adjacent to pin one and shall be located within the shaded area shown. The manufacturer's identification shall not be used as a pin one identification mark.

- The maximum limits of lead dimensions b and c or M shall be measured at the centroid of the finished lead surfaces, when solder dip or tin plate lead finish is applied.

- 3. Dimensions b1 and c1 apply to lead base metal only. Dimension M applies to lead plating and finish thickness.

- Corner leads (1, N, N/2, and N/2+1) may be configured with a partial lead paddle. For this configuration dimension b3 replaces dimension b2.

- 5. This dimension allows for off-center lid, meniscus, and glass overrun.

- 6. Dimension Q shall be measured from the seating plane to the base plane.

- 7. Measure dimension S1 at all four corners.

- 8. N is the maximum number of terminal positions.

- 9. Dimensioning and tolerancing per ANSI Y14.5M 1982.

- 10. Controlling dimension: INCH.

| F14.3 MIL-STD-1835 GDIP1-T14 (D-1, CONFIGURATION A) |

|-----------------------------------------------------|

| 14 LEAD CERAMIC DUAL-IN-LINE FRIT SEAL PACKAGE      |

|        | INC             | INCHES MILLIMETERS |                 |                  |       |

|--------|-----------------|--------------------|-----------------|------------------|-------|

| SYMBOL | MIN             | MAX                | MIN             | MAX              | NOTES |

| А      | -               | 0.200              | -               | 5.08             | -     |

| b      | 0.014           | 0.026              | 0.36            | 0.66             | 2     |

| b1     | 0.014           | 0.023              | 0.36            | 0.58             | 3     |

| b2     | 0.045           | 0.065              | 1.14            | 1.65             | -     |

| b3     | 0.023           | 0.045              | 0.58            | 1.14             | 4     |

| С      | 0.008           | 0.018              | 0.20            | 0.46             | 2     |

| c1     | 0.008           | 0.015              | 0.20            | 0.38             | 3     |

| D      | -               | 0.785              | -               | 19.94            | 5     |

| E      | 0.220           | 0.310              | 5.59            | 7.87             | 5     |

| е      | 0.100 BSC       |                    | 2.54 BSC        |                  | -     |

| eA     | 0.300 BSC       |                    | 7.62 BSC        |                  | -     |

| eA/2   | 0.150 BSC       |                    | 3.81 BSC        |                  | -     |

| L      | 0.125           | 0.200              | 3.18            | 5.08             | -     |

| Q      | 0.015           | 0.060              | 0.38            | 1.52             | 6     |

| S1     | 0.005           | -                  | 0.13            | -                | 7     |

| α      | 90 <sup>0</sup> | 105 <sup>0</sup>   | 90 <sup>0</sup> | 105 <sup>0</sup> | -     |

| aaa    | -               | 0.015              | -               | 0.38             | -     |

| bbb    | -               | 0.030              | -               | 0.76             | -     |

| ссс    | -               | 0.010              | -               | 0.25             | -     |

| М      | -               | 0.0015             | -               | 0.038            | 2, 3  |

| Ν      | 14              |                    | 14              |                  | 8     |

Rev. 0 4/94

All Intersil products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at website <u>www.intersil.com/design/quality/iso.asp</u>.

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site www.intersil.com

## Sales Office Headquarters

NORTH AMERICA

Intersil Corporation 2401 Palm Bay Rd. Palm Bay, FL 32905 TEL: (321) 724-7000 FAX: (321) 724-7240

#### EUROPE

Intersil SA Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05 ASIA Intersil Ltd. 8F-2, 96, Sec. 1, Chien-kuo North, Taipei, Taiwan 104 Republic of China TEL: 886-2-2515-8508 FAX: 886-2-2515-8369