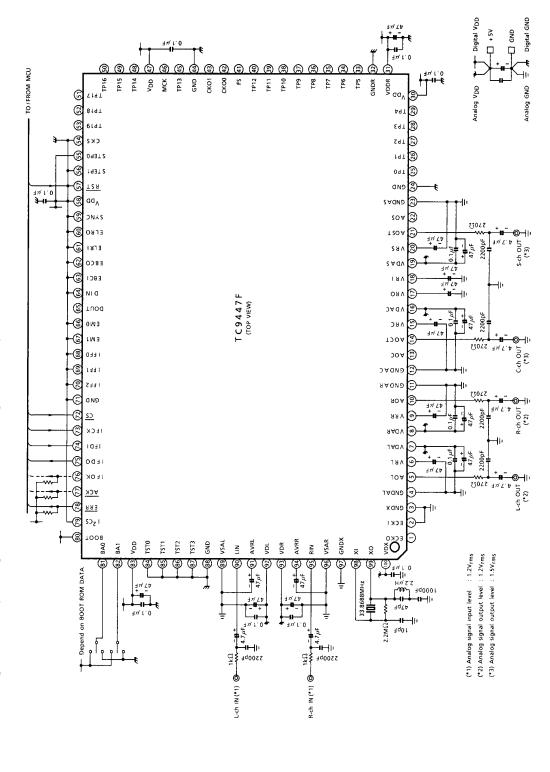

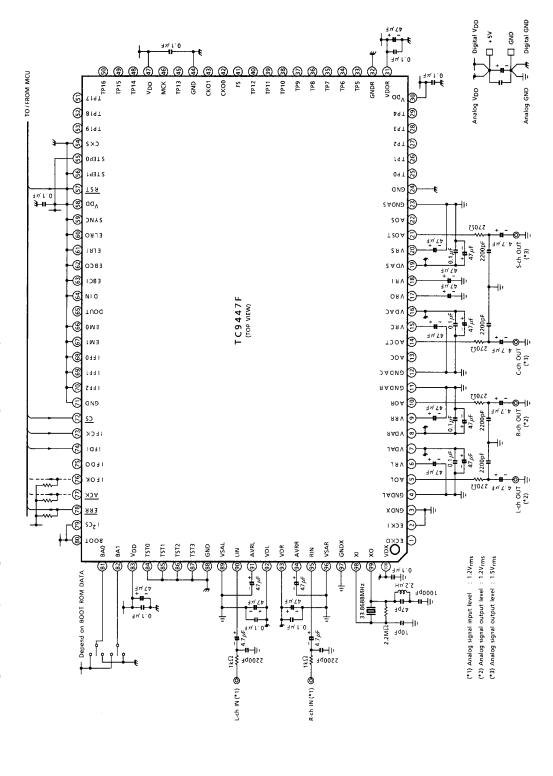

TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

### TC9447F

### Single-Chip Audio Digital Signal Processor

The TC9447F is a single-chip audio digital signal processor incorporating an AD/DA converter. The built-in program memory (ROM) can contain a range of application programs for concert hall acoustic field simulation, for digital filters such as equalizers, and for dynamic range control. In addition, the device includes 64kb of data delay RAM, making external RAM unnecessary.

### Features

- Incorporates a 1-bit  $\Sigma\Delta$ -type AD converter (two channels). THD: -82dB, S/N ratio: 95dB (typ.)

- Incorporates a 1-bit ΣΔ-type DA converter (four channels). THD: -85dB, S/N ratio: 100dB (typ.)

Weight: 1.57g (typ.)

- A ±10-dB attenuator is built into the DA converter output block (two channels only)

- Each port has a digital input/output (three lead-type)

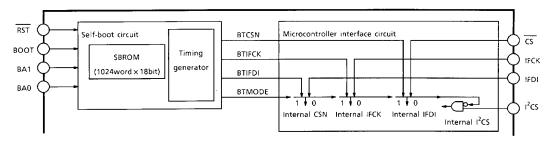

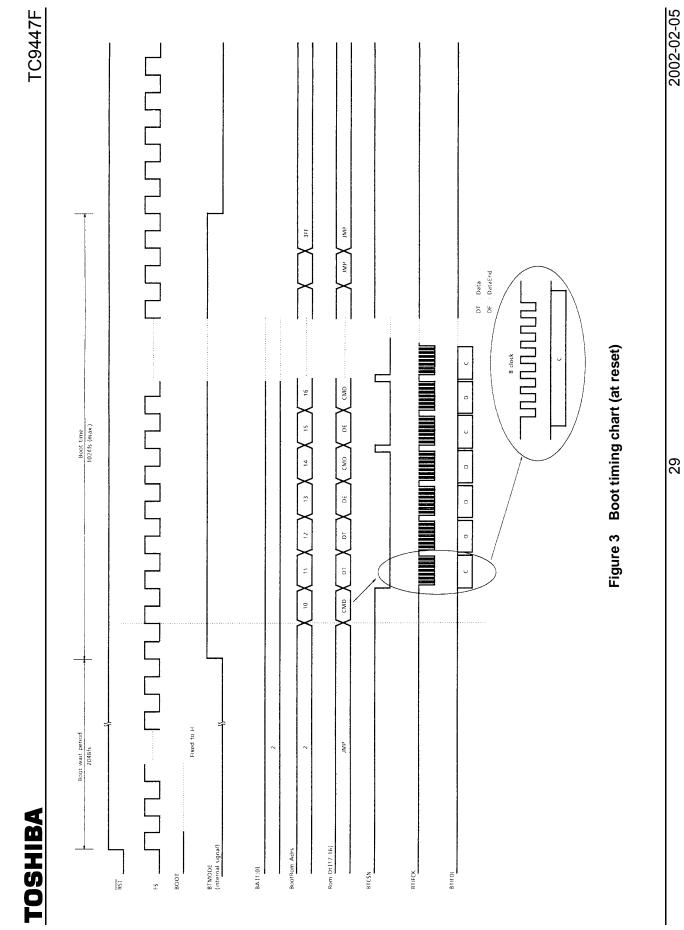

- A built-in self-boot function automatically sets the coefficients and register values at initialization. Boot ROM : 1024 words × 18 bits

- The DSP block specifications are as follows:

| Data bus             | : 24 bits                                                       |

|----------------------|-----------------------------------------------------------------|

| Multiplier/adder     | : 24 bits × 16 bits + 43 bits $\rightarrow$ 43 bits             |

| Accumulator          | : 43 bits (sign extension: 4 bits)                              |

| Program ROM          | : 1024 words $\times$ 32 bits                                   |

| Coefficient RAM      | $\therefore$ 320 words $\times$ 16 bits                         |

| Coefficient ROM      | $\therefore 256 \text{ words} \times 16 \text{ bits}$           |

| Offset RAM           | $: 64 \text{ words} \times 16 \text{ bits}$                     |

| Data RAM             | $\therefore 256 \text{ words} \times 24 \text{ bits}$           |

| Operation speed      | : 44ns (510-step (approx) operation per cycle at fs = 44.1 kHz) |

| Interface buffer RAM | I : 32 words $\times$ 16 bits                                   |

- Incorporates data delay RAM.

- Delay RAM : 4096 words × 16 bits (64 kbits)

- The microcontroller interface can be selected between Standard Transmission mode and I<sup>2</sup>C bus mode.

- CMOS silicon structure supports high speed.

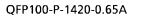

- The package is a 100-pin flat package.

TC9447F

TOSHIBA

2002-02-05

2

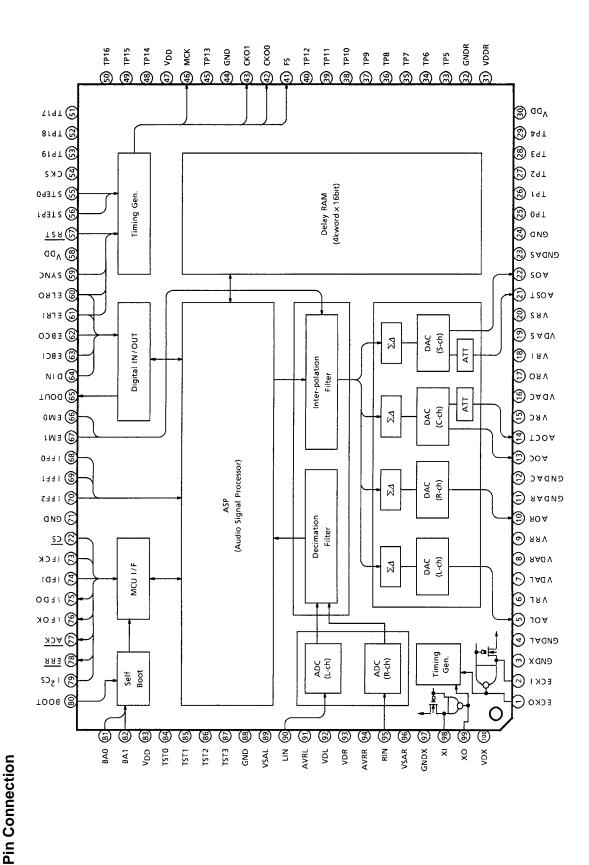

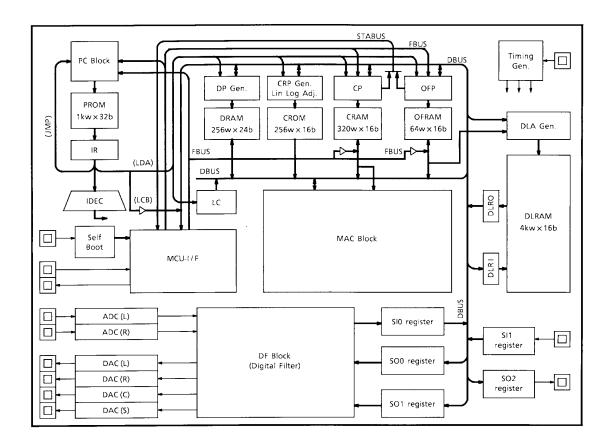

### **Block Diagram**

### **Pin Function**

| Pin<br>No. | Symbol          | I/O | Function                                                 | Remarks                                                     |

|------------|-----------------|-----|----------------------------------------------------------|-------------------------------------------------------------|

| 1          | ECKO            | 0   | Amp output pin for external clock input                  |                                                             |

| 2          | ECKI            | I   | Amp input pin for external clock input                   | Pulled-down resistor<br>(with on/off switching<br>function) |

| 3          | GNDX            | —   | Ground pin for oscillator circuit                        |                                                             |

| 4          | GNDAL           | _   | Ground pin for DAC L channel                             |                                                             |

| 5          | AOL             | 0   | DAC analog signal output pin (L channel)                 |                                                             |

| 6          | VRL             | —   | DAC reference voltage pin (L channel)                    |                                                             |

| 7          | VDAL            | —   | Power pin for DAC L channel                              |                                                             |

| 8          | VDAR            | —   | Power pin for DAC R channel                              |                                                             |

| 9          | VRR             | _   | DAC reference voltage pin (R channel)                    |                                                             |

| 10         | AOR             | 0   | DAC analog signal output pin (R channel)                 |                                                             |

| 11         | GNDAR           | _   | Ground pin for DAC R channel                             |                                                             |

| 12         | GNDAC           | _   | Ground pin for DAC C channel                             |                                                             |

| 13         | AOC             | 0   | DAC analog signal output pin (C channel)                 |                                                             |

| 14         | AOCT            | 0   | DAC analog signal output pin with attenuator (C channel) |                                                             |

| 15         | VRC             | _   | DAC reference voltage pin (C channel)                    |                                                             |

| 16         | VDAC            | _   | Power pin for DAC C channel                              |                                                             |

| 17         | VRO             | 0   | Reference voltage pin for attenuator (buffer output)     |                                                             |

| 18         | VRI             | Ι   | Reference voltage pin for attenuator (buffer input)      |                                                             |

| 19         | VDAS            | _   | Power pin for DAC S channel                              |                                                             |

| 20         | VRS             | _   | DAC reference voltage pin (S channel)                    |                                                             |

| 21         | AOST            | 0   | DAC analog signal output pin with attenuator (S channel) |                                                             |

| 22         | AOS             | 0   | DAC analog signal output pin (S channel)                 |                                                             |

| 23         | GNDAS           | _   | Ground pin for DAC S channel                             |                                                             |

| 24         | GND             | _   | Ground pin                                               |                                                             |

| 25~29      | TP0~TP4         | 0   | Test pins (leave open)                                   |                                                             |

| 30         | VDD             | _   | Power pin                                                |                                                             |

| 31         | VDDR            | _   | Power pin for DLRAM                                      |                                                             |

| 32         | GNDR            | _   | Ground pin for DLRAM                                     |                                                             |

| 33~40      | TP5~TP12        | 0   | Test pins (leave open)                                   |                                                             |

| 41         | FS              | 0   | Clock output pin (1 fs)                                  |                                                             |

| 42         | CKO0            | 0   | Clock output pin 0                                       |                                                             |

| 43         | CKO1            | 0   | Clock output pin 1                                       |                                                             |

| 44         | GND             | _   | Ground pin                                               |                                                             |

| 45         | TP13            | 0   | Test pin (leave open)                                    |                                                             |

| 46         | MCK             | 0   | MCK clock output pin (256 fs/512 fs/ (384/768 fs) )      | Push-pull output                                            |

| 47         | V <sub>DD</sub> | _   | Power pin                                                |                                                             |

| 48~53      | TP14~TP19       | 0   | Test pin (leave open)                                    |                                                             |

| 54         | CKS             | I   | Master clock switching pin                               | Schmitt input                                               |

| 55         | STEP0           | Ι   | Execution step switching pin 0                           | Schmitt input                                               |

| 56         | STEP1           | Ι   | Execution step switching pin 1                           | Schmitt input                                               |

| 57         | RST             | Ι   | Reset pin                                                | Schmitt input                                               |

| Pin<br>No. | Symbol            | I/O | Function                                                                                               | Remarks                                                     |

|------------|-------------------|-----|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 58         | V <sub>DD</sub>   | —   | Power pin                                                                                              |                                                             |

| 59         | SYNC              | Ι   | Program SYNC signal input pin                                                                          | Schmitt input                                               |

| 60         | ELRO              | Ι   | LR clock input pin for serial data output                                                              | Schmitt input                                               |

| 61         | ELRI              | Ι   | LR clock input pin for serial data input                                                               | Schmitt input                                               |

| 62         | EBCO              | I   | Bit clock input pin for serial data output                                                             | Schmitt input                                               |

| 63         | EBCI              | Ι   | Bit clock input pin for serial data input                                                              | Schmitt input                                               |

| 64         | DIN               | Ι   | Serial data input pin                                                                                  | Schmitt input                                               |

| 65         | DOUT              | 0   | Serial data output pin                                                                                 | Push-pull output                                            |

| 66         | EM0               | Ι   | De-emphasis setting pin 0                                                                              | Schmitt input                                               |

| 67         | EM1               | I   | De-emphasis setting pin 1                                                                              | Schmitt input                                               |

| 68         | IFF0              | Ι   | Interface flag pin 0                                                                                   | Schmitt input                                               |

| 69         | IFF1              | I   | Interface flag pin 1                                                                                   | Schmitt input                                               |

| 70         | IFF2              | Ι   | Interface flag pin 2                                                                                   | Schmitt input                                               |

| 71         | GND               | _   | Ground pin                                                                                             |                                                             |

| 72         | CS                | Ι   | Microcontroller interface chip select signal input pin                                                 | Schmitt input                                               |

| 73         | IFCK              | I   | Microcontroller interface data shift clock input pin                                                   | Schmitt input                                               |

| 74         | IFDI              | I/O | Microcontroller interface data input pin<br>(Data input/output pin when I <sup>2</sup> C bus selected) | Schmitt input/<br>open drain output                         |

| 75         | IFDO              | 0   | Microcontroller interface data output pin<br>(Leave open when I <sup>C</sup> C bus selected.)          | Push-pull output                                            |

| 76         | IFOK              | 0   | Microcontroller interface operation flag output pin                                                    | Open drain output                                           |

| 77         | ACK               | 0   | Microcontroller interface acknowledge output pin                                                       | Open drain output                                           |

| 78         | ERR               | 0   | Microcontroller interface error flag output pin                                                        | Open drain output                                           |

| 79         | I <sup>2</sup> CS | Ι   | Microcontroller interface I <sup>2</sup> C bus switching pin                                           |                                                             |

| 80         | BOOT              | I   | Self-boot control pin                                                                                  | Schmitt input                                               |

| 81         | BA0               | Ι   | Boot address setting pin 0                                                                             | Schmitt input                                               |

| 82         | BA1               | I   | Boot address setting pin 1                                                                             | Schmitt input                                               |

| 83         | VDD               | —   | Power pin                                                                                              |                                                             |

| 84~87      | TST0~TST3         | I   | Test pins. Use fixed to low level.                                                                     | Schmitt input                                               |

| 88         | GND               | _   | Ground pin                                                                                             |                                                             |

| 89         | VSAL              | _   | Ground pin for analog mode (ADC L channel)                                                             |                                                             |

| 90         | LIN               | I   | ADC analog signal input pin (L channel)                                                                |                                                             |

| 91         | AVRL              | _   | ADC reference voltage pin (L channel)                                                                  |                                                             |

| 92         | VDL               | _   | Power pin for analog mode (ADC L channel)                                                              |                                                             |

| 93         | VDR               | _   | Power pin for analog mode (ADC R channel)                                                              |                                                             |

| 94         | AVRR              | _   | ADC reference voltage pin (R channel)                                                                  |                                                             |

| 95         | RIN               | Ι   | ADC analog signal input pin (R channel)                                                                |                                                             |

| 96         | VSAR              | _   | Ground pin for analog mode (ADC R channel)                                                             |                                                             |

| 97         | GNDX              | _   | Ground pin for oscillator circuit                                                                      |                                                             |

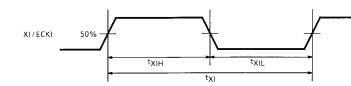

| 98         | XI                | I   | Crystal oscillator connecting pin (input)                                                              | Pulled-down resistor<br>(with on/off switching<br>function) |

| 99         | ХО                | 0   | Crystal oscillator connecting pin (output)                                                             |                                                             |

| 100        | VDX               | _   | Power pin for oscillator circuit                                                                       |                                                             |

### Operation

### 1. Pin operations

| Pin<br>No. | Symbol            |                                                                                                           |                                                                                                                                                                                                                       |                      |       | Fu         | nctio | on            |        |        |                            |   |  |  |

|------------|-------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------|------------|-------|---------------|--------|--------|----------------------------|---|--|--|

| 1          | ECKO              |                                                                                                           | upplies an external clock to ECKI (for slave operations).<br>/hen CKS pin = H, oscillation activated. When CKS = L, pulled down internally.                                                                           |                      |       |            |       |               |        |        |                            |   |  |  |

| 2          | ECKI              | When one                                                                                                  |                                                                                                                                                                                                                       |                      |       |            |       |               |        |        |                            |   |  |  |

| 3~24       | Omitted           |                                                                                                           |                                                                                                                                                                                                                       |                      |       |            |       |               |        |        |                            |   |  |  |

| 25~40      | TP [0:12]         | Test pins (                                                                                               | est pins (leave open) (TPx description is omitted.)                                                                                                                                                                   |                      |       |            |       |               |        |        |                            |   |  |  |

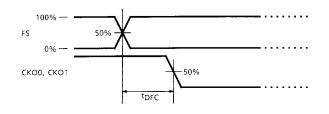

| 41         | FS                | 1 fs output                                                                                               | fs output                                                                                                                                                                                                             |                      |       |            |       |               |        |        |                            |   |  |  |

|            |                   | Timing out                                                                                                | ning output pins. The output frequency is set from the microcontroller. (CMD-40h)                                                                                                                                     |                      |       |            |       |               |        |        |                            |   |  |  |

|            |                   |                                                                                                           | KOS0                                                                                                                                                                                                                  | ско                  | 0     |            |       |               | KOS    | 1      | СКО1                       |   |  |  |

|            |                   | 2                                                                                                         | 1 0                                                                                                                                                                                                                   |                      |       |            | -     | 2             | 2 1    |        |                            |   |  |  |

|            |                   |                                                                                                           | 0 Fixed to L (initial value)<br>1 fs2                                                                                                                                                                                 |                      |       |            |       |               |        | 0      | Fixed to L (initial value) | _ |  |  |

|            |                   | 0 -                                                                                                       | 1                                                                                                                                                                                                                     |                      |       | -          | 0     |               | 1      | fs2    | _                          |   |  |  |

| 42, 43     | CKO [1:0] 1 0 fs4 |                                                                                                           |                                                                                                                                                                                                                       |                      |       |            |       |               | 1      | 0      | fs4                        |   |  |  |

| , -        |                   |                                                                                                           | 1 fs8                                                                                                                                                                                                                 |                      |       |            |       |               |        | 1      | fs8                        |   |  |  |

|            |                   | 0 fs16                                                                                                    |                                                                                                                                                                                                                       |                      |       |            |       |               | 0      | 0      | fs16                       |   |  |  |

|            |                   | 1                                                                                                         | 1                                                                                                                                                                                                                     | fs32                 |       |            | 1 -   |               | 1      | fs32   |                            |   |  |  |

|            |                   |                                                                                                           | 1 0                                                                                                                                                                                                                   | fs64                 |       |            |       |               | 1      | 0      | fs64                       |   |  |  |

|            |                   |                                                                                                           | 1                                                                                                                                                                                                                     | fs128                |       |            |       |               | 1      | 1      | 1/2 XI or 1/2 ECKI         |   |  |  |

| 46         | МСК               | MCKE<br>0                                                                                                 | Fixed to I                                                                                                                                                                                                            | MCK                  |       | MCKE<br>0  | TEP1  |               |        | MCK    | -                          |   |  |  |

|            |                   | MCKE                                                                                                      |                                                                                                                                                                                                                       | MCK                  |       | MCKE       | S     | TEP1          | МСК    |        |                            |   |  |  |

| 40         | MCK               |                                                                                                           |                                                                                                                                                                                                                       |                      |       | 0          | dor   |               |        | -      |                            |   |  |  |

|            |                   | 1                                                                                                         | Output va                                                                                                                                                                                                             | alid (initial value) |       | 1          |       | 0             | Sou    | rce os | cillation (XI/XO or ECKI)  | _ |  |  |

|            |                   |                                                                                                           |                                                                                                                                                                                                                       |                      |       |            |       | 1 For testing |        |        |                            |   |  |  |

|            |                   | Source osc                                                                                                | cillation sel                                                                                                                                                                                                         | ector pin            | 1     |            |       |               |        |        |                            |   |  |  |

| -          | 0140              | CKS                                                                                                       | Sour                                                                                                                                                                                                                  | ce Oscillation       |       |            |       |               |        |        |                            |   |  |  |

| 54         | CKS               | 0                                                                                                         | XI/XO pir                                                                                                                                                                                                             | ı                    |       |            |       |               |        |        |                            |   |  |  |

|            |                   | 1                                                                                                         | ECKI/EC                                                                                                                                                                                                               | KO pin               |       |            |       |               |        |        |                            |   |  |  |

|            |                   |                                                                                                           |                                                                                                                                                                                                                       |                      | -     |            |       |               |        |        |                            |   |  |  |

|            |                   | Source os                                                                                                 | cillation free                                                                                                                                                                                                        | quency/ASP opera     | tion  | speed s    | witch | ning pin      | s      |        |                            |   |  |  |

|            |                   | STEP1                                                                                                     | STEP0                                                                                                                                                                                                                 | Source Oscilla       | atior | n Frequer  | ю     |               | No.    | of AS  | SP Operation Steps         |   |  |  |

| 55, 56     | STEP [1:0]        | 0                                                                                                         | 0                                                                                                                                                                                                                     | 51                   | 2 fs  |            |       |               |        |        | 340/fs                     |   |  |  |

| 00, 00     |                   | U                                                                                                         | 1                                                                                                                                                                                                                     | 76                   | 8 fs  |            |       |               |        |        | 510/fs                     |   |  |  |

|            |                   | 1                                                                                                         | *                                                                                                                                                                                                                     |                      |       |            | F     | or testin     | g      |        |                            |   |  |  |

|            |                   | *: don'i                                                                                                  | t care                                                                                                                                                                                                                |                      |       |            |       |               |        |        |                            |   |  |  |

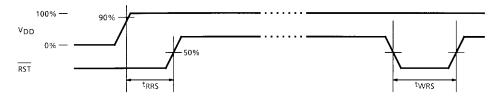

| 57         | RST               |                                                                                                           |                                                                                                                                                                                                                       | lization)            |       |            |       |               |        |        |                            |   |  |  |

| 59         | SYNC              |                                                                                                           | Reset input (L at initialization) Program operation SYNC signal input pin. Valid when program is executing a slave operation.                                                                                         |                      |       |            |       |               |        |        |                            |   |  |  |

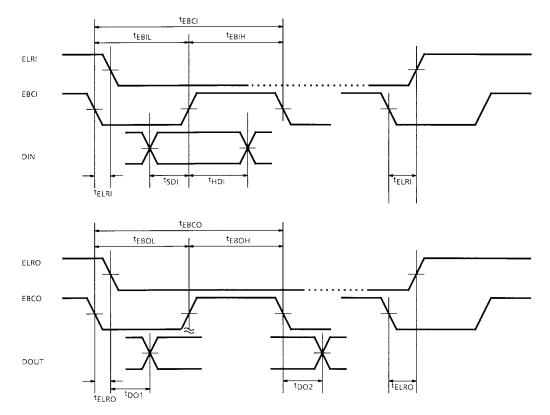

| 60         | ELRO              | LR clock signal input pin for serial output data. Valid when serial data are output in a slave operation. |                                                                                                                                                                                                                       |                      |       |            |       |               |        |        |                            |   |  |  |

| 61         | ELRI              | LR clock signal input pin for serial input data. Valid when serial data are input in a slave operation.   |                                                                                                                                                                                                                       |                      |       |            |       |               |        |        |                            |   |  |  |

| 62         | EBCO              |                                                                                                           | EX clock signal input pin for serial input data. Valid when serial data are input in a slave operation.<br>Bit clock signal input pin for serial output data. Valid when serial data are output in a slave operation. |                      |       |            |       |               |        |        |                            |   |  |  |

|            |                   |                                                                                                           | • • •                                                                                                                                                                                                                 |                      |       |            |       |               |        |        |                            |   |  |  |

| 63         | EBCI              | DIL CIUCK SI                                                                                              | ignal input                                                                                                                                                                                                           | on to senal input    | udlâ  | a. valio W | пеп   | senal 0       | ลเส สี | e inpl | ut in a slave operation.   |   |  |  |

| Pin<br>No. | Symbol                         |                                                         |                                                                                                                                                                                              |                          | Function                                                                   | n                                         |  |  |  |  |  |  |  |  |

|------------|--------------------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------------------------------|-------------------------------------------|--|--|--|--|--|--|--|--|

| 64         | DIN                            | Sei                                                     | rial input data signal input pin. Normally connected to internal register SI2 in ASP block.<br>rial output data signal output pin. Normally connected to internal register SO2 in ASP block. |                          |                                                                            |                                           |  |  |  |  |  |  |  |  |

| 65         | DOUT                           | Sei                                                     | rial output data signal output pin. Normally connected to internal register SO2 in ASP block.                                                                                                |                          |                                                                            |                                           |  |  |  |  |  |  |  |  |

|            |                                | De                                                      | -emphas                                                                                                                                                                                      | is contro                | pins                                                                       |                                           |  |  |  |  |  |  |  |  |

|            |                                |                                                         | EM1                                                                                                                                                                                          | EM0                      | De-Emphasis Settings                                                       |                                           |  |  |  |  |  |  |  |  |

|            |                                |                                                         | 0                                                                                                                                                                                            | 0                        | De-emphasis off                                                            | -                                         |  |  |  |  |  |  |  |  |

| 66, 67     | EM [1:0]                       | 1 [1:0]                                                 | 0                                                                                                                                                                                            | 1                        | For fs = 48 kHz                                                            |                                           |  |  |  |  |  |  |  |  |

|            |                                |                                                         | 1                                                                                                                                                                                            | 0                        | For fs = 44.1 kHz                                                          |                                           |  |  |  |  |  |  |  |  |

|            |                                |                                                         | 1                                                                                                                                                                                            | 1                        | For fs = 32 kHz                                                            |                                           |  |  |  |  |  |  |  |  |

|            |                                |                                                         |                                                                                                                                                                                              |                          |                                                                            |                                           |  |  |  |  |  |  |  |  |

| 68~70      | IFF [2:0]                      | IFF<br>The                                              | control i<br>e prograr                                                                                                                                                                       | nput pins<br>n uses th   | s. This functions the same as the micro<br>le latest changes to the flags. | rocontroller IFF [2:0] setting.           |  |  |  |  |  |  |  |  |

| 72         | CS                             | Mic                                                     | rocontro                                                                                                                                                                                     | ller interf              | ace pins                                                                   |                                           |  |  |  |  |  |  |  |  |

| 73         | IFCK                           |                                                         |                                                                                                                                                                                              | Stand                    | lard Transmission Mode ( $I^2$ CS = L)                                     | $I^2C$ Mode ( $I^2CS = H$ )               |  |  |  |  |  |  |  |  |

| 74         | IFDI                           |                                                         | I <sup>2</sup> CS                                                                                                                                                                            | Transmi                  | t/receive mode switching (Standard T                                       | ransmission mode/l <sup>2</sup> C mode)   |  |  |  |  |  |  |  |  |

| 75         | IFDO                           | -                                                       |                                                                                                                                                                                              |                          | ect (Control required)                                                     | Chip select (Can be fixed to L)           |  |  |  |  |  |  |  |  |

| 76         | IFOK                           | -                                                       | IFCK                                                                                                                                                                                         | •                        | t/receive clock                                                            |                                           |  |  |  |  |  |  |  |  |

| 77         | ACK                            |                                                         | IFDI                                                                                                                                                                                         | MCU da                   |                                                                            | MCU data input/output                     |  |  |  |  |  |  |  |  |

| 78         | ERR                            |                                                         | IFDO                                                                                                                                                                                         |                          | data output                                                                | Fixed to L output                         |  |  |  |  |  |  |  |  |

|            |                                | -                                                       | ACK                                                                                                                                                                                          |                          | edge signal output                                                         | Fixed to HZ                               |  |  |  |  |  |  |  |  |

| 79         | I <sup>2</sup> CS              | ·                                                       | ERR                                                                                                                                                                                          | Error flag signal output |                                                                            |                                           |  |  |  |  |  |  |  |  |

| 13         | 1.00                           | IFOK Internal operation confirmation flag signal output |                                                                                                                                                                                              |                          |                                                                            |                                           |  |  |  |  |  |  |  |  |

|            |                                | For                                                     | details,                                                                                                                                                                                     | see 2, m                 | icrocontroller interface below.                                            |                                           |  |  |  |  |  |  |  |  |

|            |                                | Sel                                                     | f-boot se                                                                                                                                                                                    | elect pin                |                                                                            |                                           |  |  |  |  |  |  |  |  |

|            |                                |                                                         | BOOT                                                                                                                                                                                         |                          | Operation                                                                  | 7                                         |  |  |  |  |  |  |  |  |

| 80         | BOOT                           |                                                         | 0                                                                                                                                                                                            | Does n                   | ot boot at reset                                                           | —                                         |  |  |  |  |  |  |  |  |

|            |                                |                                                         | 1                                                                                                                                                                                            | Boot at                  |                                                                            | -                                         |  |  |  |  |  |  |  |  |

|            |                                |                                                         |                                                                                                                                                                                              | 2001 4                   |                                                                            |                                           |  |  |  |  |  |  |  |  |

|            |                                | Sel                                                     | f-boot st                                                                                                                                                                                    | art addre                | ss pins (at reset)                                                         |                                           |  |  |  |  |  |  |  |  |

|            |                                |                                                         | BA1                                                                                                                                                                                          | BA0                      | Start Address                                                              |                                           |  |  |  |  |  |  |  |  |

|            | <b>D</b> / <b>I</b> / <b>I</b> |                                                         | 0                                                                                                                                                                                            | 0                        | 000h                                                                       | 7                                         |  |  |  |  |  |  |  |  |

| 81, 82     | BA [1:0]                       |                                                         | 0                                                                                                                                                                                            | 1                        | 001h                                                                       |                                           |  |  |  |  |  |  |  |  |

|            |                                |                                                         | 1                                                                                                                                                                                            | 0                        | 002h                                                                       |                                           |  |  |  |  |  |  |  |  |

|            |                                |                                                         | I                                                                                                                                                                                            | 1                        | 003h                                                                       |                                           |  |  |  |  |  |  |  |  |

| 84~87      | TST [3:0]                      | Pin                                                     | Pins for inputting test settings. Use fixed to L.                                                                                                                                            |                          |                                                                            |                                           |  |  |  |  |  |  |  |  |

| 88~97      | Omitted                        |                                                         | _                                                                                                                                                                                            |                          |                                                                            |                                           |  |  |  |  |  |  |  |  |

| 98         | XI                             | Со                                                      | Connect the crystal oscillator (master mode).                                                                                                                                                |                          |                                                                            |                                           |  |  |  |  |  |  |  |  |

| 99         | ХО                             |                                                         |                                                                                                                                                                                              |                          |                                                                            | s down XI/XO using the internal resistor. |  |  |  |  |  |  |  |  |

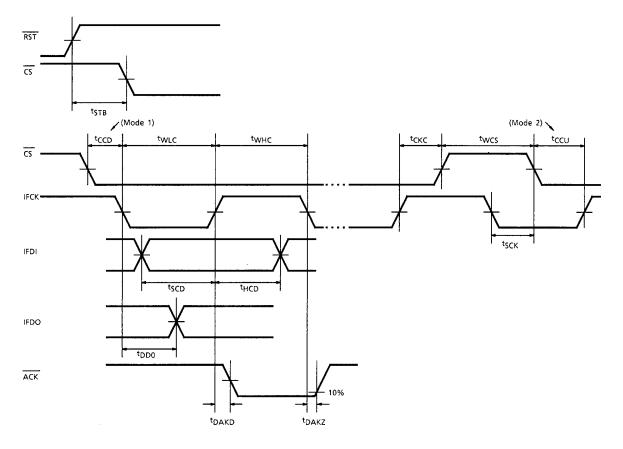

### 2. Microcontroller interface

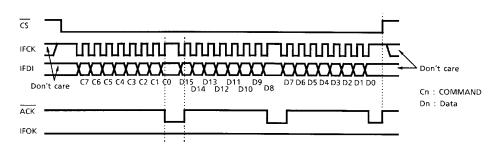

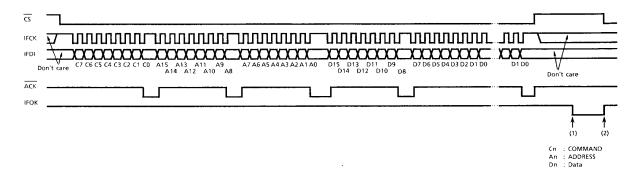

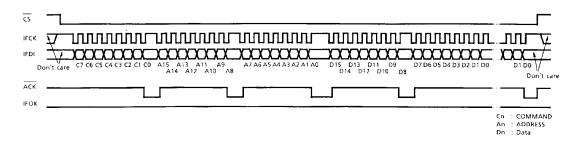

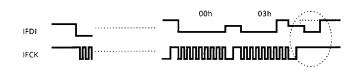

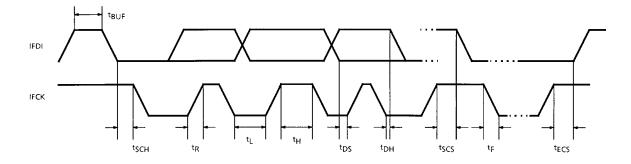

(1)Standard transmission mode 1

> When  $I^2CS = L$ , data can be transmitted or received in Standard Transmission mode. When the  $\overline{\text{CS}}$  signal is Low, control from the microcontroller is enabled. The IFCK signal is the transmit/receive clock. The IFDI signal is the data. The TC9447F loads the IFDI data on the IFCK signal rising edge. When  $\overline{CS} = H$ , the IFCK and IFDI signals are don't care.

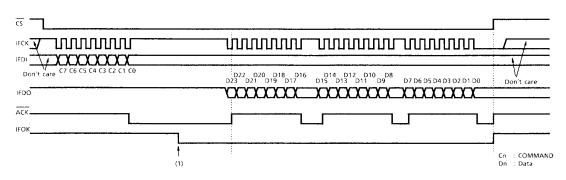

(1-1)Setting registers

The registers are set by command data using the IFDI signal. The first byte is a command, which differs for each register. The data sent after that are fixed to two bytes. Both command and data are sent starting from the MSB.

The  $\overline{\text{ACK}}$  signal is the acknowledge signal that the TC9447F returns to the microcontroller. Because the ACK signal is open drain output, it must be pulled up outside the pin. Data are loaded on the rising edge of the IFCK signal.

Note that commands or data that must be switched on the SYNC signal, such as the RUN command or the IFF flag, must be synchronized with the SYNC signal and loaded on that signal.

cs արուսու հայուսուսու ூ **IFCK** ¥ V IF DI \* \* \* \* \* \* \* \* \* C7 C6 C5 C4 C3 C2 C1 C0 A15 A13 A11 A9 A14 A12 A10 A8 A7 A6 A5 A4 A3 A2 A1 A0 D15 D13 D11 D9 D14 D12 D10 D7 D6 D5 D4 D3 D2 D1 D 0.010 Dor , D8 Don't care ACK Г IFOK Cn An Dn COMMAND ADDRESS

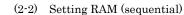

The RAMs are set by command data using the IFDI signal. The first byte is a command, which differs for each RAM. The next two bytes contain the start address for the RAM written. The length of the data field following the RAM address bytes is  $2 \times n$  bytes. The address is automatically incremented by 1.

Setting RAM (sequential)

(1-2)

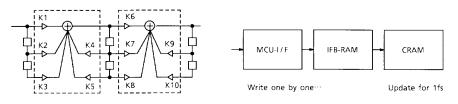

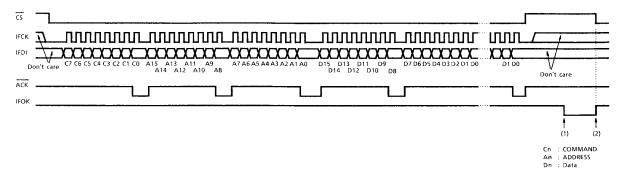

(1-3) Setting RAM (ACMP mode)

In ACMP mode, the TC9447F does not write data directly to coefficient RAM (CRAM) or offset RAM (OFRAM). In this mode, data must first be written to the interface buffer RAM (IFB-RAM). Then, all the data are updated together in a period of 1 fs.

For example, if a signal flow filter is designed as in the following diagram, unless the K1 to K5 data are batch-updated, the circuit may resonate. The same applies to the K6 to K10 data.

Using ACMP mode can reduce the noise caused by updating coefficients while the TC9447F is operating. This mode can suppress noise in almost all cases.

IFB-RAM is 32-word memory. Therefore, data can be updated at one time in units of up to 32 words.

The format of IFB-RAM is similar to the format of the RAM in 1-2 above. The length of the data field is  $2 \times n$  bytes, where  $n \le 32$ .

In ACMP mode, the IFOK pin outputs an ACMP operation end flag.

When ACMP operations complete, the flag is set to Low (1) and is initialized at the next low chip select  $\overline{CS}$  signal (2).

### <u>TOSHIBA</u>

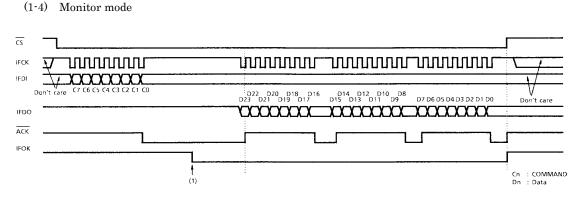

Monitor mode is used to monitor the data bus or pointers.

There are two further modes: a mode where the data bus or pointer (s) is monitored at a preset program counter (PC) and a mode where a loop counter (LC) is added to monitor conditions in addition to the PC. After the command is issued, when the TC9447F loads data to the IFDO register (IFDOR), the IFOK pin signal is set to Low (see (1) above).

Next, when the IFCK signal is sent, the data are output on the IFCK signal falling edge starting from the MSB. The data length is at its maximum (24 bits or three bytes) during monitoring of the data bus. In cases where transfer must be interrupted, such as where only eight or 16 bits of the MSB side are required, monitoring can be interrupted at any time by setting the  $\overline{CS}$  signal to High. When the  $\overline{CS}$  signal goes High, the IFOK signal also goes High. When  $\overline{CS} = H$ , all monitor circuits are initialized. (2) Standard transmission mode 2

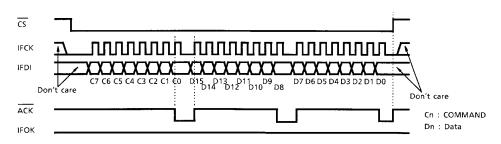

When  $I^2CS = L$ , data can be transmitted or received in Standard Transmission mode. When the  $\overline{CS}$  signal is Low, control from the microcontroller is enabled. The IFCK signal is the transmit/receive clock. The IFDI signal is the data. The TC9447F loads the IFDI data on the IFCK signal rising edge. When  $\overline{CS} = H$ , the IFCK and IFDI signals are don't care.

(2-1) Setting registers

The registers are set by command data using the IFDI signal. The first byte is a command, which differs for each register. The data sent after that are fixed to two bytes. Both command and data are sent starting from the MSB.

The  $\overline{ACK}$  signal is the acknowledge signal that the TC9447F returns to the microcontroller. As the  $\overline{ACK}$  signal is open drain output, it must be pulled up outside the pin. The data are loaded on the rising edge of the IFCK signal.

Note that commands or data that must be switched on the SYNC signal, such as the RUN command or the IFF flag, must be synchronized with the SYNC signal and loaded on that signal.

The RAMs are set by command data using the IFDI signal. The first byte is a command, which differs for each RAM. The next two bytes contain the start address for the RAM written. The length of the data field following the RAM address bytes is  $2 \times n$  bytes. The address is automatically incremented by 1.

(2-3) Setting RAM (ACMP mode)

In ACMP mode, the TC9447F does not write data directly to coefficient RAM (CRAM) or offset RAM (OFRAM). In this mode, data must first be written to the interface buffer RAM (IFB-RAM). Then, all the data are updated together in a period of 1 fs.

For example, if a signal flow filter is designed as in the following diagram, unless the K1 to K5 data are batch-updated, the circuit may resonate. The same applies to the K6 to K10 data. Using ACMP mode can reduce the noise caused by updating coefficients while the TC9447F is operating. This mode can suppress noise in almost all cases.

IFB-RAM is 32-word memory. Therefore, data can be updated at one time in units of up to 32 words. The format of IFB-RAM is similar to the format of the RAM in 2-2 above. The length of the data field is  $2 \times n$  bytes, where  $n \leq 32$ .

In ACMP mode, the IFOK pin outputs an ACMP operation end flag.

When ACMP operations complete, the flag is set to Low (1) and is initialized at the next low chip select  $\overline{CS}$  signal (2).

(2-4) Monitor mode

Monitor mode is used to monitor the data bus or pointers.

There are two further modes: a mode where the data bus or pointer (s) is monitored at a preset program counter (PC) and a mode where a loop counter (LC) is added to monitor conditions in addition to the PC. After the command is issued, when the TC9447F loads data to the IFDO register (IFDOR), the IFOK pin signal is set to Low (see (1) above).

Next, when the IFCK signal is sent, data are output on the IFCK signal falling edge from the MSB first. The data length is at its maximum (24 bits or three bytes) during monitoring of the data bus. In cases where transfer must be interrupted, such as where only eight or 16 bits of the MSB side are required, monitoring can be interrupted at any time by setting the  $\overline{CS}$  signal to High. When the  $\overline{CS}$  signal goes High, the IFOK signal also goes High. When  $\overline{CS} = H$ , all monitor circuits are initialized.

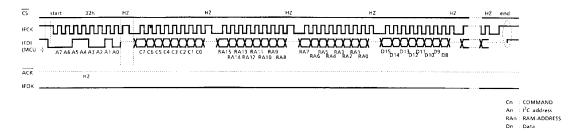

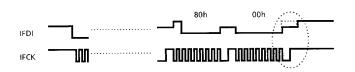

(3)I<sup>2</sup>C bus mode When  $I^2CS = H$ , data can be transmitted or received in Standard Transmission mode. When the  $\overline{CS}$  signal is Low, control from the microcontroller is enabled. In I<sup>2</sup>C mode, the  $\overline{CS}$  signal can be used fixed to L. The IFCK signal is the transmit/receive clock. The IFDI signal is the data. The TC9447F loads the IFDI data on the IFCK signal rising edge. When CS = H, the IFCK and IFDI signals are don't care. (3-1)Setting registers cs start 32h H7 НŻ нz mmm IFCK IED (MCU-D7 D6 D5 D4 D3 D2 D1 D0 4 A3 A2 A1 A0 A6 A5 D8 ACK нz IFOK

> An : I<sup>2</sup>C address Cn : COMMAND Dn : Data

The registers are set by command data using the IFDI signal. The first byte after the  $I^2C$  address (32h) is a command, which differs for each register. The data sent after that are fixed to two bytes. Both command and data are sent starting from the MSB in  $I^2C$  format.

The  $\overline{\text{ACK}}$  pin cannot be used in I<sup>2</sup>C format. However, the acknowledge signal can be read by using data signals in I<sup>2</sup>C format. The data are loaded internally every two bytes. Note that commands or data that must be switched on the SYNC signal, such as the RUN command or the IFF flag, must be synchronized with the SYNC signal and loaded on that signal.

### (3-2) Setting RAM (sequential)

The RAMs are set by command data using the IFDI signal.

The first byte after the I<sup>2</sup>C address (32h) is a command, which differs for each RAM. The next two bytes contain the start address for the RAM to be written to. The length of the data field following the RAM address bytes is  $2 \times n$  bytes. The address is automatically incremented by 1.

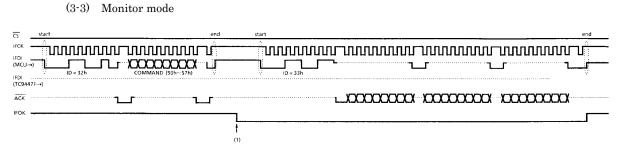

Monitor mode is used to monitor the data bus or pointers.

There are two further modes: a mode where the data bus or pointer (s) is monitored at a preset program counter (PC) and a mode where a loop counter (LC) is added to monitor conditions in addition to the PC.

First, issue the monitoring command, which has no data.

When the TC9447F loads data to the IFDO register (IFDOR), the IFOK pin signal is set to Low (see (1) above).

Next, the I<sup>2</sup>C read command (ID = 33h) is issued, then when the IFCK signal is sent, the data are output on the IFCK signal falling edge starting from the MSB. The data length is at its maximum (24 bits or three bytes) during monitoring of the data bus. In cases where transfer must be interrupted, such as where only eight or 16 bits of the MSB side are required, monitoring can be interrupted by sending the I<sup>2</sup>C end condition (set data level to H while the clock = H). After issuing a monitor command (50h~56h), be sure to perform a continuous read operation by issuing the I<sup>2</sup>C read command (ID = 33h).

(3-4) MCU does not write data by ACMP mode at  $I^2C$  bus controlling.

### (4) IFOK pin description

The IFOK signal has the following three functions.

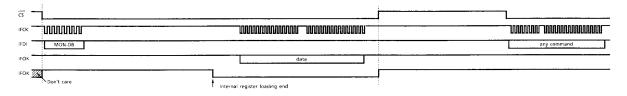

(4-1) ACMP mode end flag output

After the completion of a RAM data update with CRAM-ACMP (CMD: 47h) or OFRAM-ACMP (CMD: 49h), the IFOK pin goes Low. Setting the  $\overline{\text{CS}}$  signal to Low changes the IFOK signal from Low to High.

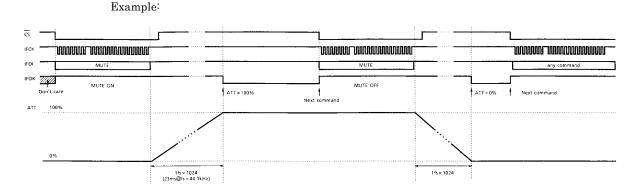

Example:

| cs   | <b>-</b>   | J               | L            |

|------|------------|-----------------|--------------|

| IFCK |            |                 |              |

| IFDI | CRAM-ACMP  | ſ               | any command  |

| IFOK | Don't care | Update complete | Next command |

(4-2) Loading end flag output in Monitor mode

When monitoring using the bus monitor command (CMD: 50h), for example, after data are loaded to the internal register under the specified conditions, the IFOK signal goes Low. In monitor mode, when the  $\overline{\text{CS}}$  signal goes High, the IFOK signal also goes High.

Example:

(4-3) Mute end flag output for digital filter (DF) block

When using a command to control the DF block mute on/off (CMD: 36h, bit 5), the mute end flag is output from the IFOK pin after the mute operation completes.

Note 1: At power on, the IFOK pin output is undefined. When the  $\overline{CS}$  signal goes Low, the IFOK signal goes High.

### 3. Control commands

The following table lists the control commands that can be used from the microcontroller.

(1) Control commands

| Command    | Code | R/W | Description                 | RAM<br>Sequential | Transfer Sync With/Async to<br>Sync Signal |  |  |  |  |  |

|------------|------|-----|-----------------------------|-------------------|--------------------------------------------|--|--|--|--|--|

| TIMING     | 40h  |     | Timing — Async              |                   |                                            |  |  |  |  |  |

| BOOT       | 41h  |     | Self-boot ROM start address | -                 | Async                                      |  |  |  |  |  |

| DAC        | 42h  |     | DAC output attenuator       | -                 | Async                                      |  |  |  |  |  |

| SIO        | 43h  |     | SIO setting                 | -                 | Async                                      |  |  |  |  |  |

| RUN-MUTE   | 44h  |     | Program execution, mute     | -                 | Sync (Note 2)                              |  |  |  |  |  |

| MSEQ       | 45h  |     | Sequential RAM              |                   | Sync (RUN)/Async (STOP)                    |  |  |  |  |  |

| CRAM       | 46h  |     | CRAM                        |                   | Sync (RUN)/Async (STOP)                    |  |  |  |  |  |

| CRAM-ACMP  | 47h  | w   | CRAM (ACMP mode)            | Enable            | Async                                      |  |  |  |  |  |

| OFRAM      | 48h  | vv  | OFRAM                       |                   | Sync (RUN)/Async (STOP)                    |  |  |  |  |  |

| OFRAM-ACMP | 49h  |     | OFRAM (ACMP mode)           |                   | Async                                      |  |  |  |  |  |

| IFF        | 4Ah  |     | Interface flag (IFF)        | _                 | Sync (Note 2)                              |  |  |  |  |  |

| MONI-PC    | 4Bh  |     | Monitor (PC conditions)     | _                 | Async                                      |  |  |  |  |  |

| MONI-LC    | 4Ch  |     | Monitor (LC conditions)     | _                 | Async                                      |  |  |  |  |  |

| MISC       | 4Dh  |     | Others                      | _                 | Async                                      |  |  |  |  |  |

| _          | 4Eh  |     | (Prohibited)                | _                 | _                                          |  |  |  |  |  |

| M-RST      | 4Fh  |     | Initialization              | _                 | Async                                      |  |  |  |  |  |

| MONI-DB    | 50h  |     | DB monitor                  | _                 | Async                                      |  |  |  |  |  |

| MONI-CP    | 51h  |     | CP monitor                  | _                 | Async                                      |  |  |  |  |  |

| MONI-OFP   | 52h  |     | OFP monitor                 | _                 | Async                                      |  |  |  |  |  |

| MONI-DP    | 53h  | R   | DP monitor                  | _                 | Async                                      |  |  |  |  |  |

| MONI-AR    | 54h  |     | AR monitor                  | _                 | Async                                      |  |  |  |  |  |

| MONI-CRP   | 55h  |     | CRP monitor                 | Async             |                                            |  |  |  |  |  |

| MONI-SR    | 56h  |     | SR monitor                  | _                 | Async                                      |  |  |  |  |  |

### Table 1 Control commands

Note 2: The command which is "Sync" in the transfer Sync with Sync signal needs to set the  $\overline{CS}$  = H section to a minimum of 1 fs more until it transmits the following command.(It needs more than 22.68 µs at fs = 44.1 kHz)

(2) Control commands

| COMMAND-40h<br>(Timing) | 0100 0000 |

|-------------------------|-----------|

|-------------------------|-----------|

| D15  | D14  | D13  | D12  | D11  | D10  | D9   | D8   | D7   | D6              | D5         | D4         | D3    | D2         | D1         | D0         |

|------|------|------|------|------|------|------|------|------|-----------------|------------|------------|-------|------------|------------|------------|

| SYPD | SYD1 | SYD0 | SYPA | SYA1 | SYA0 | SYPS | SYS1 | SYS0 | Unas-<br>signed | CKOS1<br>2 | CKOS1<br>1 | CKOS1 | CKOS0<br>2 | CKOS0<br>1 | CKOS0<br>0 |

| Name         | Description                            | Value | Operation                                                           |

|--------------|----------------------------------------|-------|---------------------------------------------------------------------|

| SYPD         | Digital block sync polarity switching  | 0     | ASP program starts on falling edge                                  |

| OND          |                                        | 1     | ASP program starts on rising edge (initial value)                   |

|              |                                        | 0     | Signal after SYNC output (initial value)                            |

| SYD          | ASP digital block SYNC signal input    | 1     | SYNC pin                                                            |

|              | switching                              | 2     | ELRI pin                                                            |

|              |                                        | 3     | ELRO pin                                                            |

| SYPA         | Analog block sync polarity switching   | 0     | Digital filter (DF) program starts on falling edge (initial value)  |

| STPA         | Analog block sync polarity switching   | 1     | Digital filter (DF) program starts on rising edge                   |

|              |                                        | 0     | Signal after SYNC output (initial value)                            |

| SYA<br>[1:0] | Analog block SYNC signal input         | 1     | SYNC pin                                                            |

|              | switching                              | 2     | ELRI pin                                                            |

|              |                                        | 3     | ELRO pin                                                            |

|              |                                        | 0     | Operates at polarity for SYPD, SYPA settings above (initial value). |

| SYPS         | Overall system sync polarity switching | 1     | Reverses all polarities for SYPD, SYPA settings above.              |

|              |                                        | 0     | Internal SYNC signal (initial value)                                |

| SYS          | CVNC aircuit input autitabing          | 1     | SYNC pin                                                            |

| [1:0]        | SYNC circuit input switching           | 2     | ELRI pin                                                            |

|              |                                        | 3     | ELRO pin                                                            |

|              |                                        | 0     | Fixed to L (initial value)                                          |

|              |                                        | 1     | fs2                                                                 |

|              |                                        | 2     | fs4                                                                 |

| CKOS1        | CKO1 nin autnut adaption               | 3     | fs8                                                                 |

| [2:0]        | CKO1 pin output selection              | 4     | fs16                                                                |

|              |                                        | 5     | fs32                                                                |

|              |                                        | 6     | fs64                                                                |

|              |                                        | 7     | Outputs XI or ECKI clock divided by 2                               |

|              |                                        | 0     | Fixed to L (initial value)                                          |

|              |                                        | 1     | fs2                                                                 |

|              |                                        | 2     | fs4                                                                 |

| CKOS0        |                                        | 3     | fs8                                                                 |

| [2:0]        | CKO0 pin output selection              | 4     | fs16                                                                |

|              |                                        | 5     | fs32                                                                |

|              |                                        | 6     | fs64                                                                |

|              |                                        | 7     | fs128                                                               |

|              | COMMAND-41h<br>(BOOT) 0100 0001 |        |           |           |       |                   |          |           |                      |           |           |           |          |       |       |

|--------------|---------------------------------|--------|-----------|-----------|-------|-------------------|----------|-----------|----------------------|-----------|-----------|-----------|----------|-------|-------|

| D15          | D14                             | D13    | D12       | D11       | D10   | D9                | D8       | D7        | D6                   | D5        | D4        | D3        | D2       | D1    | D0    |

| 0            | 0                               | 0      | 0         | 0         | 0     | BTA9              | BTA8     | BTA7      | BTA6                 | BTA5      | BTA4      | BTA3      | BTA2     | BTA1  | BTA0  |

| Name         |                                 | D      | escriptio | n         |       | Value             |          | Operation |                      |           |           |           |          |       |       |

| BTA<br>[9:0] | Self-bo                         | ot ROM | start ad  | dress     |       | 000h<br>~<br>3FFh | Starts s | elf-boot  | operatio             | on from : | specified | addres    | s.       |       |       |

|              | 1AND-42<br>DAC)                 | 2h 01  | 00 0010   |           |       |                   |          |           |                      |           |           |           |          |       |       |