TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

# TC94A58FG

#### Single-Chip CD Processor with Built-in Controller

The TC94A58FG is a single-chip CD processor for digital servo, which incorporates a 4-bit microcontroller.

The controller features an LCD driver, 4-channel 6-bit AD converter, 1 port 2-channel 2/3-line or UART serial interface module, a buzzer, 20-bit general-purpose counter function, interrupt function, and 8-bit timer/counter. The CPU can select one of four operating clocks (16.9344-MHz, 75-kHz or 32.768-kHz crystal oscillator and external clock input), facilitating interface with the CD processor.

The CD processor incorporates sync separation protection and interpolation, EFM demodulator, error correction, digital equalizer for servo, and servo controller. The CD processor also

Weight: 1.20 g (typ.)

incorporates a 1-bit DA converter. In combination with the TA2157F/FG/FN/FNG digital servo head amplifier, the TC94A58FG can very simply configure an adjustment-free CD player.

Thus, the IC is suitable for CD systems for automobiles and radio-cassette players.

#### **Features**

- Single-chip CD processor with on-chip CMOS LCD driver and 4-bit microcontroller

- Operating supply voltage:

- CD in operation:  $V_{DD} = 3.0$  to 3.6 V (3.3 V typ.)

- CD stopped:  $V_{DD} = 1.8 \text{ to } 3.6 \text{ V}$  (only CPU in operation)

- Supply current:

- CD in operation: IDD = 30 mA (typ.)

- CD stopped: IDD = 1.5 mA (CD standby mode, with 16.9344-MHz crystal oscillator, CPU in operation)

- CD stopped: IDD = 50 µA (CD standby mode, with 75-kHz crystal oscillator, CPU in operation)

- Operating temperature range: Ta = -40 to 85°C

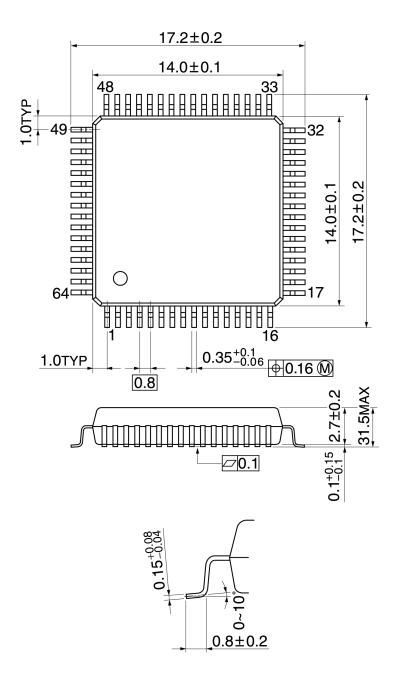

- Package: QFP (0.8-mm pitch, 2.8 mm thick)

- E<sup>2</sup>PROM: TC94AE29FAG

#### 4-bit Microcontroller

- Program memory (ROM): 16 bits × 16 Ksteps

- Data memory (RAM): 4 bits × 512 words

- Instruction execution time: 1.42 μs, 40 μs, 91.6 μs, TOSC × 3 (Every instruction consists of a single word.)

- Crystal oscillator frequency: 16.9344 MHz, 75 kHz, 32.768 kHz, external clock input

- Stack levels: 16

- AD converter: 6 bits × 4 channels

- LCD driver: 1/4 duty, 1/2 or 1/3 bias method, 64 segments (max)

- I/O ports: CMOS I/O ports: 26 (max)

N-channel open-drain I/O ports (for up to 5.5 V): 3 (max)

- Timer/counter: 8 bits (timer mode, pulse width detector and measure function)

- General purpose counter: 20 bits, 0.1 MHz to 20 MHz, Vin = 0.2 Vpp (min), input amplifier incorporated

- Serial interface module: 1 port 2 channel supporting 2/3-line method or UART (two input channels)

- Four buzzer types: 0.75 kHz, 1 kHz, 1.5 kHz, and 3 kHz

- Four modes: continuous, single-shot, 10 Hz intermittent, and 10 Hz intermittent at 1 Hz intervals

- Interrupts: 1 external, 3 internal (CD sub-sync, serial interface, 8-bit timer)

- Back-up mode: Four types: CD standby (CD processor stopped)

Clock stop (oscillator stopped)

Hardware wait (only crystal oscillator in operation)

Software wait (CPU in intermittent operation)

- Reset function: Power-on reset circuit, supply voltage detector (detection voltage = 1.5 V typ.)

- Multiplexed CD processor pins:

Each of the following pins can be switched by program to a CD processor-dedicated pin:

DSP output: BCK, LRCK, AOUT, DOUT, IPF, SBOK, CLCK, DATA, and SFSY pins.

DAC input: DACin, BCKin, and LRCKin pins.

Note: BCKin and LRCKin are switched as a pair. A CD command is used to specify DAC input settings.

#### **CD Processor**

- · Reliable sync pattern detection, sync signal protection and interpolation

- Built-in EFM demodulator and subcode decoder

- High-correction capability using Cross Interleave Read Solomon Code (CIRC) logical equation

C1 correction: dual

C2 correction: quadruple

- Jitter absorption capability of ± 6 frames

- Built-in 16 KB RAM

- Built-in digital output circuit

- · Built-in L/R independent digital attenuator

- · Bilingual audio output

- Audio output: 32fs, 48fs or 64fs selectable

- Subcode Q data is read-timing free and can be driven out in sync with audio data.

- Built-in data slicer and analog PLL (adjustment-free VCO used) circuit

- · Automatic adjustment of loop gain, offset, and balance at focus servo and tracking servo

- Built-in RF gain auto-adjusting circuit

- · Built-in digital equalizer for phase compensation

- · Supports different pickups using on-chip digital equalizer coefficient RAM.

- · Built-in focus and tracking servo control circuit

- Search control supports all modes and realizes high-speed, stable search.

- Lens kick and feed kick use speed control method.

- Built-in AFC and APC circuits for disc motor CLV servo

- Built-in defect/shock detector

- Built-in 8 times over-sampling digital filter and 1-bit DA converter

- Built-in analog filter for 1-bit DA converter

- Built-in zero-data detection output circuit

- Supports double-speed operation.

Note: Output pins for subcode Q data and audio data have multiplexed functions for controller-dedicated pins. The function of each pin can be switched by program.

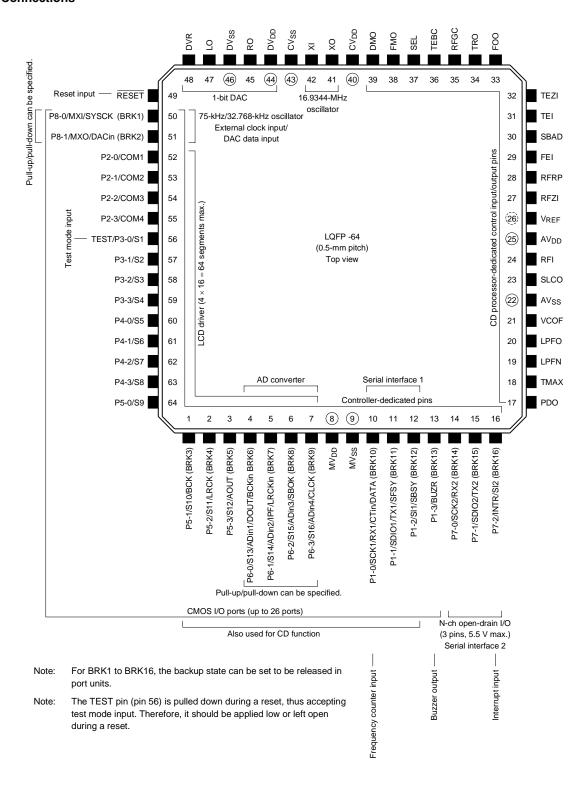

#### **Pin Connections**

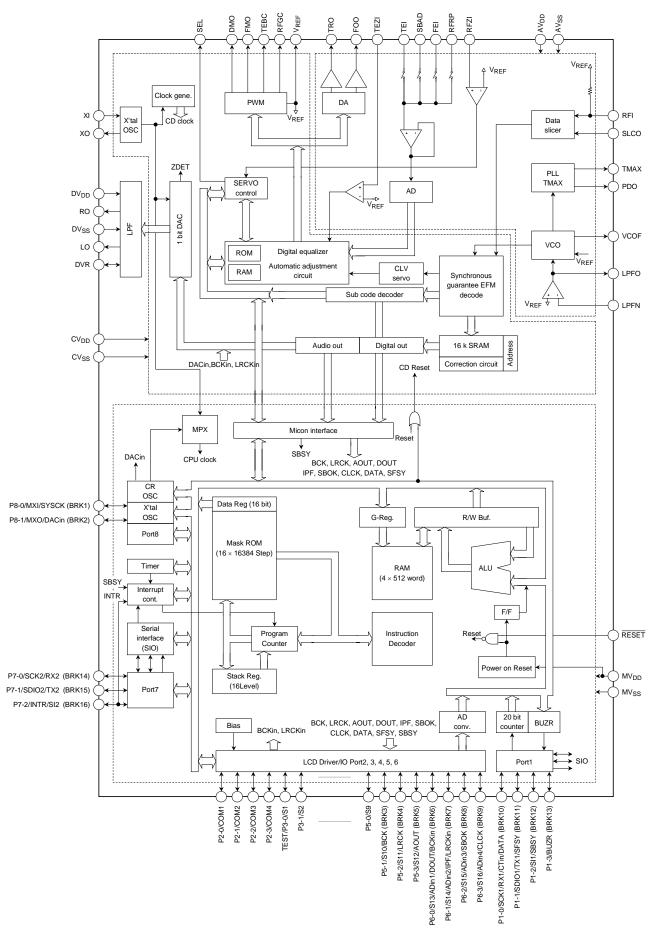

#### **Block Diagram**

5

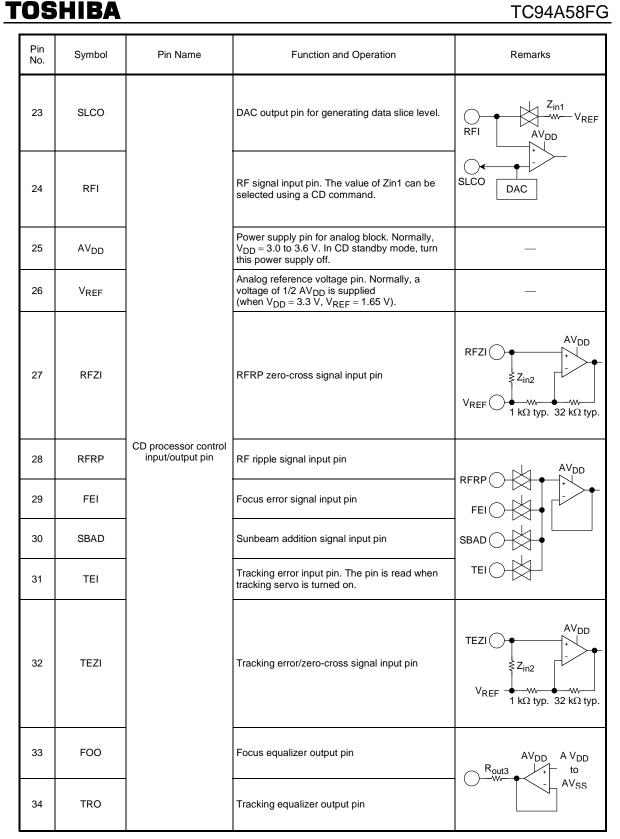

# **Pin Functions**

| Pin<br>No. | Symbol                                                           | Pin Name                                                                                                  | Function and Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Remarks                                                                                                                                                                                                            |

|------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 49         | RESET                                                            | Reset input                                                                                               | System reset input pin for the device.  A reset is applied while the RESET signal is low. When it is high, the 16.9344-MHz crystal oscillator (XI, XO) starts operating. The controller counts clock pulses from this oscillator and waits a specified standby time (approximately 50 ms) before starting the controller program from address 0. The CD processor is placed in the standby state at this time.  Normally, raising the voltage on MVDD from 0 to 1.8 V or higher triggers a system reset (power-on reset) so that the RESET pin should be held at high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MV <sub>DD</sub> MV <sub>SS</sub>                                                                                                                                                                                  |

| 50         | P8-0<br>/MXI/SYSCK<br>(BRK1)<br>P8-1<br>/MXO<br>/DACin<br>(BRK2) | I/O port 8-0 /crystal oscillator /CPU clock input  I/O port 8-1 /crystal oscillator /1-bit DAC data input | 2-bit CMOS I/O port.  Input/output can be specified for each bit. When the pins are used as I/O port input, each pin can be pulled up or down by program. When backup release for clock stop mode or wait mode is enabled for the pins, a change in a pin can release the backup state.  The program can set these pins to be used for a 75-kHz or 32.768-kHz dedicated crystal oscillator. The P8-0 pin can also be used to accept an external CPU operating clock input (SYSCK). The P8-1 pin can also be used to accept data for the 1-bit DAC (DACin) when a CD command is executed.  The 75-kHz or 32.768-kHz dedicated crystal oscillator and CPU clock input are used for the operation of the controller and peripheral devices. Upon a system reset, the 16.9344-MHz crystal oscillator (XI, XO) is selected as the clock for controller and peripheral device operation. The program can subsequently set the pins to oscillator pins and switch the clock generated from the oscillator to the controller clock. When the pins are used for an oscillator, executing the CKSTP instruction causes its oscillation to stop.  (Note) When the P8-0 pin is used for a CR oscillator, the P8-1 pin can used as an I/O port pin.  (Note) Backup release is enabled for both pins simultaneously.  (Note) Use a crystal oscillator having a good startup characteristic.  (Note) Upon a system reset, the pins are set to I/O port input.  (Note) After setting the pins to oscillator pins, wait until oscillation settles before switching the controller clock.  (Note) For an external CPU clock, usually use a 32.768-kHz clock. The pin has CMOS input configuration. | MV <sub>DD</sub> Input instructio  RIN1  MV <sub>DD</sub> MV <sub>SS</sub> (When used for I/O port)  Rout2  MXO  RfXT2  MV <sub>DD</sub> MXI  MV <sub>DD</sub> MV <sub>SS</sub> (When used for crystal oscillator) |

| Pin<br>No.           | Symbol                                           | Pin Name                                           | Function and Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Remarks                                                                                        |

|----------------------|--------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 52<br>53<br>54<br>55 | P2-0/COM1<br>P2-1/COM2<br>P2-2/COM3<br>P2-3/COM4 | I/O port 2<br>/LCD common output                   | 24-bit CMOS I/O port and 3-bit N-channel open-drain I/O port.  Input/output can be specified for each bit. When the P6-0 to P6-3 pins are used as I/O port input, each pin can be pulled up or down by program. When the P5-1 (BRK3) to P7-2 (BRK16) pins are used as I/O port input and backup release for clock stop mode or wait mode is enabled for those pins (enabled/disabled in port units), a change in any of the pins can release the backup state. The P7-0 to P7-2 pins constitute an N-channel open-drain I/O port, to which a voltage of up to 5.5 V can be applied.  I/O ports 2 to 6 can be set to LCD driver output pins by program. The COM1 to COM4 pins                                                                                                                                                                                                             | LCD voltage WV <sub>DD</sub>                                                                   |

| 56                   | TEST<br>/P3-0/S1                                 | Test input<br>/I/O port 3-0<br>/LCD segment output | drive common signals to the LCD panel while the S1 to S16 pins drive segment signals. The COM1 to COM4 signals configure a matrix with the S1 to S16 signals to display up to 64 segments.  When the LCDoff bit is set to 0, the COM1 to COM4 and S1 to S4 pins are collectively set to LCD output. For S5 to S16, the program can specify either I/O port or segment output individually for each pin.  The LCD can be driven by the 1/4-duty, 1/2-bias method (frame frequency: 62.5 Hz) or the 1/4-duty, 1/3-bias method (frame frequency: 125 Hz). When the 1/2 bias method is set, three common output levels (MVDD, 1/2MVDD and GND) and two segment output levels (MVDD and GND) appear on the pins. When the 1/3 bias method is set, four common and segment output levels (MVDD, 1/3MVDD, 2/3MVDD and GND) appear on the pins.  After clock stop mode is released, a non-select | LCD voltage  MV <sub>DD</sub> MV <sub>DD</sub> MV <sub>DD</sub> Reset signal  MV <sub>SS</sub> |

| 57<br>58<br>59       | P3-1/S2<br>P3-2/S3<br>P3-3/S4                    | I/O port 3<br>/LCD segment output                  | waveform (bias voltage) is driven and the DISP OFF bit is set to 0, after which the common signals are driven.  During a system reset ( RESET = low), the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LCD voltage                                                                                    |

|                      |                                                  |                                                    | TEST/P3-0/S1 pin is pulled down and accepts test mode input. This pin should be left open or applied low level during a reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>▼</b> F                                                                                     |

| 60                   | P4-0/S5                                          |                                                    | The P5-1 to P6-3 and P1-0 to P1-2 pins can be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                |

| 61                   | P4-1/S6                                          | I/O port 4                                         | set to CD processor-dedicated pins on a per pin<br>basis. The CD processor functions are as<br>follows:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                |

| 62                   | P4-2/S7                                          | /LCD segment output                                | ioliows.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | MV <sub>DD</sub>                                                                               |

| 63                   | P4-3/S8                                          |                                                    | (Continued on next page)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Input  instruction                                                                             |

| Pin<br>No.  | Symbol                                                                                                                                                                               | Pin Name                                              | Function and Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Remarks                                                                      |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| 64          | P5-0/S9                                                                                                                                                                              | I/O port 5-0<br>/LCD segment output                   | BCK: Bit clock output pin. One of three frequencies, 32, 48 or 64 can be specified using a CD command.  At normal speed: 32 f <sub>S</sub> = 1.4112 MHz  CLRCK: LR channel clock output pin. For the L channel, this pin drives a low level. For the R channel, it drives a high level. The polarity can be inverted using a CD command.  At normal speed: 44.1 kHz  AOUT: Audio data output pin. Either MSB first or LSB first can be specified using a CD command.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | LCD voltage  MV <sub>DD</sub> MV <sub>DD</sub> Input Instruction             |

| 1 2 3       | P5-1/S10<br>/BCK<br>(BRK3)<br>P5-2/S11<br>/LRCK<br>(BRK4)<br>P5-3/S12<br>/AOUT<br>(BRK5)                                                                                             | I/O port 5 /LCD segment output /CD processor function | <ul> <li>DOUT: Digital data output pin. It drives data at up to double speed (complying with CP-1201).</li> <li>IPF: Correction flag output pin. If the AOUT output is C2 error detection/correction, a high level appears to indicate an uncorrectable symbol. (Also called C2PO)</li> <li>SBOK: CRCC test result output pin for subcode Q data. A high level appears when the data has passed the test.</li> <li>CLCK: Clock input/output pin for reading subcode P to W data. The input/output polarity can be inverted using a CD command.</li> <li>DATA: Subcode P to W data output pin.</li> <li>SFSY: Frame sync signal output pin for</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LCD voltage  MVDD  MVDD  MVDD  MVDD  MVDD  MVDD  MVDD                        |

| 4<br>5<br>6 | P6-0/S13<br>/ADin1<br>/DOUT<br>/BCKin<br>(BRK6)<br>P6-1/S14<br>/ADin2<br>/IPF<br>/LRCKin<br>(BRK7)<br>P6-2/S15<br>/ADin3<br>/SBOK<br>(BRK8)<br>P6-3/S16<br>/ADin4<br>/CLCK<br>(BRK9) | I/O port 6 /LCD segment output /CD processor function | playback.  SBSY: Block sync signal output pin for subcode. When a subcode sync is detected, a high level appears at S1. The controller enables CD interrupts. When an interrupt occurs on the falling edge of the SBSY signal, the program jumps to address 2.  BCKin: Bit clock input pin for 1-bit DAC.  LRCKin: LR channel clock input pin for 1-bit DAC  (Note) Interrupts should not be enabled when CD processor operation is undefined.  (Note) Unlike other CD processor pins, LRCKin and BCKin are configured as a pair so their functions are always switched together. When these pins are used, they should be set as I/O port input.  P6-0 to P6-3 pins have multiplexed functions for the on-chip 6-bit 4-channel AD converter analog input. The on-chip AD converter uses successive approximation. The conversion time is 242 μs when the 16.9344-MHz crystal oscillator is used and 7 instruction cycles (280 μs) when the 75-kHz crystal oscillator is used. The program can specify necessary pins for AD analog input on a per bit basis. The internal power supply (MV <sub>DD</sub> ) is used as the reference voltage. When the P6-0 to P6-3 pins are used as I/O port input, each pin can be pulled up or down by program. | AD input LCD voltage  MVDD  Input instruction Release enable RIN1 MVDD  MVSS |

| Pin<br>No. | Symbol                                         | Pin Name                                                                                                     | Function and Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Remarks                                |  |  |

|------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|--|

| 10         | P1-0/SCK1<br>/RX1<br>/CTin<br>/DATA<br>(BRK10) | I/O port 1-0 /serial clock input/output 1 /serial receive data 1 /counter clock input /CD processor function | The P1-0 pin has multiplexed functions for general-purpose counter input. The input frequency is 0.1 MHz to 20 MHz. The counter incorporates an input amplifier and operates with capacitance-coupled small amplitudes. The counter is a 20-bit counter and can store 20-bit data directly in memory. The gate time can be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MV <sub>DD</sub>                       |  |  |

| 11         | P1-1/SDIO1<br>/TX1<br>/SFSY<br>(BRK11)         | I/O port 1-1<br>/serial data<br>input/output 1<br>/serial transmit data 1<br>/CD processor<br>function       | selected from among 1 ms, 4 ms, 16 ms and 64 ms (when the 75-kHz crystal oscillator is used). In manual mode, the gate can be turned on and off within the specified time using instructions.  The P1-0 to P1-2 and P7-0 to P7-2 pins have multiplexed functions for serial interface (SIO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Input instruction Release enable       |  |  |

| 12         | P1-2/SI1<br>/SBSY<br>(BRK12)                   | I/O port 1-2<br>/serial data input 1<br>/CD processor<br>function                                            | circuit input/output pins.  The SIO is a serial interface supporting 2-line and 3-line methods as well as UART. The TC94A58FG has CMOS input/output pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | (When used for I/O port) $R_{\rm flN}$ |  |  |

| 13         | P1-3/BUZR<br>(BRK13)                           | I/O port 1-3<br>/buzzer output                                                                               | open-drain (supporting up to 5.5 V) input/output pins (SCK2/RX2, SDIO2/TX2, SI2). One of the two sets of pins can be selected as serial interface. The serial interface circuit supports various options, including the number of the clock edge to be used, the serial clock input/output, and the clock frequency. These options facilitate controlling the LSI and communications between the controllers. When SIO interrupts are enabled, an interrupt is general-purpose generated as soon as execution of the SIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                        |  |  |

| 14         | P7-0/SCK2<br>/RX2<br>(BRK14)                   | I/O port 7-0<br>/serial clock<br>input/output 2<br>/serial receive data 2                                    | completes, causing the program to jump to address 4.  The P1-3 pin has multiplexed functions for a buzzer output pin. One of four frequencies within the page 27 february 27 f |                                        |  |  |

| 15         | P7-1/SDIO2<br>/TX2<br>(BRK15)                  | I/O port 7-1<br>/serial data<br>input/output 2<br>/serial transmit data 2                                    | within the range from 0.75 kHz, 1 kHz, 1.5 kHz and 3 kHz can be selected for buzzer output (when the 75-kHz clock is used). The buzzer is driven at the selected frequency in one of four modes: continuous, single-shot, 10-Hz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |  |  |

| 16         | P7-2/INTR<br>/SI2<br>(BRK16)                   | I/O port 7-2<br>/interrupt input<br>/serial data input 2                                                     | intermittent, and 10-Hz intermittent at 1-Hz intervals.  The P7-2 pin has multiplexed functions for an external interrupt input pin. When interrupts are enabled and a pulse of 1.65 µs to 4.96 µs or more (13.3 µs to 40 µs when the 75-kHz clock is used) is applied to this pin, an interrupt is generated and the program jumps to address 1. The input logic and rising/falling edge can be selected for interrupt inputs. This input can be applied as the clock gate signal to the internal 8-bit timer/counter, which allows input pulse width to be detected and measured.  (Note) Backup release is enabled or disabled in port units.  (Note) Upon a system reset, the pins are set to I/O port input.  (Note) When the 32.768-kHz crystal oscillator or the CR oscillator is used, the general-purpose counter is used as a timer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Input instruction Release enable       |  |  |

| Pin<br>No. | Symbol           | Pin Name                                 | Function and Operation                                                                                                                                                                                                                                                                                                                                                        | Remarks                                                              |

|------------|------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 8          | MV <sub>DD</sub> | - Power supply pins for controller block | Power supply pins for the controller block. Normally, $V_{DD} = 3.0$ to $3.6$ V. When only the CPU operates (when the 75-kHz/32.768-kHz oscillator is used), it can operate at $V_{DD} = 1.8$ to $3.6$ V. In the backup state (when the CKSTP instruction is executed), current dissipation decreases (10 $\mu$ A or below), allowing the power                               | MV <sub>DD</sub>                                                     |

| 9          | MV <sub>SS</sub> |                                          | supply voltage to be reduced to 1.0 V.  Raising the voltage on MVDD pin from 0 V to 1.8 V or higher triggers a system reset, causing the program to start from address 0 (power-on reset).  (Note) At power-on reset operation, allow 1 ms to 50 ms while the device power supply voltage rises.  (Note) The backup current is the total of currents for CVDD, MVDD and DVDD. | → MV <sub>SS</sub>                                                   |

| 17         | PDO              |                                          | Output pin for a phase error signal between the EFM and PLCK signals.  Drives one of four values: AV <sub>DD</sub> , Hi-Z, V <sub>REF</sub> , AV <sub>SS</sub>                                                                                                                                                                                                                | AV <sub>DD</sub> R <sub>out4</sub> AV <sub>SS</sub> V <sub>REF</sub> |

| 18         | TMAX             | CD processor control input/output pin    | TMAX detection result output pin.  Longer than specified cycle: Drives a high level (AV <sub>DD</sub> )  Shorter than specified cycle: Drives a low level (AV <sub>SS</sub> )  Within specified cycle: Hi-Z                                                                                                                                                                   | AV <sub>DD</sub>                                                     |

| 19         | LPFN             |                                          | Inverted input pin for PLL low-pass filter amplifier.                                                                                                                                                                                                                                                                                                                         | AV <sub>DD</sub>                                                     |

| 20         | LPFO             |                                          | Output pin for PLL low-pass filter amplifier.                                                                                                                                                                                                                                                                                                                                 | LPFO C                                                               |

| 21         | VCOF             |                                          | VCO filter pin                                                                                                                                                                                                                                                                                                                                                                | VREF VCO                                                             |

| 22         | AV <sub>SS</sub> |                                          | Ground pin for analog block                                                                                                                                                                                                                                                                                                                                                   | _                                                                    |

| Pin<br>No. | Symbol           | Pin Name                | Function and Operation                                                                                                                                                                                                                                                                         | Remarks              |

|------------|------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 35         | RFGC             |                         | Control signal output pin for adjusting RF amplitude. Drives three-level PWM signal (PWM carrier = 88.2 kHz).                                                                                                                                                                                  | AV <sub>DD</sub>     |

| 36         | TEBC             |                         | Tracking balance control signal output pin. Drives three-level PWM signal (PWM carrier = 88.2 kHz).                                                                                                                                                                                            | V <sub>REF</sub>     |

| 37         | SEL              | input/output pin        | APC circuit ON/OFF signal output pin. When laser is turned on, this pin will be in a high-impedance state.                                                                                                                                                                                     | AV <sub>DD</sub>     |

| 38         | FMO              |                         | Feed equalizer output pin. Drives three-level PWM signal (PWM carrier = 88.2 kHz).                                                                                                                                                                                                             | AV <sub>DD</sub>     |

| 39         | DMO              |                         | Disc equalizer output pin. Drives three-level PWM signal (PWM carrier = 88.2 kHz).                                                                                                                                                                                                             | V <sub>REF</sub>     |

| 40         | CV <sub>DD</sub> | Power supply pins       | Logic power supply pins for the CD processor block and 16.9344-MHz dedicated crystal oscillator. Normally, the same power supply as                                                                                                                                                            | ○ CVDD               |

| 43         | CV <sub>SS</sub> |                         | that for the MV <sub>DD</sub> and MV <sub>SS</sub> pins is connected. In CD standby mode, current dissipation decreases.                                                                                                                                                                       | CV <sub>SS</sub>     |

| 41         | хо               |                         | Input/output pins for the CD processor-dedicated crystal oscillator. Connect a 16.9344-MHz crystal oscillator. This clock is used as the CD processor system clock and controller system clock. Upon a system reset, this clock is supplied as the controller system clock and starts the CPU. | XO R <sub>fXT1</sub> |

| 42         | XI               | Crystal oscillator pins | The crystal oscillator can be stopped by program. If the 75/32.768-kHz or external CPU clock is selected as the controller system clock, the CD processor oscillator is stopped by program when the CD processor is turned off.  (Note) When switching the controller system                   | XI CV <sub>SS</sub>  |

|            |                  |                         | clock from the controller oscillator to the CD crystal oscillator, make sure that the CD crystal oscillator is sufficiently stable.                                                                                                                                                            |                      |

**TOSHIBA**

| Pin<br>No. | Symbol           | Pin Name         | Function and Operation                                                                      | Remarks          |

|------------|------------------|------------------|---------------------------------------------------------------------------------------------|------------------|

| 44         | DV <sub>DD</sub> |                  | DA converter block power supply pin The TC94A58FG consumes less current in CD standby mode. | DV <sub>DD</sub> |

| 45         | RO               |                  | R-channel data forward rotation output pin                                                  | DVR              |

| 46         | DV <sub>SS</sub> | Audio DAC output | DA converter block ground pin                                                               | RO/LO P          |

| 47         | LO               |                  | L-channel data forward rotation output pin                                                  | DV <sub>SS</sub> |

| 48         | DVR              |                  | Reference voltage pin                                                                       | Vss              |

# Maximum Ratings (Ta = 25°C, $CV_{DD} = DV_{DD} = AV_{DD} = MV_{DD}$ )

| Characteristics        |                      | Symbol           | Rating                         | Unit |

|------------------------|----------------------|------------------|--------------------------------|------|

| Supply voltage         |                      | $V_{DD}$         | -0.3 to 4.0                    | V    |

|                        | CV <sub>DD</sub> pin | V <sub>IN1</sub> | -0.3 to CV <sub>DD</sub> + 0.3 |      |

|                        | AV <sub>DD</sub> pin | V <sub>IN2</sub> | -0.3 to AV <sub>DD</sub> + 0.3 |      |

| Input voltage (Note 1) | DV <sub>DD</sub> pin | V <sub>IN3</sub> | -0.3 to DV <sub>DD</sub> + 0.3 | V    |

|                        | MV <sub>DD</sub> pin | V <sub>IN4</sub> | -0.3 to MV <sub>DD</sub> + 0.3 |      |

|                        |                      | V <sub>IN5</sub> | −0.3 to 6.0                    |      |

| Power dissipation      |                      | P <sub>D</sub>   | 500                            | mW   |

| Operating temperature  |                      | T <sub>opr</sub> | -40 to 85                      | °C   |

| Storage temperature    |                      | T <sub>stg</sub> | -65 to 150                     | °C   |

Note 1:  $V_{IN1}$ ; Pins 41 and 42

V<sub>IN2</sub>; Pins 17 to 39 (excluding power supply pins)

V<sub>IN3</sub>; Pins 45, 47 and 48

$V_{\text{IN4}}$ ; Pins 1 to 13 and 49 to 64 (excluding power supply pins)

V<sub>IN5</sub>; Pins 14, 15 and 16

# Electrical Characteristics (Ta = 25°C, CV<sub>DD</sub> = MV<sub>DD</sub> = DV<sub>DD</sub> = AV<sub>DD</sub> = 3.3 V, V<sub>REF</sub> = 1.65 V unless otherwise stated)

| Characteristics                            | Symbol                          | Test<br>Circuit | Test Condition                                                                                                                          | Min  | Тур.    | Max | Unit |

|--------------------------------------------|---------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------|------|---------|-----|------|

|                                            | V <sub>DD1</sub>                |                 | CPU and CD in operation $\label{eq:def_NDD} MV_{DD} = CV_{DD} \geqq DV_{DD} = AV_{DD} $ (Note 4)                                        | 3.0  | ~       | 3.6 |      |

| Operating supply voltage range             | V <sub>DD2</sub>                | _               | CPU in operation (CD standby,<br>16.9344-MHz crystal oscillator/CR oscillator<br>used) (Note 4)                                         | 3.0  | ~       | 3.6 | V    |

|                                            | V <sub>DD3</sub>                |                 | Only CPU in operation (CD standby,<br>75-kHz/32.768-kHz crystal oscillator used)<br>(Note 5)                                            | 1.8  | ~       | 3.6 |      |

| Memory hold voltage range                  | MV <sub>HD</sub>                | _               | Crystal oscillator stopped (CKSTP instruction executed) (Note 4)                                                                        | 1.0  | ~       | 3.6 | ٧    |

|                                            | I <sub>DD1</sub>                |                 | CPU and CD in operation<br>(XI = 16.9344-MHz crystal oscillator used)                                                                   | _    | 30      | 50  | mA   |

| Operating power supply                     | I <sub>DD2</sub>                |                 | Only CPU in operation<br>(XI = 16.9344-MHz crystal oscillator used)                                                                     | _    | 1.5     |     | IIIA |

| current (Note 2)                           | I <sub>DD3</sub>                | _               | CPU in operation<br>(MXI = 75-kHz crystal oscillator connected)                                                                         |      | 50      | 100 | μА   |

|                                            | I <sub>DD4</sub>                |                 | Standby mode<br>(only crystal oscillator in operation,<br>MXI = 75 kHz)                                                                 |      | 30      | 80  | μА   |

| Memory hold current                        | MI <sub>HD</sub>                | _               | (CV <sub>DD</sub> /MV <sub>DD</sub> /AV <sub>DD</sub> /DV <sub>DD</sub> ) Crystal<br>oscillator stopped<br>(CKSTP instruction executed) | _    | 0.1     | 10  | μА   |

| Oscillation frequency                      | f <sub>MXT</sub>                | _               | (MXI-MXO) Crystal oscillator selected (Note 3) (Note 5)                                                                                 | 30   | ~       | 100 | kHz  |

| . ,                                        | fXT                             |                 | (XI-XO) (Note 4)                                                                                                                        | _    | 16.9344 | _   | MHz  |

| Crystal oscillator start time              | t <sub>st</sub>                 | _               | (MXI-MXO)<br>Crystal oscillator f <sub>mxt</sub> = 75 kHz/32.768 kHz                                                                    | _    | _       | 1.0 | s    |

| Crystal oscillator amplifier               | R <sub>fXT1</sub>               |                 | (XI-XO)                                                                                                                                 | 0.5  | 1.0     | 2.0 | Мо   |

| feedback resistance                        | R <sub>fXT2</sub>               |                 | (MXI-MXO)                                                                                                                               | _    | 20      | _   | ΜΩ   |

| Crystal oscillator output                  | R <sub>out1</sub>               |                 | (XO)                                                                                                                                    | 0.25 | 0.5     | 1.0 | kΩ   |

| resistance                                 | R <sub>out2</sub>               |                 | (MXO)                                                                                                                                   | 50   | 100     | 200 | NS 2 |

| Dropout voltage detect voltage             | V <sub>DET</sub>                | _               | (M)/) Proposit voltage detector analysis                                                                                                | 1.4  | 1.5     | 1.6 | ٧    |

| Dropout voltage detector operating current | I <sub>DD</sub> -V <sub>D</sub> | _               | (MV <sub>DD</sub> ) Dropout voltage detector enabled                                                                                    | _    | 100     | _   | μА   |

- Note 2: The operating power supply current includes the total current through all CV<sub>DD</sub>, MV<sub>DD</sub>, DV<sub>DD</sub> and AV<sub>DD</sub> power supply pins.

- Note 3: Design and specify constants according to the crystal oscillator to be connected.

- Note 4: The values are guaranteed when  $CV_{DD} = MV_{DD} = DV_{DD} = AV_{DD} = 3.0$  to 3.6 V, Ta = -40 to 85°C.

- Note 5: The values are guaranteed when  $CV_{DD} = MV_{DD} = DV_{DD} = AV_{DD} = 1.8$  to 3.6 V, Ta = -30 to 75°C.

#### **General-purpose counter (CTin)**

| Characteristics                     | Symbol             | Test<br>Circuit | Test Condition                                                                | Min | Тур. | Max  | Unit             |

|-------------------------------------|--------------------|-----------------|-------------------------------------------------------------------------------|-----|------|------|------------------|

| Frequency range                     | f <sub>CT</sub>    | _               | $V_{\mbox{\footnotesize{IN}}} = 0.2 \ V_{\mbox{\footnotesize{P-P}}}$ (Note 6) | 0.1 | _    | 20   | MHz              |

| Input amplitude range               | V <sub>CT</sub>    | _               | (Note 6)                                                                      | 0.2 | _    | 2.0  | V <sub>P-P</sub> |

| Operating power supply current      | I <sub>DD-CT</sub> | _               | General-purpose counter operating current, $f_{\text{in}} = 20 \text{ MHz}$   |     | 0.5  |      | mA               |

| Input amplifier feedback resistance | R <sub>fIN</sub>   | _               | (CTin)                                                                        | 200 | 350  | 1000 | kΩ               |

Note 6: The values are guaranteed when  $CV_{DD} = MV_{DD} = DV_{DD} = AV_{DD} = 3.0$  to 3.6 V, Ta = -40 to  $85^{\circ}C$ .

#### LCD common and segment outputs (COM1 to COM4, S1 to S16)

| Characteristics |              | Symbol               | Test<br>Circuit | Test Condition                            | Min  | Тур. | Max  | Unit |

|-----------------|--------------|----------------------|-----------------|-------------------------------------------|------|------|------|------|

| Output current  | High level   | I <sub>OH1</sub>     |                 | V <sub>OH</sub> = 2.9 V (LCD output)      | _    | -300 | _    | μА   |

| Output current  | Low level    | I <sub>OL1</sub>     |                 | V <sub>OL</sub> = 0.4 V (LCD output)      | _    | 450  | _    | μΑ   |

|                 | 1/2 level    | V <sub>BS2</sub>     |                 | No load (common output, 1/2 bias method)  | 2.3  | 2.5  | 2.7  |      |

| Bias current    | 1/3 level    | V <sub>BS1</sub>     | _               | No local (LOD coderest 4/0 bigg grade at) | 1.47 | 1.67 | 1.87 | V    |

|                 | 2/3 level    | V <sub>BS3</sub>     |                 | No load (LCD output, 1/3 bias method)     | 3.13 | 3.33 | 3.53 |      |

| LCD operating p | power supply | I <sub>DD-</sub> LCD |                 | LCD driver operating current              |      | 50   |      | μΑ   |

#### I/O ports (P1-0 to P6-3, P8-0, P8-1, P7-0 to P7-3)

| Characte                      | ristics    | Symbol           | Test<br>Circuit | Test Condition                                                               | Min                   | Тур. | Max                                                               | Unit |     |   |  |

|-------------------------------|------------|------------------|-----------------|------------------------------------------------------------------------------|-----------------------|------|-------------------------------------------------------------------|------|-----|---|--|

|                               | High level | I <sub>OH2</sub> |                 | V <sub>OH</sub> = 2.9 V (P1-0 to P1-3, P6-2, P6-3, P8-0, P8-1)               | -1.0                  | -2.0 | _                                                                 |      |     |   |  |

|                               |            | I <sub>OH3</sub> |                 | V <sub>OH</sub> = 2.9 V (P2-0 to P5-3, P6-0, P6-1)                           | -3.0                  | -6.0 |                                                                   |      |     |   |  |

| Output current                |            | I <sub>OL2</sub> | _               | V <sub>OL</sub> = 0.4 V (P1-0 to P1-3 , P6-2 , P6-3, P8-0, P8-1)             | 1.0                   | 2.0  | _                                                                 | mA   |     |   |  |

|                               | Low level  | I <sub>OL3</sub> |                 | V <sub>OL</sub> = 0.4 V (P7-0 to P7-3)                                       | 5                     | 15   | _                                                                 |      |     |   |  |

|                               | Low level  | Low level        | Low level       | Low level                                                                    | I <sub>OL4</sub>      |      | V <sub>OL</sub> = 0.4 V<br>(P2-2, P2-3, P3-0 to P5-3, P6-0, P6-1) | 3.0  | 6.0 | _ |  |

|                               |            | I <sub>OL5</sub> |                 | V <sub>OL</sub> = 0.4 V (P2-0, P2-1)                                         | 15                    | 30   | _                                                                 |      |     |   |  |

| Input leakage cu              | ırrent     | ILI              | _               | V <sub>IH</sub> = 3.3 V,<br>V <sub>IL</sub> = 0 V (P1-0 to P6-3, P8-0, P8-1) |                       |      | ±1.0                                                              | μА   |     |   |  |

|                               |            |                  | •               | V <sub>IH</sub> = 5.5 V, V <sub>IL</sub> = 0 V (P7-0 to P7-3)                | _                     | _    | ±1.0                                                              |      |     |   |  |

| Input voltage                 | High level | V <sub>IH</sub>  |                 | _                                                                            | V <sub>DD</sub> × 0.8 | ~    | $MV_{DD}$                                                         | V    |     |   |  |

| Input voltage                 | Low level  | V <sub>IL</sub>  |                 | _                                                                            | 0                     | ~    | MV <sub>DD</sub> × 0.2                                            | V    |     |   |  |

| Input pull-up/down resistance |            | R <sub>IN1</sub> | _               | (P6-0 to P6-3, P8-0, P8-1)<br>Pull-down/up specified                         | 25                    | 50   | 120                                                               | kΩ   |     |   |  |

|                               |            | R <sub>IN2</sub> |                 | (P3-0) Test input pulled down                                                | _                     | 10   | _                                                                 |      |     |   |  |

#### AD converter (ADin1 to ADin4)

| Characteristics              | Symbol           | Test<br>Circuit | Test Condition                                                                 | Min | Тур. | Max       | Unit |

|------------------------------|------------------|-----------------|--------------------------------------------------------------------------------|-----|------|-----------|------|

| Analog input voltage range   | $V_{AD}$         | _               | ADin1 to ADin4                                                                 | 0   | ~    | $MV_{DD}$ | V    |

| Resolution                   | V <sub>RES</sub> | _               | _                                                                              | _   | 6    | _         | bit  |

| Total conversion error       |                  |                 | $MV_{DD} = 1.8 \sim 3.6 V$ , $Ta = -30 \sim 75 °C$ (Note 7)                    | _   | _    | ±2.0      | LSB  |

| Total conversion error       | _                |                 | $MV_{DD} = 2.0 \sim 3.6 \text{V}, \text{ Ta} = -40 \sim 85 \text{°C}$ (Note 7) | _   | _    | ±1.0      | LOD  |

| Analog input leakage current | ILI              | _               | $V_{IH} = 3.3 \text{ V}, V_{IL} = 0 \text{ V} \text{ (ADin1 to ADin4)}$        | _   | _    | ±1.0      | μА   |

Note 7: The values are guaranteed when  $\text{CV}_{DD} = \text{DV}_{DD} = \text{AV}_{DD} = 3.0$  to 3.6 V.

# PDO, TMAX, RFGC, TEBC, FMO, DMO, TRO, FOO, and SEL output

| Characte                   | ristics                               | Symbol            | Test<br>Circuit | Test Condition                      | Min  | Тур. | Max | Unit |

|----------------------------|---------------------------------------|-------------------|-----------------|-------------------------------------|------|------|-----|------|

| Output current High level  | High level                            | I <sub>OH6</sub>  |                 | V <sub>OH</sub> = 2.9 V (SEL, TMAX) | -2.0 | _    | _   | mA   |

| Output current             | Low level                             | I <sub>OL4</sub>  |                 | V <sub>OL</sub> = 0.4 V (SEL, TMAX) | 2.0  | _    | 1   | ША   |

| Output registere           | Output maintage                       |                   |                 | (RFGC, TEBC, FMO, DMO, TRO, FOO)    | _    | 3.0  | 1   | kΩ   |

| Output resistance          |                                       | R <sub>out4</sub> |                 | (PDO)                               | _    | 5.0  | _   | KS 2 |

| V <sub>REF</sub> output ON | V <sub>REF</sub> output ON resistance |                   | _               | (RFGC, TEBC, FMO, DMO, PDO)         | _    | _    | 500 | Ω    |

#### Transfer delay time (BCK, LRCK, AOUT, DOUT, IPF, SBOK, CLCK, DATA, SFSY, SBSY)

| Characte       | ristics    | Symbol           | Test<br>Circuit | Test Condition | Min | Тур. | Max | Unit |

|----------------|------------|------------------|-----------------|----------------|-----|------|-----|------|

| Transfer delay | High level | t <sub>pLH</sub> |                 | _              | _   | 10   | _   | ns   |

| time           | Low level  | t <sub>pHL</sub> |                 | _              | _   | 10   | _   | 113  |

## CD processor AD conversion block (FEI, TEI, RFRP, SBAD)

| Characteristics        | Symbol | Test<br>Circuit | Test Condition                                  | Min                        | Тур.  | Max                        | Unit |