# TOSHIBA

# 32-Bit TX System RISC TX19 Family TMP1940CYAF/TMP1940FDBF

**TOSHIBA CORPORATION**

MIPS16, application Specific Extensions and R3000A are a trademark of MIPS Technologies, Inc.

The information contained herein is subject to change without notice.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others.

The products described in this document contain components made in the United States and subject to export control of the U.S. authorities. Diversion contrary to the U.S. law is prohibited.

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress.

It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications.

Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

The Toshiba products listed in this document are intended for usage in general electronics applications ( computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.).

These Toshiba products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of Toshiba products listed in this document shall be made at the customer's own risk.

The products described in this document may include products subject to the foreign exchange and foreign trade laws.

#### Preface

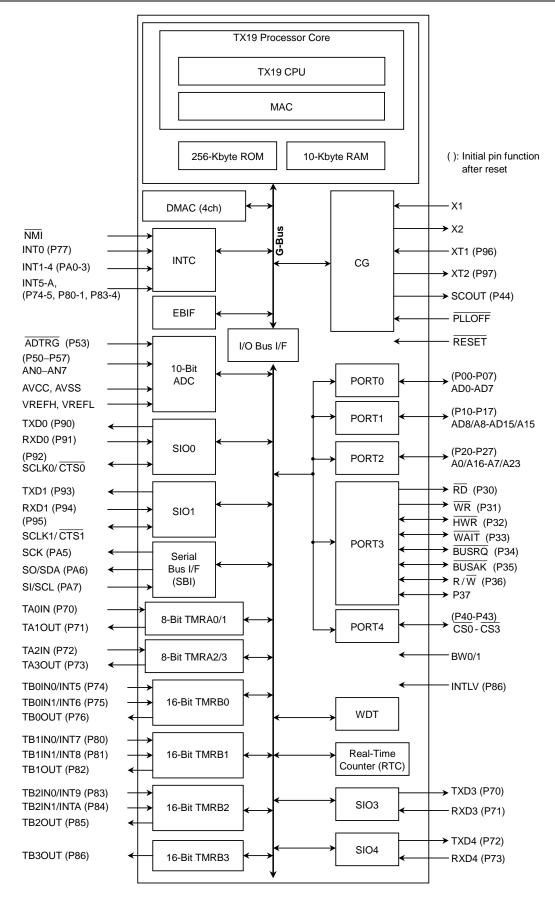

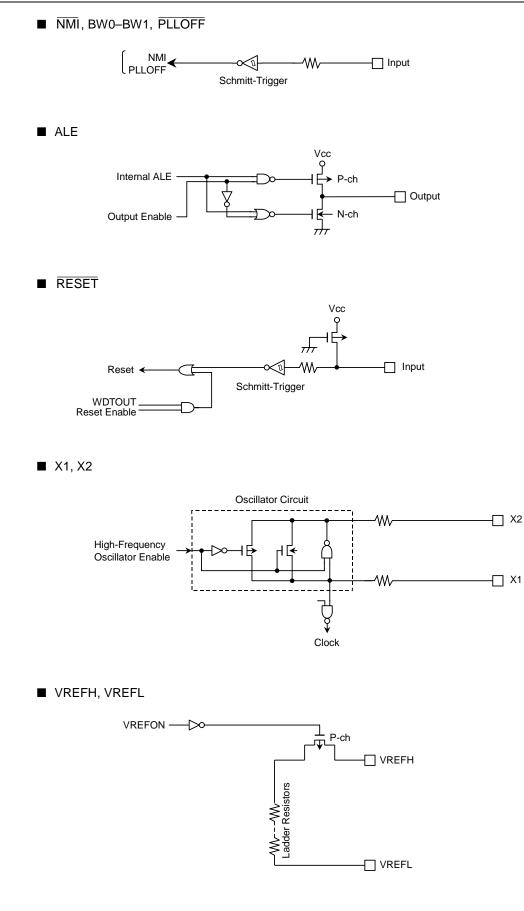

Toshiba offers a broad range of microcontrollers targeted for both commercial and industrial applications. The *TX System RISC TX19 Family* manual contains the detailed specifications of the TX1940, including the architecture, programming, capabilities, operation, electrical characteristics, packaging and so forth.

The TX1940 is a high-performance RISC processor based on the R3000A architecture and the MIPS16 Application Specific Extension pioneered by MIPS Technologies, Inc.

Recently, with the ever-growing market for lightweight portable devices, manufacturers of electronic systems have been seeking cost-effective, single-chip solutions to processor-based applications. Toshiba has designed the TX1940 to help customers achieve the best cost performance for their products.

### Contents

#### **Handling Precaution**

| Part 1 TMP1940<br>TMP1940CYAF                                                                                                       |   |  |

|-------------------------------------------------------------------------------------------------------------------------------------|---|--|

| 1. Features                                                                                                                         | 1 |  |

| 2. Signal Descriptions                                                                                                              | 5 |  |

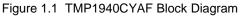

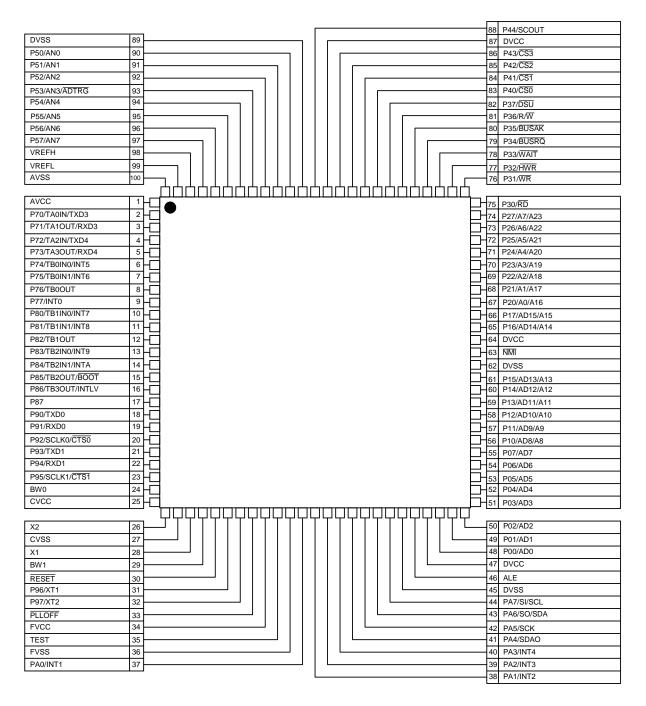

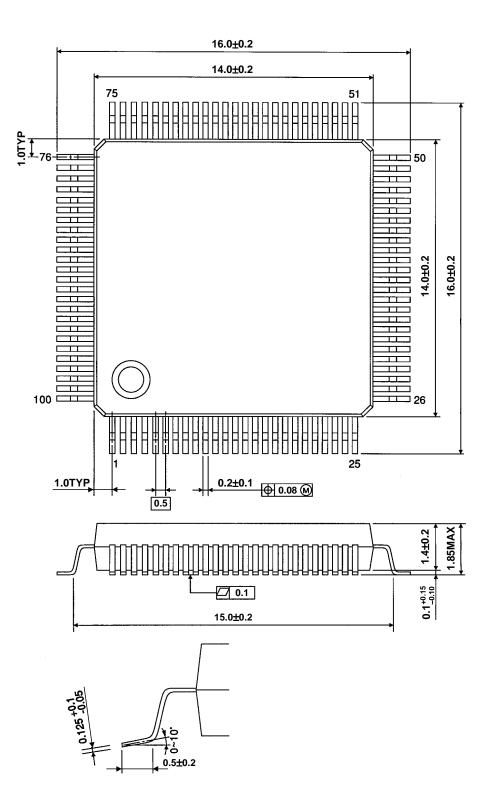

| 2.1 Pin Assignment                                                                                                                  | 5 |  |

| 2.2 Pin Usage Information                                                                                                           | 6 |  |

| 3. Core Processor                                                                                                                   | 0 |  |

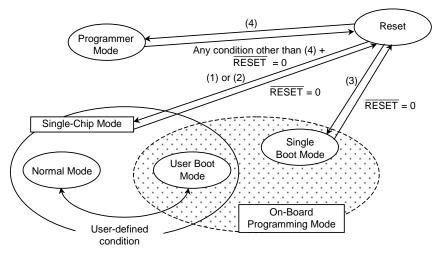

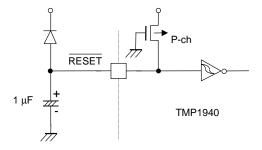

| 3.1 Reset Operation                                                                                                                 |   |  |

|                                                                                                                                     |   |  |

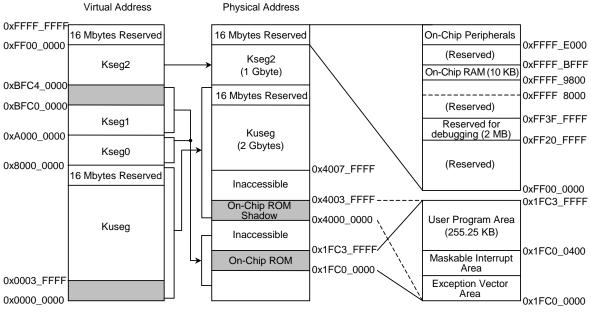

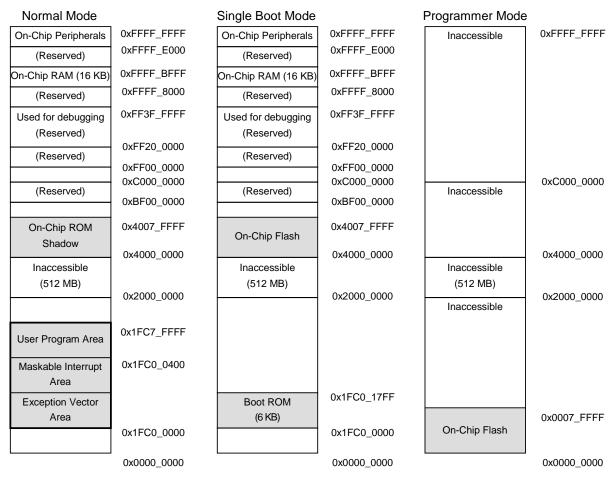

| 4. Memory Map                                                                                                                       |   |  |

| 5. Clock/Standby Control                                                                                                            |   |  |

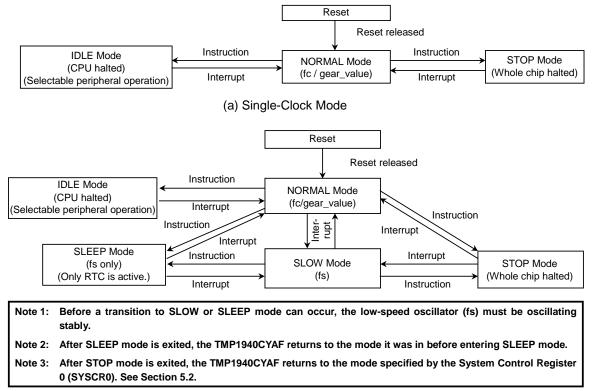

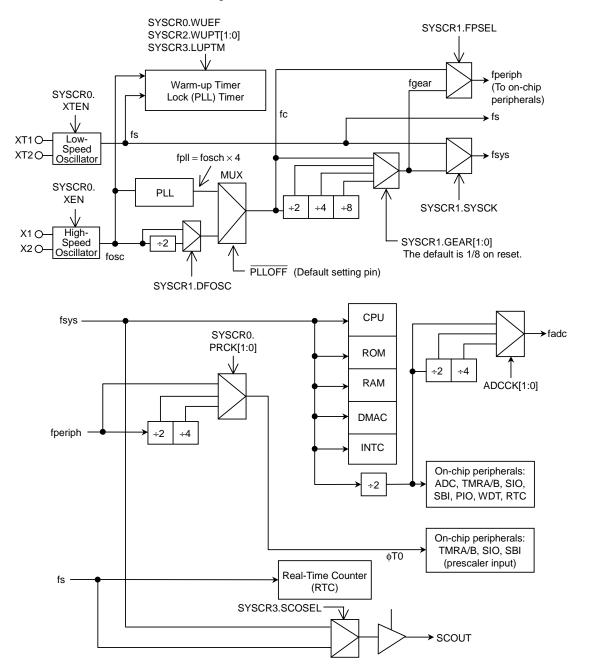

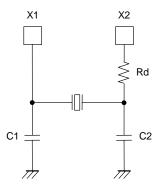

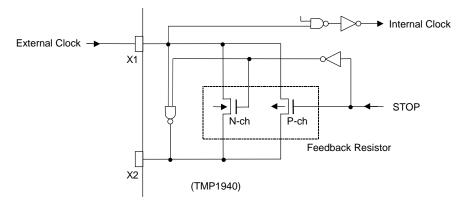

| 5.1 Clock Generation                                                                                                                |   |  |

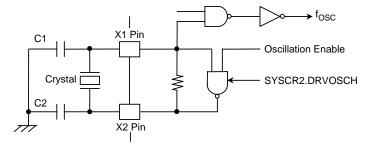

| 5.1.1 Main System Clock                                                                                                             |   |  |

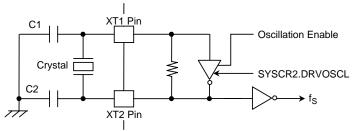

| 5.1.2 Subsystem Clock                                                                                                               |   |  |

| 5.1.3 Clock Source Block Diagrams                                                                                                   |   |  |

| 5.2 Clock Generator (CG) Registers                                                                                                  |   |  |

| 5.2.1 System Clock Control Registers                                                                                                |   |  |

| 5.2.2 ADC Conversion Clock                                                                                                          |   |  |

| 5.2.3 STOP/SLEEP Wake-up Interrupt Control Registers (INTCG Registers)                                                              |   |  |

| 5.2.4 Interrupt Request Clear Register                                                                                              |   |  |

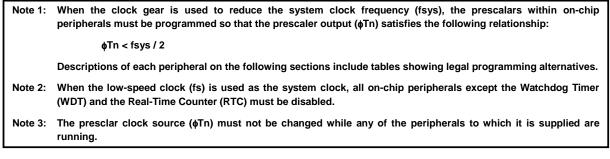

| 5.3 System Clock Control Section                                                                                                    |   |  |

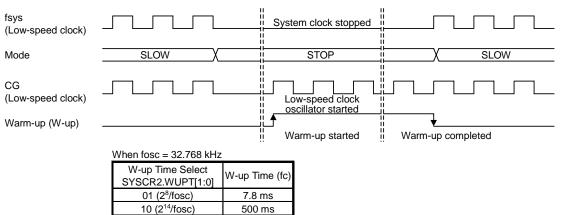

| 5.3.1 Oscillation Stabilization Time When Switching Between NORMAL and SLOW Mode                                                    |   |  |

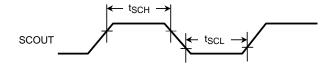

| 5.3.2 System Clock Output                                                                                                           |   |  |

| 5.3.3 Reducing the Oscillator Clock Drive Capability                                                                                |   |  |

| 5.4 Prescalar Clock Control Section                                                                                                 |   |  |

| 5.5 Clock Frequency Multiplication Section (PLL)                                                                                    |   |  |

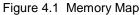

| 5.6 Standby Control Section                                                                                                         |   |  |

| <ul> <li>5.6.1 TMP1940CYAF Operation in NORMAL and Standby Modes</li> <li>5.6.2 CG Operation in NORMAL and Standby Modes</li> </ul> |   |  |

| 5.6.3 Processor and Peripheral Block Operation in Standby Modes                                                                     |   |  |

| 5.6.4 Wake-up Signaling                                                                                                             |   |  |

| 5.6.5 STOP Mode                                                                                                                     |   |  |

| 5.6.6 Returning from a Standby Mode                                                                                                 |   |  |

|                                                                                                                                     |   |  |

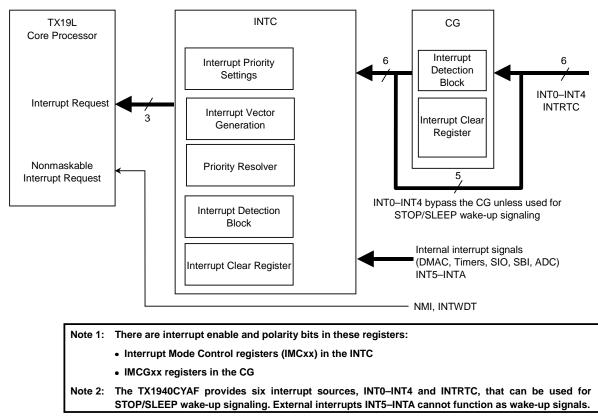

| 6. Interrupts                                                                                                                       |   |  |

| 6.1 Overview                                                                                                                        |   |  |

| 6.2 Interrupt Sources                                                                                                               |   |  |

| 6.3 Interrupt Detection                                                                                                             |   |  |

| 6.4 Resolving Interrupt Priority                                                                                                    |   |  |

| 6.5 Register Description                                                                                                            |   |  |

| 6.1.1 Interrupt Vector Register (IVR)                                                                                               |   |  |

| 6.1.2 Interrupt Mode Control Registers (IMCF–IMC0)                                                                                  |   |  |

| 6.1.3 Interrupt Request Clear Register (INTCLR)                                                                                     |   |  |

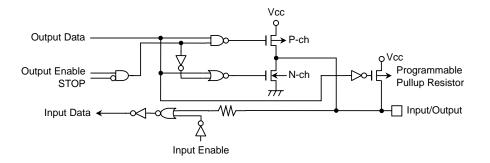

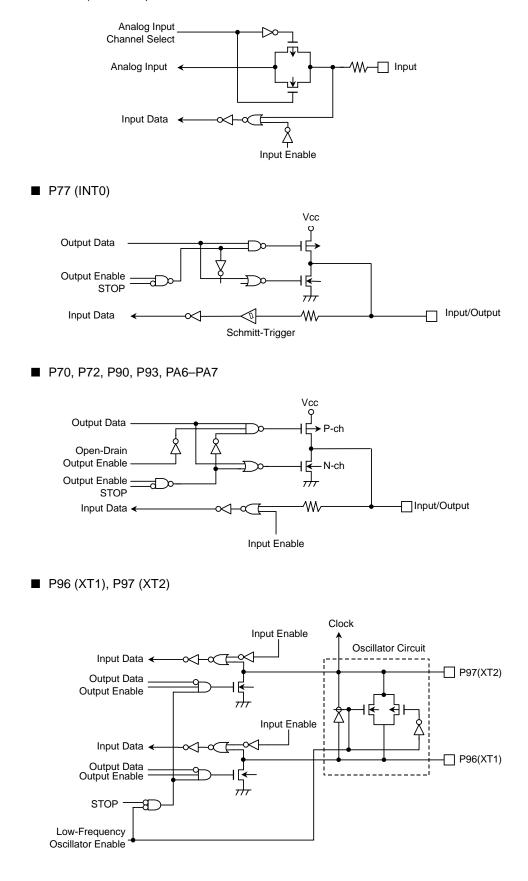

| 7. I/O Ports                                                                                                                        |   |  |

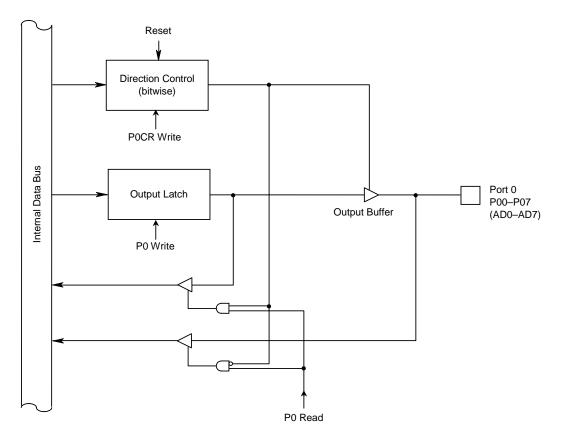

| 7.1 Port 0 (P00–P07)                                                                                                                |   |  |

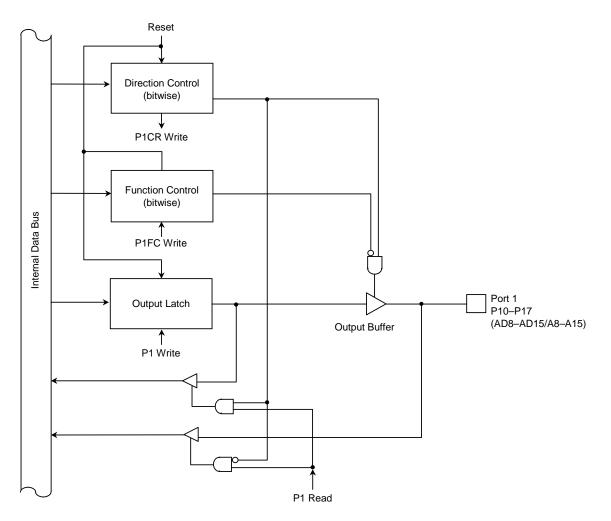

| 7.2 Port 1 (P10–P17)                                                                                                                |   |  |

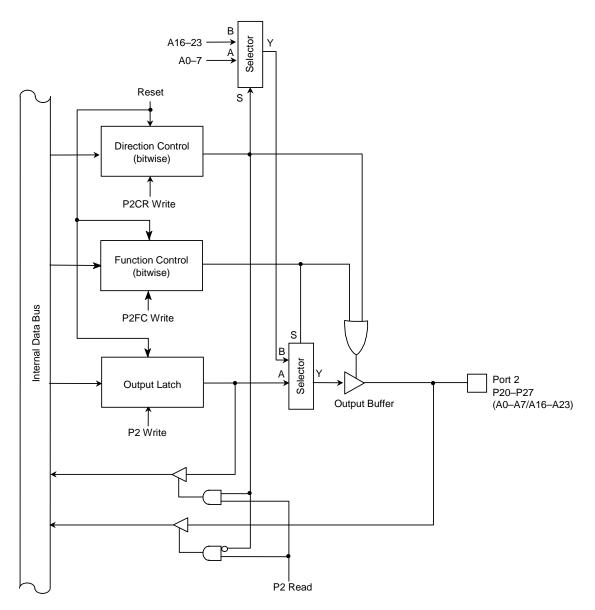

| 7.3 Port 2 (P20–P27)                                                                                                                |   |  |

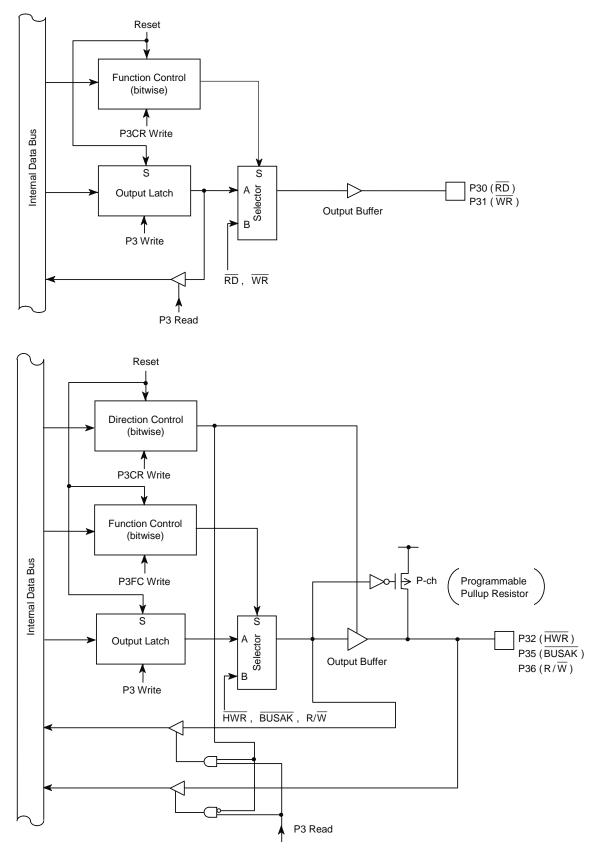

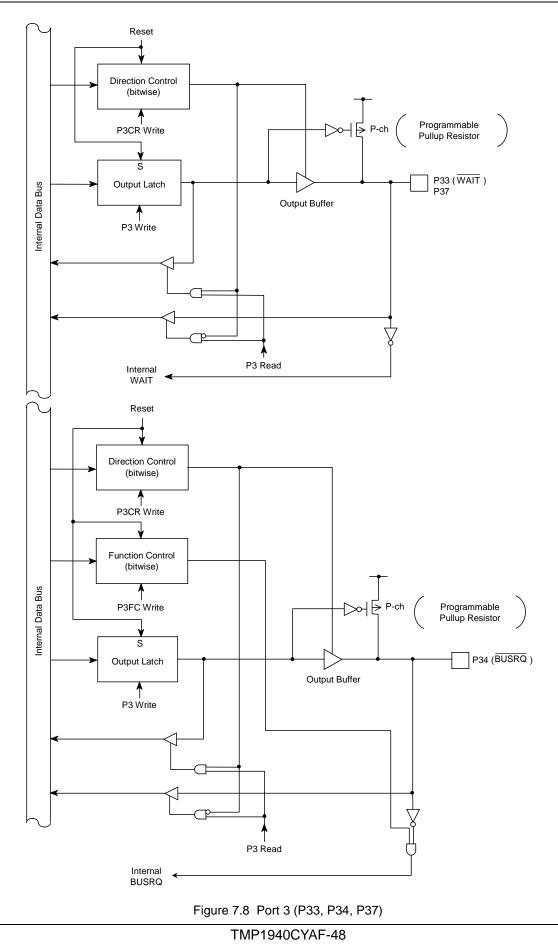

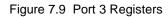

| 7.4 Port 3 (P30–P37)                                                                                                                |   |  |

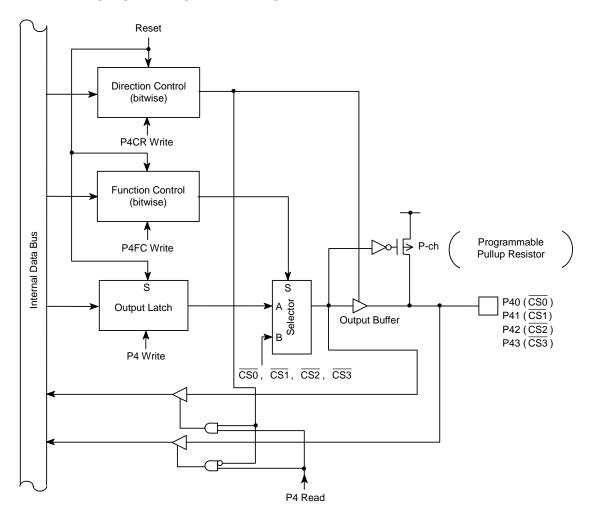

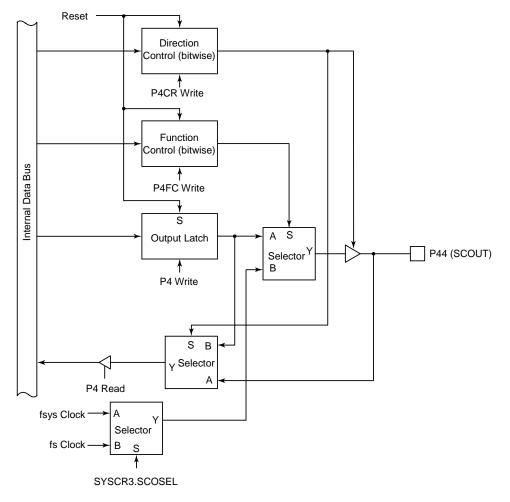

| 7.5 Port 4 (P40–P44)                                                                                                                |   |  |

|                                                                                                                                     |   |  |

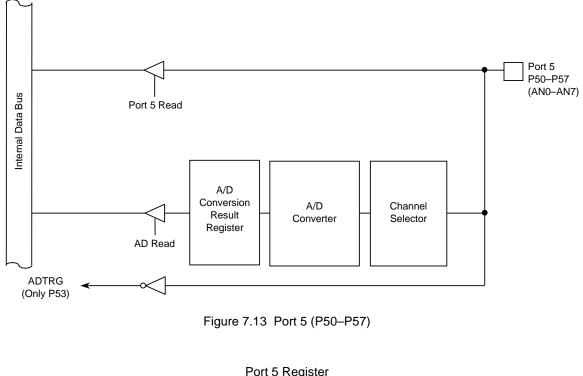

| 7.6 Port 5 (P50–P57)                                            |     |

|-----------------------------------------------------------------|-----|

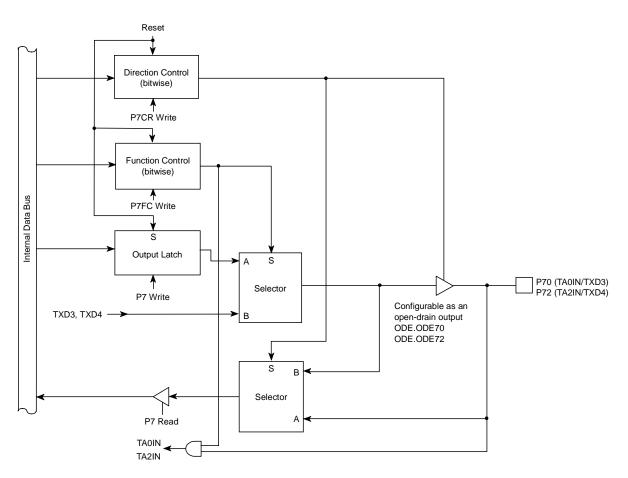

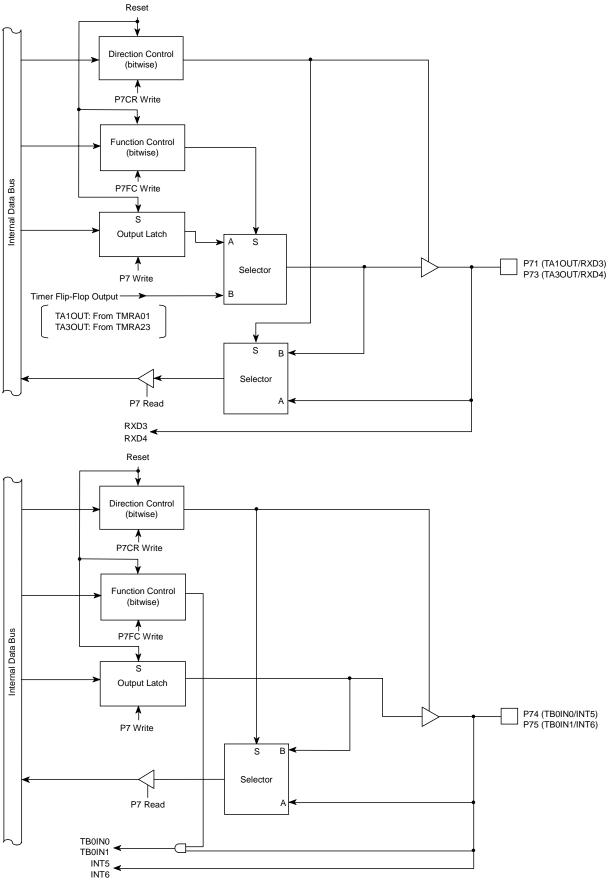

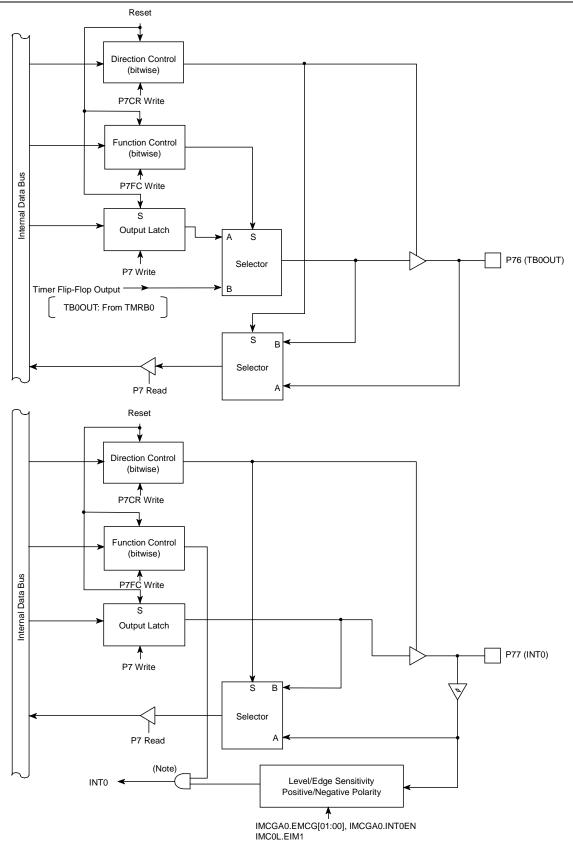

| 7.7 Port 7 (P70–P77)                                            |     |

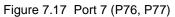

| 7.8 Port 8 (P80–P87)                                            |     |

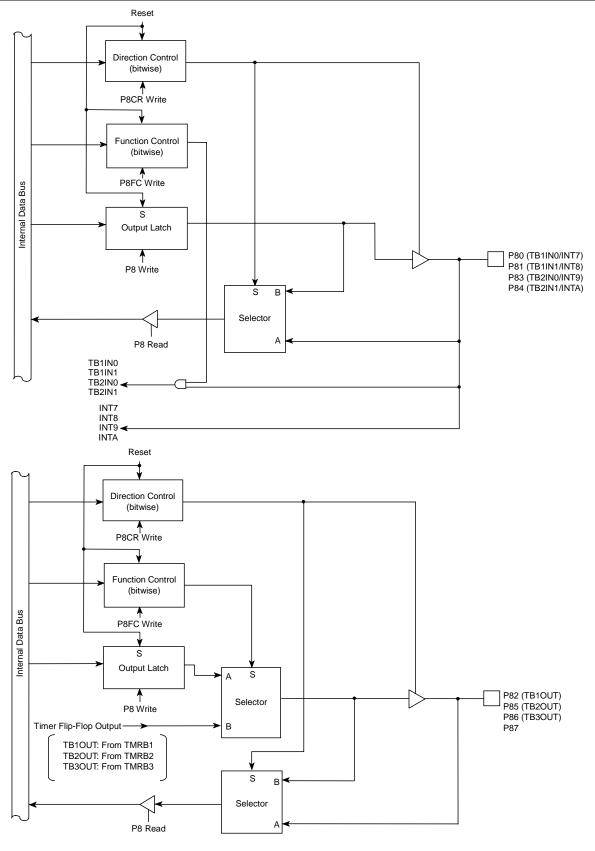

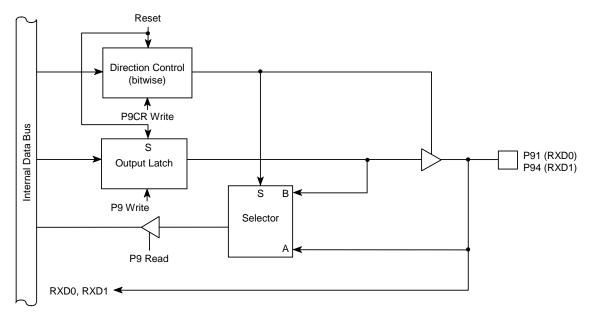

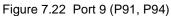

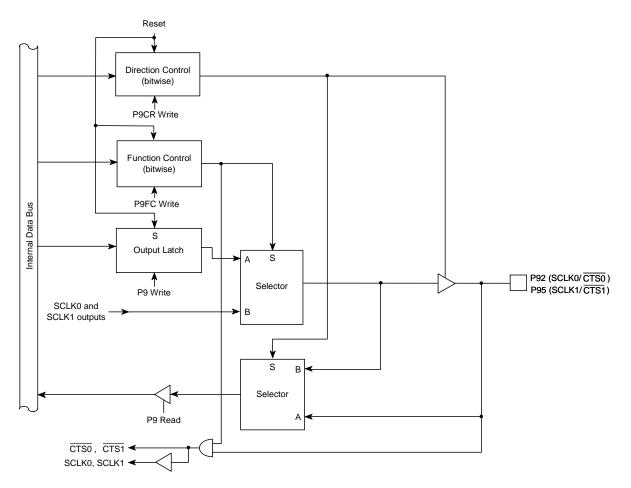

| 7.9 Port 9 (P90–P97)                                            |     |

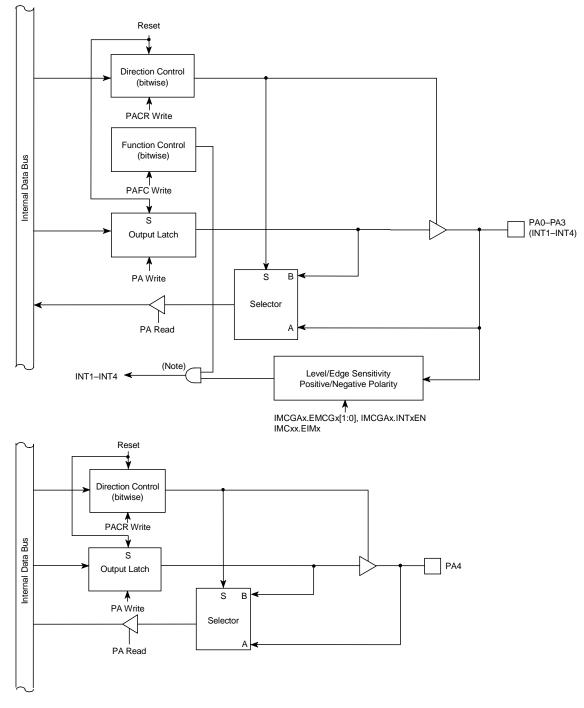

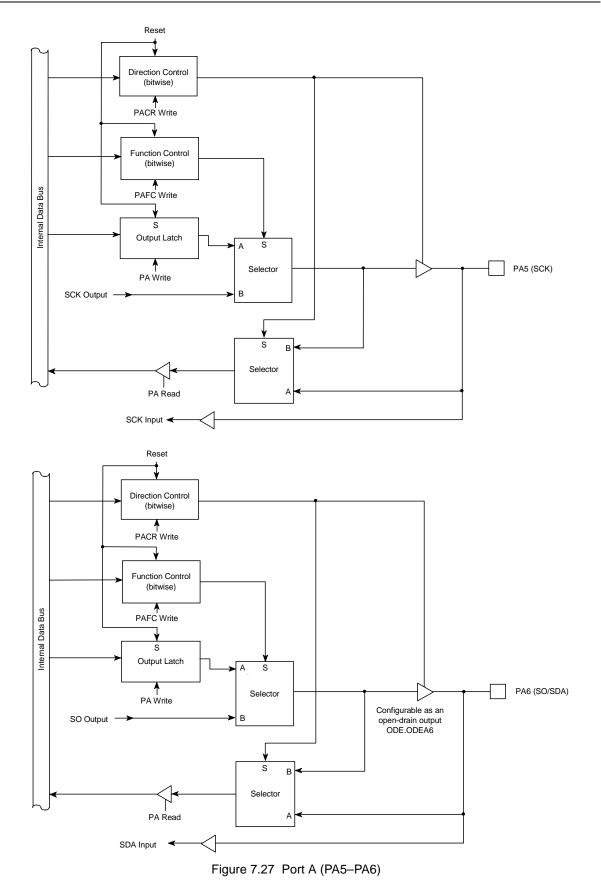

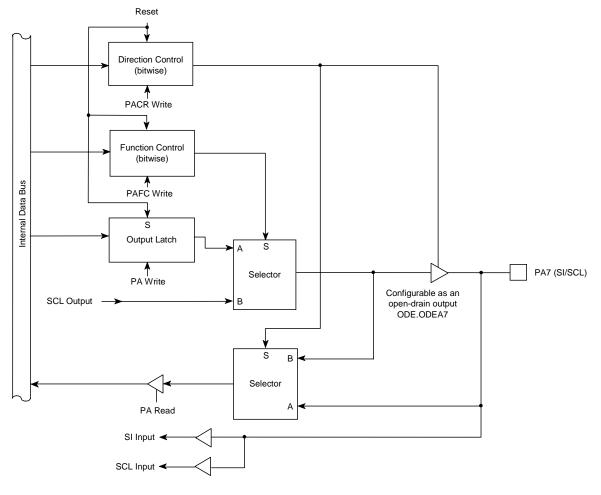

| 7.10 Port A (PA0–PA7)                                           |     |

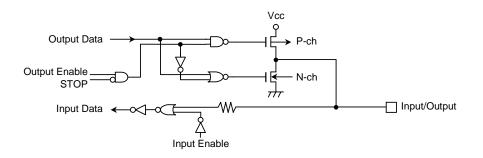

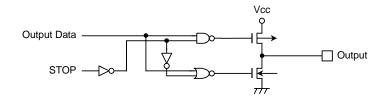

| 7.11 Open-Drain Output Control                                  |     |

|                                                                 |     |

| 8. External Bus Interface                                       |     |

| 8.1 Address and Data Buses                                      |     |

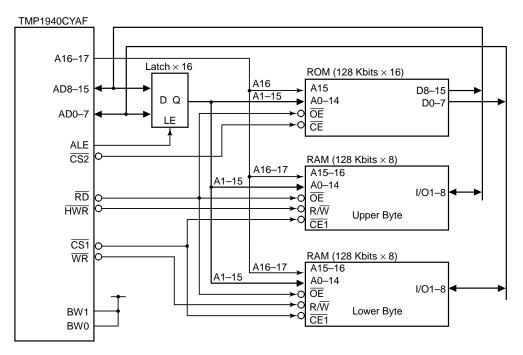

| 8.1.1 Supported Configurations                                  |     |

| 8.1.2 States of the Address Bus During On-Chip Address Accesses |     |

| 8.2 External Bus Operation                                      |     |

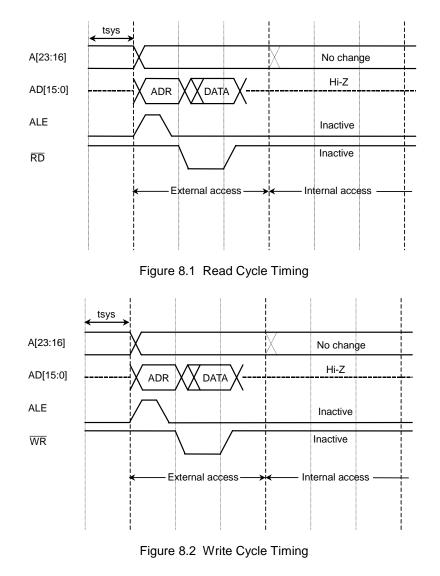

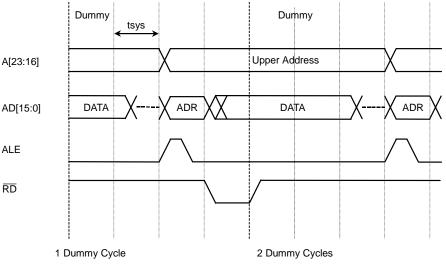

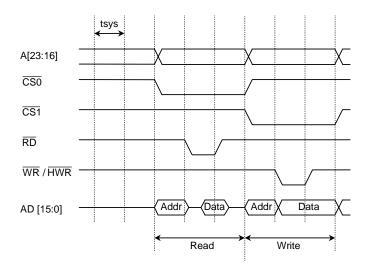

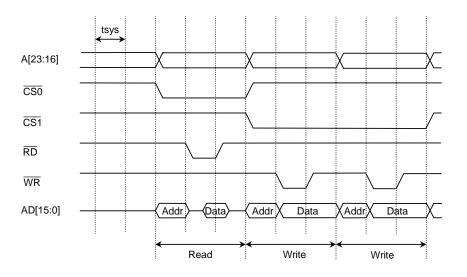

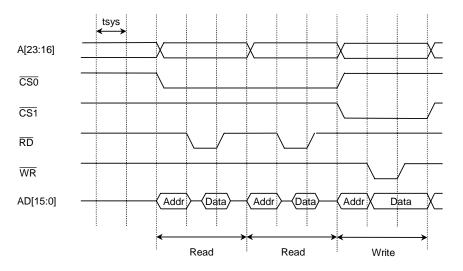

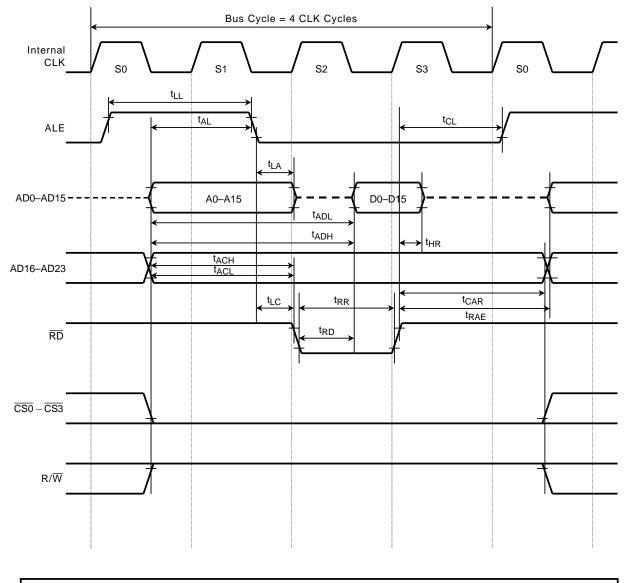

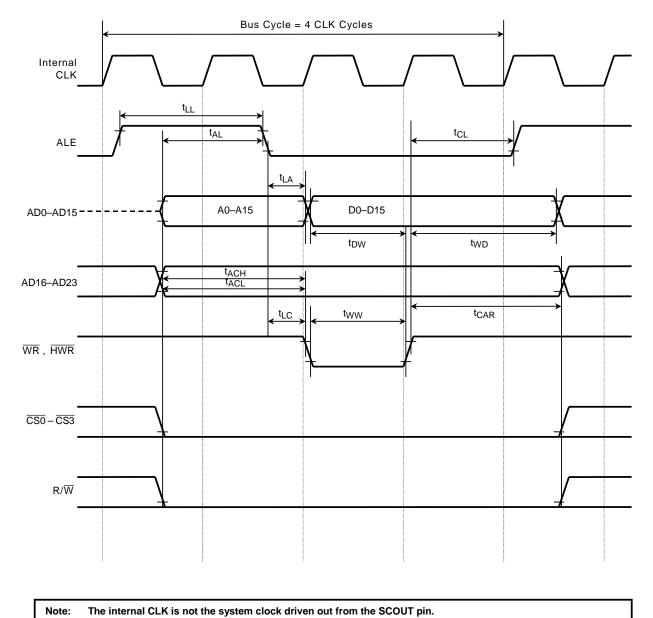

| 8.2.1 Basic Bus Operation                                       |     |

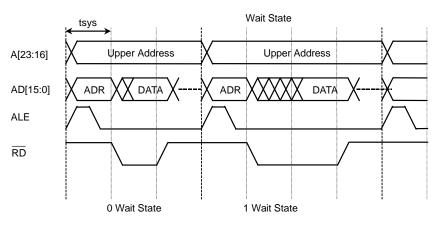

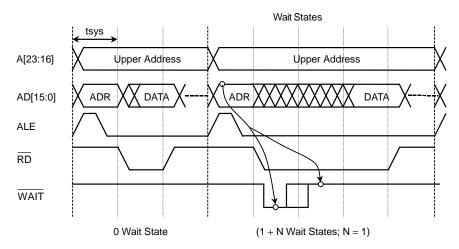

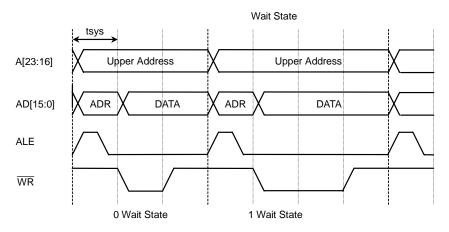

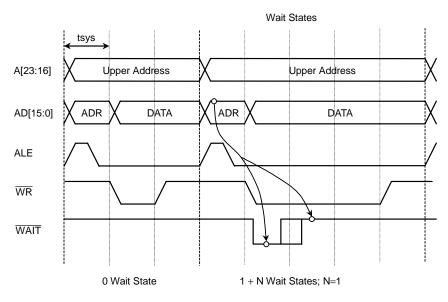

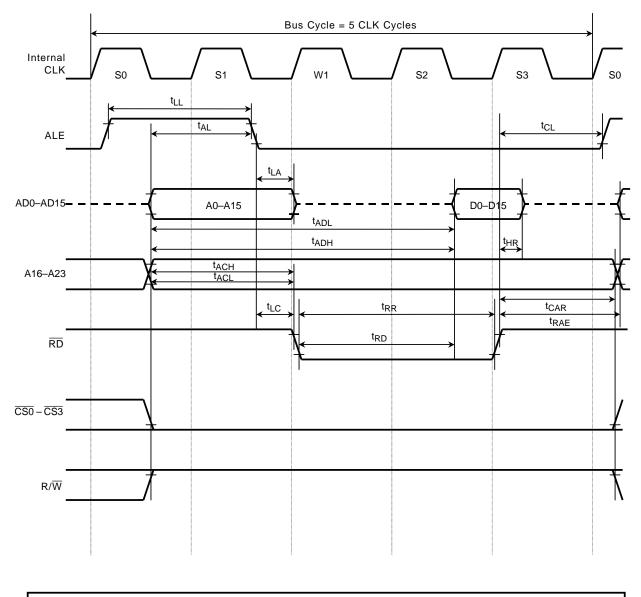

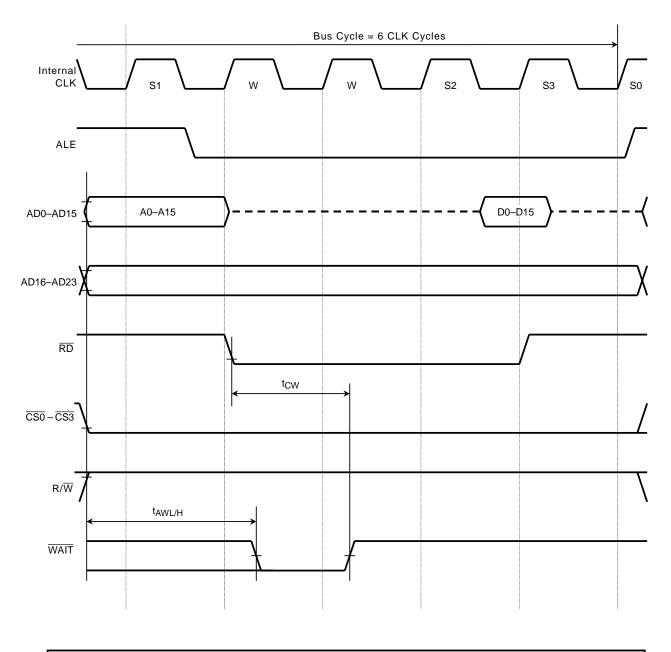

| 8.2.2 Wait Timing                                               |     |

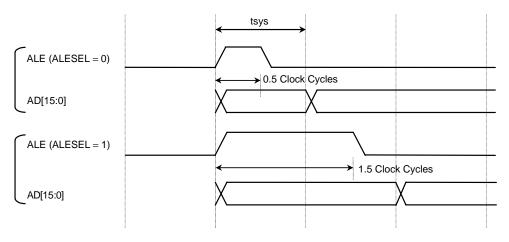

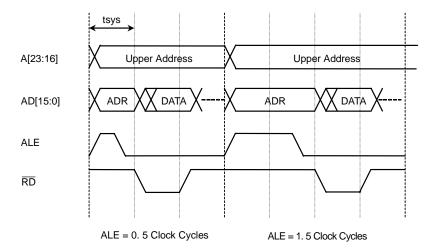

| 8.2.3 ALE Pulse Width                                           |     |

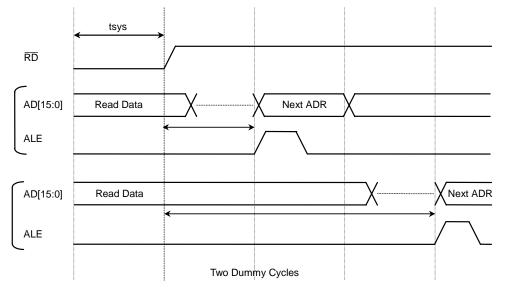

| 8.2.4 Read Recovery Time                                        |     |

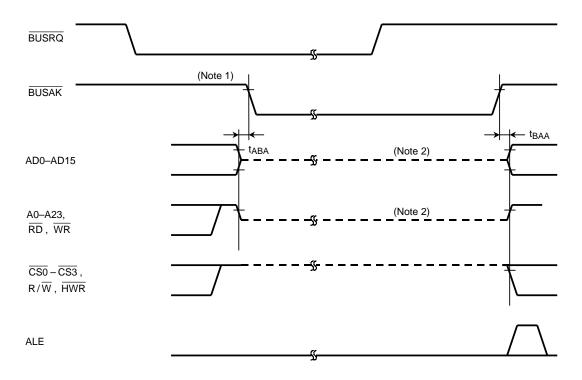

| 8.3 Bus Arbitration                                             |     |

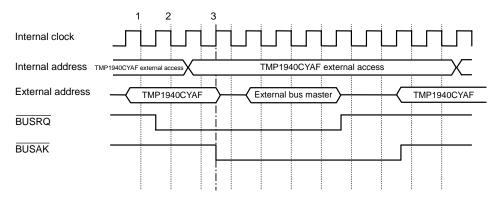

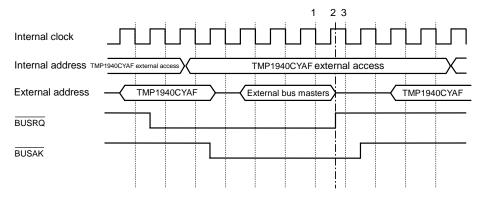

| 8.3.1 Bus Access Control                                        |     |

| 8.3.2 Bus Arbitration Flow                                      |     |

| 8.3.3 Relinquishing the bus                                     |     |

| 9. Chip Select/Wait Controller                                  | 81  |

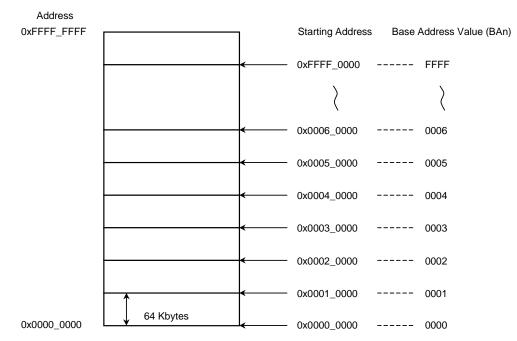

| 9.1 Programming Chip Select Ranges                              |     |

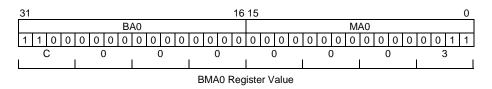

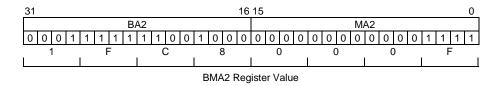

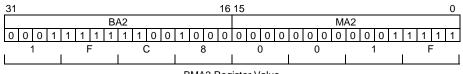

| 9.1.1 Base/Mask Address Registers (BMA0–BMA3)                   |     |

| 9.1.2 Base Address and Address Mask Value Calculations          |     |

| 9.2 Chip Select/Wait Control Registers                          |     |

| 9.3 Application Example                                         |     |

|                                                                 |     |

| 10. DMA Controller (DMAC)                                       |     |

| 10.1 Features                                                   |     |

| 10.2 Implementation                                             | 91  |

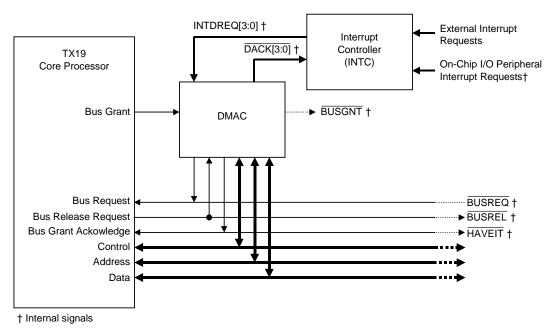

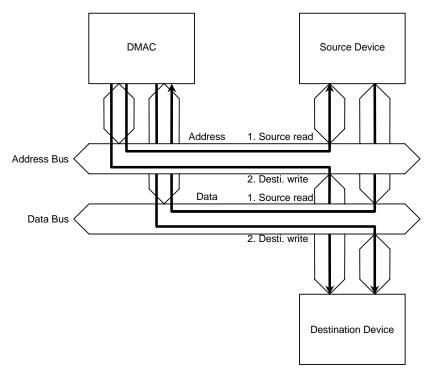

| 10.2.1 On-Chip DMAC Interface                                   |     |

| 10.2.2 DMAC Block                                               |     |

| 10.2.3 Bus Snooping                                             |     |

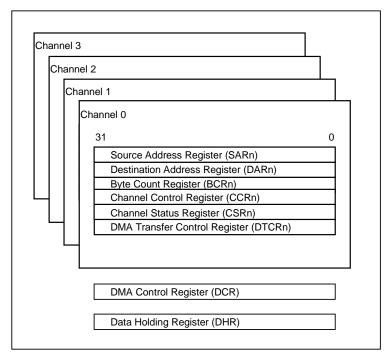

| 10.3 Register Description                                       |     |

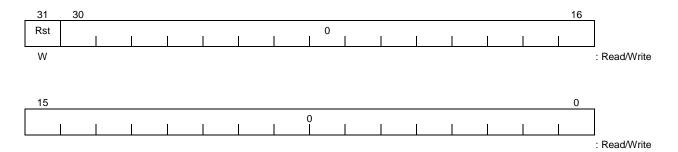

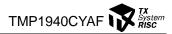

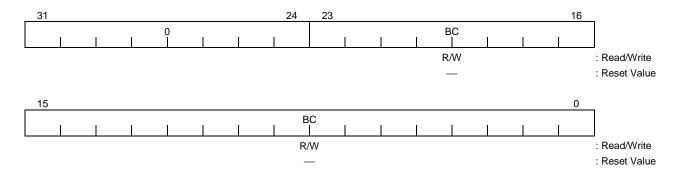

| 10.3.1 DMA Control Register (DCR)                               |     |

| 10.3.2 Channel Control Registers (CCRn)                         |     |

| 10.3.3 Channel Status Registers (CSRn)                          |     |

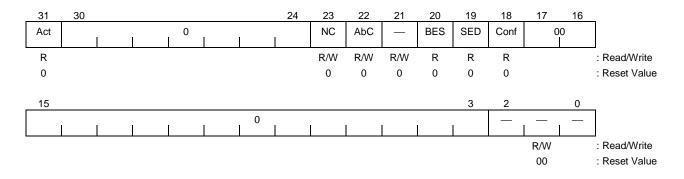

| 10.3.4 Source Address Registers (SARn)                          |     |

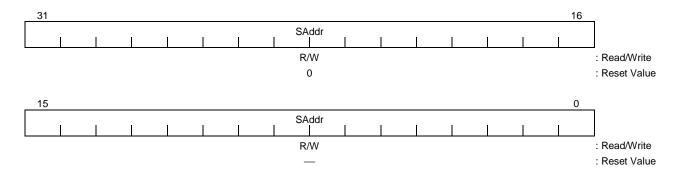

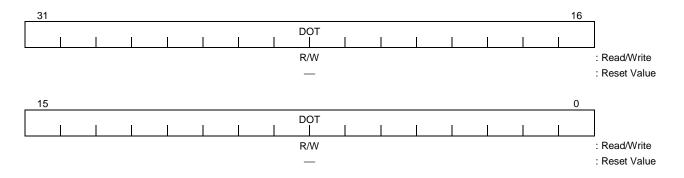

| 10.3.5 Destination Address Registers (DARn)                     |     |

| 10.3.6 Byte Count Registers (BCRn)                              |     |

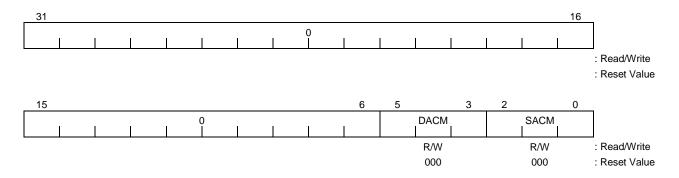

| 10.3.7 DMA Transfer Control Registers (DTCRn)                   |     |

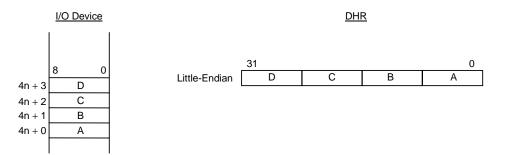

| 10.3.8 Data Holding Register (DHR)                              |     |

| 10.4 Operation                                                  |     |

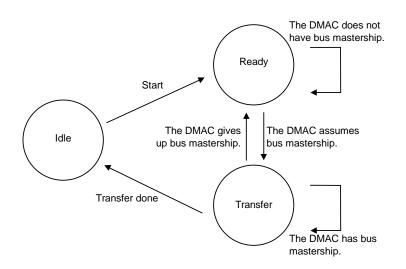

| 10.4.1 Overview                                                 |     |

| 10.4.2 Transfer Request Generation                              |     |

| 10.4.3 DMA Address Modes                                        |     |

| 10.4.4 DMA Channel Operation                                    |     |

| 10.4.5 DMA Channel Priority                                     |     |

| 10.4.6 Interrupts                                               |     |

| 10.4.7 Data Packing and Unpacking                               |     |

| 10.5 DMA Transfer Timing                                        |     |

| 10.5.1 Dual-Address Mode                                        |     |

| 10.6 Programming Example                                        |     |

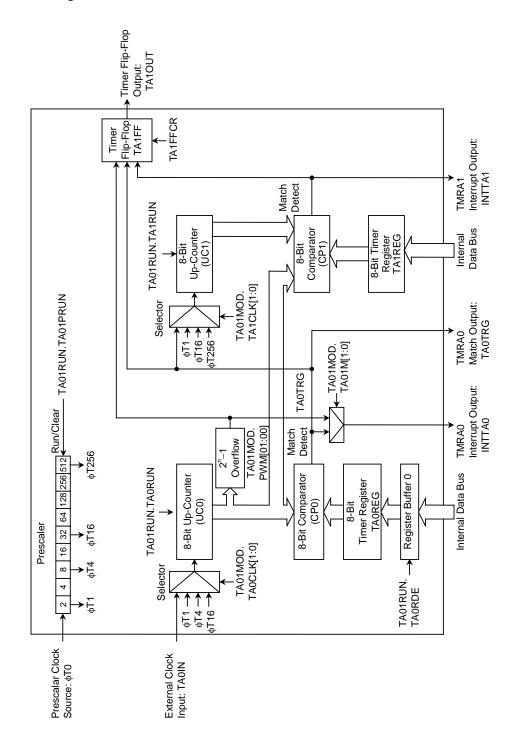

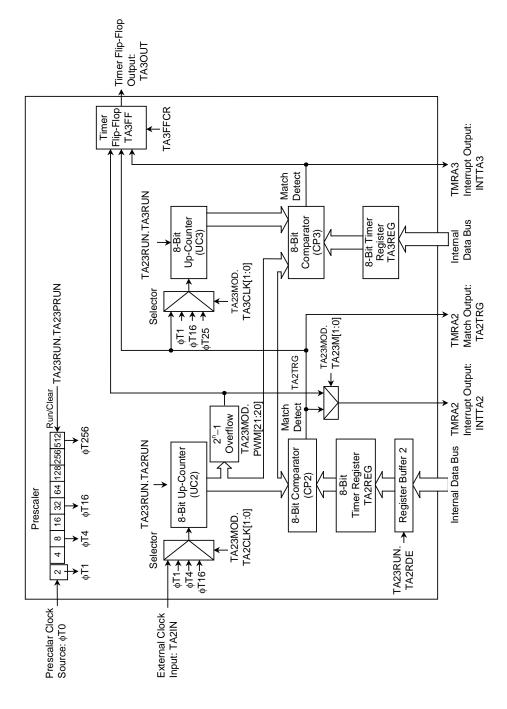

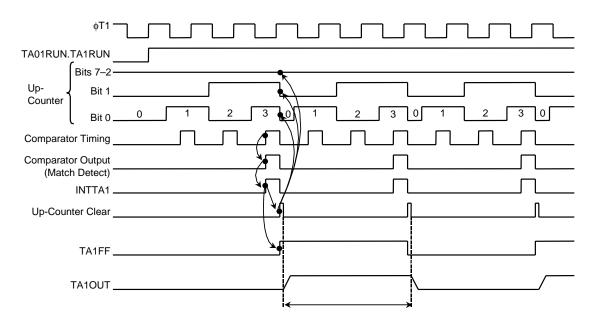

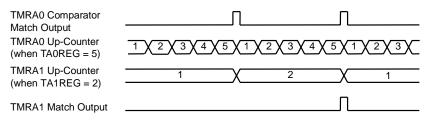

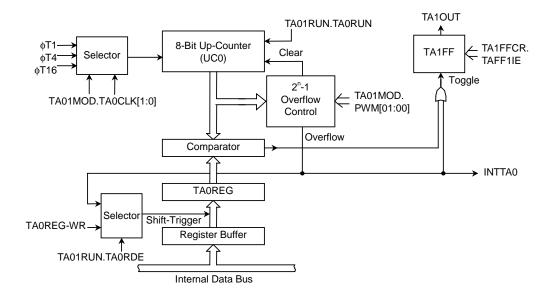

| 11. 8-Bit Timers (TMRAs)                                        | 115 |

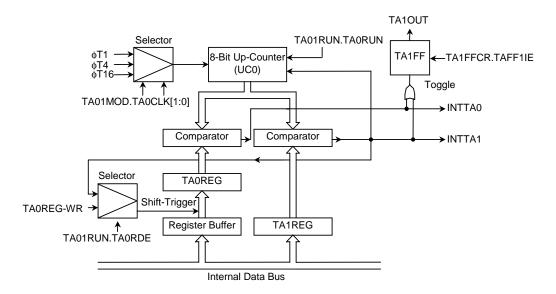

| 11.1 Block Diagrams                                             |     |

| 11.1 Block Diagrams                                             |     |

| 11.2 Third Components                                           |     |

| 11.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Prescaler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11.2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Up-Counters (UC0 and UC1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                    |

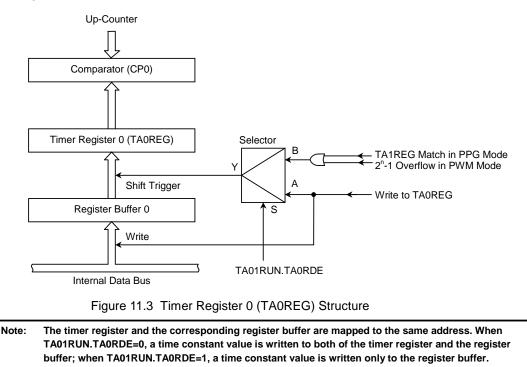

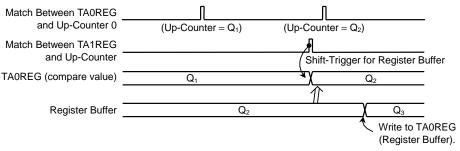

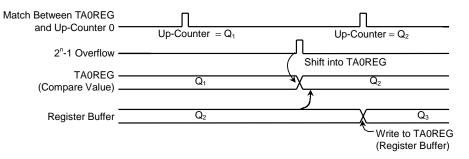

| 11.2.3                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Timer Registers (TA0REG and TA1REG)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                    |

| 11.2.4                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Comparators (CP0 and CP1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                    |

| 11.2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Timer Flip-Flop (TA1FF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ister Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                    |

| 11.4 Ope                                                                                                                                                                                                                                                                                                                                                                                                                                                | rating Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                    |

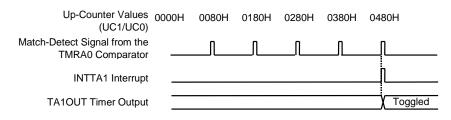

| 11.4.1                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8-Bit Interval Timer Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                    |

| 11.4.2                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 16-Bit Interval Timer Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                    |

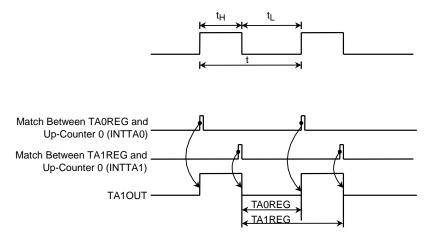

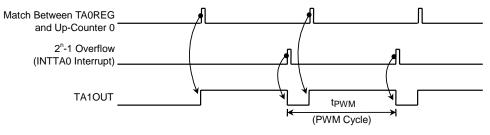

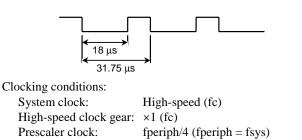

| 11.4.3                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8-Bit Programmable Pulse Generation (PPG) Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                    |

| 11.4.4                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8-Bit PWM Generation Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                    |

| 11.4.5                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Operating Mode Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                    |

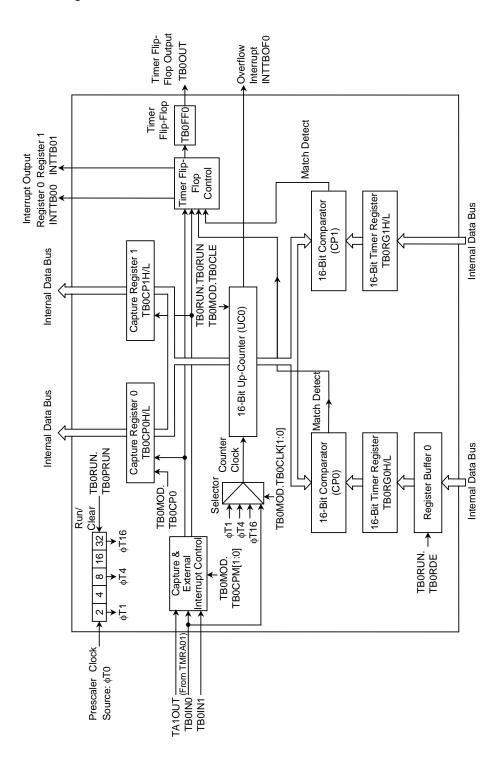

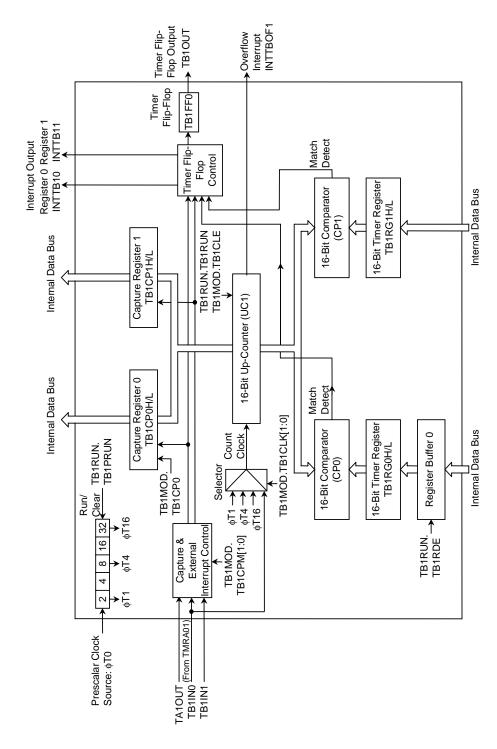

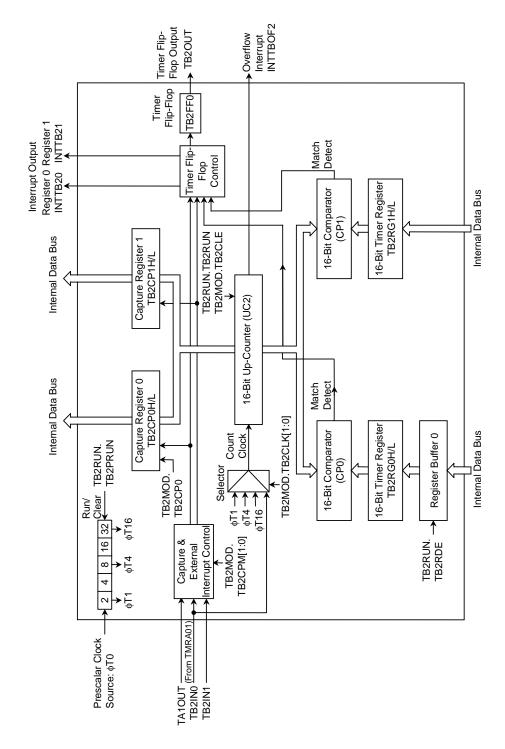

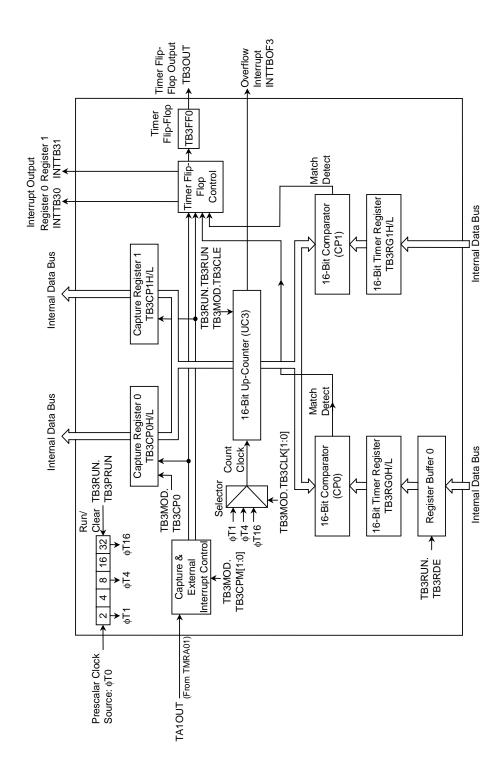

| 12 16-Bit                                                                                                                                                                                                                                                                                                                                                                                                                                               | Timer/Event Counters (TMRBs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 135                                                                                                                                                                                                                                                                                |

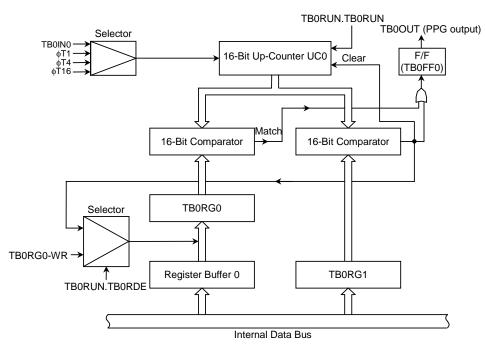

|                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ck Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                         | er Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                    |

| 12.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Prescaler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                    |

| 12.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Up-Counter (UC0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                    |

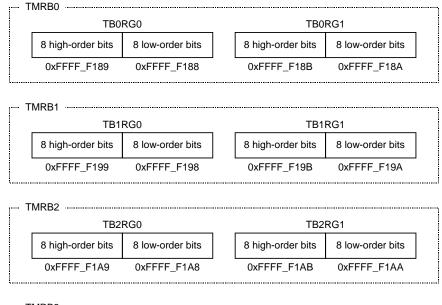

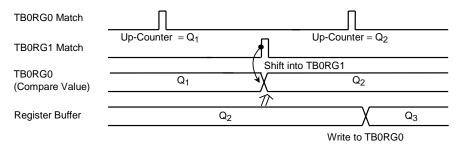

| 12.2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Timer Registers (TB0RG0H/L and TB0RG1H/L)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                    |

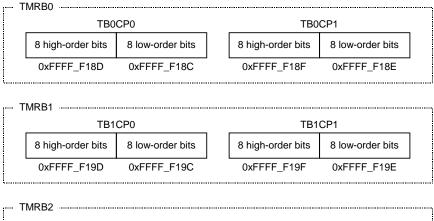

| 12.2.3                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Capture Registers (TB0CP0H/L and TB0CP1H/L).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                    |

| 12.2.4                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Capture Control Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                    |

| 12.2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Comparators (CP0 and CP1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                    |

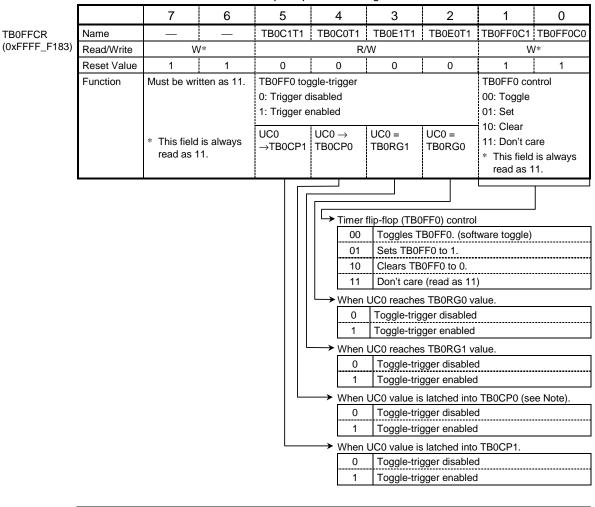

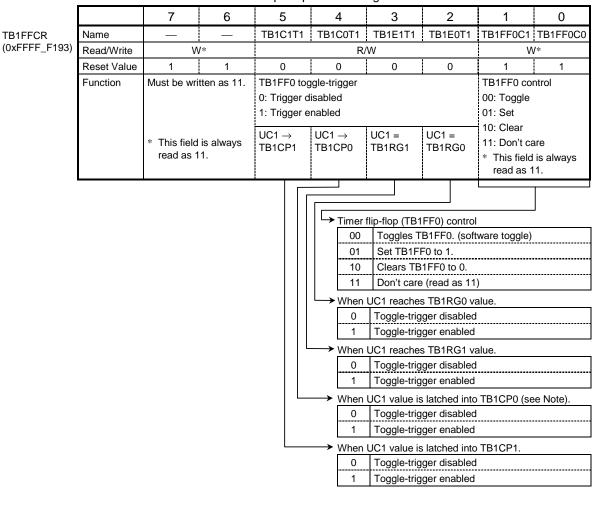

| 12.2.0                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Timer Flip-Flop (TB0FF0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ister Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                    |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                       | rating Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                    |

| 12.4.1                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 16-Bit Interval Timer Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                    |

| 12.4.2                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 16-Bit Event Counter Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                    |

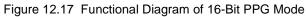

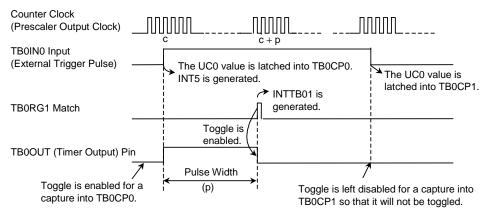

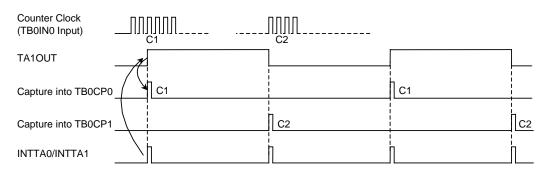

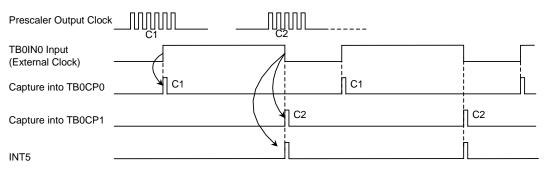

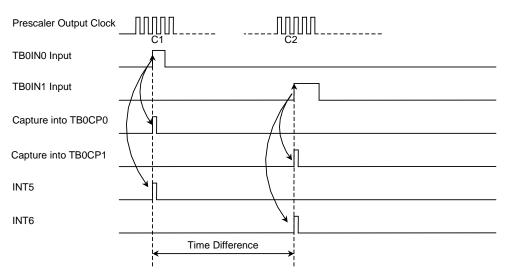

| 12.4.3                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 16-Bit Programmable Pulse Generation (PPG) Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                    |

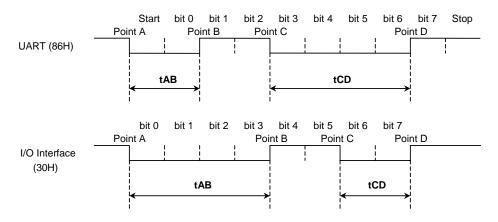

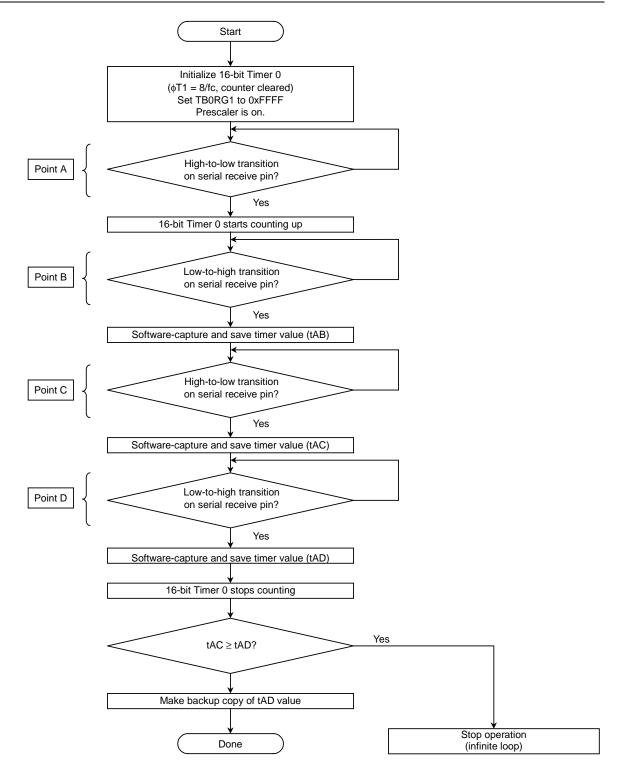

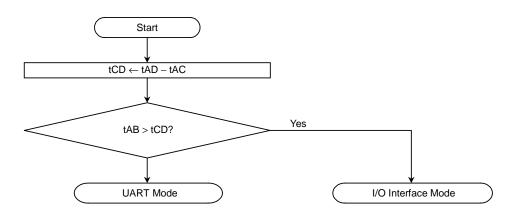

| 12.4.4                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Timing and Measurement Functions Using the Capture Capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                    |

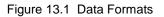

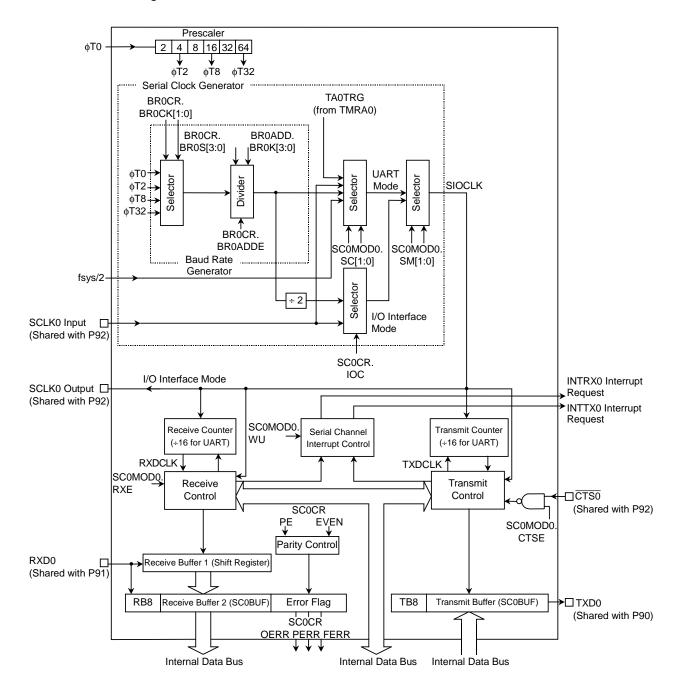

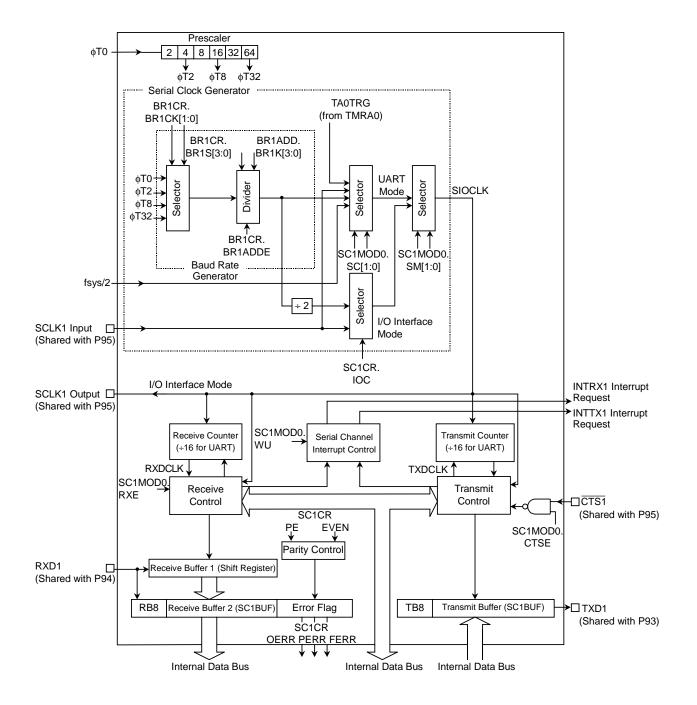

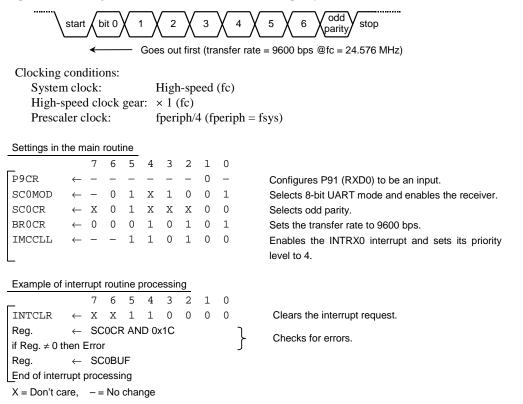

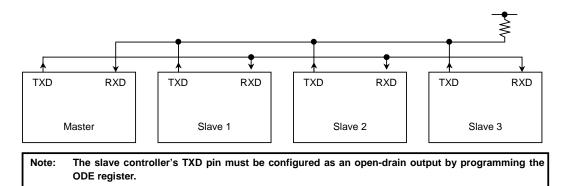

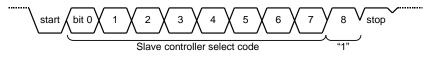

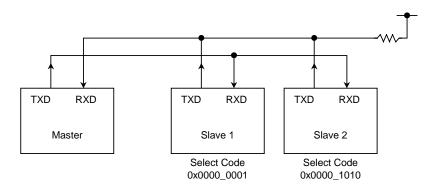

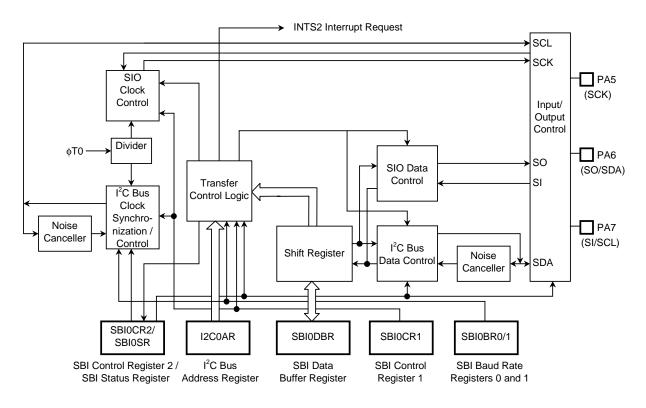

| 13. Serial I                                                                                                                                                                                                                                                                                                                                                                                                                                            | /O (SIO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                    |

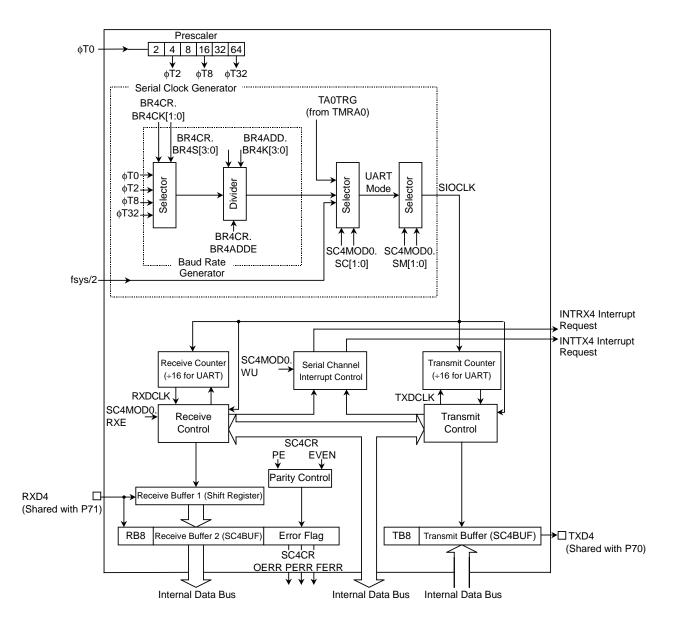

|                                                                                                                                                                                                                                                                                                                                                                                                                                                         | /O (SIO)<br>ck Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                    |

| 13.1 Blo                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                    |

| 13.1 Blo                                                                                                                                                                                                                                                                                                                                                                                                                                                | ck Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                    |

| 13.1 Blo<br>13.2 SIO                                                                                                                                                                                                                                                                                                                                                                                                                                    | ck Diagrams<br>Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 165<br>169<br>169                                                                                                                                                                                                                                                                  |

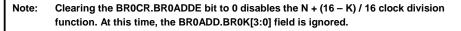

| 13.1 Blo<br>13.2 SIO<br>13.2.1                                                                                                                                                                                                                                                                                                                                                                                                                          | ck Diagrams<br>Components<br>Prescaler<br>Baud Rate Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                    |

| 13.1 Blo<br>13.2 SIC<br>13.2.1<br>13.2.2                                                                                                                                                                                                                                                                                                                                                                                                                | ck Diagrams<br>Components<br>Prescaler<br>Baud Rate Generator<br>Serial Clock Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                    |

| 13.1 Blo<br>13.2 SIO<br>13.2.1<br>13.2.2<br>13.2.3<br>13.2.4                                                                                                                                                                                                                                                                                                                                                                                            | ck Diagrams<br>Components<br>Prescaler<br>Baud Rate Generator<br>Serial Clock Generator<br>Receive Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                    |

| 13.1 Blo<br>13.2 SIC<br>13.2.1<br>13.2.2<br>13.2.3<br>13.2.4<br>13.2.5                                                                                                                                                                                                                                                                                                                                                                                  | ck Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                    |

| 13.1 Blo<br>13.2 SIO<br>13.2.1<br>13.2.2<br>13.2.3<br>13.2.4                                                                                                                                                                                                                                                                                                                                                                                            | ck Diagrams<br>Components<br>Prescaler<br>Baud Rate Generator<br>Serial Clock Generator<br>Receive Counter<br>Receive Controller<br>Receive Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                    |

| 13.1 Blo<br>13.2 SIC<br>13.2.1<br>13.2.2<br>13.2.3<br>13.2.4<br>13.2.5<br>13.2.6                                                                                                                                                                                                                                                                                                                                                                        | ck Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                    |

| 13.1 Blo<br>13.2 SIO<br>13.2.1<br>13.2.2<br>13.2.3<br>13.2.4<br>13.2.5<br>13.2.6<br>13.2.7<br>13.2.8                                                                                                                                                                                                                                                                                                                                                    | ck Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 165<br>169<br>170<br>173<br>173<br>173<br>173<br>173<br>173<br>174<br>174                                                                                                                                                                                                          |

| 13.1 Blo<br>13.2 SIO<br>13.2.1<br>13.2.2<br>13.2.3<br>13.2.4<br>13.2.5<br>13.2.6<br>13.2.7<br>13.2.8<br>13.2.9                                                                                                                                                                                                                                                                                                                                          | ck Diagrams<br>Components<br>Prescaler<br>Baud Rate Generator<br>Serial Clock Generator<br>Receive Counter<br>Receive Controller<br>Receive Buffer<br>Transmit Counter<br>Transmit Controller<br>Transmit Controller                                                                                                                                                                                                                                                                                                                                                                | 165<br>169<br>170<br>173<br>173<br>173<br>173<br>173<br>173<br>173<br>174<br>174<br>176                                                                                                                                                                                            |

| 13.1 Blo<br>13.2 SIO<br>13.2.1<br>13.2.2<br>13.2.3<br>13.2.4<br>13.2.5<br>13.2.6<br>13.2.7<br>13.2.8<br>13.2.9<br>13.2.10                                                                                                                                                                                                                                                                                                                               | ck Diagrams<br>Components<br>Prescaler<br>Baud Rate Generator<br>Serial Clock Generator<br>Receive Counter<br>Receive Controller<br>Receive Buffer<br>Transmit Counter<br>Transmit Controller<br>Transmit Buffer<br>Parity Controller                                                                                                                                                                                                                                                                                                                                               | 165<br>169<br>169<br>170<br>173<br>173<br>173<br>173<br>173<br>173<br>174<br>174<br>176<br>176                                                                                                                                                                                     |

| 13.1 Blo<br>13.2 SIO<br>13.2.1<br>13.2.2<br>13.2.3<br>13.2.4<br>13.2.5<br>13.2.6<br>13.2.7<br>13.2.8<br>13.2.9<br>13.2.10<br>13.2.11                                                                                                                                                                                                                                                                                                                    | ck Diagrams<br>Components<br>Prescaler<br>Baud Rate Generator<br>Serial Clock Generator<br>Receive Counter<br>Receive Controller<br>Receive Buffer<br>Transmit Counter<br>Transmit Counter<br>Transmit Controller<br>Parity Controller<br>Error Flags (UART mode only)                                                                                                                                                                                                                                                                                                              | 165<br>169<br>169<br>170<br>173<br>173<br>173<br>173<br>173<br>173<br>173<br>174<br>174<br>176<br>176<br>176                                                                                                                                                                       |

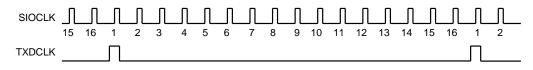

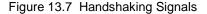

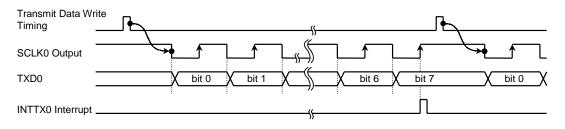

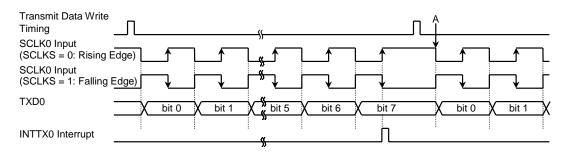

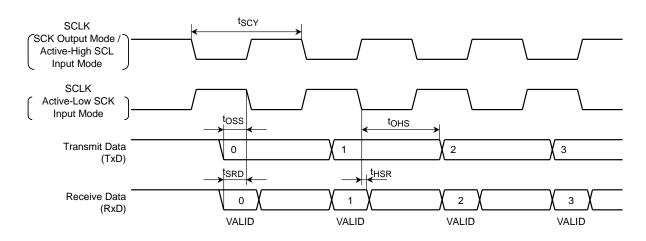

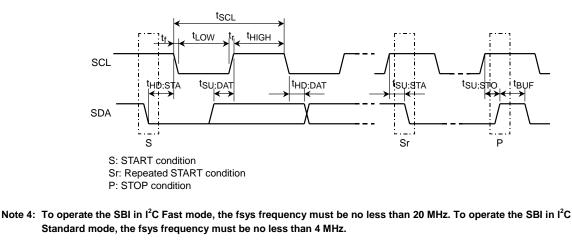

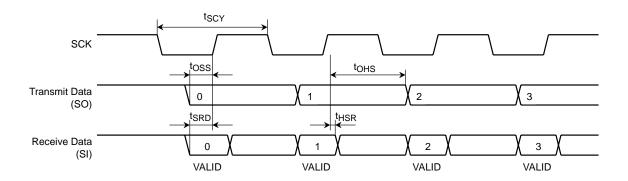

| 13.1 Blo<br>13.2 SIO<br>13.2.1<br>13.2.2<br>13.2.3<br>13.2.4<br>13.2.5<br>13.2.6<br>13.2.7<br>13.2.8<br>13.2.9<br>13.2.10<br>13.2.11<br>13.2.12                                                                                                                                                                                                                                                                                                         | ck Diagrams<br>Components<br>Prescaler<br>Baud Rate Generator<br>Serial Clock Generator<br>Receive Counter<br>Receive Controller<br>Receive Buffer<br>Transmit Counter<br>Transmit Counter<br>Transmit Controller<br>Parity Controller<br>Error Flags (UART mode only)<br>Signal Generation Timing                                                                                                                                                                                                                                                                                  | $\begin{array}{c} 165 \\ 169 \\ 169 \\ 170 \\ 173 \\ 173 \\ 173 \\ 173 \\ 173 \\ 173 \\ 174 \\ 174 \\ 174 \\ 174 \\ 176 \\ 176 \\ 176 \\ 177 \end{array}$                                                                                                                          |

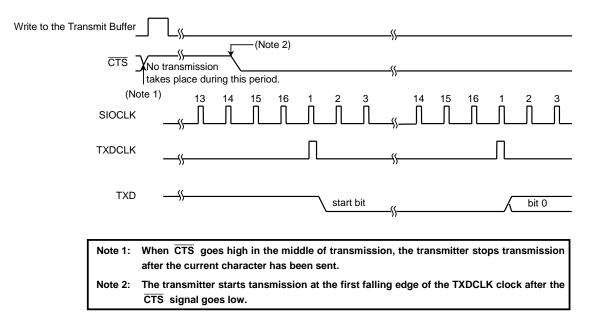

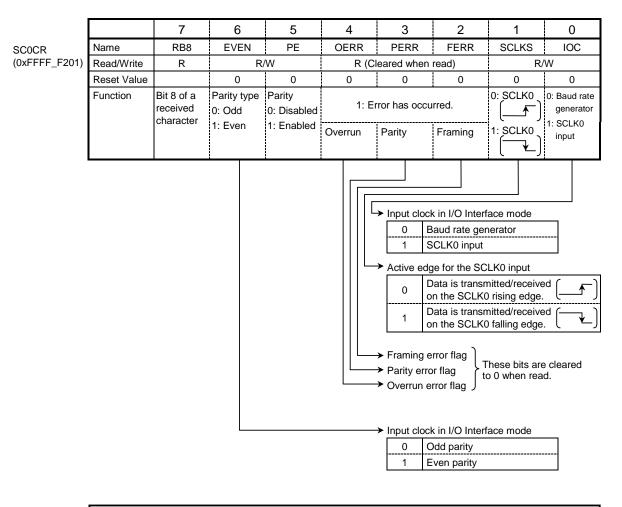

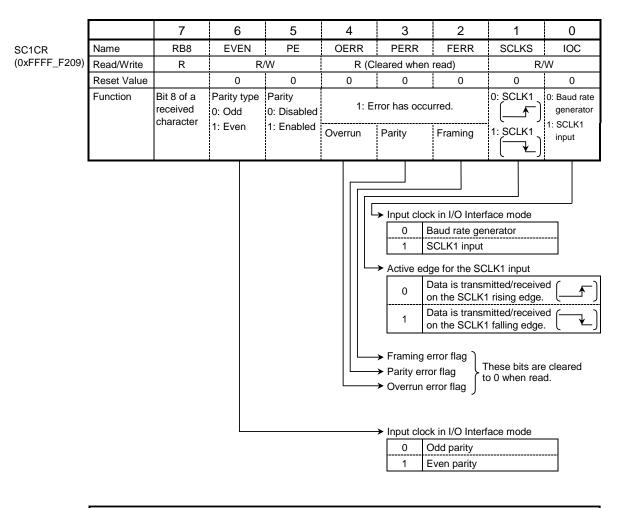

| 13.1 Blo<br>13.2 SIO<br>13.2.1<br>13.2.2<br>13.2.3<br>13.2.4<br>13.2.5<br>13.2.6<br>13.2.7<br>13.2.8<br>13.2.9<br>13.2.10<br>13.2.11<br>13.2.12<br>13.3 Reg                                                                                                                                                                                                                                                                                             | ck Diagrams<br>Components<br>Prescaler<br>Baud Rate Generator<br>Serial Clock Generator<br>Receive Counter<br>Receive Controller<br>Receive Buffer<br>Transmit Counter<br>Transmit Controller<br>Transmit Buffer<br>Parity Controller<br>Error Flags (UART mode only)<br>Signal Generation Timing                                                                                                                                                                                                                                                                                   | 165           169           169           170           173           173           173           173           173           173           173           173           174           176           176           177           178                                                |

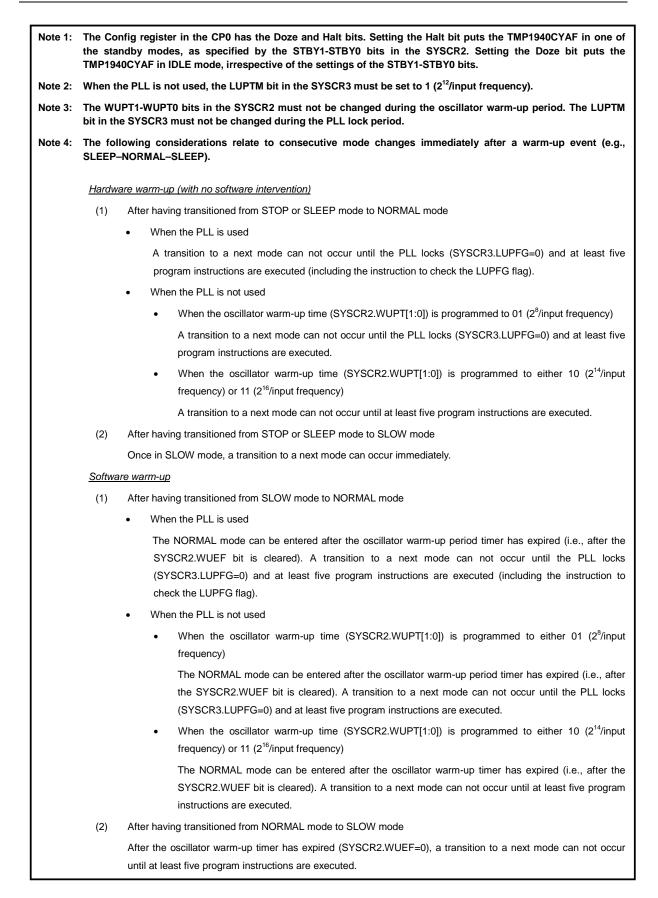

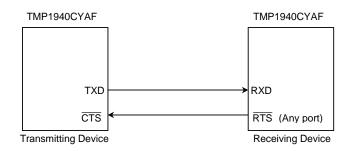

| 13.1 Blo<br>13.2 SIO<br>13.2.1<br>13.2.2<br>13.2.3<br>13.2.4<br>13.2.5<br>13.2.6<br>13.2.7<br>13.2.8<br>13.2.9<br>13.2.10<br>13.2.11<br>13.2.12<br>13.3 Reg<br>13.4 Opt                                                                                                                                                                                                                                                                                 | ck Diagrams<br>Components<br>Prescaler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 165           169           169           170           173           173           173           173           173           173           173           173           174           174           176           176           177           178           192                    |