#### CMOS 4-BIT MICROCONTROLLER

## TMP47C456AF

The 47C456A is a high speed and high performance 4-bit single chip microcomputer based on the TLCS-47 CMOS series. The 47C456A has LCD driver, DTMF generator and large-capacity RAM for repertory dial, which is suitable for application in telephones. The 47C456A has two oscillation circuits. It is possible to switch the operating mode; high speed operation.

| PART   | No.    | ROM          | RAM         | PACKAGE | PIGGYBACK   |

|--------|--------|--------------|-------------|---------|-------------|

| TMP470 | 1456AF | 4096 x 8-bit | 768 × 4-bit | QFP80   | TMP47C956AG |

#### **FEATURES**

- ◆4-bit single chip microcomputer

- ◆Instruction execution time:

8.3µs (at 960KHz), 244µs (at 32.8KHz)

- ◆Low voltage operation: 2.7V min.

- ♦90 basic instructions

- ◆ Table look-up instructions

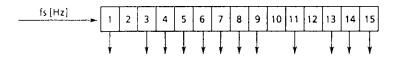

- ◆ Subroutine nesting: 15 levels max.

- ♦6 interrupt sources (External: 2, Internal: 4)

All sources have independent latches each, and multiple interrupt control is available.

- ◆I/O port (34 pins)

- Input 1 port 4 pins

I/O 7 ports 27 pins

- Output 1 port 3 pins

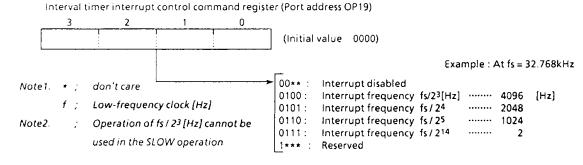

- ♦Interval Timer

- ◆Two 12-bit Timer/Counters

Timer, event counter, and pulse width measurement mode

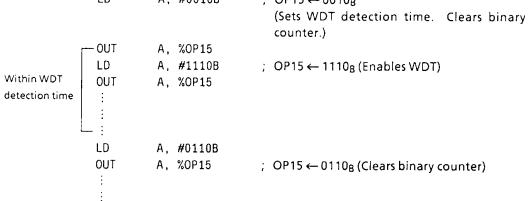

- ◆Watchdog Timer

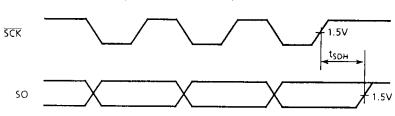

- ◆ Serial Interface with 4-bit buffer

External/internal clock, and leading/trailing edge shift mode

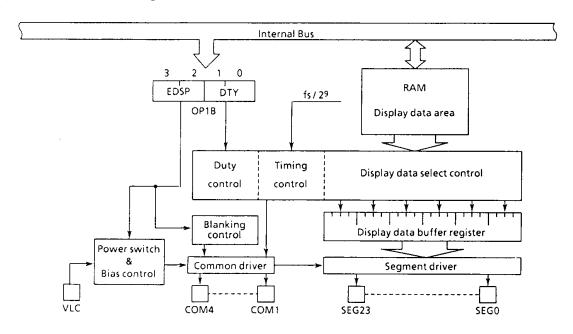

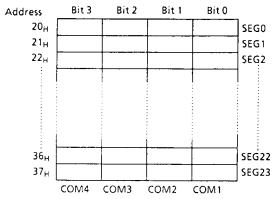

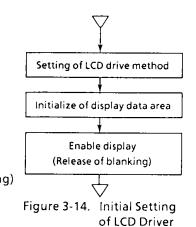

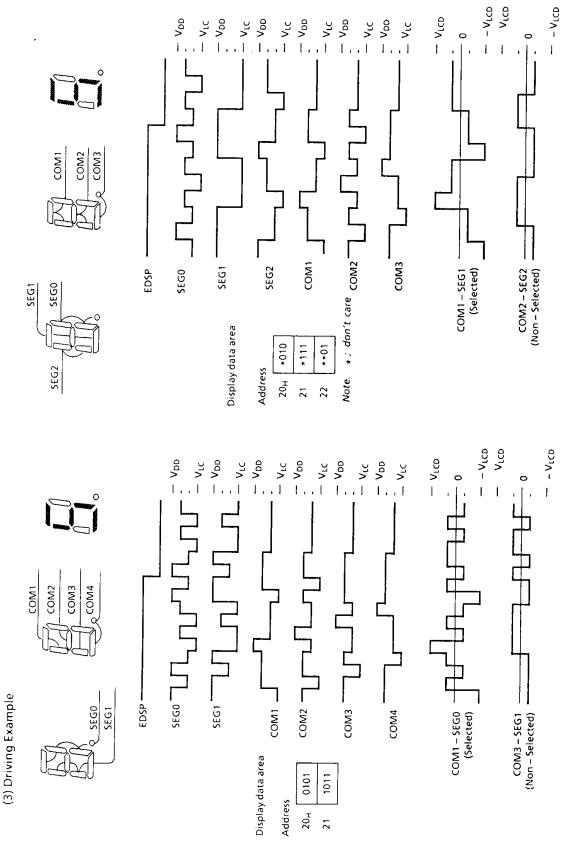

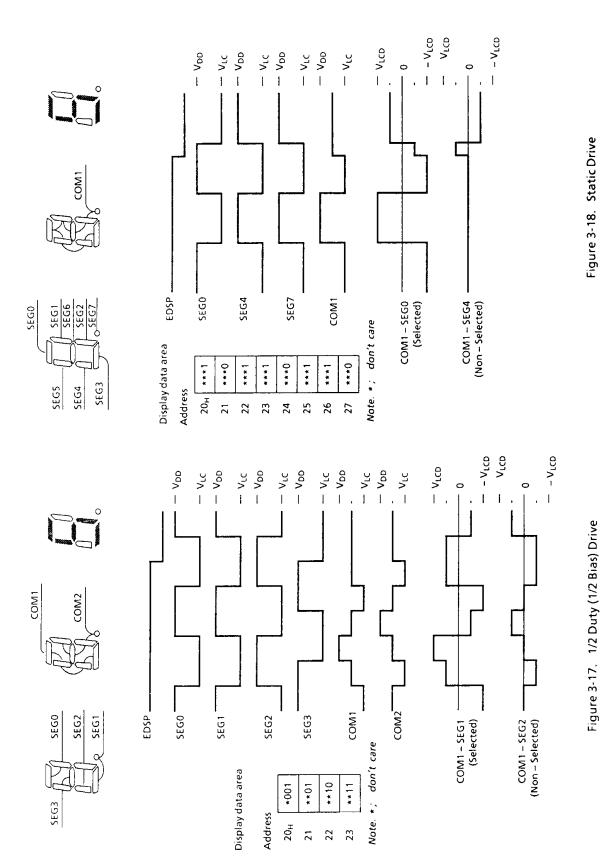

- ◆ LCD driver (automatic display)

- LCD direct drive (Max.16-digit display at 1/4 duty LCD)

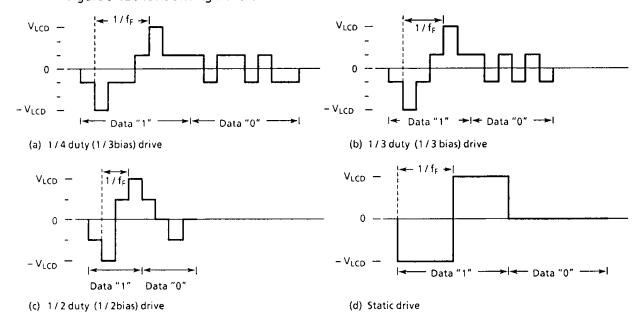

- 1/4, 1/3, 1/2 duties or static drive are programmably selectable.

- ◆DTMF (Dual Tone Multi Frequency) output

- DTMF output with one instruction

- Single tone output function

- $\Rightarrow$  RAM for repartry dial : 768  $\times$  4-bit max.

- **◆BEEP** output function

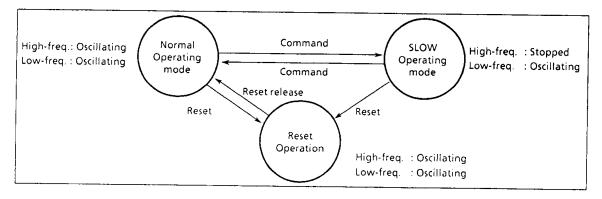

- ◆ Dual-clock operation

High-speed/Low-power-consumption operating mode

◆Real Time Emulator: BM47216A

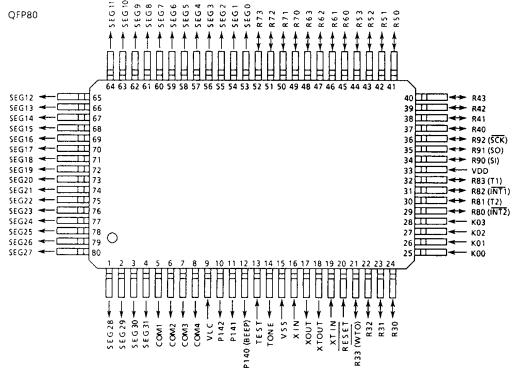

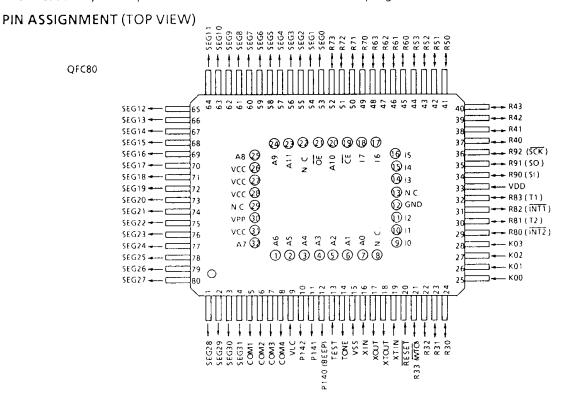

## PIN ASSIGNMENT (TOP VIEW)

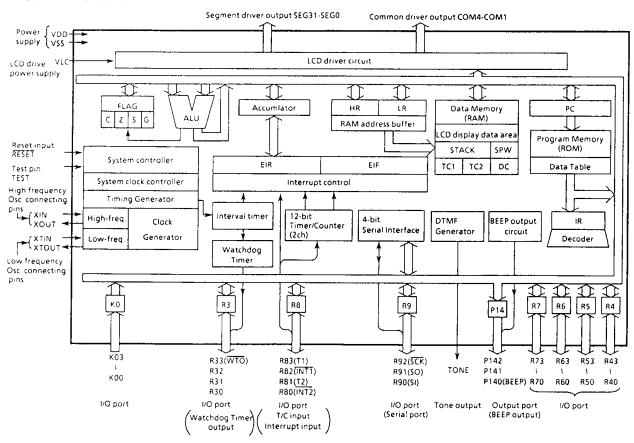

#### **BLOCK DIAGRAM**

# PIN FUNCTION

| PIN NAME               | Input/Output    | FUNCTIONS                                                                      | <u> </u>                       |

|------------------------|-----------------|--------------------------------------------------------------------------------|--------------------------------|

| K03 - K00              | Input           | 4-bit input port                                                               |                                |

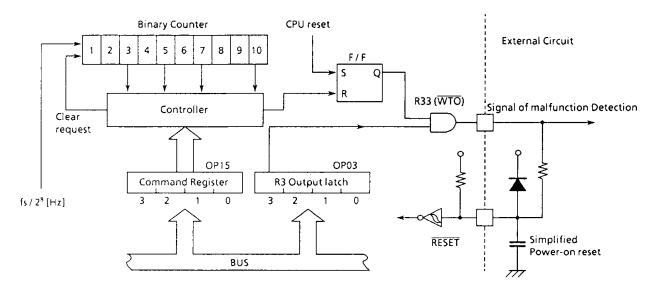

| R33 ( <del>WTO</del> ) | I/O (Output)    | 4-bit I/O port with latch.  When used as the input port, the latch must be     | Watchdog timer output          |

| R32 - R30              | 1/0             | set to "1".                                                                    |                                |

| R43 - R40              |                 |                                                                                |                                |

| R53 - R50              |                 | 4-bit I/O port with latch.                                                     |                                |

| R63 - R60              | 1/0             | When used as the input port, the latch must be s                               | et to "1".                     |

| R73 - R70              |                 |                                                                                |                                |

| R83 (T1)               |                 | 4-bit I/O port with latch.                                                     | Timer/Counter 1 external input |

| R82 (ĪNT1)             |                 | When used as the input port, external                                          | External interrupt 1 input     |

| R81 (T2)               | !/O (Input)     | interrupt input pin, or timer/counter input pin, the latch must be set to "1". | Timer/Counter 2 external input |

| R80 (ĪNT2)             |                 |                                                                                | External interrupt 2 input     |

| R92 (ŠČK)              | 1/0 (1/0)       | 3-bit I/O port with latch.                                                     | Serial clock I/O               |

| R91 (SO)               | I/O (Output)    | When used as the input port or serial port, the latch must be set to "1".      | Serial data output             |

| R90 (\$1)              | I/O (Input)     | Taker most de set to                                                           | Serial data input              |

| P142 - P141            | Output          | 3-bit I/O port with latch                                                      |                                |

| P140 (BEEP)            | Output (Output) | 3-ort //O port with fatch                                                      | BEEP output                    |

| SEG31 - SEG0           | Output          | LCD Segment driver output                                                      |                                |

| COM4 - COM1            | Jacque          | LCD Common driver output                                                       |                                |

| TONE                   | Output          | Tone output                                                                    |                                |

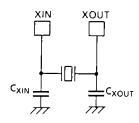

| XIN                    | Input           | Resonator connecting pins (High-frequency).                                    |                                |

| XOUT                   | Output          | For inputting external clock, XIN is used and XOU                              | T is opened.                   |

| XTIN                   | Input           | Resonator connecting pins (Low-frequency).                                     |                                |

| XTOUT                  | Output          | For inputting external clock, XIN is used and XOU                              | T is opened.                   |

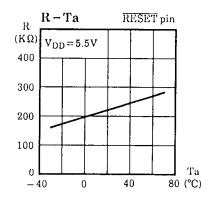

| RESET                  | Input           | Reset signal input                                                             |                                |

| TEST                   | Input           | Test pin for shipping test. Be opened or fixed to lo                           | ow level.                      |

| VDD                    |                 | + 2.7V to 6.0V                                                                 |                                |

| vss                    | Power Supply    | 0V (GND)                                                                       |                                |

| VLC                    |                 | LCD drive power supply                                                         |                                |

#### OPERATIONAL DESCRIPTION

Concerning the 47C456A, the configuration and functions of hardwares are described. As the description has been provided with priority on those parts differing from the 47C400A, the technical data sheets for the 47C400A shall also be referred to.

#### 1. SYSTEM CONFIGURATION

- (1) Data Memory

- (2) I/O port

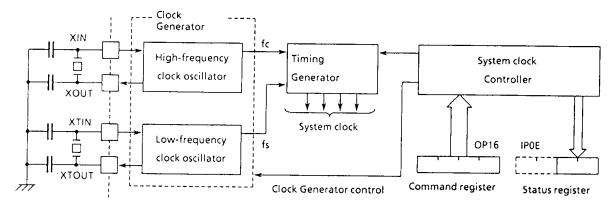

- (3) System Clock Controller

- (4) Interval Timer

- (5) Timer/Counter (TC1, TC2)

- (6) Serial Interface

- (7) LCD Driver

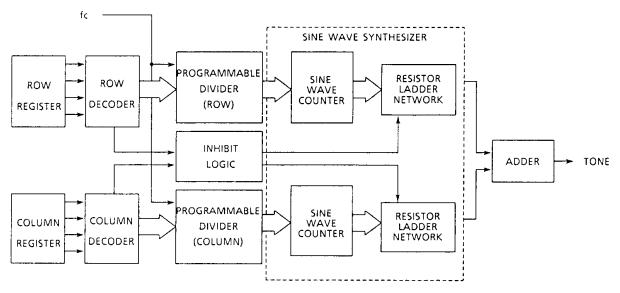

- (8) DTMF Generator

- (9) BEEP Output Circuit

- (10) Watchdog Timer

## 2. INTERNAL CPU FUNCTION

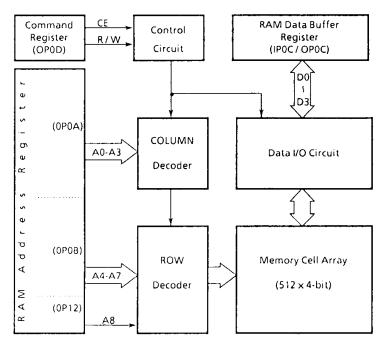

### 2.1 Data Memory

The 47C456A data memory consists of a 768 x 4-bit RAM. First 256 x 4-bit RAM is the same as the data memory built into the 47C400A, so refer to the technical data sheets for the 47C400A for an explanation of the operation. Extended 512 x 4-bit RAM is mainly used for storing repertory dialing data and is controlled by the RAM address register, RAM data buffer register and TONE/RAM command register.

Figure 2-1. RAM Block Diagram

## (1) RAM (512 × 4-bit) Address Register

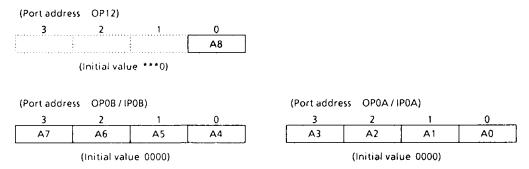

The RAM address register is a 9-bit register to specify addresses for the RAM data memory. The upper 1 bit is accessed with port address OP12, the next 4 bits are accessed with the port address OP0B/IP0B and the lower 4 bits are accessed with port address OP0A/IP0A.

These registers are initialized to "0" during reset.

Figure 2-2. RAM Address Register

## (2) RAM (512 x 4-bit) Data Buffer Register

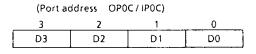

The RAM data buffer register is a 4-bit buffer register to read or write RAM data. When writing data to RAM, it is accessed as port address OPOC. Port address IPOC is used for access when reading data from RAM.

Figure 2-3. RAM Data Buffer Register

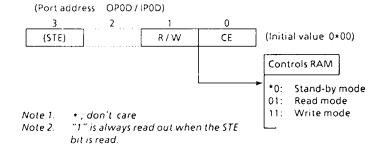

#### (3) RAM (512 × 4-bit) Command Register

The RAM command register (OPOD/IPOD) controls the reading or writing data, and whether RAM is to be accessed or put in stand-by mode. This register is accessed as the port address OPOD/IPOD. The RAM command register is also used as the TONE command register.

Figure 2-4. RAM Command Register

### 2.1.1 Access for RAM (512 $\times$ 4-bit)

To write data to RAM; load the address into the RAM address register and the data into the RAM data buffer register (OPOC), then put the RAM command register in the write mode. The data will be written to the specified RAM address by this operation.

The data are latched in the RAM data buffer register, therefore, RAM data buffer register operation is not necessary when the same data are written continuously.

To read data from RAM, set the RAM command register to the read mode and load the address into the RAM address register, then read the data via RAM data buffer register (IPOC). Data are not latched in the RAM data buffer register.

```

Example 1: To write data "9" to address 182H and data "7" to address 15AH in RAM.

LD

A,#1

; Sets data "182H" to RAM address register.

OUT

A,%OP12

#8,%OPQB

OUT

OUT

#2,%OP0A

OUT

#9,%OPOC

; Writes data "9" to RAM data buffer register.

OUT

#0011B,%OP0D

; Sets RAM to write mode.

OUT

#0010B,%OP0D

; Sets RAM to stand-by mode.

OUT

#5,%OP0B

; Sets data "15AH" to RAM address register.

OUT

#0AH,%OPOA

OUT

; Writes data "7" to RAM data buffer register.

#7.%OPOC

OUT

#0011B,%OP0D

; Sets RAM to write mode.

OUT

#0010B,%OP0D

; Sets RAM to stand-by mode.

Example 2: To write data "0" to address 120H through 127H in RAM.

OUT

#0,%OPOC

; Writes data "0" to RAM data buffer register.

LD

A,#0

; Sets data "120H" to RAM address register.

OUT

#1,%OP12

OUT

#2,%OP0B

OUT

A,%OPOA

OUT

#0011B,%OP0D

: Sets RAM to write mode.

SLOOP : CMPR

A,#7

; Increases address register.

TESTP

ZF

В

SWEND

INC

OUT

A,%OPOA

BR

SLOOP.

SWEND : OUT

#0010B,%OP0D

; Sets RAM to stand-by mode.

Example 3: To read data from address OB1H in RAM and store to Accumulator.

OUT

#0001B,%OP0D

; Sets RAM to read mode.

LD

A,#0

; Sets data "OB1H" to RAM address register

OUT

A,%OP12

OUT

#0BH,%0P0B

OUT

#1,%OP0A

IN

%IPOC,A

; Reads data from RAM and stores to

Accumulator.

```

## 3. PERIPHERAL HARDWARE FUNCTION

#### 3.1 I/O Ports

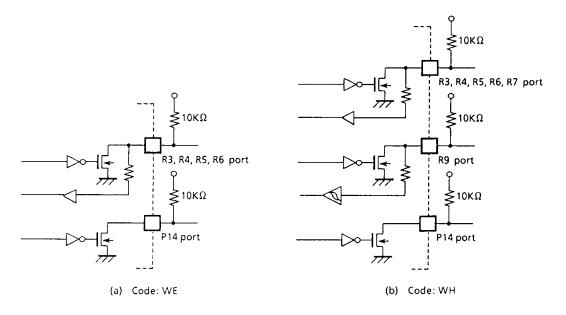

The 47C456A has 9 ports (34 pins) each as follows:

(i) K0 ; 4-bit input (2) R3 ; 4-bit input/o

(2) R3 ; 4-bit input/output (3) R4, R5, R6, R7 ; 4-bit input/output

4 R8 ; 4-bit input/output (shared by external interrupt input and

timer/counter input)

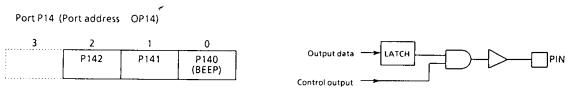

(5) R9 ; 3-bit input/output (shared by serial port) (6) P14 : 3-bit output (P140 is shared by REEP output

6 P14 ; 3-bit output (P140 is shared by BEEP output)

The port K0, R3 and P14 of the 47C456A differ from those of the 47C400A. The 47C456A does not have the port P1 and P2.

Table 3-1 lists the port address assignments and the I/O instructions that can access the ports.

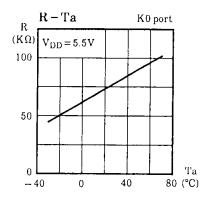

#### (1) Port K0 (K03-K00)

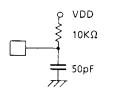

The 4-bit input port with pull-up resistors.

Figure 3-1. Port K0

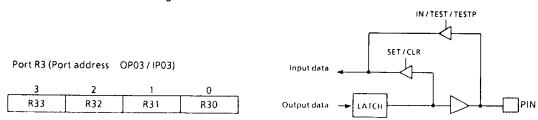

### (2) Port R3 (R33-R30)

The 4-bit I/O port with latch. When used as an input port, the latch must be set to "1". The latch is initialized to "1" during reset.

Figure 3-2. Port R3

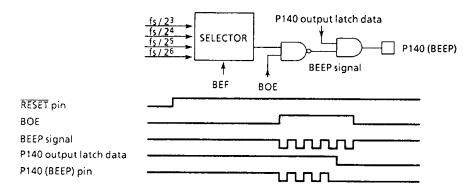

#### (3) Port P14 (P142-P140)

The 3-bit output port with latch. The latch is initialized to "1" during reset. The pin P140 is shared by the BEEP output. When used as the BEEP output, the latch must be set to "1".

Figure 3-3. Port P14

| t od            | Por                        | Ţ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                        |                         | Input/Ou   | Input/Output instruction | tion                   |               |                            |

|-----------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------------|------------|--------------------------|------------------------|---------------|----------------------------|

| address<br>(**) | Input (IP**)               | Output (OP**)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | IN %p, A<br>IN %p, @HL | OUT A, %p<br>OUT@HL, %p | OUT #k, %p | OUTB @HL                 | SET %p, b<br>CLR %p, b | TEST %p, b    | SET @L<br>CLR @L<br>TEST@L |

| 00              | troo troo. CX              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |                         |            | 1                        |                        |               |                            |

| T ,             |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | )(                     | (                       | (          | (                        | . (                    | ) (           |                            |

|                 | KOW register               | ROW register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | )                      | )                       | j          | (Anora)                  | )                      | j             | ı                          |

| 02              | COLUMN register            | COLUMN register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                      | Ö                       | 0          | ( )                      | ()                     | ( )           | ı                          |

| 03              | R3 input port              | R3 output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                      | O                       | $\bigcirc$ | ı                        | 0                      | ()            | ı                          |

| 04              | R4 input port              | R4 output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | С                      | · ( )                   | С          | ı                        | (C)                    | ()            | 0                          |

| 70              | troot troots               | B5 out out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ) (                    | ) (                     | (          |                          | ) C                    | ι(,           | C                          |

| 50              |                            | 100000000000000000000000000000000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | )(                     | )(                      | )(         | 1                        | )(                     | )(            | )(                         |

| 90              | Re input port              | Re output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | )(                     | )(                      | )(         | ı                        | )(                     | )(            | )(                         |

| 07              | R7 input port              | R7 output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                      | 0                       | 0          | ļ                        | 0                      | $\overline{}$ | Э                          |

| 80              | R8 input port              | R8 output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                      | 0                       | 0          | 1                        | ()                     | $\overline{}$ | ı                          |

| 60              | R9 input port              | R9 output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                      | $\bigcirc$              | 0          | ì                        | $\bigcirc$             | $\bigcirc$    | í                          |

| 0A              | RAM address register       | RAM address register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                      | ()                      | 0          | 1                        | ()                     | ()            | ı                          |

| 90              | RAM address register       | RAM address register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                      | ()                      | 0          | 1                        | $\bigcirc$             | ()            | ı                          |

| JU.             | RAM data buffer register   | RAM data buffer register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | C                      | С                       | ·C         | 1                        | С                      | C             | 1                          |

|                 | BAM command register       | BAM Command register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ) (                    | ) (                     | ) (        | ,                        | )                      | ) (           |                            |

| ) i             | CONTRACTOR SEGISCE         | יאואן כסוויווופן ומ נבאוזים                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | )(                     | )                       | )          | ì                        | ı                      | )(            | )                          |

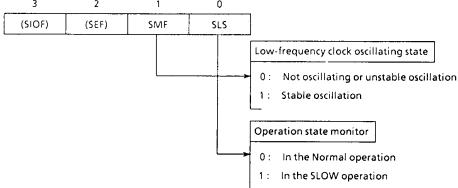

| 0E              | SIO, SLOW operation status |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | )<br>                  | i                       | 1          | ł                        | 1                      | .)            | ı                          |

| 0F              | Serial receive buffer      | Serial transfer buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0                      | 0                       | ()         | _                        | _                      | 1             | 1                          |

| 10 <sub>H</sub> | Undefined                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                      | 1                       |            |                          | i                      |               |                            |

| =               | Undefined                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                      | ı                       | ı          | ı                        | ı                      | ı             | ı                          |

| 12              | Undefined                  | RAM address register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ı                      | 0                       | i          | 1                        | ı                      | ì             | 1                          |

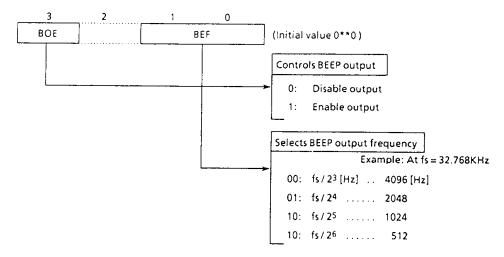

| 13              | Undefined                  | BEEP output control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | l                      | 0                       | ı          | 1                        | ı                      | ı             | ı                          |

| 14              | Undefined                  | P14 output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                      | 0                       | ı          | •                        | ı                      | ,             | ı                          |

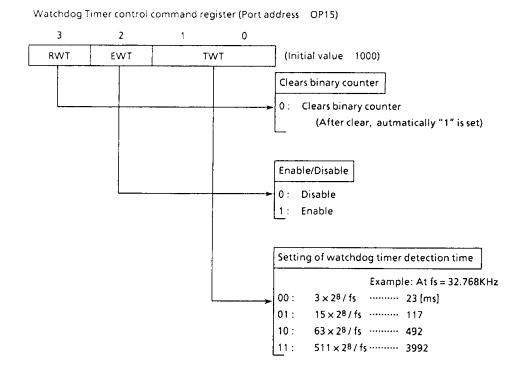

| 15              | Undefined                  | Watchdog Timer control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                      | ()                      | 1          | ı                        | ı                      | 1             | ı                          |

| 16              | Undefined                  | System clock control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                      | 0                       | ı          | 1                        | ı                      | ı             | 1                          |