No.2810A

LM7005

# Electronic AV Tuner-Use Electronic Tuning PLL Frequency Synthesizer

#### **Features**

The LM7005 is an N-channel MOS LSI used as an AV tuner-use electronic tuning PLL frequency synthesizer converting a wide range of fequency bands from UHF to LW.

(1) Programmable divider

· RF 1 pin: 1/2 prescaler + 1/16 or 1/17 swallow counter + main counter 400MHz to 900MHz (18bits)

· RF 2 pin: 1/16 or 1/17 swallow counter + main counter 30MHz to 450MHz (18bits)

· RF 3 pin : 1/16 or 1/17 swallow counter + main counter 30MHz to 150MHz (18bits)

RF 4 pin: Direct input to main counter 0.5MHz to 35MHz (14bits)

(2) Reference frequency

. Programmable divider (14bits) 220Hz to 450kHz at Fundamental Crystal (X'tal) oscillation frequency : 7.2MHz

- (3) Unlock detection pin available

- (4) Deadlock clear circuit available

- (5) Output ports: 7 pins

N-ch open drain output type

(6) Package: DIP24S (Slim)

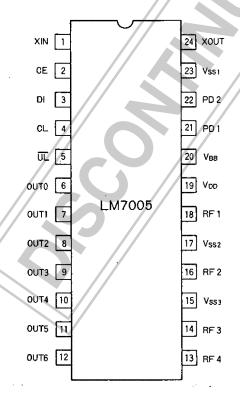

#### Pin Assignment

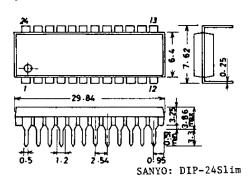

# Package Dimensions 3084 (unit: mm)

SANYO Electric Co., Ltd. Semiconductor Business Headquarters

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

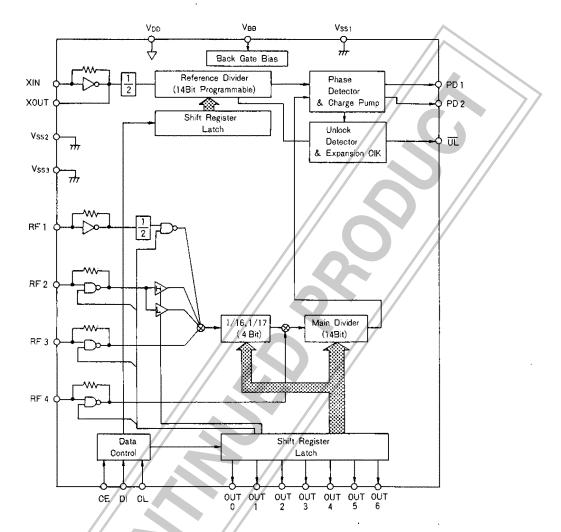

#### Block Diagram

( >/> : Input frequency selection)

Pin symbol

XIN, XOUT : X'tal OSC

RF1 to RF4 : Local oscillation signal input

CE, DI, CL : Serial data input

OUT0 to OUT6 : Output ports

Unlock signal output

PD1, PD2

Charge pump output

Back gate bias input

V<sub>DD</sub> : Supply voltage

VSS1, VSS2, VSS3 : Ground

| Absolute Maximum Ratio  | ngs at Ta=        | 25°C.             | $V_{SS} = 0V$                          | •                                               |        |                         | unit |

|-------------------------|-------------------|-------------------|----------------------------------------|-------------------------------------------------|--------|-------------------------|------|

| Maximum Supply Voltag   |                   |                   | $\widetilde{\mathrm{V}}_{\mathrm{DD}}$ |                                                 |        | -0.3 to $6.0$           |      |

| Back Gate Bias Input    | $V_{BB}$          |                   | $V_{BB}$                               |                                                 | _      | 4.0  to  -2.0           |      |

| Input Voltage           | V <sub>IN</sub> ( | 1)                | CE,CL,                                 | DI                                              |        | -0.3 to $6.0$           |      |

| •                       | V <sub>IN</sub> ( |                   |                                        | ns other than V <sub>IN</sub> (1)               | -0.3 t | o V <sub>DD</sub> + 0.3 |      |

| Output Voltage          | Vou               |                   |                                        | o OUT6,UL                                       |        | -0.3 to 15              |      |

| Output Current          | I <sub>OL</sub> n |                   |                                        | o OUT6,UL                                       | // >   | 3.0                     |      |

| Allowable Power Dissipa |                   |                   | Ta≦85°                                 |                                                 | /      | 430                     |      |

| Operating Temperature   | Topr              |                   |                                        |                                                 |        | -40 to +85              |      |

| Storage Temperature     | Tstg              |                   |                                        |                                                 |        | 55 to +125              |      |

|                         | · ·               |                   |                                        |                                                 |        | 7 //                    |      |

| Allowable Operating Con |                   |                   | -40 to +                               | $85^{\circ}\text{C}, V_{\text{SS}} = 0\text{V}$ | min    | typ max                 |      |

| Supply Voltage          | $ m v_{DD}$       | $V_{\mathrm{DD}}$ |                                        |                                                 | 4.5    | 5.5                     |      |

| 'H'-Level Input Voltage | $V_{IH}$          | CE,C              |                                        |                                                 | 2.2    | 5.5                     |      |

| 'L'-Level Input Voltage | $ m V_{IL}$       | CE,C              |                                        |                                                 | 0      | 0.7                     |      |

| Output Voltage          | $v_{out}$         |                   | to OUT                                 |                                                 | 0      | 13                      |      |

| Input Frequency         | $f_{IN}(1)$       | XIN               |                                        | Capacitor coupled                               | 1.0    | 16                      | MHz  |

|                         |                   |                   |                                        | sine wave input:                                |        |                         |      |

|                         | $f_{IN}(2)$       | RF1               |                                        | Capacitor coupled                               | 400    | 900                     | MHz  |

|                         |                   |                   |                                        | sine wave input : $SP = *$                      |        |                         |      |

|                         | $f_{IN}(3)$       | RF2               |                                        | Capacitor coupled                               | 100    | 450                     | MHz  |

|                         |                   |                   |                                        | sine wave input: $SP=1$                         |        |                         |      |

|                         | $f_{IN}(4)$       | RF2               |                                        | Capacitor coupled                               | 30     | 150                     | MHz  |

|                         |                   |                   |                                        | sine wave input: $SP = 0$                       |        |                         |      |

|                         | $f_{IN}(5)$       | RF3               | // /                                   | Capacitor coupled                               | 30     | 150                     | MHz  |

|                         |                   |                   |                                        | sine wave input: $SP = *$                       |        |                         |      |

|                         | $f_{IN}(6)$       | RF4               |                                        | Capacitor coupled                               | 0.5    | 35                      | MHz  |

|                         |                   |                   |                                        | sine wave input: SP=*                           |        |                         |      |

| Guaranteed Crystal      | X'tal             | XIN-              | TUOX                                   | (CI≦50Ω)                                        | 3.0    | 7.2 8.0                 | MHz  |

| Oscillation Resonator   | /                 |                   |                                        | /_ //                                           |        |                         |      |

| Input Amplitude         | $V_{IN}(1)$       | XIN               |                                        | Capacitor coupled                               | 0.5    | 1.5                     | Vrms |

|                         | /./.              |                   |                                        | sine wave input                                 |        |                         |      |

|                         | $V_{IN}(2)$       | RF1               |                                        | Capacitor coupled                               | 0.1    | 1.5                     | Vrms |

|                         | <b>4</b>          |                   |                                        | sine wave input                                 |        |                         |      |

|                         | $V_{\rm IN}(3)$   | RF2               | • //                                   | Capacitor coupled                               | 0.1    | 1.5                     | Vrms |

| //                      |                   |                   |                                        | sine wave input                                 |        |                         |      |

|                         | $V_{IN}(4)$       | RF3               |                                        | Capacitor coupled                               | 0.1    | 1.5                     | Vrms |

|                         | - 131             |                   |                                        | sine wave input                                 |        |                         |      |

|                         | $V_{IN}(5)$       | RF4               |                                        | Capacitor coupled                               | 0.1    | 1.5                     | Vrms |

|                         |                   |                   | 7                                      | sine wave input                                 |        |                         |      |

sine wave input

Note: SP is one of the control data bits, which is used for selecting a desired input frequency band.

(\* Don't care)

| Electrical Characteristics | under rece          | ommended oper | rating conditions | min   | typ    | max     | unit               |

|----------------------------|---------------------|---------------|-------------------|-------|--------|---------|--------------------|

| On-chip Feedback           | Rf (1)              | XIN           | -                 |       | 1.0    |         | $\mathbf{M}\Omega$ |

| Resistor                   | Rf (2)              | RF1           |                   |       | 500    |         | $\mathbf{k}\Omega$ |

|                            | Rf (3)              | RF2           |                   |       | 500    |         | $\mathbf{k}\Omega$ |

|                            | Rf (4)              | RF3           |                   |       | 500    |         | $\mathbf{k}\Omega$ |

|                            | Rf (5)              | RF4           |                   |       | 500    |         | $\mathbf{k}\Omega$ |

| 'H'-Level Input Current    | $I_{IH}(1)$         | CE,CL,DI      | $V_{IN} = 5.5V$   |       |        | 5.0     | $\mu$ A            |

|                            | $I_{IH}(2)$         | XIN           | $V_{IN} = V_{DD}$ |       |        | 20      | $\mu$ A            |

|                            | I <sub>IH</sub> (3) | RF1,2,3,4     | $V_{IN} = V_{DD}$ |       |        | 40      | $\mu$ A            |

| 'L'-Level Input Current    | $I_{IL}(1)$         | CE,CL,DI      | $V_{IN} = V_{SS}$ |       |        | 5.0     | μΑ                 |

| *                          | $I_{IL}(2)$         | XIN           | $V_{IN} = V_{SS}$ |       |        | 20      | $\mu$ A            |

|                            | $I_{IL}(3)$         | RF1,2,3,4     | $V_{IN} = V_{SS}$ |       |        | 40      | $\mu$ A            |

|                            |                     |               |                   | Conti | nued o | on next | nage               |

|                          |             |                                      |                             | min                  | typ  | max  | unit |

|--------------------------|-------------|--------------------------------------|-----------------------------|----------------------|------|------|------|

| 'H'-Level Output Voltage | $v_{oh}$    | PD1,PD2                              | $I_0 = 0.1 \text{mA}$       | $0.6V_{\mathrm{DD}}$ |      |      | V    |

| 'L'-Level Output Voltage | $V_{OL}(1)$ | PD1,PD2                              | $I_0 = 0.1 \text{mA}$       |                      |      | 0.3  | V    |

|                          | $V_{OL}(2)$ | OUT0 to OUT6, UL                     | $I_0 = 2mA$                 | ^                    |      | 1.0  | V    |

| Output OFF Leak Current  |             | OUT0 to OUT6, $\overline{\text{UL}}$ | $V_O = 13V$                 |                      |      | 5.0  | μA   |

| 'H'-Level Tri-State OFF  | $I_{OFFH}$  | PD1,PD2                              | $V_O = V_{DD}$              |                      | 0.01 | 10.0 | nΑ   |

| Leak Current             |             |                                      |                             |                      |      |      |      |

| 'L'-Level Tri-State OFF  | $I_{OFFL}$  | PD1,PD2                              | $V_O = V_{SS}$              |                      | 0.01 | 10.0 | nA   |

| Leak Current             |             |                                      | //                          |                      |      | 7    |      |

| Input Capacitance        | $C_{IN}$    | RF1                                  |                             |                      | 2.5  |      | рF   |

| Supply Current           | $I_{DD}$    |                                      | $f_{IN}(2) = 900MHz$        | ,                    | 55   | 80   | mA   |

| •••                      |             |                                      | $V_{IN}(2) = 100 \text{mV}$ | rms,                 |      |      |      |

|                          |             |                                      | X'tal=7.2MHz,               |                      |      |      |      |

|                          |             |                                      | other input pins:           | $=V_{SS}$            |      |      |      |

|                          |             |                                      | output pins = ope           |                      |      |      |      |

|                          |             |                                      |                             |                      | / /  |      |      |

## [1] Pin Description

| Symbol      | Pin No. | Contents                                       | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | I/O Type        |

|-------------|---------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| XIN<br>XOUT | 1<br>24 | X'tal OSC                                      | Crystal oscillation frequency input pin.  Connected with the crystal oscillation resonator with an oscillation frequency of 7.2MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Input<br>Output |

| RF1         | 18      | Local oscillation<br>signal frequency<br>input | <ul> <li>Serial data input pin: This input pin is selected when bits DV0 and DV1 are set to 0. The serial input data to this pin is transmitted to a programmable divider circuit.</li> <li>The input frequency range is between 400MHz and 900MHz (100mVrms: Minimum).</li> <li>The input signal is transmitted to the swallow counter via the internal prescaler.</li> <li>The settable division ratio is between 256 and 262143. Please note that the actual division ratio will be twice the value set because the internal prescaler is provided.</li> </ul>                                                                                                                                                                                                                                                                                                                                                     | Input           |

| RF2         | 16      | Local oscillation signal frequency input       | <ul> <li>Serial data input pin: This pin is selected when control data bits DV0 and DV1 are set to 1 and 0, respectively. The input serial data to this pin is transmitted to a programmable divider circuit.</li> <li>Serial input data with control data bit SP=1:</li> <li>The input frequency range is between 100 MHz and 450MHz (100mVrms: Minimum).</li> <li>The input signal frequency to this pin is directly transmitted to the swallow counter, not via the 1/2 internal prescaler.</li> <li>The settable division ratio can be between 256 and 262143.</li> <li>Serial input data with control data bit SP=0:</li> <li>The input signal frequency is between 30MHz and 150MHz (100mVrms: Minimum).</li> <li>The input signal frequency is directly transmitted to the swallow counter, not via the 1/2 internal prescaler.</li> <li>The settable division ratio can be between 256 and 262143.</li> </ul> | Input           |

Continued on next page.

|                                                      | Pin No.                            | Contents                                       | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I/O Type                             |

|------------------------------------------------------|------------------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| RF3                                                  | 14                                 | Local oscillation<br>signal frequency<br>input | <ul> <li>Serial data input pin: This pin is selected when control data bits DV0 and DV1 are set to 0 and 1, respectively. The serial input data to this pin is transmitted to a programmable divider circuit.</li> <li>The input frequency range is between 30MHz and 150MHz (100mVrms: Minimum).</li> <li>The input signal frequency is directly transmitted to the swallow counter, not via the 1/2 internal prescaler.</li> <li>The settable division ratio can be between 256 and 626143.</li> </ul> | Input                                |

| RF4                                                  | 13                                 | Local oscillation<br>signal frequency<br>input | <ul> <li>Serial data input pin: This is selected when control data bits DV0 and DV1 are set to 1. The input serial data to this pin is transmitted to a programmable divider circuit.</li> <li>The input frequency range is between 0.5MHz and 35MHz.</li> <li>The input signal frequency is directly transmitted to the 14-bit main divider.</li> <li>The settable division ratio is between 16 and 16383.</li> </ul>                                                                                   | Input                                |

| PD1<br>PD2                                           | 21<br>22                           | Phase<br>comparator<br>Charge pump<br>output   | · Charge pump output from the PLL circuit: H-level output Reference frequency (fref) < fosc/N. L-level output Reference frequency (fref) > fosc/N. Floating state Reference frequency (fref) = fosc/N. Note: fosc/N = local cillston planet frequency divided by N                                                                                                                                                                                                                                       | Output<br>(Tri-state)                |

| ÜL                                                   | 5                                  | Unlock<br>detection output                     | ocillation signal frequency divided by N.  · Used for PLL lock/unlock state output.  · PLL in lock state: Open-circuited.  · PLL in unlock state: Low  · For more information, refer to the unlock detection circuit.                                                                                                                                                                                                                                                                                    | Output  N-ch open drain circuit type |

| CE                                                   | 2                                  | Chip enable<br>signal input                    | · Set this pin to the H-level state to input serial data to the LM7005.                                                                                                                                                                                                                                                                                                                                                                                                                                  | Input *                              |

| CL                                                   | 4                                  | Clock pulse<br>input                           | · Provide synchronization timings for inputting serial data into the LM7005.                                                                                                                                                                                                                                                                                                                                                                                                                             | Input *                              |

| DI                                                   | 3                                  | Serial data<br>input                           | <ul> <li>Pin for inputting serial data to the LM7005.</li> <li>To set the initial value in the LM7005, the total number of 56 bits must be used.</li> </ul>                                                                                                                                                                                                                                                                                                                                              | lnput <b></b> ₩                      |

| OUTO<br>OUT1<br>OUT2<br>OUT3<br>OUT4<br>OUT5<br>OUT6 | 6<br>7<br>8<br>9<br>10<br>11<br>12 | Output port                                    | <ul> <li>Output ports used for outputting the 7-bit serial data from the controller to an external circuit. This synthesizer receives 7-bit serial data O0 to O6 from the controller and then latches it into the shift register. That 7-bit serial data is then output in parallel to an external device from these 7 ports.</li> <li>Data logic "1": Open-circuited</li> <li>Data logic "0": Low</li> <li>Withstand voltage level: 13V</li> </ul>                                                      | Output  N-ch open drain circuit type |

Continued on next page.

| Symbol            | Pin No. | Contents                | Functional Description                                                                                          | I/O Type         |

|-------------------|---------|-------------------------|-----------------------------------------------------------------------------------------------------------------|------------------|

| V <sub>BB</sub>   | 20      | Back gate bias<br>input | $\cdot$ Pin for back gate bias input (The capacitor of 0.01 $\mu F$ is needed between this pin and the ground.) |                  |

| $V_{\mathrm{DD}}$ | 19      | Supply voltage          | · Supply voltage pin.<br>(Supply voltage : 4.5V to 5.5V)                                                        | _                |

| V <sub>SS1</sub>  | 23      | Ground                  | · Ground pin                                                                                                    | \ <del>-</del> \ |

| V <sub>SS2</sub>  | 17      | Ground                  | · Ground pin for high frequency signal: For RF1 pin                                                             | //               |

| V <sub>SS3</sub>  | 15      | Ground                  | · Ground pin for high frequency signal: For RF2/3/4 pin                                                         |                  |

$<sup>\</sup>times$  H-level input voltage for pins CE, CL and DI: 2.2V to 5.5V (V<sub>IH</sub>). L-level input voltage for pins CE, CL and DI: 0V to 0.7V (V<sub>IL</sub>). These voltage levels are independent of the supply voltage (V<sub>DD</sub>).

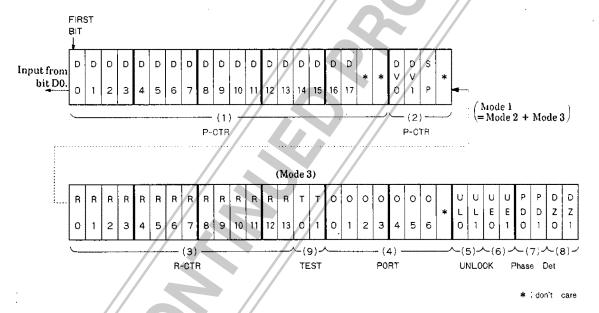

#### [2] Control data (serial data) configuration

The sirial data for controlling the LM7005 consists of 56 bits. After the power on, all the 56 bits must be input to the LM7005 for initialization.

Mode 1: The LSI test mode selection data (T0 and T1) must be set to 0.

Mode 2: The 24 bits from D0 to \* must be used.

Mode 3: The 32 bits from R0 to DZ1 must be used.

○ : Input required, — : Input not required.

|        | /// |     |     | O 1 24. | harrod | war ou, | ,pu | 0110010 | qual ca. |

|--------|-----|-----|-----|---------|--------|---------|-----|---------|----------|

|        | (1) | (2) | (3) | (4)     | (5)    | (6)     | (7) | (8)     | (9)      |

| Mode 1 | 0   | 0   | 0   | 0       | 0      | 0       | 0   | 0       | 0        |

| Mode 2 | Ó   | 0   | _   | _       |        |         | _   |         | _        |

| Mode 3 | _   | _   | 0   | 0       | 0      | 0       | 0   | 0       | 0        |

# [3] Control data bit description

| No. | Data                                                                                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Associated data bits     |

|-----|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| (1) | Programmable<br>divider control<br>data D0 to D17 :<br>Specify a desired<br>division ratio     | The control data (D0 to D17) must be input to the LM7005 for setting a desired division ratio in the programmable divider circuit. This control data is a binary value. Bit D17 is the most significant bit (MSB) of the control data. The least significant bit (LSB) of this control data depends on bits DV0 and DV1 as shown in the table below.                                                                                                                      | DV0<br>DV1               |

| (2) | DV0 and DV1 ;<br>Divider selection<br>data<br>SP : Select a<br>desired input<br>frequency band | Bits DV0 and DV1 are used to select a desired local oscillation signal input pin from RF1 to RF4.  Bit SP has meaning if RF2 pin has been selected. This bit is used to select a desired input frequency range. *: Do not care.  DV0 DV1 Pin SP H/L Settable division ratio  0 0 RF1 * - 400MHz to 900MHz  1 0 RF2 1 H 100MHz to 450MHz  1 0 RF3 * - 30MHz to 150MHz  0 1 RF3 * - 30MHz to 150MHz  1 1 RF4 * - 0.5MHz to 35MHz                                            | D0<br>to<br>D17          |

| (3) | R0 to R13 :<br>Select a desired<br>reference<br>frequency                                      | <ul> <li>Bits R0 to R13 are used to set a desired division ratio in the reference divider circuit.</li> <li>The control data (R0 to R13) is a binary value. The least significant bit (LSB) of this control data is R0.</li> <li>Settable division ratio: 8 to 16383.</li> <li>Actual division ratio = division ratio set ×2</li> <li>Reference frequency = Crystal oscillation frequency: XIN/actual division ratio</li> </ul>                                           | UL0<br>UL1<br>UE0<br>UE1 |

| (4) | O0 to O6: Specify<br>output port data                                                          | Bits O0 to O6 are used to determine the output data to an external device from ports OUT0 to OUT6.  The control data (O0 to O6) is input to the LM7005 from the controller and then latched into the shift register. The content of the shift register is output to an external device from output ports OUT0 to OUT6. Each output port consists of an N-ch open drain output circuit and enters the following state:  Data logic "1": Open-circuited Data logic "0": Low | _                        |

Continued on next page.

| No. | Data                                                   | Description                                                                                                                                                                                                                                                                                                                      | Associated data bits |

|-----|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|     |                                                        | Data bits (ULO and UL1) are used for detecting a pulse width of a phase error signal from the phase comparator to the pulse width detection circuit. Data bits (UEO and UE1) are used to specify a desired expansion time data for output unlock signal from the LM7005 to an external circuit.                                  |                      |

|     |                                                        | UL0 UL1 Phase error signal Division ratio for detection width reference divider                                                                                                                                                                                                                                                  |                      |

| (5) | UL0 and UL1, and<br>UE0 and UE1:                       | 0   0   Direct   8 or more   1   0   ±4/fx'tal or longer   8 or more   0   1   ±16/fx'tal or longer   24 or more                                                                                                                                                                                                                 | R0<br>to             |

| (6) | Unlock detection<br>data bits                          | 1 1 ±64/fx'talor longer 96 or more (fx'tal; Crystaloscillation frequency)                                                                                                                                                                                                                                                        | R13                  |

|     |                                                        | UE0                                                                                                                                                                                                                                                                                                                              |                      |

|     |                                                        | For more information, please refer to the unlock detection circuit to be later discussed.                                                                                                                                                                                                                                        |                      |

| (7) | PD0 and PD1 :<br>Charge pump<br>output control<br>data | These two bits are used to control the charge pump outputs (PD1 and PD0).  When the PLL is forced into a deadlock state, these data bits are used to control the charge pump outputs and then allows the PLL to exit from the deadlock state.  PD0 PD1 Charge pump output  O O Normal operation  1 O High  O 1 Low  1 1 Floating | -                    |

| (8) | DZ0 and DZ1 :<br>Dead zone control<br>data             | These two data bits are used to select a desired dead zone for the phase detector from the following four options.  DZC > DZB > DZA  Dead zone  DZA  DZB  DZB  DZB  DZB  DZB  DZB  DZC  I DDCC  I I DDCC  I I Input inhibited                                                                                                    | _                    |

| (9) | T0 and T1 :<br>LSI test data                           | These two data bits are used to select a desired test mode. They have nothing to do with the user operation.  Normally, these bits are set to 0.  Note that these data bits must be always set to "0" right after power is supplied.                                                                                             |                      |

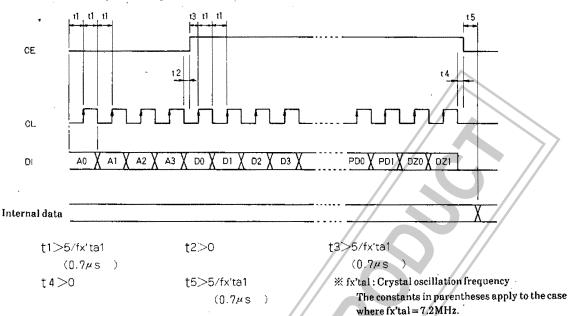

#### [4] Control data (serial data) entry

There are three control data entry modes available on the LM7005. Control data can be input to this LSI after one of the three entry modes has been selected.

The one of the three entry modes can be selected by four data bits (A0 to A3) input to the DI pin before the CE pin level becomes High. Note that the these four bits are input to the LSI on the rising edge of the clock pulses input to the CL pin.

The timing chart is given under the table below.

| The timing that the Biven under the table below. |                        |              |         |              |                                                                                                |                                                                                                                                                              |  |  |  |

|--------------------------------------------------|------------------------|--------------|---------|--------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Mode                                             | A0                     | A1           | A2      | А3           | Function Description                                                                           | Operations Description                                                                                                                                       |  |  |  |

| 1                                                | 1                      | 0            | 0       | 0            | All the control data bits<br>need to be input.                                                 | This mode allows all the 56 control data bits to be input to the LM7005. This mode must be used for initializing the LSI immediately after power is applied. |  |  |  |

| 2                                                | 0                      | 1            | 0       | 0            | Only the control data<br>bits for controlling the<br>programmable divider<br>need to be input. | · This mode allows only the 24 control data bits (D0 to SP, *) to be input to the LM7005. The other bits than the 32 bits remain unchanged.                  |  |  |  |

| 3                                                | 1                      | 1            | 0       | 0            | Only the control data<br>bits for controlling the<br>reference divider need to<br>be input.    | • This mode allows only the 32 control data bits (R0 to DZ1) to be input to the LM7005. The other bits than the 24 bits remain unchanged.                    |  |  |  |

|                                                  | 0<br>to<br>0           | 0<br>to<br>0 | to<br>0 | 0<br>to<br>0 | Invalid                                                                                        | · This is an invalid mode. No control data can not be input to the LSI.                                                                                      |  |  |  |

|                                                  | CE Mode select         |              |         |              |                                                                                                |                                                                                                                                                              |  |  |  |

| ,                                                | CL                     |              |         |              |                                                                                                |                                                                                                                                                              |  |  |  |

|                                                  | DI AO X A1 X A2 X A3 X |              |         |              |                                                                                                |                                                                                                                                                              |  |  |  |

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

#### [5] Serial control data input timing

- Mode 1: This mode allows the user to input 60 bits to the DI pin: 4 mode selection data bits + 56 control data bits

- Mode 2: This mode allows the user to input 28 bits to the DI pin: 4 mode selection data bits + 24 control data bits

- Mode 3: This mode allows the user to input 36 bits to the DI pin: 4 mode selection data bits + 32 control data bits

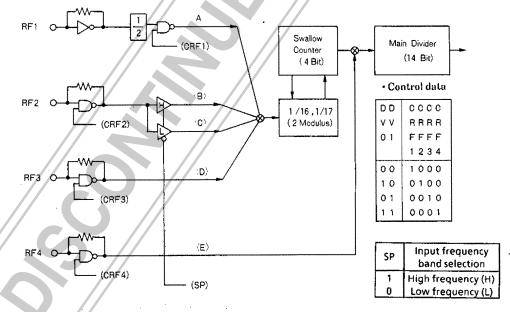

#### [6] Programmable divider circuit configuration

| Pin | DVO | DV1 | Settable<br>division ratio | Actual division ratio        | SP | Channel | Input frequency range | Frequency band |

|-----|-----|-----|----------------------------|------------------------------|----|---------|-----------------------|----------------|

| RF1 | 0,  | 0   | 256 to 262134              | Division ratio set $	imes 2$ | *  | (A)     | 400MHz to 900MHz      | UHF            |

| nno |     |     | C                          | Division ratio set           | 1  | (B)     | 100MHz to 450MHz      | VHF            |

| PF2 | 1   | 0   | Same as above              | Division ratio set           | 0  | (C)     | 30MHz to 150MHz       | FM             |

| RF3 | 0   | 1   | Same as above              | Division ratio set           | *  | ⟨D⟩     | 30MHz to 150MHz       | FM             |

| RF4 | 1   | 1   | 16 to 16383                | Division ratio set           | *  | (E)     | 0.5MHz to 35MHz       | SW,MW,LW       |

DV0, DV1 and SP: Control data bits and \* indicates that any bit value will be accepted.

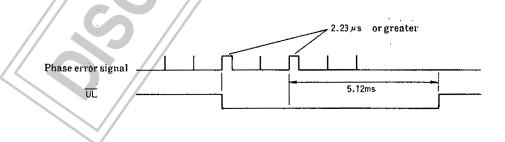

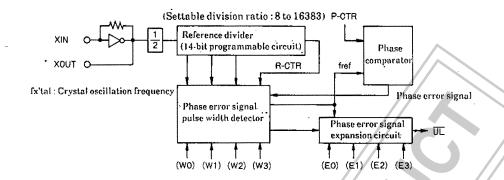

#### [7] Unlock detector circuit configuration

| ULO | ULI |    | Phase error detector | Division ratio set for reference divider | Detection pulse width at fx'tal = 7.2MHz |

|-----|-----|----|----------------------|------------------------------------------|------------------------------------------|

| 0   | 0   | W0 | (Direct output)*     | 8 or greater                             | // -                                     |

| 1   | 0   | W1 | ±4/fx'tal or longer  | 8 or greater                             | ±0.56μs or greater                       |

| 0   | 1   | W2 | ±16/fx'tal or longer | 24 or greater                            | ±2.23μs or greater                       |

| 1   | 1   | W3 | ±64/fx'tal or longer | 96 or greater                            | ±8.89µs or greater                       |

| UL0 | ULI |    | Expansion time period = N cycles of fref<br>(reference frequency) | Reference frequency : fref = 100kHz |

|-----|-----|----|-------------------------------------------------------------------|-------------------------------------|

| 0   | 0   | E0 | 8 cycles                                                          | 0.08ins                             |

| 1   | oi  | E1 | 64 cycles                                                         | 0.64ms                              |

| 0   | 1   | E2 | 128 cycles                                                        | 1.28ms                              |

| 1   | 1   | E3 | 512 cycles                                                        | 5.12ms                              |

ULO, UL2, UEO and UE1: Control data bits and \* indicates that phase error signal pulse width will not be expanded.

- · Phase error signal detection width is closely related to a division ratio set in the reference divider. Please keep it in mind.

- · Phase error signal detection width and expansion time period are determined by a crystal oscillation resonator frequency and a selected reference frequency. Please keep it in mind.

Example: Crystal oscillation resonator --- 7.2MHz. Reference frequency --- 100kHz

- ① Division ratio set in the reference divider:  $7.2MHz \div 100kHz \div 2 = 36$

- ② Phase error signal detection width: UL0=0, UL=1→W2---±2.23µs or greater. Note that W3 cannot be selected.

- ③ Expansion time period: UE0 = UE1 =  $1 \rightarrow$ E3 - 5.12msec.