ML4877\*

# **LCD Desktop Backlight Lamp Driver**

### **GENERAL DESCRIPTION**

The ML4877 is an ideal solution for driving multiple cold cathode fluorescent tubes (CCFL) used in liquid crystal display (LCD) backlight applications. It provides dimming ballast control for the LCD display.

By utilizing differential drive the ML4877 can deliver the same light output with significantly less input power compared to existing single ended drive schemes. Improvements as high as 30% can be realized when using low power lamps and advanced LCD screen housings. This increased light output is achieved because the differential drive configuration is much less sensitive, and therefore less power is wasted in the capacitive parasitics that exist in the backlight housing. An additional benefit of this configuration is an even distribution of light.

The IC includes an adjustable lamp out detect circuit that latches the IC off when a lamp fault is detected. Also, the unique architecture of the ML4877 allows the development of a backlight system that will inherently meet the UL requirements for safety.

The ML4877 is optimized for large LCD applications applications where high efficiency is critical to maximize battery life. The high efficiency is achieved by a resonant scheme with zero voltage switching.

### **FEATURES**

- Ideal for 30W inverter designs, 1 to 8 lamp design

- PWM dimming capability

- Backlight lamp driver with differential drive

- Up to 30% lower power for same light output

- Low standby current (<10µA)

- Improved efficiency (≈95%)

- Allows all N-channel MOSFET drive

- Adjustable lamp out detect with latch

- Resonant threshold detection and synchronous rectification

- Positive input for dimming control

#### \* THIS PART IS END OF LIFE AS OF JULY 1, 2000

#### **B SYNC OUT** BON **B** OFF VDD 13 19 20 11 VDD 10 L RTD LINEAR HVDD 12 REGULATOR DR3 DR1 DR1 14 L GATE 1 DR2 ō MASTER ONE BIAS NEG SHOT VREF 5 16 L GATE 2 O DR2 & FDGF ō UVLO s DELAY RQ 6 L ILIM 0.5V ON/OFF 15 8 LEA OUT RESONANT ssŀ THRESHOLD 7 LEA-DETECTOR ō 1 LEA+ VDD QR OSCILLATOR SS 18 - 3 4 9 PGND GND R<sub>T</sub> SS CAP Ст

Micro Linear

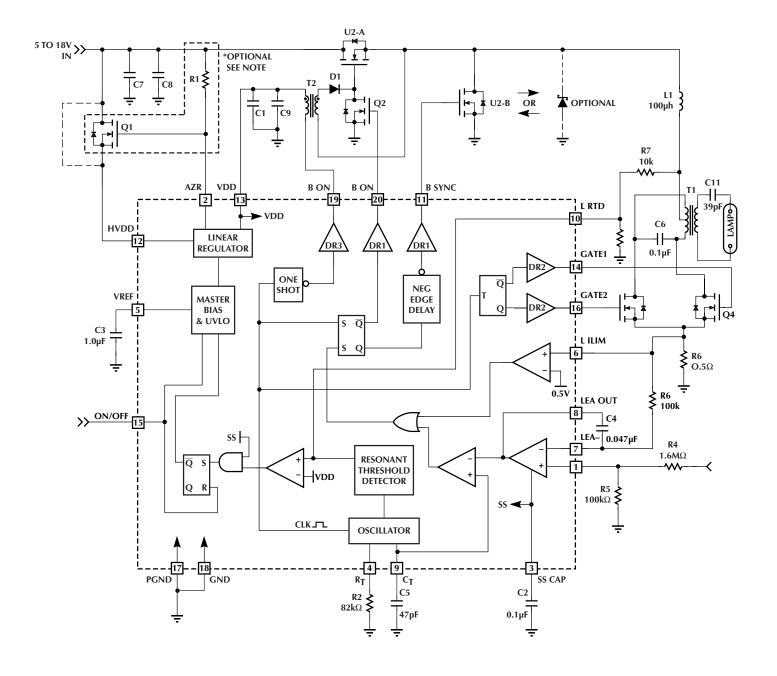

**BLOCK DIAGRAM**

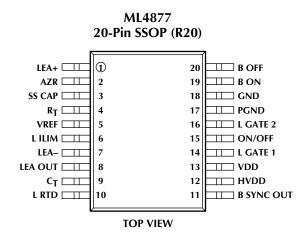

### PIN CONFIGURATION

### PIN DESCRIPTION

| PIN | NAME           | FUNCTION                                                                                                 | PIN | NAME          | FUNCTION                                                                                     |

|-----|----------------|----------------------------------------------------------------------------------------------------------|-----|---------------|----------------------------------------------------------------------------------------------|

| 1   | LEA+           | Positive input for lamp error amp                                                                        | 11  | b sync<br>out | Output of MOSFET driver to gate of synchronous FET catch diode.                              |

| 2   | AZR            | Connection to gate of external FET for<br>high voltage regulator. Internally a<br>zener diode to ground. | 12  | HVDD          | ,<br>Battery power input to linear regulator                                                 |

| 3   | SS CAP         | Connection of optional external soft                                                                     | 13  | VDD           | Output of linear regulator. Positive power for IC.                                           |

| 4   | R <sub>T</sub> | start capacitor<br>Oscillator timing resistor                                                            | 14  | L GATE1       | Output of MOSFET driver. Connection to gate of one side of inverter FET                      |

| 5   | VREF           | Voltage reference output                                                                                 |     |               | drive pair.                                                                                  |

| 6   | l ILIM         | Input to current limit amplifier                                                                         | 15  | ON/OFF        | Logic input for chip                                                                         |

| 7   | LEA-           | Negative input for lamp error<br>amplifier                                                               | 16  | l gate2       | Output of MOSFET driver. Connection to gate of one side of inverter FET drive pair.          |

| 8   | LEA OUT        | Output of lamp error amplifier.                                                                          | 17  | PGND          | Power ground                                                                                 |

|     |                | External compensation capacitor connects between this pin and LEA.                                       | 18  | GND           | Signal ground                                                                                |

| 9   | C <sub>T</sub> | Oscillator timing capacitor                                                                              | 19  | BON           | Connection to primary side of gate pulse transformer                                         |

| 10  | L RTD          | Input to resonant threshold detector                                                                     | 20  | B OFF         | '<br>Output of MOSFET driver. Connection<br>to gate of FET that disables the input<br>power. |

### ABSOLUTE MAXIMUM RATINGS

Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

| Supply Current (I <sub>CC</sub> )                         |  |

|-----------------------------------------------------------|--|

| Output Current, Source or Sink 250mA                      |  |

| Voltage on Pins LEA+, AZR, SS CAP, R <sub>T</sub> , VREF, |  |

| l ILIM, LEA-, LEA OUT, C <sub>t</sub> , B Sync Out, VDD,  |  |

| L GATE 1, ON/OFF, L GATE 2, PGND, GND,                    |  |

| B ON, B OFF –0.3V to VDD +0.3V                            |  |

| Voltage on HVIDD                     |               |

|--------------------------------------|---------------|

| Current into L RTD                   | ±10mA         |

| Junction Temperature                 |               |

| Storage Temperature Range            | 65°C to 150°C |

| Lead Temperature (Soldering 10 sec.) |               |

| Thermal Resistance $(\theta_{JA})$   | 100°C/W       |

|                                      |               |

### **OPERATING CONDITIONS**

| Temperature Range |               |

|-------------------|---------------|

| ML4877C           | 0°C to 70°C   |

| ML4877E           | –20°C to 70°C |

### **ELECTRICAL CHARACTERISTICS**

Unless otherwise specified, VDD = 5V  $\pm$ 5%, T<sub>A</sub>= Operating Temperature Range, C<sub>T</sub> = 47pF, R<sub>T</sub> = 82k $\Omega$  (Note 1)

| SYMBOL   | PARAMETER                            | CONDITIONS                                   | MIN   | ТҮР | MAX   | UNITS |

|----------|--------------------------------------|----------------------------------------------|-------|-----|-------|-------|

| CURRENT  | REGULATOR                            |                                              | I     | 1   | 1     |       |

| ERROR AN | MPLIFIER                             |                                              |       |     |       |       |

|          | Open Loop Gain                       |                                              |       | 60  | 70    | dB    |

|          | Output High                          | $I_{LOAD} = 5\mu A$                          | 2.8   | 3.0 |       | V     |

|          | Output Low                           | $I_{LOAD} = 25 \mu A$                        |       | 0.4 | 0.7   | V     |

|          | Bandwidth (-3dB)                     |                                              |       | 1   |       | MHz   |

|          | Common Mode Voltage Range            |                                              | 0     |     | 1.0   | V     |

|          | Input Bias Current                   |                                              |       | 50  | 100   | nA    |

|          | Input Offset Voltage                 |                                              | -5    | 0   | 5     | mv    |

|          | Soft Start Charge Current            | $V_{SSCAP} = 1V$                             | 550   | 750 | 950   | nA    |

|          | Soft Start Threshold (LEA OUT)       | $V_{SSCAP} = 1V$                             | 2     |     | 2.5   | V     |

| CURRENT  | LIMIT COMPARATOR                     | ·                                            | ·     | ·   | ·     |       |

|          | Current Threshold                    |                                              | 450   | 500 | 550   | mV    |

|          | Input Bias Current                   | $V_{ILIM} = 0.1V$                            |       | 50  | 100   | nA    |

|          | Propagation Delay                    | (Note 2)                                     |       | 150 | 250   | ns    |

| OUTPUT   | DRIVERS                              |                                              |       |     |       | _     |

|          | Output High - B SYNC OUT, B OFF      | VDD 5V, I <sub>LOAD</sub> = 12mA             | 4.625 | 4.8 |       | V     |

|          | Output Low - B SYNC OUT, B OFF       | I <sub>LOAD</sub> 12mA                       |       | 0.2 | 0.375 | V     |

|          | Rise & Fall time - B SYNC OUT, B OFF | C <sub>LOAD</sub> =100pF                     |       | 20  | 50    | ns    |

|          | Output High - B ON                   | VDD 5V, I <sub>LOAD</sub> = 12mA             | 4.625 | 4.8 |       | V     |

|          | Output Low - B ON                    | I <sub>LOAD</sub> 50mA                       |       | 0.2 | 0.375 | V     |

|          | Fall Time - B ON                     | $C_{LOAD} = 2400 \text{pF} (\text{Note } 2)$ |       | 45  | 80    | ns    |

| ONE SHO  | т<br>Т                               |                                              | 1     | 1   |       |       |

|          | Pulse Width                          |                                              | 100   | 150 | 200   | ns    |

## ML4877

### ELECTRICAL CHARACTERISTICS (Continued)

| SYMBOL     | PARAMETER                         | CONDITIONS                | MIN   | ТҮР  | MAX   | UNITS |

|------------|-----------------------------------|---------------------------|-------|------|-------|-------|

| DELAY TI   | MER                               |                           |       |      | 1     | 4     |

|            | Delay Time                        |                           | 20    | 35   | 55    | ns    |

| HIGH VO    | DLTAGE INVERTER                   |                           |       |      | 1     | 4     |

| Oscillator |                                   |                           |       |      |       |       |

|            | Nominal Frequency                 |                           | 68    | 80   | 92    | kHz   |

|            | Discharge Current                 | $V_{CT} = 2V$             | 500   | 700  | 900   | μΑ    |

|            | Peak Voltage                      |                           | 2.3   | 2.5  | 2.7   | V     |

|            | Valley Voltage                    |                           | 0.8   | 1    | 1.2   | V     |

| Output D   | rivers                            |                           |       |      |       | _     |

|            | Output High - L GATE 1, 2         | $VDD = 5V, I_{LOAD} 12mA$ | 4.625 | 4.8  |       | V     |

|            | Output Low - L GATE 1, 2          | $I_{LOAD} = 50 \text{mA}$ |       | 0.2  | 0.375 | V     |

|            | Rise & Fall Time - L GATE 1, 2    | C <sub>LOAD</sub> =1000pF |       | 20   | 50    | ns    |

| Resonant   | Threshold Detector                | ·                         |       |      |       |       |

|            | Threshold                         |                           | 0.45  | 0.8  | 1.15  | V     |

|            | Hysteresis                        |                           | 0.15  | 03   | 0.45  | mV    |

| Lamp Out   | t Detect                          | ·                         |       |      |       |       |

|            | Threshold                         |                           | -2    | VDD  | 2     | %     |

|            | Latch Inhibit Threshold (SSCAP)   | LRTD > VDD + 0.1V         |       | 2.5  |       | V     |

| Under Vo   | Itage Detector                    |                           |       |      |       | _     |

|            | Start Up Threshold                |                           | 3.8   | 4.1  | 4.4   | V     |

|            | Hysteresis                        |                           | 150   | 300  | 450   | mV    |

| Logic Inte | erface (ON/OFF)                   |                           |       |      |       |       |

|            | V <sub>IH</sub>                   | 2.5                       |       |      |       | V     |

|            | V <sub>IL</sub>                   |                           |       | 0.5  |       | V     |

|            | Input Bias Current                | ON/OFF = 3V               |       | 10   | 25    | μΑ    |

| Linear Re  | gulator                           |                           |       |      |       |       |

|            | Aux Zener Reference Voltage (AZR) | $I_{AZR} = 10 \mu A$      | 12.3  | 13.5 | 14.7  | V     |

|            | Regulator Voltage (VDD)           | HVDD = 12V                | 4.75  | 5.0  | 5.35  | V     |

|            | Regulator Source Current          | External to device        |       | 10   |       | mA    |

|            | Drop Out Voltage                  | I <sub>HVDD</sub> = 1mA   |       | 30   | 90    | mA    |

|            | Drop Out Voltage                  | I <sub>HVDD</sub> = 5mA   |       | 125  | 275   | mA    |

|            | HVDD Input Voltage Range          |                           | 5     |      | 18    | V     |

4

### ELECTRICAL CHARACTERISTICS (Continued)

| SYMBOL | PARAMETER             | CONDITIONS               | MIN   | ТҮР | MAX   | UNITS |

|--------|-----------------------|--------------------------|-------|-----|-------|-------|

| BIAS   |                       |                          |       |     | •     |       |

|        | VDD Supply Current    | ON/OFF = "1", no load    |       | 375 | 450   | μΑ    |

|        | VDD Supply Current    | ON/OFF = "0", HVDD = 12V |       | 1   | 10    | μΑ    |

|        | VREF Load Regulation  | $I_{LOAD} = 25 \mu A$    |       | 10  | 20    | mV    |

|        | VREF Output Voltage   | $T_A = 25^{\circ}C$      | 2.47  | 2.5 | 2.53  | V     |

|        | VREF Line Regulation  |                          |       | 20  | 30    | mV    |

|        | VREF Line, Load, Temp |                          | 2.465 | 2.5 | 2.535 | V     |

Note 1: Limits are guaranteed by 100% testing, sampling, or correlation with worst case test conditions.

Note 2: Actual load is 1200pF. The 2:1 transformer reflects an effective 2400pF.

Figure 1. Typical Application Schematic for the ML4877

6

### FUNCTIONAL DESCRIPTION

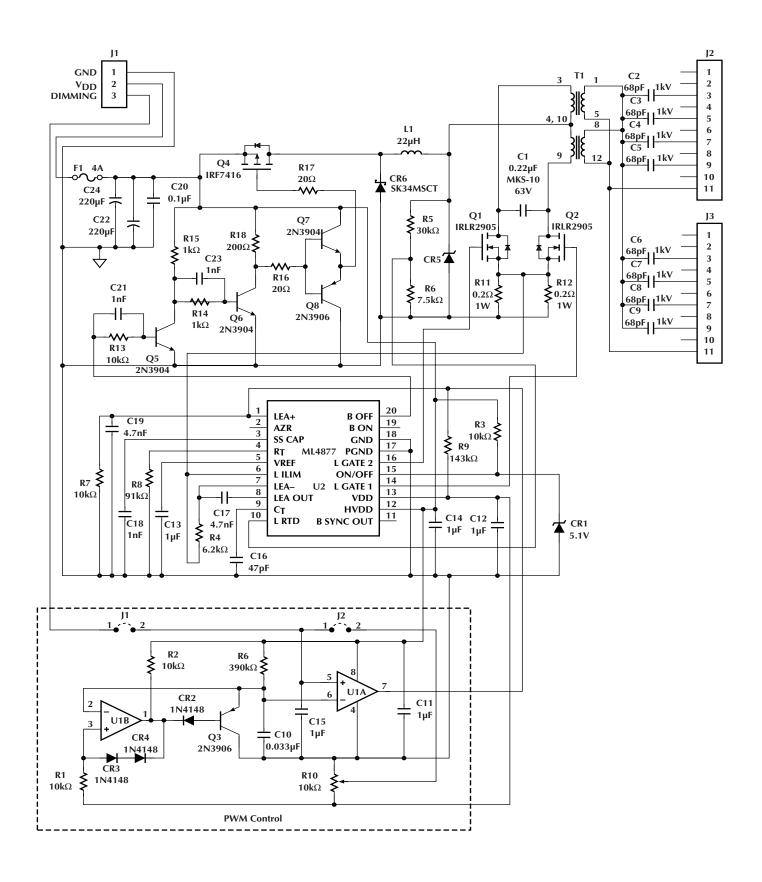

The ML4877 consists of a PWM regulator, a lamp driver/ inverter, a linear regulator and control circuits. This IC, in conjunction with external components, converts a DC battery voltage into the high voltage and high frequency AC signal required to start and drive miniature cold cathode fluorescent lamps. Typical application circuits are shown in Figure 1 and Figure 5. Note: Please read the Power Sequencing section below prior to using the ML4877.

### LAMP DRIVER

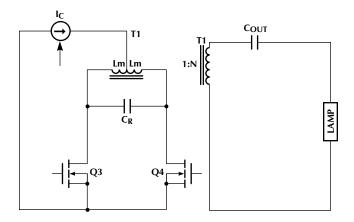

The lamp driver, sometimes referred to as a lamp inverter, is comprised of a PWM regulator and a Royer type inverter circuit to drive the lamp. The PWM regulator, in a buck configuration, controls the magnitude of the lamp current to provide the dimming capability. Figure 2 shows a simplified circuit to more easily illustrate the operation of the circuit.

Due to the presence of the buck inductor, L1, the circuit shown in Figure 2 is essentially a current fed parallel loaded resonant circuit. Lm is the primary inductance of the output transformer, T1, which tunes with the resonant capacitor  $C_R$  to set the resonant frequency of the inverter. The oscillator frequency is always set lower than the natural resonant frequency to ensure synchronization. The current source IC models the current through the buck inductor L1.

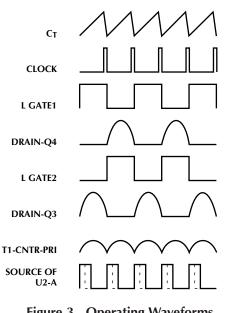

The MOSFETs, (Q3 and Q4) are alternately turned on with a constant 50% duty cycle signal (L GATE1, L GATE2) at one-half the frequency of the oscillator. In this way each transistor pulses, or excites, the resonant tank on each half cycle. The combination of these two signals appear across the primary winding of the output transformer as a sinusoidal waveform. This voltage is multiplied by the step-up turns ratio of the output transformer and impressed across the lamp.

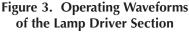

The output transitions are controlled by feedback through the L RTD pin by sensing the voltage at the center tap of the output transformer. Each time this signal reaches the minimum resonant threshold detection point an internal clock pulse is generated to keep the system synchronized. Figure 3 shows some of these representative waveforms at the important nodes of the circuit.

The PWM regulator is comprised of a MOSFET (U2-A), inductor L1, and the gate control and drive circuitry as shown in Figure 1. A signal with a constant pulse width of I 50ns is applied to the primary of the 2:1 pulse transformer T2, rectified by diode D1, and used to charge the gate capacitance of U2-A, thereby turning it on. The turn off is controlled by discharging this capacitance through MOSFET Q2. The pulse width of the signal on the gate of Q2 (B OFF) varies according to the difference of the amplitude of the feedback signal on LEA+, and LEA-. The signal on LEA- is proportional to the AC current flowing in the lamp, while the signal on LEA+ is a function of the brightness control setting. The AC lamp current feedback signal is developed by monitoring the current through resistor R6 in the common source connection of the inverter MOSFETs, Q3 and Q4. The lamp current, and therefore brightness, is adjusted by varying the voltage applied to R4, at the brightness adjust control point. Increasing this voltage increases the brightness.

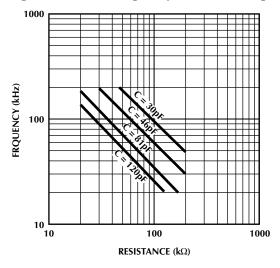

#### OSCILLATOR

Micro Linear

The frequency of the oscillator in the ML4877 is set by selecting the values Of  $C_T$  and  $R_T$ . Figure 4 shows the

Figure 2. Kelvin Sense Connections

### FUNCTIONAL DESCRIPTION (Continued)

oscillator frequency versus the value of RT for different values Of CT. This nomograph may be used to select the appropriate value of RT and CT to achieve the desired oscillator frequency for the ML4877.

### LINEAR REGULATOR

A linear voltage regulator is provided to power the low voltage and low current control circuitry on the ML4877. This is typically used when there is no separate 5V supply available at the inverter board. For operation up to 18V, the linear regulator is used by connecting the HVDD pin to the input battery voltage. For operation over 18V, a MOSFET, and a resistor (Q and R1, Figure 1) are connected as shown. The MOSFET is required to stand off the high voltage. The AZR pin is just a zener diode to ground used to bias the gate of Q1.

### LAMP OUT DETECT

In those cases when there is no lamp connected, or the connection is faulty, the output voltage of the lamp driver circuit will tend to rise to a high level in an attempt to start the nonexistent lamp. The lamp out detect circuit on the ML4877 will detect this condition by sensing a voltage proportional to the center tap voltage on the primary of the output transformer, T1 on the L RTD pin. The ration of resistors R7 and R8 sets the lamp out detect threshold. When the voltage on the L RTD pin exceeds VDD, an internal latch is set and the lamp driver goes into a shutdown mode. The logic control pin ON/OFF must be cycled low, then high to reset the latch and return the lamp driver to the normal state. The input to the lamp out latch is inhibited by the signal on the soft start pin. The latch will not be set until the voltage on SS CAP (pin 3) rises to more than 4.2V nominally.

#### SOFT START

The capability to control the start up behavior is achieved by setting the value of a single capacitor, C2 in Figure 1.

Figure 4. Oscillator Frequency Nomograph

By selecting the appropriate value the AC lamp current can be set to slowly increase with a controlled time constant. The capacitor value can be calculated according to the following formula.

$$C = (3 X 10-7)TS$$

(1)

Where TS = Duration of the soft start sequence in seconds

#### LOGIC CONTROL

The ML4877 is controlled by a single logic input, ON/ OFF. A logic level high on this pin enables the lamp driver. A logic zero puts the circuit into a very low power state.

#### **POWER SEQUENCING**

It is important to observe correct power and logic input sequencing when powering up the ML4877. The following procedure must be observed to avoid damaging the device.

- 1. Apply the battery power to HVDD, or

- 2. If HVDD is not used. Apply the VDD voltage. With HVDD connected the VDD voltage is supplied by the internal regulator on the ML4877.

- 3. Apply a logic high to the ON/OFF input.

Please refer to Application Note 32 for detailed application information beyond what is presented here.

### APPLICATIONS SECTION

#### **HIGH POWER INVERTER**

The ML4877 is easily adapted to high power CCFL inverter designs. Figure 5 displays a schematic of a 30W ML4877 application. This particular design employs PWM dimming in order to extend dimming range.

The 30W inverter design is ideal for applications between the 20W and 30W range. Deep dimming capability is achieved via PWM technique with no flicker and no popon effects. Uniform intensity can be maintained across 1 to 8 lamps to well below 5%.

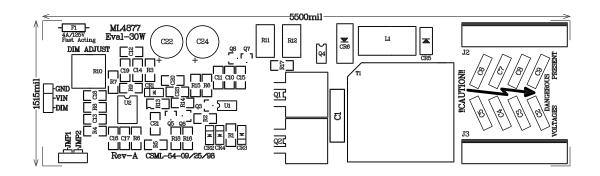

Figure 6 provides a top view of an example of a ML4877 30W design. This design can be modified for 1 to 8 lamps and contains a PWM dimming interface using standard low cost components.

For the latest application notes and other information, visit the Micro Linear website at www.microlinear.com.

Figure 5. 30W Backlight CCFL Inverter with PWM Dimming

Micro Linear

Figure 6. 30W CCFL Inverter Board, 1 to 8 Lamps

10

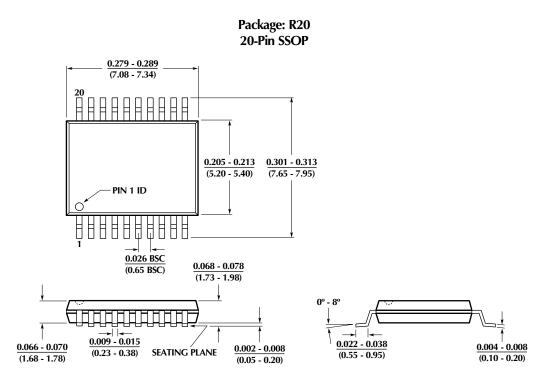

### PHYSICAL DIMENSIONS inches (millimeters)

### **ORDERING INFORMATION**

| PART NUMBER            | TEMPERATURE RANGE | PACKAGE           |  |  |

|------------------------|-------------------|-------------------|--|--|

| ML4877CR (END OF LIFE) | 0°C to 70°C       | Molded SSOP (R20) |  |  |

| ML4877ER (OBSOLETE)    | –20°C to 70°C     | Molded SSOP (R20) |  |  |

Micro Linear

© Micro Linear 1998. 🕸 Micro Linear is a registered trademark of Micro Linear Corporation. All other trademarks are the property of their respective owners.

#### DS4877-01

Products described herein may be covered by one or more of the following U.S. patents: 4,897,611; 4,964,026; 5,027,116; 5,281,862; 5,283,483; 5,418,502; 5,508,570; 5,510,727; 5,523,940; 5,546,017; 5,559,470; 5,565,761; 5,592,128; 5,594,376; 5,652,479; 5,661,427; 5,663,874; 5,672,959; 5,689,167; 5,714,897; 5,717,798; 5,742,151; 5,747,977; 5,754,012; 5,757,174; 5,767,653; 5,777,514; 5,793,168; 5,798,635; 5,804,950; 5,808,455; 5,811,999; 5,818,207; 5,818,669; 5,825,165; 5,825,223. Japan: 2,598,946; 2,619,299; 2,704,176; 2,821,714. Other patents are pending.

Micro Linear reserves the right to make changes to any product herein to improve reliability, function or design. Micro Linear does not assume any liability arising out of the application or use of any product described herein, neither does it convey any license under its patent right nor the rights of others. The circuits contained in this data sheet are offered as possible applications only. Micro Linear makes no warranties or representations as to whether the illustrated circuits infringe any intellectual property rights of others, and will accept no responsibility or liability for use of any application herein. The customer is urged to consult with appropriate legal coursel before deciding on a particular application.

2092 Concourse Drive San Jose, CA 95131 Tel: (408) 433-5200 Fax: (408) 432-0295 www.microlinear.com

10/29/98 Printed in U.S.A.