# TMP82C51AP-2 / TMP82C51AP-10 TMP82C51AM-2 / TMP82C51AM-10

## PROGRAMMABLE COMMUNICATION INTERFACE

#### GENERAL DESCRIPTION

The TMP82C51A is the industry standard Universal Synchronous/Asynchronous Receiver/Transmitter (USART) that is fabricated using C-MOS silicon gate technology. The 82C51A is mainly used for 8-bit microcomputer extention system, which require serial data communications.

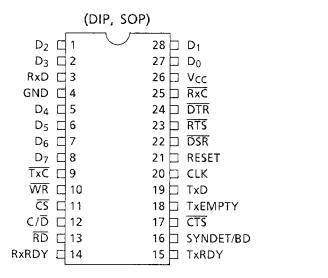

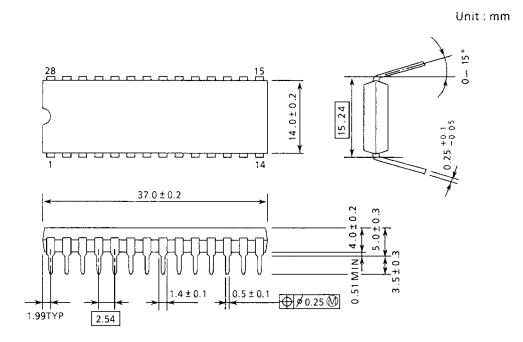

The TMP82C51AP-2/TMP82C51AP-10 is packaged in the 28 pin standard Dual Inline Package.

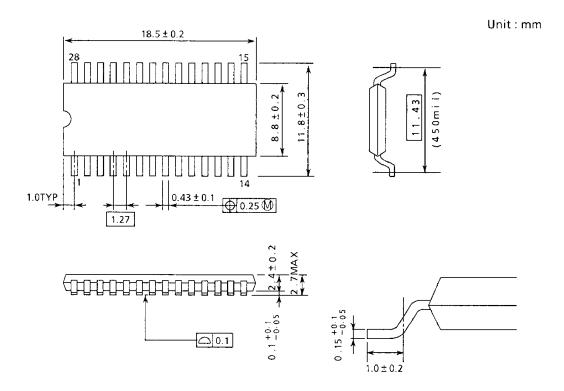

The TMP82C51AM-2/TMP82C51AM-10 is packaged in the 28 pin Small Out Line Package.

#### **FEATURES**

#### • Synchronous:

5-8 Bit Characters

Internal or External Character Synchronization

Single or Double Character Synchronization (Inrternal)

Automatic Sync Character(s) Insertion

#### • Asynchronous:

5-8 Bit Characters

Clock Rate -1, 16 or 64 Times Transfer Rate

**Break Character Generation**

1, 1.5 or 2 stop Bits

False Start Bit Detection

Automatic Break Detect and Handling

• Transfer Rate TMP82C51A-2 TMP82C51A-10

DC-104K bps DC-300K bps

- Full-Duplex, Double-Buffered, Transmitter and Receiver

- Error DetectionParity, Overrun and Framing.

- Single +5V Supply:  $5V \pm 10\%$

050489

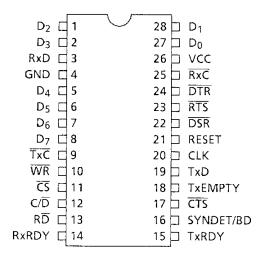

### 2. PIN CONNECTIONS

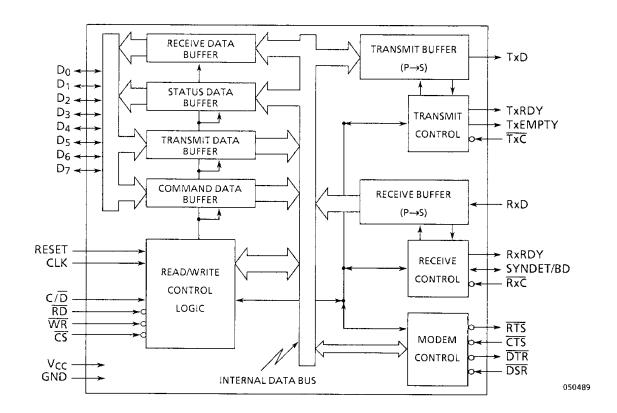

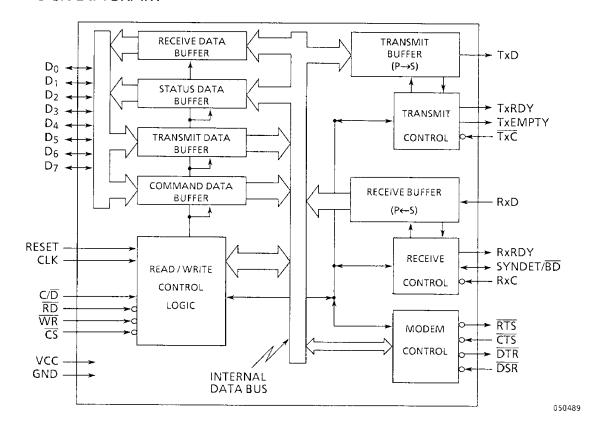

3. BLOCK DIAGRAM

### 4. PIN NAMES AND PIN DESCRIPTIONS

### 4.1 INTERFACE SIGNALS TO CPU (MAIN SYSTEM)

## • D0-D7 (Input/Output)

This 3-state, bidirectional, 8-bit buffer is used to interface with the system Data Bus. Data is transmitted or received through the buffer upon execution of Input or Output Instructions of the CPU. Control Words, Command Words and Status Information are also transferred through the Data Bus Buffer.

## • WR (Input)

A "low" level signal on this input informs the 82C51A that the CPU is Writing Data or Control Words to the 82C51A.

### • RD (Input)

A "low" level signal on this input informs the 82C51A that the CPU is Reading Data or Status Information from the 82C51A.

### • $\overline{\text{CS}}$ (Input)

A "low" level signal on this input selects the 82C51A. No reading or writing operation will occur unless the device is selected. When  $\overline{CS}$  is "high" the Data Bus is in the floating state and  $\overline{RD}$  and  $\overline{WR}$  have no effect on the chip.

### • C/\overline{D} (Input)

This input signal, in conjuction with the  $\overline{WR}$  and  $\overline{RD}$  inputs, informs the 82C51A that the word on the Data Bus is either a Data Bus Character, Control Word or Status Information. A "high" level signal means Control or Status, a "low" level signal means Data.

| C/ <u>D</u> | RD | WR | CS |                                        |

|-------------|----|----|----|----------------------------------------|

| 0           | 0  | 1  | 0  | 82C51A Receive DATA Buffer → DATA Bus  |

| 0           | 1  | 0  | 0  | 82C51A Transmit DATA Buffer ← DATA Bus |

| 1           | 0  | 1  | 0  | 82C51A Status DATA Buffer → DATA Bus   |

| X           | 1  | 1  | 0  | DATA Bus is in floating state.         |

| X           | Х  | Х  | 1  | DATA Bus is in floating state.         |

#### CLK (Input)

The CLK input is used to generate internal device timing. No external input or output referenced to CLK, but the frequency of CLK must be greater than 30 times the Receiver or Transmitter Data Bit Rates ( $\overline{\text{RxC}}$  or  $\overline{\text{TxC}}$ ) in Synchronous Operation, and greater than 4.5 times the Receiver Data Bit Rates ( $\overline{\text{RxC}}$  or Transmiter,  $\overline{\text{TxC}}$ ) in Asynchronous operation.

## • RESET (Input)

A "high" level signal on this input forces the 82C51A into an "Idle" mode. The device will remain "Idle" until a new set of Control Words is written into the 82C51A to program its functional definition. Minimum RESET pulse width is 6 tcy.

#### 4.2 MODEM CONTROL SIGNALS

### • $\overline{\mathrm{DSR}}$ (Input)

The  $\overline{\rm DSR}$  input signal is a general purpose, 1-bit inverting input port. Its condition can be tested by the CPU using a Status Read Operation. The  $\overline{\rm DSR}$  input is normally used to test MODEM conditions such as Data Set Ready signal.

## • $\overline{\mathrm{DTR}}$ (Output)

The  $\overline{DTR}$  output signal is a general purpose, 1-bit inverting output port. It can be set "low" by programming the appropriate bit in the Command Instruction Words. The  $\overline{DTR}$  output signal is normally used for MODEM control such as Data Terminal Ready or Rate Select signal.

## • RTS (Output)

The  $\overline{\text{RTS}}$  output signal is a general purpose, 1-bit inverting output port. It can be set "low" by pogramming the appropriate bit in the Command Instruction Word. The  $\overline{\text{RTS}}$  output signal is normally used for MODEM control such as Request to Send signal.

## • $\overline{\text{CTS}}$ (Input)

A "low" level signal on this input enables the 82C51A to transmit serial data, if the Tx Enable Bit in the Command Byte is set to a "one" (TxEN=1). If either a Tx Enable off (TxEN=0) or  $\overline{CTS}$  off (CTS=1) condition occurs while the Tx is in operaion, the Tx will transmit all the data in the USART, written prior to Tx Disable Command before shutting down.

#### 4.3 TRANSMIT CONTROL SIGNALS

### • TxC (Input)

The transmitter Clock controls the rate at which the character is to be transmitted. In the Synchronous Transmission Mode, the Transfer Rate (1x) is equal to the  $\overline{TxC}$  frequency. In Asynchronous Transmission Mode the transfer rate is a fraction of the actual  $\overline{TxC}$  ferquency. A portion of the Mode Instruction selects this factor; it can be 1, 1/16 or 1/64 the  $\overline{TxC}$ .

For Example:

```

If Transfer Rate equals 110 bps,

\overline{\text{TxC}} = 110 \text{ Hz} (1x)

```

$\overline{\text{TxC}} = 1.76 \text{ kHz} \quad (16x)$   $\overline{\text{TxC}} = 7.04 \text{ Hz} \quad (64x)$

The falling edge of  $\overline{\text{TxC}}$  shifts the serial data out of the 82C51A.

## • TxD (Output)

This line is used to transmit serial data. Serial output data on TxD is changed from parallel data to serial data in accordance with the TxD line will be held in the marking state ('1' level) immediately on one of the followings.

- · Master Reset ·

- · Tx Disable (TxEN = 0)

- · CTS signal is high  $(\overline{CTS}=1)$  · TxEMPTY signal is high (TxEMPTY=1)

### • TxRDY (Output)

This output informs the CPU that the transmitter is ready to accept a Data Character. The TxRDY output pin can be used as an interrupt to the system, since it is masked by Tx Disable (TxEN=0), or, for polled Operation, the CPU can check TxRDY using a Status Read Operation, TxRDY is automatically reset by the trailing edge of  $\overline{WR}$  when a Data Character is loaded from the CPU. The TxRDY pin output status (TxRDY (pin)) is different from the TxRDY status bit status register (TxRDY (status bit)) as follows.

```

TxRDY (status bit) = (Transmit Data Buffer Empty)

TxRDY (pin) = (Transmit Data Buffer Empty) AND (\overline{CTS} = 0) AND (TxEN = 1)

```

### • TxEMPTY (Output)

The TxEMPTY output will go "high" when the 82C51A has no characters to send. It resets upon receiving a character from the CPU if the transmitter is enabled.

In Synchronous Mode, a "high" level signal on this output indicates that a Character has not been loaded and the SYNC Character or Characters are about to be or are being transmitted automatically as "fillers". TxEMPTY does not go "low" when the SYNC characters are being shifted out.

TOSHIBA TMP82C51A

#### 4.4 RECEIVE CONTROL SIGNALS

## • RxC (Input)

The Receiver Clock controls the rate at which the character is to be received. In Synchronous Mode, the Transfer Rate (1x) is equal to the actual frequency of  $\overline{RxC}$ . In Asynchronous Mode, the Transfer Rate is a fraction of the actual  $\overline{RxC}$  frequency. A portion of the Mode Instruction selects this factor; 1, 1/16 or 1/64 the  $\overline{RxC}$ .

For Example:

If Transfere Rate equals 2400 bps,

$\overline{\text{RxC}} = 2.4 \text{ kHz}$  (1x)

$\overline{RxC} = 38.4 \text{ kHz}$  (16x)

$RxC = 153.6 \, \text{kHz} \, (64x)$

Data is sampled into the 82C51A on the rising edge of RxC.

#### • RxD (Input)

This line is used to receive the serial data. Serial input data on this line is changed to parallel data in accordance with the format specified by the Control Words, and then transfered to the Receive Data Buffer.

## • RxRDY (Output)

This output indicates that the 82C51A contains a Data Character that is ready to be input to the CPU. RxRDY can be connected to the interrupt structure of the CPU, or, for Polled Operation, the CPU can check the condition of RxRDY using Status Read Operation.

Rx Enable off both masks and holds RxRDY in the Reset Condition.

#### • SYNDET/BD (Input/Output)

This pin is used for SYNDET in Synchronous Mode and may used as either input or output, programmable through the Control Word. It is reset to output mode "low" upon RESET. When used as an Output (Internal Sync Mode), the SYNDET pin will go "high" to indicate that the 82C51A has located the SYNC Character in the Receive Mode. If the 82C51A is programmed to use Double Sync Characters then SYDET will go "high" in the middle of the last bit of the second SYNC Character. SYNDET is automatically reset upon a Status Read Operation. When used as an Input (External Sync Mode), a positive going signal will cause the 82C51A to start assembling Data Characters on the rising edge of the next  $\overline{RxC}$ .

In Asynchronous Mode this pin is used BD.

This output will go "high" whenever the receiver remains "low" through two consecutive Stop Bit Sequences (including the Start Bits, Data Bits, and parity bits). Break Detect may also be read as a Status Bit.

It is reset only upon a Master Chip Reset or Rx Data returning to a "one" state.

#### 4.5 POWER SUPPLY

- VCC (Power)

- +5 Volt supply

- GND (Power)

- 0 Volt supply

## 5. ELECTRICAL CHARACTERISTICS

## 5.1 MAXIMUM RATINGS

| Symbol              | ltem                                       | Rating                          |

|---------------------|--------------------------------------------|---------------------------------|

| Vcc                 | Power Supply Voltage (with respect to GND) | - 0.5V to 7.0V                  |

| V <sub>IN</sub>     | Input Voltage (with respect to GND)        | - 0.5V to V <sub>CC</sub> + 0.5 |

| V <sub>QUT</sub>    | Output Voltage (with respect to GND)       | - 0.5V to V <sub>CC</sub> + 0.5 |

| PD                  | Power Dissipation                          | 250mW                           |

| T <sub>SOLDER</sub> | Soldering Temperature (10 sec)             | 260°C                           |

| T <sub>STG.</sub>   | Storage Temperature                        | – 65°C to 150°C                 |

| T <sub>OPR</sub> .  | Operating Temperature                      | – 40°C to 85°C                  |

050489

## 5.2 D.C CHARACTERS

Topr = -40°C to +85°C, VCC =  $+5V \pm 10\%$ , GND = 0V, Unless otherwise noted.

| Symbol           | Parameter                                    | Test Conditions                                                         | Min.      | Тур. | Max.      | Units |

|------------------|----------------------------------------------|-------------------------------------------------------------------------|-----------|------|-----------|-------|

| VIL              | Input Low Voltage                            |                                                                         | - 0.5     |      | 0.8       | V     |

| V <sub>IH</sub>  | Input High Voltage                           |                                                                         | 2.2       | _    | VCC + 0.5 | V     |

| V <sub>OL</sub>  | Output Low Voltage                           | IOL = 2.2mA                                                             | _         | -    | 0.45      | V     |

| V <sub>OH1</sub> | Output High Voltage                          | IOH = - 400µA                                                           | 2.4       | -    | -         | V     |

| V <sub>OH2</sub> | Output High Voltage                          | IOH = - 100μA                                                           | Vcc - 0.8 | _    | _         | V     |

| IOFL             | Output Leak Current                          | 0.45V≦ VOUT≦ VCC                                                        | -         | _    | ± 10      | μА    |

| IIL              | Input Leak Current                           | 0.45V≦ VOUT≦ VCC                                                        | -         | _    | ± 10      | μА    |

|                  | Power Supply Current<br>(AP-2/AM-2, 5MHz)    | tcyc = 200ns<br>Vin = 4.8V/0.2V                                         | -         | 1.2  | 5.0       | mA    |

| ICC1             | Power Supply Current<br>(AP-8/AM-8, 8MHz)    | tcyc = 125ns<br>Vin = 4.8V/0.2V                                         | _         | 2.0  | 10.0      | mA    |

|                  | Power Supply Current<br>(AP-10/AM-10, 10MHz) | tcyc = 100ns<br>Vin = 4.8V/0.2V                                         | _         | 2.5  | 15        | mA    |

| ICC2             | Power Supply Current<br>(Standby Mode)       | STOP All Clocks<br>VCC = 5V, \( \overline{CS} = 1 \)<br>Vin = 4.8V/0.2V | _         | 0.5  | 10.0      | μΑ    |

## 5.3 AC CHARACTERISTICS

Topr = -40°C to 85°C, VCC =  $5V \pm 10\%$ , GND = 0V, Unless otherwise noted.

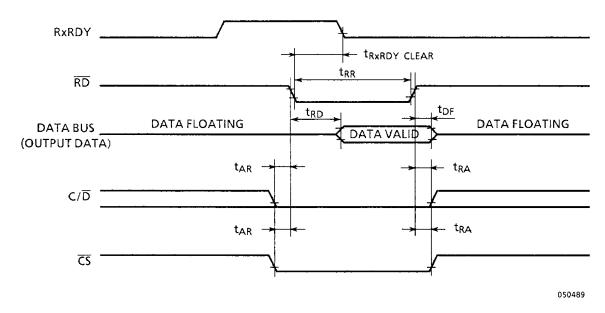

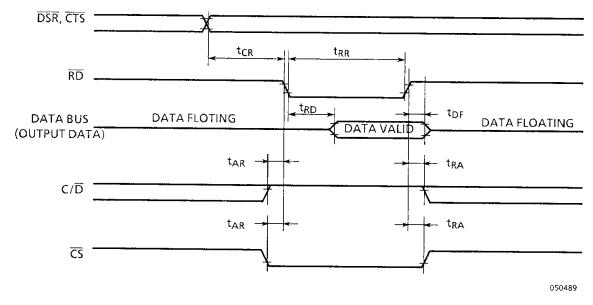

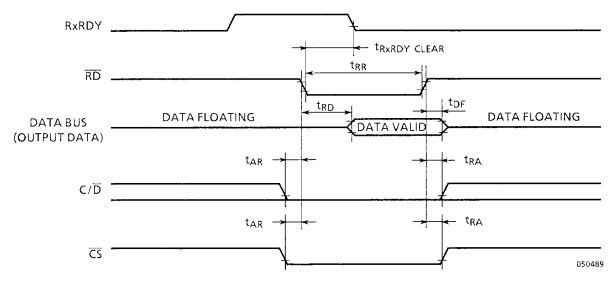

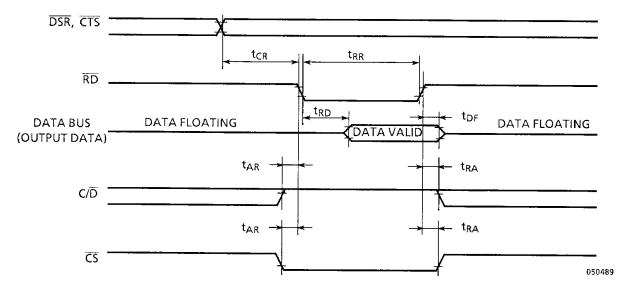

## 5.3.1 Bus Read Cycle Timing Note 1)

| Symbol          | Parameter                         | Test                  | AP-2 / AM-2 |      | AP-10 | 11-14- |       |  |

|-----------------|-----------------------------------|-----------------------|-------------|------|-------|--------|-------|--|

| Symbol          | rarameter                         | Conditions            | Min.        | Max. | Min.  | Max.   | Units |  |

| tAR             | CS, C/D Set-up<br>Time for RD     |                       | 0           | _    | 0     | _      | nS    |  |

| t <sub>RA</sub> | CS, C/D Hold<br>Time for RD       |                       | 0           | _    | 0     | -      | nS    |  |

| t <sub>RR</sub> | RD Pulse Width                    |                       | 150         | -    | 120   | _      | nS    |  |

| t <sub>RD</sub> | Data Delay Time<br>for RD Note 2) | CL = 150pF<br>Note 3) |             | 140  | _     | 100    | n\$   |  |

| t <sub>DF</sub> | Data Hold Time for RD             |                       | 10          | 80   | 10    | 50     | nS    |  |

230589

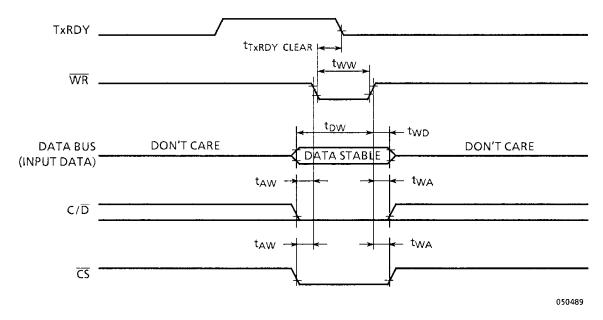

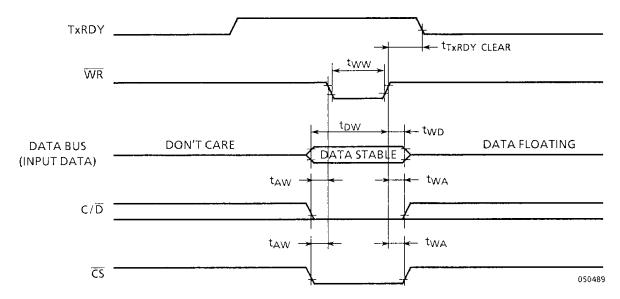

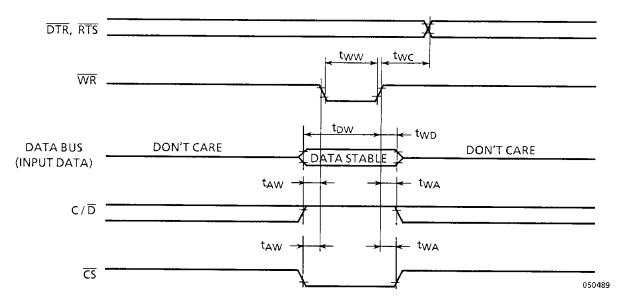

## 5.3.2 Bus Write Cycle Timing (Note 1)

| Symbol          | Parameter                      | Test       | AP-2 | 'AM-2 | AP-10 | 'AM-10 | Units |

|-----------------|--------------------------------|------------|------|-------|-------|--------|-------|

| Jymbol          | Tarameter                      | Conditions | Min. | Max.  | Min.  | Max.   | Units |

| t <sub>AW</sub> | CS, C/D Set-up<br>Time for WR  |            | 0    | _     | 0     | _      | n\$   |

| t <sub>WA</sub> | CS, C/D Hold<br>Time for WR    |            | 0    | _     | 0     | -      | nS    |

| tww             | RD Pulse Width                 |            | 150  | _     | 120   | -      | nS    |

| t <sub>DW</sub> | Data Set-up Time<br>for WR     |            | 100  | _     | 70    | _      | n\$   |

| t <sub>WD</sub> | Data Hold Time<br>for WR       |            | 0    | _     | 0     | _      | nS    |

| t <sub>RV</sub> | Recovery Time Between<br>Write | Note 4)    | 6    | _     | 6     | -      | tcyc  |

TOSHIBA TMP82C51A

## 5.3.3 Other Timings

| C       | D                    | Test           | AP-2 | / AM-2 | AP-10 | / AM-10 |       |

|---------|----------------------|----------------|------|--------|-------|---------|-------|

| Symbol  | Parameter            | Conditions     | Min. | Max.   | Min.  | Max.    | Units |

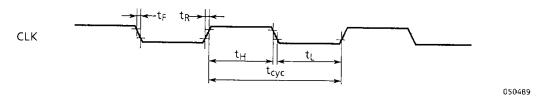

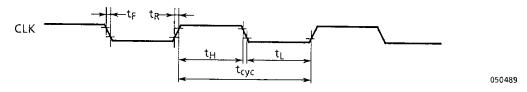

| tcyc    | Clock Period Note    | 5), 6)         | 200  | -      | 100   | -       | nS    |

| tH      | Clock High Level V   | Vdith          | 80   | _      | 40    | -       | nS    |

| tL      | Clock Low Level W    | dith/          | 50   | _      | 30    | _       | nS    |

| tR, tF  | Clock Rise, Fall Tir | ne             | _    | 20     | _     | 10      | nS    |

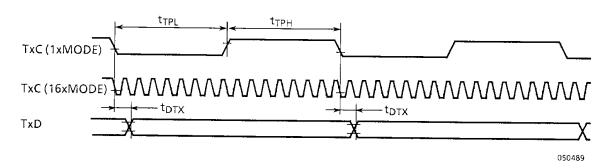

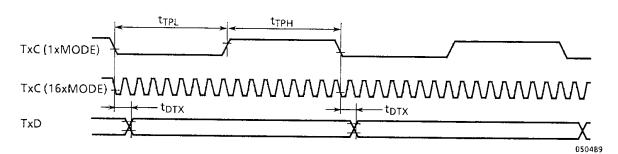

| tDTx    | TxD Delay Time fro   | om Falling     | _    | 1      | _     | 0.5     | us    |

|         | Edge of TxC          |                |      |        |       |         |       |

|         | Transmitter Input    | 1xBaud Rate    | DC   | 104    | DC    | 300     |       |

| fTx     | Clock Frequency      | 16xBaud Rate   | DC   | 528    | DC    | 2000    | kHz   |

|         |                      | 64xBaud Rate   | DC   | 832    | DC    | 2000    |       |

|         | Transmitter Input    | 1xBaud Rate    | 12   | _      | 12    |         |       |

| tTPH    | Clock Low Level      | 16x, 64x,      | 1    |        | 1     | _       | tcyc  |

|         | Width                | Baud Rate      |      |        |       |         |       |

|         | Transmitter Input    | 1xBaud Rate    | 15   | -      | 15    |         |       |

| tTPL    | Clock High Level     | 16x, 64x,      | 3    | _      | 3     | _       | tcyc  |

|         | Width                | Baud Rate      |      |        |       |         |       |

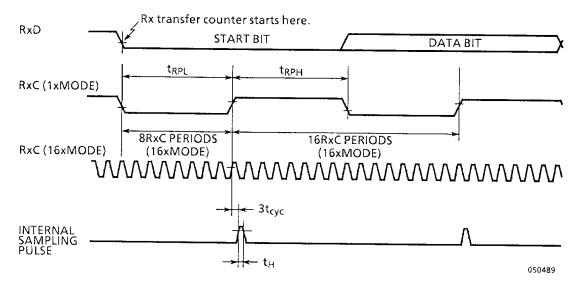

|         | Receiver Input       | 1xBaud Rate    | DC   | 104    | DC    | 300     |       |

| fRx     | Clock Frequency      | 16xBaud Rate   | DC   | 528    | DC    | 2000    | kHz   |

|         |                      | 64xBaud Rate   | DC   | 832    | DC    | 2000    | 1     |

|         | Receiver Input       | 1xBaud Rate    | 12   | _      | 12    | -       |       |

| tRPH    | Clock High Level     | 16x, 64x,      | 1    | _      | 1     | _       | tcyc  |

|         | Width                | Baud Rate      |      |        | 1     |         |       |

|         | Receiver Input       | 1xBaud Rate    | 15   |        | 15    | _       |       |

| tRPH    | Clock Low Level      | 16x, 64x,      | 3    | -      | 3     | _       | tcyc  |

|         | Width                | Baud Rate      |      |        |       |         |       |

| +TD.D.V | TxRDY Pin Delay T    | ime from       | -    | 14     |       | 14      | tcyc  |

| tTxRDY  | Center of Last Bit   |                |      |        |       |         |       |

| tTxRDY  | TxRDY Clear Delay    | Time from      | -    | 400    | _     | 150     | ns    |

| CLEAR   | Leading Edge of W    | /R             |      |        |       |         |       |

| +B.,DDV | TxRDY Pin Delay T    | ime from       | _    | 26     | _     | 26      | tcyc  |

| tRxRDY  | Center of Last Bit   |                |      |        |       |         |       |

| tRxRDY  | TxRDY Clear Delay    | Time from      | -    | 400    | _     | 150     | ns    |

| CLEAR   | Leading Edge of W    | /R             |      |        |       |         |       |

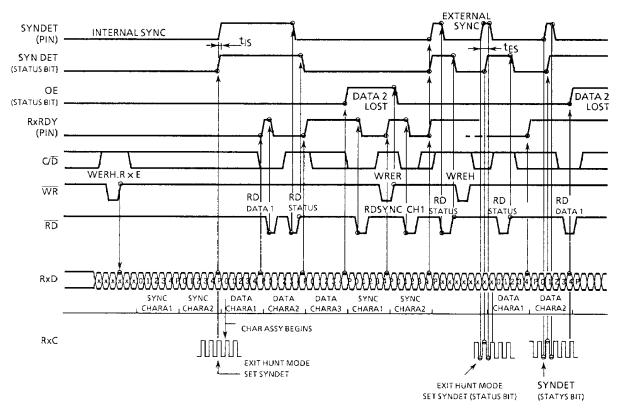

| tIS     | Internal SYNDET D    | elay Time      | -    | 26     | -     | 26      | tcyc  |

| us      | from Rising Edge o   | of RxC         |      |        |       |         |       |

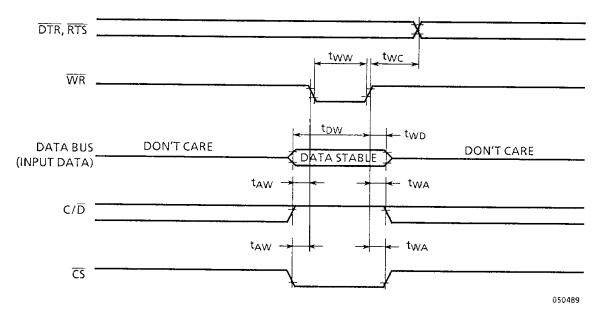

| tES     | External SYNDET S    | et-up Time for | -    | 18     | _     | 18      | tcyc  |

| (C)     | Falling Edge of Rx0  | <del>-</del>   |      |        |       | :       |       |

| tTx     | TxEMPTY Delay Tir    | ne from        | _    | 20     | -     | 20      | tcyc  |

| EMPTY   | Center of Last Bit   |                |      |        |       |         |       |

| +\\\(C  | Control Delay Time   | e from Rising  | _    | 8      | _     | 8       | tcyc  |

| tWC     | Edge of WR (TxEN,    | DTR RTS)       |      |        |       |         |       |

| tCR     | DSR, CTS Set-up Tir  | me for RD      | 20   | _      | 20    | _       | tcyc  |

#### Notes:

- 1) AC Test Condition: Output measuring points VOH=2.2V, VOL=0.8V Input supply level VIH=2.4V, VIL=0.45V

- 2) Assumes that Address is valid before the falling edge  $\overline{RD}$ .

- 3) CL means load capacitance.

- 4) This recovery time is defind only for Mode Intialization. Write Data is allowed only when TxRDY = 1. Recovery Time between Writes for Asynchronous Mode is 8 tcyc and for Synchronous Mode is 16 tcyc.

- 5) The TxC and RxC frequencies have the following limitations with respect to CLK: For 1x Transfer Rate, fTx or fRx < 1 (30 tcyc) For 16x and 64x Transfer Rate, fTx or fRx ≤ 1 (4.5 tcyc)

- 6) Minimum Reset Pulse Width is 6 tcyc. System Clock must running during Reset.

- Status up data can have a maximum delay of 28 clock periods from the event affecting the status.

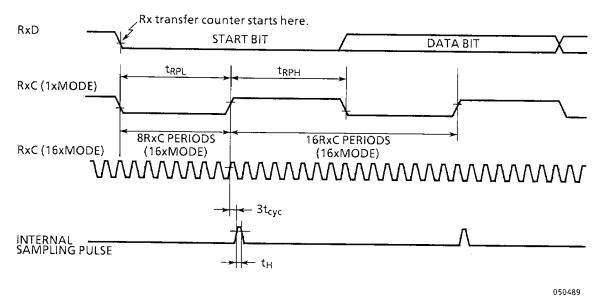

## 6. TIMING WAVEFORMS

Figure 6.1 System Clock

Figure 6.2 Transmitter Clock and Data

Figure 6.3 Receiver Clock and Data

Figure 6.4 Write Data Cycle (MPU  $\rightarrow$  82C51A)

Figure 6.5 Read Data Cycle (82C51A → MPU)

Figure 6.6 Write Control or Output Port Cycle (MPU  $\rightarrow$  82C51A)

Figure 6.7 Read Control or Input Port Cycle (82C51A  $\rightarrow$  MPU)

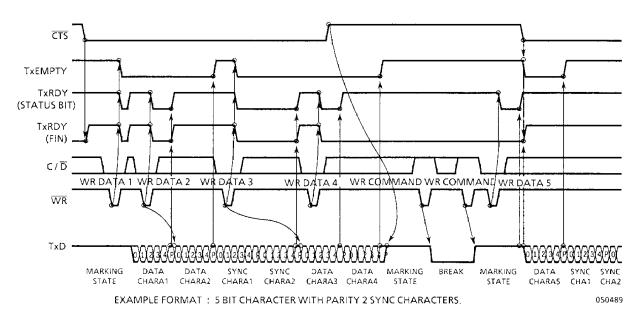

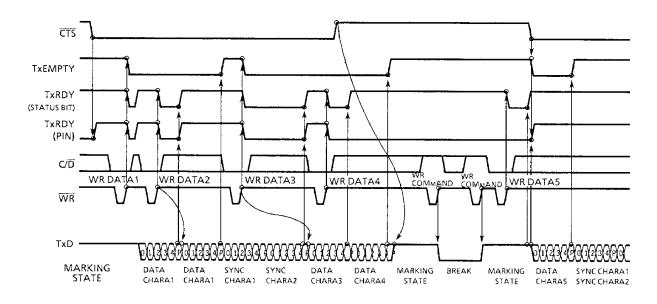

Figure 6.8 Transmitter Control and Flag Timing (SYNC Mode)

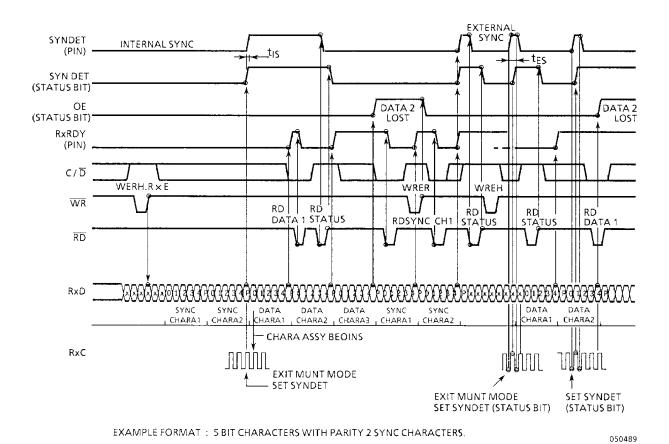

Figure 6.9 Receiver Control and Flag Timimg (SYNC Mode)

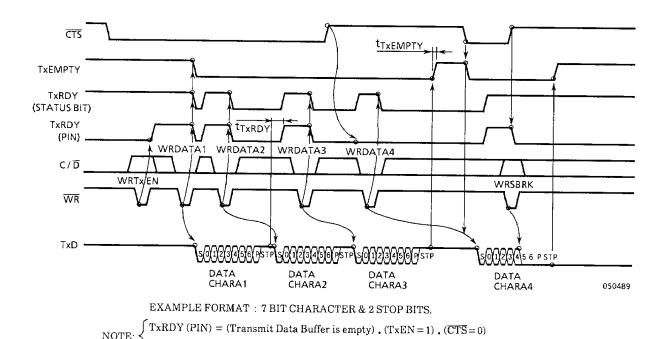

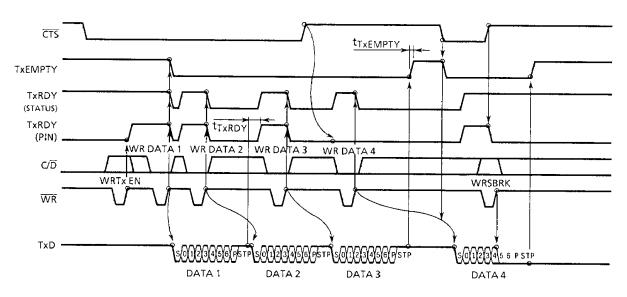

Figure 6.10 Transmitter Control and Flag Timimg (ASYNC Mode)

TxRDY (STATUS BIT) = (Transmit Data Buffer is empty)

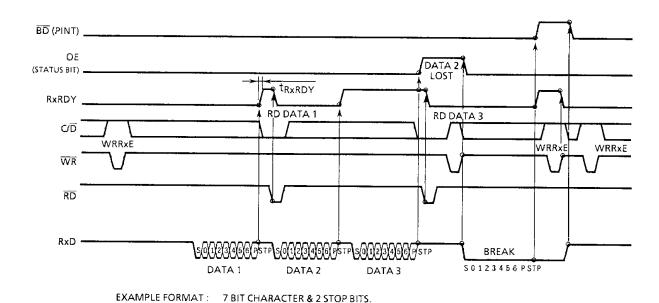

Figure 6.11 Receiver Control and Flag Timing (ASYNC Mode)

## 7. OUTLINE DRAWING

## 7.1 DIP

DIP28-P-600

270289

Note: Lead pitch is 2.54mm and to lerance is  $\pm 0.25$ mm against theoretical center of each lead that is obtained on the basis of No.1 and No.28 leads.

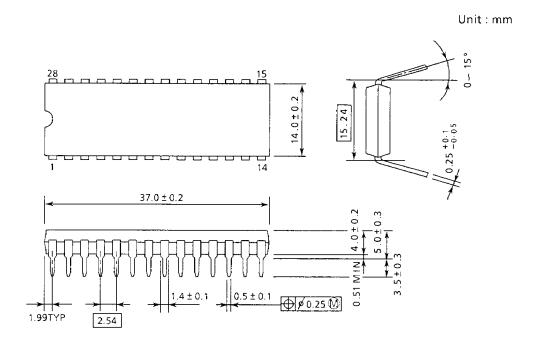

7.2 SOP

SOP28-P-450

270289

Note: Package Width and Length do not include Mold Protrusions.

Allowable Mold Protrusion is 0.15mm.

## PROGRAMMABLE COMMUNICATION INTERFACE

## TMP8251AP

## 1. GENERAL DESCRIPTION

The TMP8251AP is the industry standard Universal Synchronous/Asynchoronous Receiver/Transmitter (USART) that is fabricated using N-channel silicon gate MOS technology.

The TMP8251A is mainly used for 8-bit microcomputer extension systems, which require serial data communications.

The TMP8251AP is packaged in the 28pin standard Dual Inline package.

#### **FEATURES**

• Synchoronous:

5-8 Bit Characters

Internal or External Character Synchronization

Single or Double Character Synchronization (Internal)

Automatic Sync Insertion

Asynchronous:

5-8 Bit Characters

Clock Rate - 1, 16 or 64 Times Transfer Rate

Break Character Generation

1, 1.5, or 2 Stop Bits

False Start Bit Detection

Automatic Break Detect and Handling

Transfer Rate DC to 64K bps (Synchronous)

DC to 19.6K bps (Asynchronous)

- Full-Duplex, Double-Buffered, Transmitter and Receiver

- Error DetectionParity, Overrun and Framing

- Single +5V Supply

- Compatible with Intel's 8251A/S2657

## 2. PIN CONNECTIONS (TOP VIEW)

050489

## 3. BLOCK DIAGRAM

## 4. PIN NAMES AND PIN DESCRIPTIONS

## 4.1 INTERFACE SIGNALS TO MPU (MAIN SYSTEM)

## • D<sub>0</sub>~D<sub>7</sub> (Input/Output)

This 3-state bidirectional, 8-bit buffer is used to interface the 8251A to the system Data Bus. Data is transmitted or received through the buffer upon execution of Input or Output Instructions of the MPU. Control Words, Command Words and Status Information are also transferred through the Data Bus Buffer.

## • WR (Input)

A "low" level signal on this input informs the 8251A that the MPU is Writing Data or Control Words to the 8251A.

## • RD (Input)

A "low" level signal on this input informs the 8251A that the MPU is Reading Data or Status Information from the 8251A.

## • $\overline{\text{CS}}$ (Input)

A "low" level signal on this input selects the 8251A. No reading or writing operation will occur unless the device is selected. When  $\overline{CS}$  is "high" the Data Bus is in the floating state and  $\overline{RD}$  and  $\overline{WR}$  have no effect on the chips.

## • $C/\overline{D}$ (Input)

This input signal, in conjunction with the  $\overline{WR}$  and  $\overline{RD}$  inputs, informs the 8251A that the word on the Data Bus is either a Data Character, Control Word or Status Information. A "high" level signal means Control or Status, a "low" level signal means Data.

| C/D | RD | WR | CS |                                       |

|-----|----|----|----|---------------------------------------|

| 0   | 0  | 1  | 0  | 8251A Recieve DATA Buffer → Data Bus  |

| 0   | 1  | 0  | 0  | 8251A Transmit DATA Buffer ← Data Bus |

| 1   | 0  | 1  | 0  | 8251A Status DATA Buffer → Data Bus   |

| 1   | 1  | 0  | 0  | 8251A Command DATA Buffer ← Data Bus  |

| ×   | 1  | 1  | 0  | DATA Bus is in floating state.        |

| ×   | ×  | ×  | 1  | 4                                     |

## • CLK (Input)

The CLK input is used to generate internal device timing. No external input or output is referenced to CLK, but the frequency of CLK must be greater than 30 times the Receiver or Transmitter Data Bit Rates ( $\overline{\text{RxC}}$  or  $\overline{\text{TxC}}$ ) in Synchronous Operation, and greater than 4.5 times the Receiver Data Bit Rated ( $\overline{\text{RxC}}$ ) in Asynchronous Operation.

## • RESET (Input)

A "high" level signal on this input forces the 8251A into an "Idle" mode. The device will remain at "Idel" until a new set of Control Words is written into the 8251A to program its functional definition. Minimum RESET pulse width is 6 tcy.

#### 4.2 MODEM CONTROL SIGNALS

## • $\overline{\mathrm{DSR}}$ (Input)

The  $\overline{\text{DSR}}$  input signal is a general purpose, 1-bit inverting input port. Its condition can be tested by the MPU using a Status Read Operation. The  $\overline{\text{DSR}}$  input is normlally used to test MODEM conditions such as Data Set Ready signal.

## • DTR (Output)

The  $\overline{DTR}$  output signal is a general purpose, 1-bit inverting output port. It can be set "low" by programming the appropriate bit in the Command Instruction Word. The  $\overline{DTR}$  output signal is normally used for MODEM control such as Data Terminal Ready or Rate Select signal.

## • RTS (Output)

The  $\overline{RTS}$  output signal is a general purpose, 1-bit inverting output port. It can be set "low" by programming the appropriate bit in the Command Instruction Word. The  $\overline{RTS}$  output signal is normally used for MODEM control such as Request to Send signal.

#### $\bullet$ $\overline{\text{CTS}}$ (Input)

A "low" level signal on this input enables the 8251A to transmit serial data, if the Tx Enable Bit in the Command Byte is set to a "one" (TxEN=1). If either a Tx Enable off (TxEN=0) or CTS off (CTS=1) condition occurs while the Tx is in operation, the Tx will transmit all the data in the USART, written prior to Tx Disable Command before shutting down.

#### 4.3 TRANSMIT CONTROL SIGNALS

## • TxC (Input)

The Transmitter Clock Controls the rate at which the character is to be transmitted. In the Synchronous Transmission Mode, the transfer rate (1x) is equal to the  $\overline{\text{TxC}}$  frequency. In Asynchronous Transmission Mode, the transfer rate is a fraction of the actual  $\overline{\text{TxC}}$  frequency. A poriton of the Mode Instruction selects this factor; it can be 1,  $^{1}/_{16}$  or  $^{1}/_{64}$  the  $\overline{\text{TxC}}$ .

## For Example:

```

If transfer rate equals 110 bps,

```

$\overline{\text{TxC}} = 110 \text{ Hz} (1x)$

$\overline{\text{TxC}} = 1.76 \text{ KHz} (16x)$

$\overline{\text{TxC}} = 7.04 \text{ KHz} (64x)$

The falling edge of TxC shifts the serial data out of the 8251A.

### • TxD (Output)

This line is used to transmit the serial data. Serial output data on TxD is changed from paralled data to serial data in accordance with the format specified by the Control Words.

TxD line will be held in the marking state ('1' level) immediately on one of the following.s

· Master Reset

- Tx Disable (TxEN = 0)

- CTS signal is high  $(\overline{CTS} = 1)$

- TxEMPTY signal is high (TxEMPTY = 1)

### TxRDY (Output)

This output informs the MPU that the transmitter is ready to accept a Data Character. The TxRDY output pin can be used as an interrupt to the system, since it is masked by Tx Disable (TxEN=0), or, for polled Operation, the MPU can check TxRDY using a Status Read Operation. TxRDY is automatically reset by the trailing edge of  $\overline{WR}$  when a Data Character is loaded from the MPU. The Tx RDY pin output status (Tx RDY (pin)) is different from the TxRDY status bit status (TxRDY (status bit)) as follows.

```

TXRDY (status bit) = (Transmit Data Buffer Empty)

```

$TxRDY (pin) = (Transmit Data Buffer Empty) \cdot (CTS = 0) \cdot (TxEN = 1)$

#### TxEMPTY (Output)

The TxEMPTY output will go "high" when the 8251A has no characters to send. It resets upon receiving as character from the MPU if the transmitter is enabled.

In Synchronous Mode, a "high" level signal on this output indicates that a Character has not been loaded and the SYNC Character or Characters are about to be or are being transmitted automatically as "fillers". Tx EMPTY does not go "low" when the SYNC characters are being shifted out.

#### 4.4 RECEIVE CONTROL SIGNLAS

## • $\overline{RxC}$ (Input)

The Receiver Clock controls the rate at which the character is to be received. In Synchronous Mode, the Transfer Rate (1x) is equal to the actual frequency of  $\overline{RxC}$ . In Asynchronous Mode, the Transfer Rate is a fraction of the actual  $\overline{RxC}$  frequency. A portion of the Mode Instruciton selects this factor; 1,  $^1/_{16}$  or  $^1/_{64}$  the  $\overline{RxC}$ .

### For Example:

if Transfer Rate equals 2400 bps,

$\overline{RxC} = 2.4 \text{ KHz} (1x)$

$\overline{\text{RxC}} = 38.4 \text{ KHz} (16x)$

$\overline{\text{RxC}} = 153.6 \text{ KHz} (64x)$

Data is sampled into the 8251A on the rising edge of  $\overline{RxC}$ .

## • RxD (Input)

This line is used to receive the serial data. Serial input data on this line is changed to parallel data in accordance with the format specified by the Control Words, and then transferred to the Receive Data Buffer.

## • RxRDY (Output)

This output indicates that the 8251A contains a Data Character that is ready to be input to the MPU. RxRDY can be connected to the interrupt structure of the MPU, or, for Polled Operation, the MPU can check the condition of RxRDY using a Status Ready Operation.

Rx Enable off both masks and holds RxRDY in the Reset Condition.

## • SYNDET/BD (Input/Output)

This pin is used for SYNDET in Synchronous Mode and may be used as eigher input or ourput, programmable through the Contorl Word. It is reset to output mode "low" upon RESET. When used as an Output (Internal Sync Mode), the SYNDET pin will go "high" to indicate that the 8251A is programmed to use SYNC Character in the Receive Mode. If the 8251A is programmed to use Double Sync Characters then SYNDET will go "high" in the middle of the last bit of the second SYNC Character. SYNDET is automatically reset upon a Status Read Operation. When used as an Input (External Sync Mode), a positive going signal will cause the 8251A to start assembling Data Characters on the rising edge of the next  $\overline{\text{RxC}}$ .

In Asynchronous Mode this pin is used for BD. This output will go "high" whenever the receiver remains "low" through two consecutive Stop Bit Sequences (including the Start Bits, Data Bits, and Parity Bits). Break Detect may also be read as a Status Bit. It is reset only upon a Master Chip Reset or Rx Data returning to a "one" state. But, if the Rx data returns to a "one" State during the last bit of the next character after the Break, Break detect does not always reset.

#### 4.5 POWER SUPPLY

- V<sub>CC</sub> (Power)+5 Volt supply

- GND (Power) 0 Volt supply

# 5. ELECTRICAL CHARACTERISTICS

## 5.1 MAXIMUM RATINGS

| SYMBOL              | ITEM                                       | RATING          |

|---------------------|--------------------------------------------|-----------------|

| V <sub>CC</sub>     | Power Supply Voltage (with respect to GND) | - 0.5V to 7.0V  |

| V <sub>IN</sub>     | Input Voltage (with respect to GND)        | -0.5V to 7.0V   |

| V <sub>OUT</sub>    | Output Voltage (with respect to GND)       | - 0.5V to 7.0V  |

| PD                  | Power Dissipation (Ta = 70°C)              | 1W              |

| T <sub>solder</sub> | Soldering Temperature (10 sec)             | 260°C           |

| T <sub>stg.</sub>   | Storage Temperature                        | - 55°C to 150°C |

| T <sub>opr.</sub>   | Operating Temperature                      | 0°C to 70°C     |

050489

## 5.2 D.C. CHARACTERISTICS

$T_{opr} = 0$ °C to 70°C,  $V_{CC} = 5V \pm 5\%$ , GND = 0V, Unless otherwise noted.

|                  | T                    |                                        |      |      |      |      |  |

|------------------|----------------------|----------------------------------------|------|------|------|------|--|

| SYMBOL           | PARAMETER            | TEST CONDITIONS                        | MIN. | TYP. | MAX. | UNIT |  |

| V <sub>IL</sub>  | Input Low Voltage    |                                        | -0.5 | _    | 0.8  | V    |  |

| V <sub>IH</sub>  | Input High Voltage   |                                        | 2.2  | _    | Vcc  | V    |  |

| V <sub>OL</sub>  | Output Low Voltage   | I <sub>OL</sub> = 2.2mA                | _    | _    | 0.45 | V    |  |

| V <sub>OH</sub>  | Output High Voltage  | $I_{OH} = -400 \mu A$                  | 2.4  | _    | -    | V    |  |

| l <sub>OFL</sub> | Output Leak Current  | $0.45V \le V_{OUT} \le V_{CC}$         | _    | _    | ± 10 | μA   |  |

| l <sub>IL</sub>  | Input Leak Current   | 0.45V≦V <sub>IN</sub> ≦V <sub>CC</sub> | _    |      | ± 10 | μA   |  |

| lcc              | Power Supply Current | All Outputs = "High"                   | _    | _    | 100  | mA   |  |

050489

## 5.3 A.C CHARACTERISTICS

$T_{opr} = 0$ °C to 70°C,  $V_{CC} = 5V \pm 5\%$ , GND = 0V, Unless otherwise noted.

## 5.3.1 Bus Read Cycle Timing Note 1)

| SYMBOL          | PARAMETER                                                           | TEST CONDITIONS                | MIN. | TYP. | MAX. | UNIT |

|-----------------|---------------------------------------------------------------------|--------------------------------|------|------|------|------|

| tar             | CS, C/D Set-up Time for RD                                          |                                | 50   | _    | _    | ns   |

| t <sub>RA</sub> | $\overline{CS}$ , C/ $\overline{D}$ Hold Time for $\overline{RD}$   |                                | 50   | _    | _    | ns   |

| t <sub>RR</sub> | RD Pulse Width                                                      |                                | 250  |      | -    | ns   |

| t <sub>RD</sub> | Data Delay Time for RD Note 2)                                      | C <sub>L</sub> = 150pF Note 3) | _    | _    | 250  | ns   |

| t <sub>DF</sub> | $\overline{CS}$ , C/ $\overline{D}$ Set-up Time for $\overline{RD}$ |                                | 10   | _    | 100  | ns   |

## 5.3.2 Bus Write Cycle Timing Note 1)

| SYMBOL          | PARAMETER                    | TEST CONDITIONS | MIN. | TYP. | MAX. | UNIT             |

|-----------------|------------------------------|-----------------|------|------|------|------------------|

| t <sub>AW</sub> | CS, C/D Set-up Time for WR   |                 | 50   | -    | -    | ns               |

| t <sub>WA</sub> | CS, C/D Hold Time for WR     |                 | 50   | -    | -    | ns               |

| t <sub>WW</sub> | WR Pulse Width               |                 | 250  | -    | _    | ns               |

| t <sub>DW</sub> | Data Set Up Time for WR      |                 | 150  | -    | _    | ns               |

| t <sub>WD</sub> | Data Hold Time for WR        |                 | 50   | -    | _    | ns               |

| t <sub>RV</sub> | Recovery Time between WRITES | Note 4)         | 6    | _    | _    | t <sub>cyc</sub> |

**TOSHIBA**

## 5.3.3 Other Timing

| SYMBOL                          | PARA                                                            | METER              | MIN. | TYP. | MAX.                  | UNIT             | ]      |

|---------------------------------|-----------------------------------------------------------------|--------------------|------|------|-----------------------|------------------|--------|

| t <sub>cyc</sub>                | Clock PeriodNote 5                                              | 5), 6)             | 320  | _    | 1350                  | ns               | 1      |

| t <sub>H</sub>                  | Clock High Level W                                              | /idth              | 140  | -    | t <sub>cyc</sub> - 90 | ns               | 1      |

| tL                              | Clock Low Level Wi                                              | idth               | 90   | _    | -                     | ns               |        |

| t <sub>R</sub> , t <sub>F</sub> | Clock Rise and Fall                                             | Time               | _    | _    | 20                    | ns               |        |

| t <sub>DTx</sub>                | TxD Delay Time fro                                              | m Falling Edge of  | -    | -    | 1                     | μs               |        |

|                                 |                                                                 | 1x, 64x Baud Rate  | DC   | _    | 64                    |                  | 1      |

| $f_{Tx}$                        | Transmitter Input                                               | 16x Baud Rate      | DC   | _    | 310                   | kHz              |        |

|                                 | Clock Frequency                                                 | 64x Baud Rate      | DC   | -    | 615                   |                  |        |

|                                 | Transmitter Input                                               | 1x Baud Rate       | 12   | _    |                       |                  | 1      |

| t <sub>TPH</sub>                | Clock High Level<br>Width                                       | 16, 64x Baud Rate  | 1    | -    | _                     | t <sub>cyc</sub> |        |

|                                 | Transmitter Input                                               | 1x Baud Rate       | 15   | _    | _                     |                  | 1      |

| t <sub>TPL</sub>                | Clock Low Level<br>Width                                        | 64x Baud Rate      | 3    | _    | _                     | t <sub>cyc</sub> |        |

|                                 |                                                                 | 1x Baud Rate       | DC   | _    | 64                    |                  | 1      |

| $f_{Rx}$                        | Transmitter Input                                               | 16, 64x Baud Rate  | DC   | _    | 310                   | kHz              |        |

|                                 | Clock Frequency                                                 | 64x Baud Rate      | DC   | _    | 615                   |                  |        |

| t <sub>RPH</sub>                | Transmitter Input                                               | 1x Baud Rate       | 12   | _    | _                     | +                | 1      |

| יתרח                            | Clock High Level<br>Width                                       | 64x Baud Rate      | 1    | _    |                       | t <sub>cyc</sub> |        |

| tRPL                            | Transmitter Input                                               | 1x Baud Rate       | 15   | _    | _                     | _                | 1      |

| -1(1 L                          | Clock Low Level<br>Width                                        | 64x Baud Rate      | 3    | _    | _                     | t <sub>cyc</sub> |        |

| t <sub>TxRDY</sub>              | TxRDY Pin Delay Tir                                             | ne from Center of  | -    | -    | 8                     | t <sub>cyc</sub> | Note 7 |

| RxRDY CLEAR                     | TxRDY Clear Delay                                               | Time from Trailing | _    |      | 6                     | t <sub>cyc</sub> | Note 7 |

| t <sub>RxRDY</sub>              | RxRDY Pin Delay Tin                                             | me from Center of  | _    | -    | 24                    | t <sub>cyc</sub> | Note 7 |

| R×RDY CLEAR                     | RxRDY Clear Delay                                               | Time from Leading  | _    |      | 6                     | t <sub>cyc</sub> | Note 7 |

| tįs                             | Internal SYNDET De<br>Rising Edge of RxC                        | elaya Time from    | -    |      | 24                    | t <sub>cyc</sub> | Note 7 |

| t <sub>ES</sub>                 | External SYNDET Se<br>Falling Edge of RxC                       | · ·                | 16   | -    | _                     | t <sub>cyc</sub> | Note 7 |

| t <sub>TxEMPTY</sub>            | TxEMPTY Delay Tim<br>Last Bit                                   | e from Center of   | 20   | _    | _                     | t <sub>cyc</sub> | Note 7 |

| t <sub>WC</sub>                 | Control Delay Time of $\overline{WR}$ (TxEN, $\overline{DTR}$ , |                    | 8    | -    | _                     | t <sub>cyc</sub> | Note 7 |

| t <sub>CR</sub>                 | DSR, CTS Set-Up Tir                                             | ne for RD          | 20   | _    | _                     | t <sub>cyc</sub> | Note 7 |

MPU85-69

#### Note

1) AC Test Conditions: Output measuring Point  $V_{OH}$  = 2.0V,  $V_{OL}$  = 0.8V Input supply level  $V_{IH}$  = 2.4V,  $V_{IL}$  = 0.45V

- 2) Assumes that Address is valid before the falling edge of RD.

- 3) C<sub>L</sub> means load capacitance.

- 4) This recovery time is defined only for Mode Intialization.

Write Data is allowed only when TxRDY=1. Recovery Time between Writes for Asynchronous Mode is 8 tcy and for Synchronous Mode is 16 tcy.

- 5) The TxC and RxC frequencies have the following limitations with respect to CLK:

For 1x Transfer Rate,  $f_{Tx}$  or  $f_{Rx} \le 1/(30 tcy)$

For 16x and 64x Transfer Rate,  $f_{Tx}$  or  $f_{Rx} \le 1/(4.5 \text{tcy})$

- 6) Minimum Reset Pulse Width is 6 tcy. System Clock must be running during Reset.

- 7) Status up data can have a maximum delay of 28 clock periods from the event affecting the status.

## 6. TIMING WAVEFORMS

Figure 6.1 System Clock

Figure 6.2 Transmitter Clock and Data

Figure 6.3 Receiver Clock and Data

Figure 6.4 Write Data Cycle (MPU→8251A)

Figure 6.5 Read Data Cycle (8251A→MPU)

Figure 6.6 Write Contorl or Output Port Cycle (MPU→82251A)

Figure 6.7 Read Control or Input Port Cycle (8251A→MPU)

TOSHIBA TMP8251A

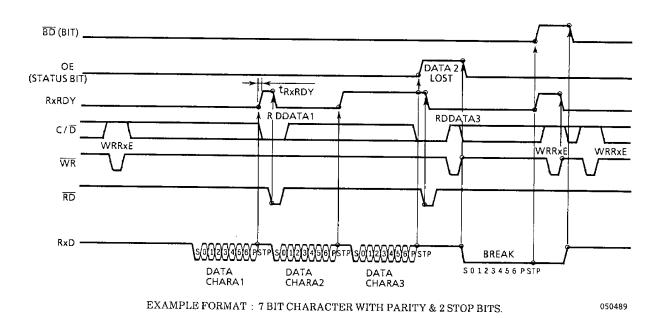

EXAMPLE FORMAT: 5 BIT CHARACTER WITH PARITY 2 SYNC CHARACTERS.

Figure 6.8 Transmitter Control and Flag Timing (SYNC Mode)

EXAMPLE FORMAT: 5 BIT CHARACTER WITH PARITY 2 SYNC CHARACTERS.

Figure 6.9 Receiver Controland Flag Timing (SYNC Mode)

EXAMPLE FORMAT: 7 BIT CHARACTER & 2 STOP BITS.

050489

050489

Note:  $TxRDY(PIN) - (Transmit Data Buffer is empty) \cdot (TxEN = 1) \cdot (CTS - 0)$

TxRDY (STATUS BIT) = (Transmit Data Buffer is empty)

Figure 6.10 Transmitter Control and Flag Timing (SYNC Mode)

Figure 6.11 Receiver Control and Flag Timing (ASYNC Mode)

**TOSHIBA**

# OUTLINE DRAWING (Dual Inline Package)

DIP28-P-600

270289

Note: Lead pitch is 2.54m and to lerance is  $\pm 25mm$  against theoretical center of each lead that is obtained on the basis of No.1 and No.28 leads.