# Ultra-Low Iq Automotive System Power Supply IC Power Saving Triple-Output Linear Regulator

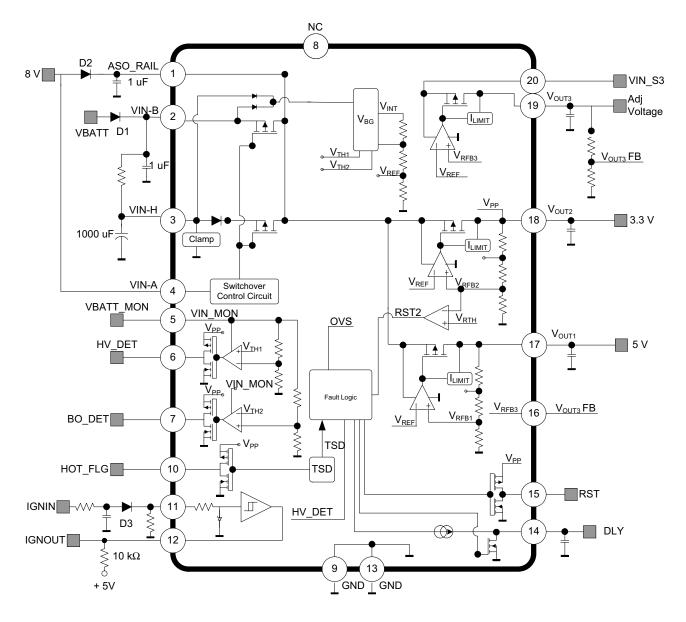

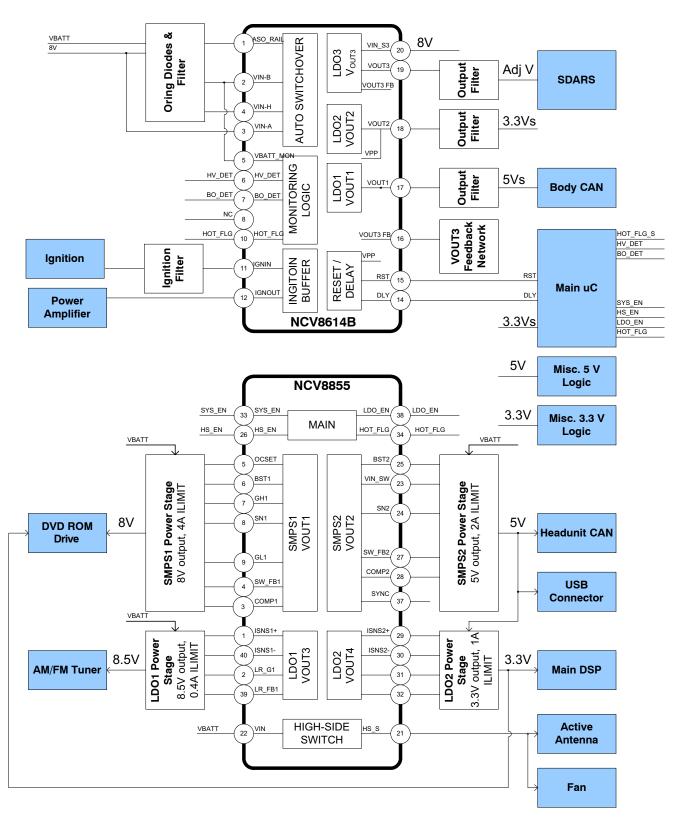

The NCV8614B is a multiple output linear regulator IC's with an Automatic Switchover (ASO) input voltage selector. The ASO circuit selects between three different input voltage sources to reduce power dissipation and to maintain the output voltage level across varying battery line voltages associated with an automotive environment.

The NCV8614B is specifically designed to address automotive radio systems and instrument cluster power supply requirements. The NCV8614B can be used in combination with the 4–Output Controller/Regulator IC, NCV885x, to form a complete automotive radio or instrument cluster power solution. The NCV8614B is intended to supply power to various "always on" loads such as the CAN transceivers and microcontrollers (core, memory and IO). The NCV8614B has three output voltages, a reset / delay circuit, and a host of control features suitable for the automotive radio and instrument cluster systems.

#### Features

- Operating Range 7.0 V to 18.0 V (45 V Load Dump Tolerant)

- Output Voltage Tolerance, All Rails,  $\pm 2\%$

- < 50 µA Quiescent Current

- Independent Input for LDO3 Linear Regulator

- High Voltage Ignition Buffer

- Automatic Switchover Input Voltage Selector

- Independent Input Voltage Monitor with a High Input Voltage and Low Input Voltage (Brown-out) Indicators

- Thermal Warning Indicator with Thermal Shutdown

- Single Reset with Externally Adjustable Delay for the 3.3 V Rail

- Push-Pull Outputs for Logic Level Control Signals

- All Ceramic Solution for Reduced Leakage Current at the Output

- NCV Prefix for Automotive and Other Applications Requiring Site and Control Changes

- This is a Pb–Free Device

### Applications

- Automotive Radio

- Instrument Cluster

### **ON Semiconductor®**

http://onsemi.com

#### **ORDERING INFORMATION**

| Device        | Package            | Shipping <sup>†</sup> |

|---------------|--------------------|-----------------------|

| NCV8614BMNR2G | DFN20<br>(Pb-Free) | 2500 / Tape & Reel    |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

| Components | Value        | Manufacturer     |

|------------|--------------|------------------|

| D1         | MBRS2H100T3G | ON Semiconductor |

| D2         | MBR0502T1    | ON Semiconductor |

| D3         | MMDL914T1    | ON Semiconductor |

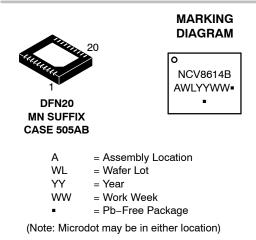

| Figure 1. | Typical | <b>Circuit with</b> | the Internal | Schematic |

|-----------|---------|---------------------|--------------|-----------|

|-----------|---------|---------------------|--------------|-----------|

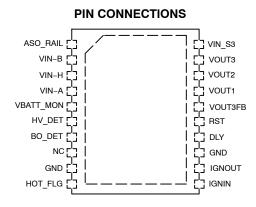

### **PIN FUNCTION DESCRIPTIONS**

| Pin No. | Symbol               | Description                                                                                                                                                                                                                                                                                                                                                                              |

|---------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | ASO_RAIL             | Output/Input of the automatic switchover (ASO) circuitry. Place a 1 uF ceramic capacitor on this pin to provide local bypassing to the LDO linear regulator pass devices.                                                                                                                                                                                                                |

| 2       | VIN-B                | Primary power supply input. Connect battery to this pin through a blocking diode.                                                                                                                                                                                                                                                                                                        |

| 3       | VIN-H                | Holdup power supply rail. Connect a storage capacitor to this pin to provide a temporary backup rail during loss of battery supply. A bleed resistor (typically 1 k $\Omega$ ) is needed from VIN–B to this pin in order to trickle charge this capacitor.                                                                                                                               |

| 4       | VIN-A                | Voltage monitor which determines whether the 8 V supply is able to power the outputs. If the 8 V supply is present, the FET's connected to VIN–B and VIN–H will be turned off, and the 8 V supply will be providing power to the outputs. If the 8 V supply is not present, the FET's on VIN–B and VIN–H will be left on, and the greater of those voltages will be driving the outputs. |

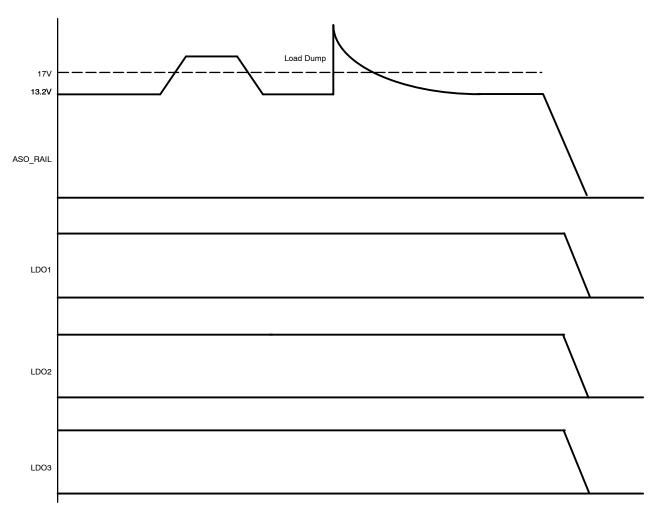

| 5       | VBATT_MON            | VBATT monitor pin. To operate overvoltage shutdown, HV_DET and BO_DET, connect this pin to ASO_RAIL or battery. To eliminate overvoltage shutdown, HV_DET and BO_DET, tie this pin to ground.                                                                                                                                                                                            |

| 6       | HV_DET               | High-voltage detect output. When VBATT_MON surpasses 17 V, this pin will be driven to ground. During normal operation, this pin is held at $V_{PP}$ .                                                                                                                                                                                                                                    |

| 7       | BO_DET               | Brown out indicator output. When VBATT_MON and VIN-A falls below 7.5 V, this pin will be driven to ground. During normal operation, this pin is held at VPP.                                                                                                                                                                                                                             |

| 8       | NC                   | No Connect                                                                                                                                                                                                                                                                                                                                                                               |

| 9       | GND                  | Ground. Reference point for internal signals. Internally connected to pin 13. Ground is <i>not</i> connected to the exposed pad of the DFN20 package.                                                                                                                                                                                                                                    |

| 10      | HOT_FLG              | Thermal warning indicator. This pin provides an early warning signal of an impending thermal shutdown.                                                                                                                                                                                                                                                                                   |

| 11      | IGNIN                | Ignition buffer input                                                                                                                                                                                                                                                                                                                                                                    |

| 12      | IGOUT                | Ignition buffer logic output                                                                                                                                                                                                                                                                                                                                                             |

| 13      | GND                  | Ground. Reference point for internal signals. Internally connected to pin 9. Ground is <i>not</i> connected to the exposed pad of the DFN20 package.                                                                                                                                                                                                                                     |

| 14      | DLY                  | Delay pin. Connect a capacitor to this pin to set the delay time.                                                                                                                                                                                                                                                                                                                        |

| 15      | RST                  | Reset pin. Monitors V <sub>OUT2.</sub>                                                                                                                                                                                                                                                                                                                                                   |

| 16      | V <sub>OUT3</sub> FB | Voltage Adjust Input; use an external voltage divider to set the output voltage                                                                                                                                                                                                                                                                                                          |

| 17      | V <sub>OUT1</sub>    | 5 V output. Voltage is internally set.                                                                                                                                                                                                                                                                                                                                                   |

| 18      | V <sub>OUT2</sub>    | 3.3 V output. Voltage is internally set.                                                                                                                                                                                                                                                                                                                                                 |

| 19      | V <sub>OUT3</sub>    | Adjustable voltage output. This voltage is set through an external resistor divider.                                                                                                                                                                                                                                                                                                     |

| 20      | VIN_S3               | Supply rail for the standby linear regulator VOUT3. Tie this pin to ASO_RAIL or a separate supply rail.                                                                                                                                                                                                                                                                                  |

| EP      | -                    | Exposed Pad of DFN device. This pad serves as the main path for thermal spreading. The Exposed Pad is <b>not</b> connected to IC ground.                                                                                                                                                                                                                                                 |

#### MAXIMUM RATINGS (Voltages are with respects to GND unless noted otherwise)

| Rating             | Symbol                                                                                             | Max | Min  | Unit |

|--------------------|----------------------------------------------------------------------------------------------------|-----|------|------|

| Maximum DC Voltage | VIN-B, VIN-A, ASO_RAIL, VBATT_MON, VIN_S3, EN, IGNIN                                               | 40  | -0.3 | V    |

| Peak Transient     | VIN-B, VIN-A, ASO_RAIL, VBATT_MON, VIN_S3, EN, IGNIN                                               | 45  | -0.3 | V    |

| Maximum DC Voltage | VIN-H                                                                                              | 24  | -0.3 | V    |

| Maximum DC Voltage | IGNOUT, V <sub>PP</sub> , HV_DET, BO_DET, HOT_FLG, RST, DLY, V <sub>OUT1</sub> , V <sub>OUT2</sub> | 7   | -0.3 | V    |

| Maximum DC Voltage | V <sub>OUT3</sub>                                                                                  | 10  | -0.3 | V    |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

### THERMAL INFORMATION

| Rating                               | Symbol           | Min         | Unit |

|--------------------------------------|------------------|-------------|------|

| Thermal Characteristic (Note 1)      | $R_{	hetaJA}$    | 40          | °C/W |

| Operating Junction Temperature Range | TJ               | -40 to 150  | °C   |

| Maximum Storage Temperature Range    | T <sub>STG</sub> | –55 to +150 | °C   |

| Moisture Sensitivity Level           | MSL              | 1           |      |

1. Values based on measurement of NCV8614B assembled on 2-layer 1-oz Cu thickness PCB with Copper Area of more than 645 mm<sup>2</sup> with several thermal vias for improved thermal performance. Refer to CIRCUIT DESCRIPTION section for safe operating area.

### ATTRIBUTES

| Rating                                          | Symbol                   | Min | Unit |

|-------------------------------------------------|--------------------------|-----|------|

| ESD Capability, Human Body Model (Note 2)       | ESD <sub>HB</sub>        | 2   | kV   |

| ESD Capability, Machine Model (Note 2)          | ESD <sub>MM</sub>        | 200 | V    |

| ESD Capability, Charged Device Model (Note 2)   | ESD <sub>CDM</sub>       | 1   | kV   |

| IGNIN ESD Capability, Human Body Model (Note 2) | ESD <sub>HB</sub> IGNIN  | 3   | kV   |

| IGNIN ESD Capability, Machine Model (Note 2)    | ESD <sub>MM</sub> _IGNIN | 200 | V    |

| IGNIN ESD Capability (Note 3)                   | ESD_IGNIN                | 10  | kV   |

2. This device series incorporates ESD protection and is tested by the following methods: ESD Human Body Model (HBM) tested per AEC-Q100-002 (EIA/JESD22-A114)

ESD Machine Model (MM) tested per AEC-Q100-003 (EIA/JESD22-A115)

ESD Charged Device Model (CDM) tested per EIA/JES D22/C101, Field Induced Charge Model 3. Device tested with external 10 kΩ series resistance and 1 nF storage capacitor.

> http://onsemi.com 4

SUPPLY VOLTAGES AND SYSTEM SPECIFICATION ELECTRICAL CHARACTERISTICS (7 V < ASO\_RAIL < 18 V, VIN-H = VIN-B  $\geq$  ASO\_RAIL, V<sub>PP</sub> = 3.3 V, VIN\_S3 tied to ASO\_RAIL, VBATT\_MON = 0 V, IGNIN = 0 V, I<sub>SYS</sub> = 3 mA (Note 6)) Minimum/Maximum values are valid for the temperature range -40°C  $\leq$  T<sub>J</sub>  $\leq$  150°C unless noted otherwise. Min/Max values are guaranteed by test, design or statistical correlation.

| Parameter                                                | Symbol            | Conditions                                                                 | Min                        | Тур  | Max  | Unit |

|----------------------------------------------------------|-------------------|----------------------------------------------------------------------------|----------------------------|------|------|------|

| SUPPLY RAILS                                             |                   |                                                                            |                            |      |      |      |

| Quiescent Current (Notes 4 and 6)                        | iq                | $T_J$ = 25°C, $I_{SYS}$ = 70 $\mu$ A, VIN–A = VIN_S3 = 0 V, VIN–B = 13.2 V |                            | 34   | 50   | μΑ   |

| Minimum Operating Voltage<br>(VIN-H, VIN-B)              |                   |                                                                            | 4.5                        |      |      | V    |

| THERMAL MONITORING                                       |                   | •                                                                          |                            |      |      |      |

| Thermal Warning (HOT_FLG)<br>Temperature                 | T <sub>WARN</sub> |                                                                            | 140                        | 150  | 160  | °C   |

| T <sub>WARN</sub> Hysteresis                             |                   |                                                                            | 10                         |      | 20   | °C   |

| Thermal Shutdown                                         |                   |                                                                            | 160                        | 170  | 180  | °C   |

| Thermal Shutdown Hysteresis                              |                   |                                                                            | 10                         |      | 20   | °C   |

| Delta Junction Temperature<br>(TSD – T <sub>WARN</sub> ) |                   |                                                                            | 10                         | 20   | 30   | °C   |

| HOT_FLG Voltage Low                                      |                   | $T_J < T_{WARN}$ , 10 k $\Omega$ Pullup to 3.3 V                           |                            |      | 0.4  | V    |

| HOT_FLG Voltage High                                     |                   | $T_J > T_{WARN}$ , 10 k $\Omega$ Pulldown to GND                           | V <sub>OUT2</sub> -<br>0.5 |      |      | V    |

| AUTO SWITCHOVER                                          |                   |                                                                            |                            |      |      |      |

| VIN-A Quiescent Current                                  |                   |                                                                            |                            | 24   |      | μΑ   |

| VIN–A to VIN–B Risetime                                  |                   | $T_J$ = 25°C, C <sub>ASO_RAIL</sub> = 1 µF,<br>I <sub>SYS</sub> = 400 mA   |                            | 200  |      | μsec |

| VIN-B to VIN-A Falltime                                  |                   | $T_J$ = 25 °C, $C_{ASO\_RAIL}$ = 1 µF,<br>$I_{SYS}$ = 400 mA               |                            | 100  |      | μsec |

| VIN-A Operating Threshold                                |                   | VIN–A Rising                                                               | 7.2                        | 7.5  | 7.75 | V    |

| VIN-A Operating Hysteresis                               |                   | VIN-A Falling                                                              | 100                        | 175  | 250  | mV   |

| Max VIN-B to VASO_RAIL Voltage Drop                      |                   | I <sub>SYS</sub> = 400 mA, VIN–B = 7 V                                     |                            |      | 1.5  | V    |

| Max VIN-H to $V_{ASO_RAIL}$ Voltage Drop                 |                   | $I_{SYS}$ = 400 mA, VIN–H = 7.5 V                                          |                            |      | 2.0  | V    |

| RESET (RST Pin)                                          |                   |                                                                            |                            |      |      |      |

| RESET Threshold                                          |                   | % of V <sub>OUT2</sub>                                                     | 90                         | 93   | 96   | %    |

| Hysteresis                                               |                   | % of V <sub>OUT2</sub>                                                     |                            |      | 2.5  | %    |

| Reset Voltage High                                       |                   | 10 k $\Omega$ Pulldown to GND                                              | V <sub>OUT2</sub> -<br>0.5 |      |      | V    |

| Reset Voltage Low                                        |                   | 10 k $\Omega$ Pullup to 3.3 V                                              |                            |      | 0.4  | V    |

| DELAY (DLY Pin)                                          |                   |                                                                            |                            |      |      |      |

| Charge Current                                           |                   |                                                                            | 2.4                        | 5    | 7    | μA   |

| Delay Trip Point Voltage                                 |                   |                                                                            |                            | 2.0  |      | V    |

| IGNITION BUFFER                                          |                   |                                                                            |                            |      |      |      |

| Schmitt Trigger Rising Threshold                         |                   |                                                                            | 2.75                       | 3.25 | 3.75 | V    |

| Schmitt Trigger Falling Threshold                        |                   |                                                                            | 0.8                        | 1.0  | 1.2  | V    |

| IGNOUT Voltage Low                                       |                   | IGNIN = 5 V, 10 k $\Omega$ Pullup to 5 V                                   |                            |      | 0.4  | V    |

| IGNOUT Leakage Current                                   |                   | $T_{J} = 25^{\circ}C$ , IGNOUT = 5 V                                       |                            | 0.1  | 0.5  | μA   |

| VBATT MONITOR                                            |                   |                                                                            |                            |      |      |      |

| VBATT_MON Quiescent Current                              |                   | $T_J = 25^{\circ}C$ , VBATT_MON = 13.2 V                                   |                            | 3    | 5    | μA   |

SUPPLY VOLTAGES AND SYSTEM SPECIFICATION ELECTRICAL CHARACTERISTICS (7 V < ASO\_RAIL < 18 V, VIN-H = VIN-B  $\geq$  ASO\_RAIL, V<sub>PP</sub> = 3.3 V, VIN\_S3 tied to ASO\_RAIL, VBATT\_MON = 0 V, IGNIN = 0 V, I<sub>SYS</sub> = 3 mA (Note 6)) Minimum/Maximum values are valid for the temperature range  $-40^{\circ}C \leq T_J \leq 150^{\circ}C$  unless noted otherwise. Min/Max values are guaranteed by test, design or statistical correlation.

| Parameter                           | Symbol | Conditions                                             | Min                        | Тур  | Max  | Unit |

|-------------------------------------|--------|--------------------------------------------------------|----------------------------|------|------|------|

| VBATT MONITOR                       |        | ·                                                      |                            |      |      |      |

| VBATT_MON Minimum Operating Voltage |        | Threshold where BO_DET and HV_DET signals become valid | 1.0                        | 2.0  | 2.5  | V    |

| VBATT_MON Hysteresis                |        |                                                        |                            | 0.25 |      | V    |

| HV_DET Voltage High                 |        | 10 kΩ Pulldown to GND<br>VBATT_MON Tied to ASO_RAIL    | V <sub>OUT2</sub> -<br>0.5 |      |      | V    |

| HV_DET Voltage Low                  |        | 10 kΩ Pullup to 3.3 V<br>VBATT_MON Tied to ASO_RAIL    |                            |      | 0.4  | V    |

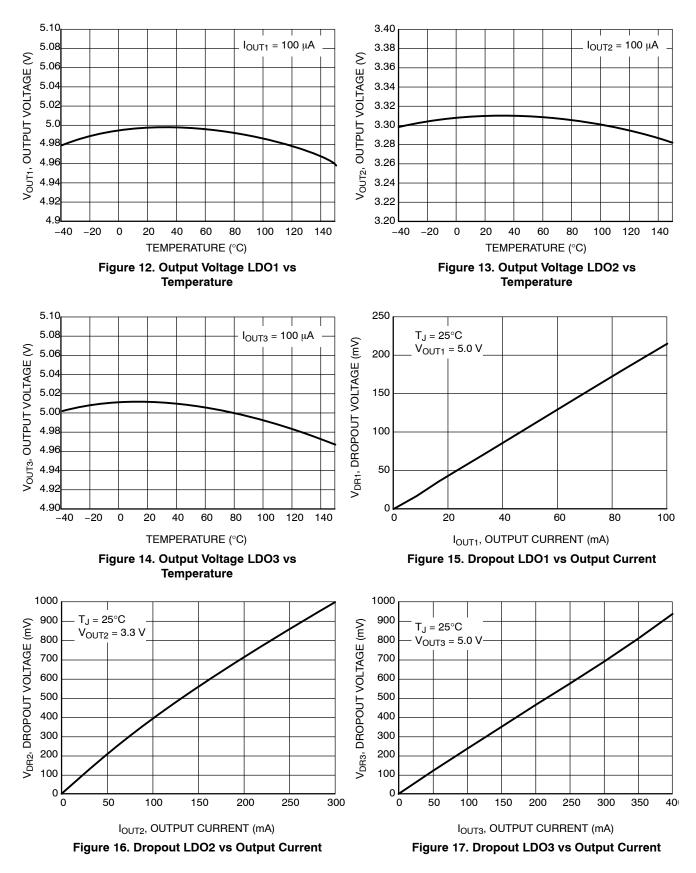

| HV_DET Threshold                    |        | VBATT_MON Rising                                       | 16.2                       |      | 17.8 | V    |

| HV_DET Hysteresis                   |        | VBATT_MON Falling                                      | 0.2                        | 0.35 | 0.5  | V    |

| BO_DET Voltage High                 |        | 10 kΩ Pulldown to GND<br>VBATT_MON Tied to ASO_RAIL    | V <sub>OUT2</sub> -<br>0.5 |      |      | V    |

| BO_DET Voltage Low                  |        | 10 kΩ Pullup to 3.3 V<br>VBATT_MON Tied to ASO_RAIL    |                            |      | 0.4  | V    |

| BO_DET Threshold                    |        | VBATT_MON Falling                                      | 7                          | 7.5  | 8    | V    |

| BO_DET Hysteresis                   |        | VBATT_MON Rising                                       | 0.2                        | 0.35 | 0.5  | V    |

i<sub>q</sub> is equal to I<sub>VIN-B</sub> + I<sub>VIN-H</sub> - I<sub>SYS</sub>

I<sub>SHDN</sub> is equal to I<sub>VIN-B</sub> + I<sub>VIN-H</sub>

I<sub>SYS</sub> is equal to I<sub>OUT1</sub> + I<sub>OUT2</sub> + I<sub>OUT3</sub>

| ELECTRICAL CHARACTERISTICS (7 V < ASO_RAIL < 18 V, VIN-H = VIN-B ≥ ASO_RAIL, V <sub>PP</sub> = 3.3 V, VIN_S3 tied to                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASO_RAIL, VBATT_MON = 0 V, IGNIN = 0 V, I <sub>SYS</sub> = $\overline{3}$ mA (Note 6)) Min/Max values are valid for the temperature range -40°C $\leq$ T <sub>J</sub> $\leq$ |

| 150 °C unless noted otherwise. Min/Max values are guaranteed by test, design or statistical correlation.                                                                     |

| Parameter                                            | Symbol            | Conditions                                                                                                                                                                                                                       | Min   | Тур | Мах   | Unit  |

|------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|-------|

| LOW DROP-OUT LINEAR REGULA                           | TOR 1 (LD         | 01) SPECIFICATION                                                                                                                                                                                                                | •     | -   | -     | -     |

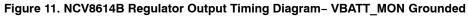

| Output Voltage                                       |                   | I <sub>OUT1</sub> = 0 mA to 100 mA,<br>7 V < ASO_RAIL < 18 V                                                                                                                                                                     | 4.9   | 5   | 5.1   | V     |

| Dropout (ASO_RAIL – V <sub>OUT1</sub> )              | V <sub>DR1</sub>  | I <sub>OUT1</sub> = 100 mA (Note 7)                                                                                                                                                                                              |       |     | 500   | mV    |

| Load Regulation                                      |                   | I <sub>OUT1</sub> = 0 mA to 100 mA, VIN_B = 13.2 V                                                                                                                                                                               |       | 0   | 75    | μV/mA |

| Line Regulation                                      |                   | I <sub>OUT1</sub> = 1 mA, 7 V < ASO_RAIL < 18 V                                                                                                                                                                                  |       | 0   | 2     | mV/V  |

| Output Current Limit                                 |                   |                                                                                                                                                                                                                                  | 200   |     |       | mA    |

| Output Load Capacitance Range                        | Co                | Output Capacitance for Stability                                                                                                                                                                                                 | 1.0   |     | 100   | μF    |

| Output Load Capacitance ESR Range<br>(Notes 8 and 9) | ESRCo             | Cap ESR for Stability                                                                                                                                                                                                            | 0.01  |     | 13    | Ω     |

| $\Delta V_{OUT1}$ (ASO Low to High Transient)        |                   | $\begin{array}{l} T_J=25~^\circ C \ , \ I_{OUT1}=100 \ \text{mA}, \ I_{SYS}=400 \\ \text{mA}, \ C_{ASO} \ \ _{RAIL}=1 \ \mu F, \ ESR_{Co}=0.01 \ \Omega, \\ Co=10 \ \mu F, \ VIN-A \ falling \end{array}$                        |       | 70  | 100   | ±mV   |

| $\Delta V_{OUT1}$ (ASO high to Low Transient)        |                   | $\begin{array}{l} T_J=25~^\circ C \ , \ I_{OUT1}=100 \ \text{mA}, \ I_{SYS}=400 \\ \text{mA}, \ C_{ASO} \ \ _{RAIL}=1 \ \mu\text{F}, \ ESR_{Co}=0.01 \ \Omega, \\ \text{Co}=10 \ \mu\text{F}, \ \text{VIN-A rising} \end{array}$ |       | 70  | 100   | ±mV   |

| Power Supply Ripple Rejection (Note 8)               | PSRR              | VIN_B = 13.2 V, 0.5 V <sub>PP</sub> , 100 Hz                                                                                                                                                                                     |       | 60  |       | dB    |

| Startup Overshoot                                    |                   | I <sub>OUT1</sub> = 0 mA to 100 mA                                                                                                                                                                                               |       |     | 3     | %     |

| LOW DROP-OUT LINEAR REGULA                           | TOR 2 (LD         | 02) SPECIFICATION                                                                                                                                                                                                                |       |     |       |       |

| Output Voltage                                       |                   | I <sub>OUT2</sub> = 0 mA to 300 mA,<br>7 V < ASO_RAIL < 18 V                                                                                                                                                                     | 3.234 | 3.3 | 3.366 | V     |

| Dropout (ASO_RAIL - V <sub>OUT2</sub> )              | V <sub>DR2</sub>  | I <sub>OUT2</sub> = 300 mA (Note 7)                                                                                                                                                                                              |       |     | 1.5   | V     |

| Load Regulation                                      |                   | I <sub>OUT2</sub> = 0 mA to 300 mA, VIN_B = 13.2 V                                                                                                                                                                               |       | 0   | 66    | μV/mA |

| Line Regulation                                      |                   | I <sub>OUT2</sub> = 1 mA,<br>7 V < ASO_RAIL < 18 V                                                                                                                                                                               |       | 0   | 1.2   | mV/V  |

| Output Current Limit                                 |                   |                                                                                                                                                                                                                                  | 400   |     |       | mA    |

| Output Load Capacitance Range                        | Co                | Output Capacitance for Stability                                                                                                                                                                                                 | 1.0   |     | 100   | μF    |

| Output Load Capacitance ESR Range<br>(Notes 8 and 9) | ESRCo             | Maximum Cap ESR for stability                                                                                                                                                                                                    | 0.01  |     | 10    | Ω     |

| $\Delta V_{OUT2}$ (ASO Low to High Transient)        |                   | $T_J$ = 25 $^{\circ}C$ , $I_{OUT2}$ = 300 mA, $I_{SYS}$ = 400 mA, $C_{ASO}$ $_{RAIL}$ = 1 $\mu F$ , $ESR_{Co}$ = 0.01 $\Omega$ , Co = 22 $\mu F$ , VIN–A falling                                                                 |       | 30  | 66    | ±mV   |

| $\Delta V_{OUT2}$ (ASO high to Low Transient)        |                   | $T_J$ = 25 $^{\circ}C$ , $I_{OUT2}$ = 300 mA, $I_{SYS}$ = 400 mA, $C_{ASO}$ $_{RAIL}$ = 1 $\mu\text{F},$ ESR $_{Co}$ = 0.01 $\Omega,$ Co = 22 $\mu\text{F},$ VIN–A rising                                                        |       | 30  | 66    | ±mV   |

| Power Supply Ripple Rejection (Note 8)               | PSRR              | VIN_B = 13.2 V, 0.5 V <sub>PP</sub> , 100 Hz                                                                                                                                                                                     | T     | 60  |       | dB    |

| Startup Overshoot                                    |                   | I <sub>OUT2</sub> = 0 mA to 300 mA                                                                                                                                                                                               |       |     | 3     | %     |

| LOW DROP-OUT LINEAR REGULA                           | TOR 3 (LD         | 03) SPECIFICATION                                                                                                                                                                                                                |       |     |       |       |

| Output Voltage                                       | V <sub>OUT3</sub> | $I_{OUT3} = 0$ mA to 400 mA,<br>V <sub>OUT3</sub> + V <sub>DR3</sub> $\leq$ VIN_S3 $\leq$ 18 V                                                                                                                                   | -2%   | -   | +2%   | V     |

|                                                      | -                 |                                                                                                                                                                                                                                  | 1     | 1   |       |       |

| Output voltage                        | VOUT3            | $V_{OUT3} = 0 \text{ mA to 400 mA,}$<br>$V_{OUT3} + V_{DR3} \le \text{VIN}S3 \le 18 \text{ V}$              | -2% | - | +2% | v     |

|---------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------|-----|---|-----|-------|

| Dropout (VIN_S3 – V <sub>OUT3</sub> ) | V <sub>DR3</sub> | I <sub>OUT3</sub> = 400 mA , V <sub>OUT3</sub> = 5 V<br>(Notes 7 and 10)                                    |     |   | 2.5 | V     |

| Output Current Limit                  |                  |                                                                                                             | 500 |   |     | mA    |

| Load Regulation                       |                  | I <sub>OUT3</sub> = 0 mA to 400 mA,<br>VIN_B = 13.2 V                                                       |     | 0 | 75  | μV/mA |

| Line Regulation                       |                  | $\begin{array}{l} I_{OUT3} = 1 \mbox{ mA}, \\ V_{REF} \leq \mbox{ VIN}\_S3  \leq  18 \mbox{ V} \end{array}$ |     | 0 | 654 | μV /V |

| ELECTRICAL CHARACTERISTICS (7 V < ASO_RAIL < 18 V, VIN-H = VIN-B ≥ ASO_RAIL, V <sub>PP</sub> = 3.3 V, VIN_S3 tied to                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASO_RAIL, VBATT_MON = 0 V, IGNIN = 0 V, I <sub>SYS</sub> = $\overline{3}$ mA (Note 6)) Min/Max values are valid for the temperature range -40°C $\leq$ T <sub>J</sub> $\leq$ |

| 150 °C unless noted otherwise. Min/Max values are guaranteed by test, design or statistical correlation.                                                                     |

| Parameter                                            | Symbol | Conditions                                                                                                                                                      | Min  | Тур | Max | Unit |  |

|------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|--|

| LOW DROP-OUT LINEAR REGULATOR 3 (LDO3) SPECIFICATION |        |                                                                                                                                                                 |      |     |     |      |  |

| Output Load Capacitance Range                        | Co     | Output Capacitance for Stability                                                                                                                                | 1.0  |     | 100 | μF   |  |

| Output Load Capacitance ESR Range<br>(Notes 8 and 9) | ESRCo  | Maximum Capacitance ESR for stability                                                                                                                           | 0.01 |     | 12  | Ω    |  |

| $\Delta V_{OUT3}$ (ASO Low to High Transient)        |        | $T_J$ = 25 $^\circ C$ , $I_{OUT3}$ = 400 mA, $I_{SYS}$ = 400 mA, $C_{ASO}$ $_{RAIL}$ = 1 $\mu F$ , $ESR_{Co}$ = 0.01 $\Omega$ , Co = 47 $\mu F$ , VIN–A falling |      | 15  | 36  | ±mV  |  |

| $\Delta V_{OUT3}$ (ASO high to Low Transient)        |        | $T_J$ = 25 $^\circ C$ , $I_{OUT3}$ = 400 mA, $I_{SYS}$ = 400 mA, $C_{ASO}$ $_{RAIL}$ = 1 $\mu F$ , $ESR_{Co}$ = 0.01 $\Omega$ , Co = 47 $\mu F$ , VIN–A rising  |      | 15  | 36  | ±mV  |  |

| Power Supply Ripple Rejection (Note 8)               | PSRR   | VIN_B = 13.2 V, 0.5 V <sub>PP</sub> , 100 Hz                                                                                                                    | 1    | 60  |     | dB   |  |

| Startup Overshoot                                    |        | I <sub>OUT3</sub> = 0 mA to 400 mA                                                                                                                              |      |     | 3   | %    |  |

7. Dropout voltage is measured when the output voltage has dropped 100 mV relative to the nominal value obtained with ASO\_RAIL = VIN\_S3 = 13.2 V.

Not tested in production. Limits are guaranteed by design.

Refer to CIRCUIT DESCRIPTION Section for Stability Consideration

10. For other voltage versions refer to Typical Performance Characteristics Section.

#### **ORDERING INFORMATION**

| Device        | Conditions                                        | Package                       | Shipping           |

|---------------|---------------------------------------------------|-------------------------------|--------------------|

| NCV8614BMNR2G | No Enable, LDO2 Reset monitor,<br>Adjustable LDO3 | 20 Lead DFN, 5x6<br>(Pb-Free) | 2500 / Tape & Reel |

Figure 2. Automotive Radio System Block Diagram Example NCV8614B with NCV8855

#### **CIRCUIT DESCRIPTION**

#### **Auto Switchover Circuitry**

The auto switchover circuit is designed to insure continuous operation of the device, automatically switching the input voltage from the ASO\_RAIL input, to the VIN–B input, to the VIN–H input depending on conditions. The primary input voltage pin is ASO\_RAIL, which is driven from the 8 V supply. When this voltage is present it will drive the output voltages. Regardless of whether the 8 V supply is available, the reference and core functions of the device will be driven by the higher of VIN–B and VIN–H. The switchover control circuitry will be powered solely by the 8 V supply, via VIN–A.

When the 8 V supply is not present, the gates of the 2 P-FET switches will be pulled to ground, turning the switches on. In this condition, the VIN-B and VIN-H voltages will be diode or'ed, with the higher voltage powering the chip. The VIN-H voltage will be one diode lower than the VIN-B voltage, thereby forcing the VIN-B voltage to be dominant supply.

In the event that both the 8 V supply and the VIN–B supply are not present, the VIN–H supply will be powering the device. The VIN–H supply is then fed from a recommended 1000  $\mu$ F cap. The duration of VIN–H supply is dependent on output current. It is intended as protection against temporary loss of battery conditions.

In the event of a double battery, or prolonged high voltage condition on the battery line, a bleed transistor has been included on the VIN–H line. With the large hold–up cap on VIN–H, the voltage on that pin has the potential to remain in an elevated position for an extended period of time. The main result of this condition would be an Overvoltage Shutdown of the device. In order to avoid this condition, a transistor that is connected to the Overvoltage Shutdown signal is tied to the VIN–H line. This transistor will become active in a high voltage event, allowing the hold–up cap to discharge the excess voltage in a timely manner.

In the Block Diagram, Figure 1,  $C_{ASO\_RAIL}$  is listed as a 1  $\mu$ F capacitor. It is required for proper operation of the device that  $C_{ASO\_RAIL}$  is no larger than 1  $\mu$ F.

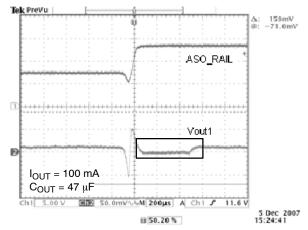

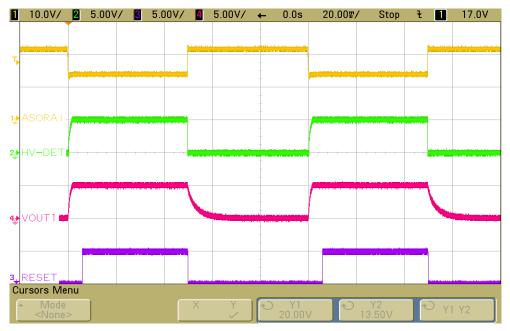

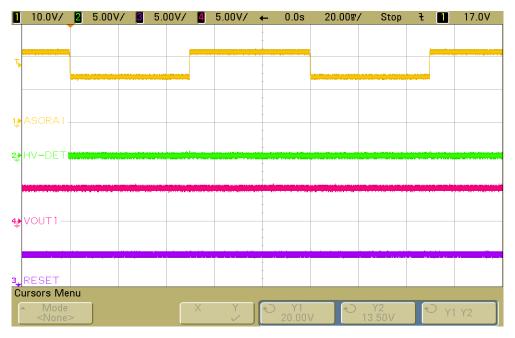

During a switchover event, a timer in the output stages prepares the regulator in anticipation of change in input voltage. The event results in a hitch in the output waveforms, as can be seen in Figure 3.

Figure 3. V<sub>OUTX</sub> Response to ASO Switchover Event

#### VIN-B/VIN-H Minimum Operating Voltage

The internal reference and core functions are powered by either the VIN–B or VIN–H supply. The higher of the two voltages will dominate and power the reference. This provides quick circuit response on start–up, as well as a stable reference voltage. Since the VIN–B voltage will come up much more quickly than the VIN–H voltage, initially, the VIN–B voltage will be running the reference. In the case of any transient drops on VIN–B, the VIN–H supply, with its large hold–up capacitor, will then be the dominant voltage, and will be powering the reference.

For proper operation of the device, VIN–B or VIN–H must be at least 4.5 V. Below that voltage the reference will not operate properly, leading to incorrect functioning by the device. VIN–B or VIN–H must be greater than 4.5 V regardless of the voltage on the VIN–A pin.

#### Internal Soft-Start

The NCV8614B is equipped with an internal soft–start function. This function is included to limit inrush currents and overshoot of output voltages. The soft–start function applies to all 3 regulators.

The soft-start function kicks in for start up, start up via enable, start up after thermal shutdown, and startup after an over voltage condition.

LDO3 is not subject to soft-start under all conditions. The LDO3 output is not affected by overvoltage shutdown, and

therefore is not effected by the soft-start function upon the device's return from an over voltage condition. Also, when VIN\_S3 is connected to an independent supply and the supply is made available after the soft-start function, LDO3 will not have an independent soft-start.

#### LDO1 Regulator

The LDO1 error amplifier compares the reference voltage to a sample of the output voltage (VOUT1) and drives the gate of an internal PFET. The reference is a bandgap design to give it a temperature–stable output.

#### LDO2 Regulator

The LDO2 error amplifier compares the reference voltage to a sample of the output voltage (VOUT2) and drives the gate of an internal PFET. The reference is a bandgap design to give it a temperature–stable output.

#### LDO3 Regulator

The LDO3 error amplifier compares the reference voltage to a sample of the output voltage (VOUT3) and drives the gate of an internal PFET. The reference is a bandgap design to give it a temperature–stable output

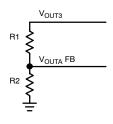

LDO3 is an adjustable voltage output. The adjustable voltage option requires an external resistor divider feedback network. LDO3 can be adjusted up to 10 V. The internal reference voltage is 0.996 V. To determine the proper feedback resistors, the following formula can be used:

$V_{OUT3} = V_{OUT3}FB [(R1+R2)/R2]$

Figure 4. Feedback Network

#### **Stability Considerations**

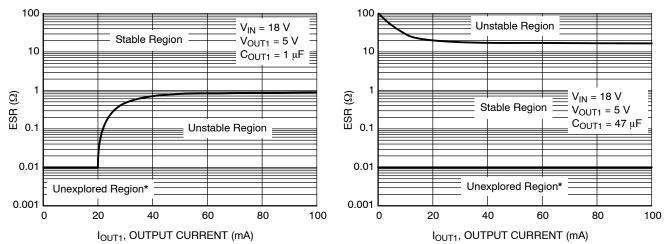

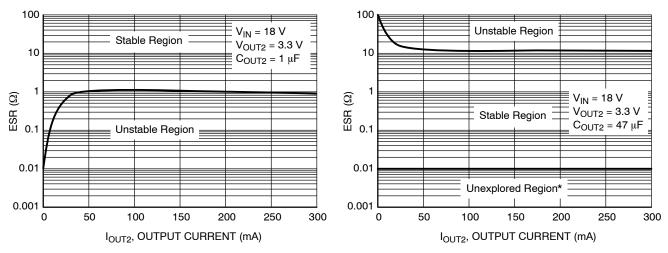

The output or compensation capacitors, COUTX help determine three main characteristics of a linear regulator: startup delay, load transient response and loop stability. The capacitor values and type should be based on cost, availability, size and temperature constraints. Tantalum, aluminum electrolytic, film, or ceramic capacitors are all acceptable solutions, however, attention must be paid to ESR constraints. The aluminum electrolytic capacitor is the least expensive solution, but, if the circuit operates at low temperatures ( $-25^{\circ}$ C to  $-40^{\circ}$ C), both the value and ESR of the capacitor will vary considerably. The capacitor manufacturer's data sheet usually provides this information. The value for each output capacitor C<sub>OUTX</sub> shown in Figures 22 – 27 should work for most applications; however, it is not necessarily the optimized solution. Stability is guaranteed at the following values:

$$\begin{array}{l} C_{OUT1} \geq 47 \ \mu\text{F}, \text{ESR} \leq 10 \ \Omega \\ C_{OUT2} \geq 47 \ \mu\text{F}, \text{ESR} \leq 10 \ \Omega \\ C_{OUT3} \geq 47 \ \mu\text{F}, \text{ESR} \leq 10 \ \Omega \end{array}$$

Actual limits are shown in graphs in the Typical Performance Characteristics section.

#### Thermal

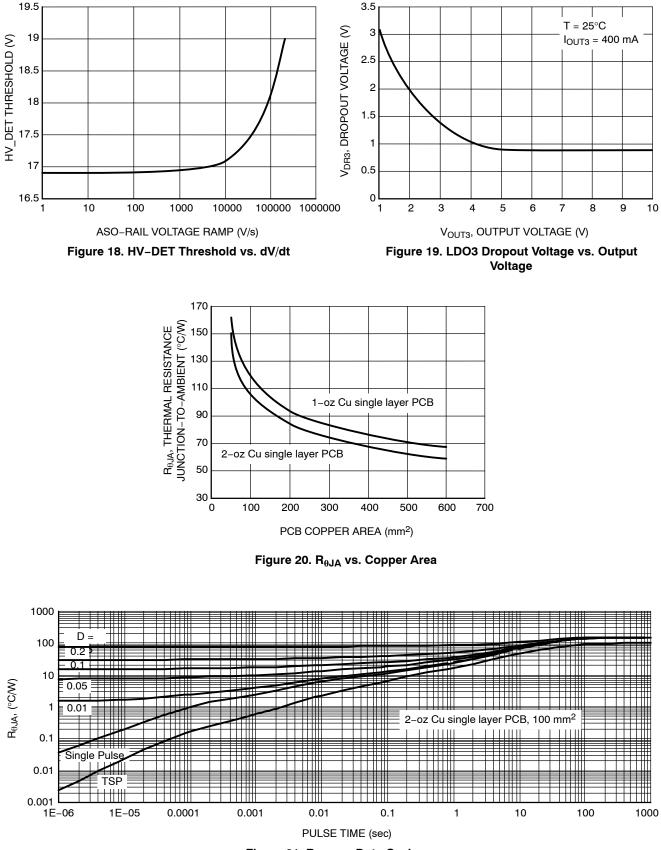

As power in the NCV8614B increases, it might become necessary to provide some thermal relief. The maximum power dissipation supported by the device is dependent upon board design and layout. Mounting pad configuration on the PCB, the board material, and the ambient temperature affect the rate of junction temperature rise for the part. When the NCV8614B has good thermal conductivity through the PCB, the junction temperature will be relatively low with high power applications.

The maximum dissipation the NCV8614B can handle is given by:

$P_{D(max)} = (T_{J(max)} - T_A)/R_{thJA}$

See Figure 20 for  $R_{thJA}$  versus PCB Area.

$R_{thJA}\xspace$  could be further decreased by using Multilayer PCB and/or if Air Flow is taken into account.

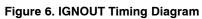

#### **IGNOUT Circuitry**

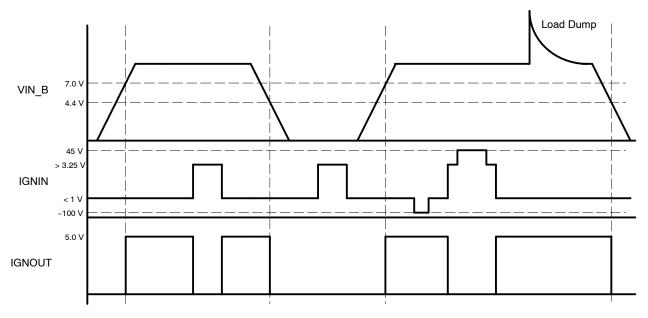

The IGNOUT pin is an open drain output Schmitt Trigger, externally pulled up to 3.3 V via a 10 k $\Omega$  resistor. The IGNOUT pin can be used to monitor the ignition signal of the vehicle, and send a signal to mute an audio amplifier during engine crank. The IGNIN pin is ESD protected, and can handle peak transients up to 45 V. An external diode is recommended to protect against negative voltage spikes.

The IGNOUT circuitry requires the device to be enabled for proper operation.

#### V<sub>PP</sub> Function

The reset and warning circuits utilize a push-pull output stage. The high signal is provided by  $V_{PP}$ ,  $V_{PP}$  is tied internally to LDO2. Under this setup, and any setup where LDO's 1–3 are tied to  $V_{PP}$ , loss of the  $V_{PP}$  signal can occur if the pull up voltage is reduced due to over current, thermal shutdown, or overvoltage conditions.

#### **Reset Outputs**

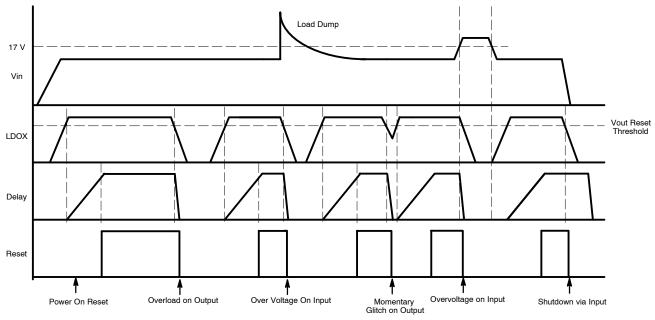

The Reset Output is used as the power on indicator to the Microcontroller. The NCV8614B Reset circuitry monitors the output on LDO2.

This signal indicates when the output voltage is suitable for reliable operation. It pulls low when the output is not considered to be suitable. The Reset circuitry utilizes a push pull output stage, with  $V_{PP}$  as the high signal. In the event of the part shutting down via Battery voltage or Enable, the Reset output will be pulled to ground.

The input and output conditions that control the Reset Output and the relative timing are illustrated in Figure 5, Reset Timing. Output voltage regulation must be maintained for the delay time before the reset output signals a valid condition. The delay for the reset output is defined as the amount of time it takes the timing capacitor on the delay pin to charge from a residual voltage of 0 V to the Delay timing threshold voltage VD of 2 V. The charging current for this is ID of 5  $\mu$ A. By using typical IC parameters with a 10 nF capacitor on the Delay Pin, the following time delay is derived:

$t_{RD} = C_D * V_{DU} / I_D$

$t_{RD} = 10 \text{ nF} * (2 \text{ V}) / (5 \mu \text{A}) = 4 \text{ ms}$

Other time delays can be obtained by changing the CD capacitor value. The Delay Time can be reduced by decreasing the capacitance of CD. Using the formula above, delay can be reduced as desired. Leaving the Delay Pin open is not desirable as it can result in unwanted signals being coupled onto the pin.

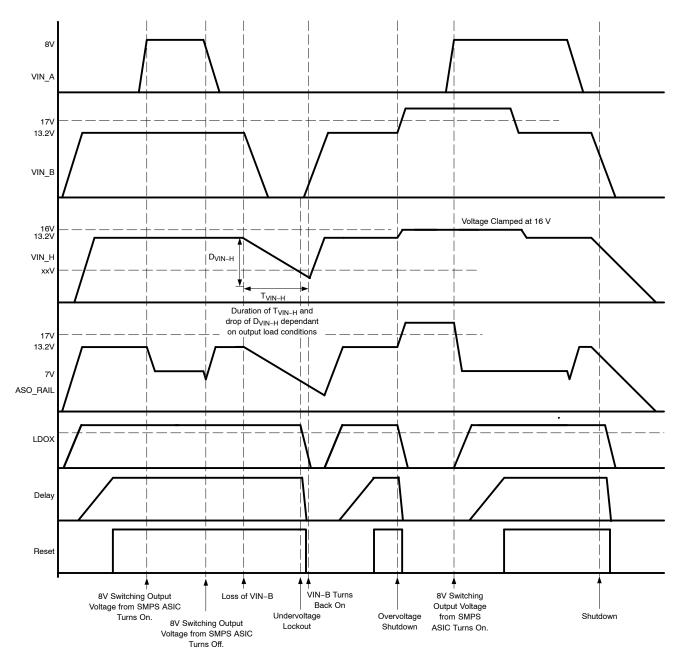

#### VBATT\_MON and Warning Flags

The NCV8614B is equipped with High Voltage Detection, Brown Out Detection, and High Temperature Detection circuitry. The Overvoltage Shutdown, High Voltage, and Brown Out Detection circuitry are all run off the VBATT\_MON input. If this functionality is not desired, grounding of the VBATT\_MON pin will turn off the functions.

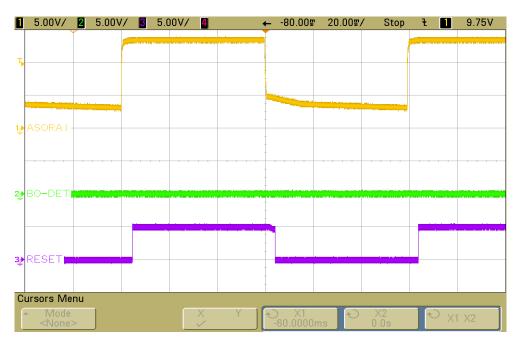

The HV\_DET and BO\_DET signals are in a high impedance state until the VBATT\_MON circuitry reaches it minimum operating voltage, typically 1.0 V to 2.5 V. At that point the BO\_DET signal will be held low, while the HV\_DET signal will go high. The BO\_DET signal will go high once the VBATT\_MON signal reaches the Brown Out Threshold, typically 7 V to 8 V. The BO\_DET signal will stay high until the VBATT\_MON voltage drops below the Brown Out Threshold. The HV\_DET signal will stay high until the VBATT\_MON voltage rises above the HV\_DET threshold, typically 16.2 V to 17.8 V. The HV\_DET signal will reassert high once the HV\_DET signal crosses the HV\_DET threshold going low.

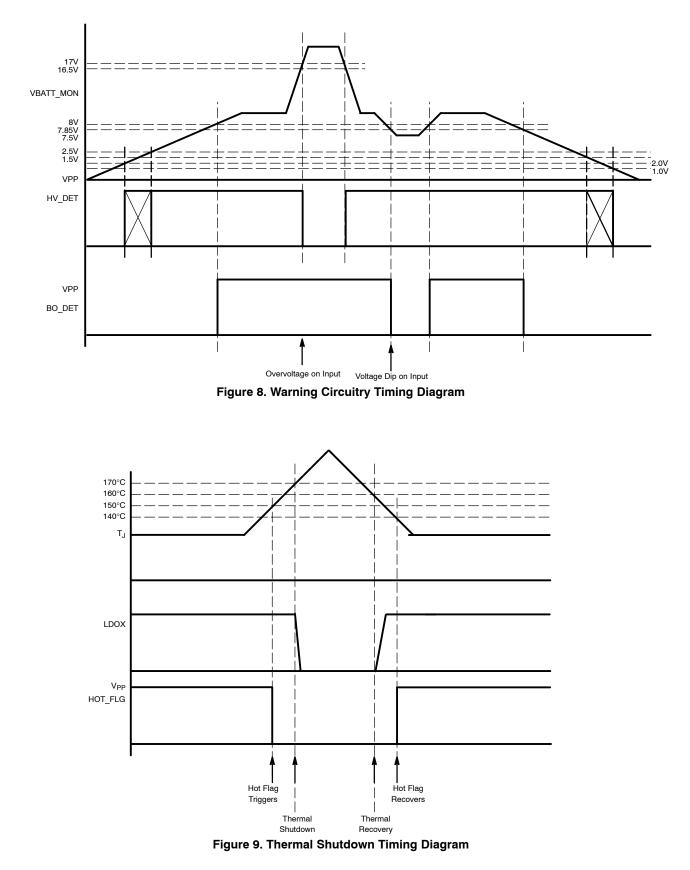

The NCV8614B is also equipped with a Hot Flag pin which indicates when the junction temperature is approaching thermal shutdown. The Hot Flag signal will remain high as long as the junction temperature is below the Hot flag threshold, typically 140°C to 160°C. This pin is intended as a warning that the junction temperature is approaching the Thermal Shutdown threshold, which is typically 160°C to 180°C. The Hot Flag signal will remain low until the junction temperature drops below the Hot Flag threshold.

The Hot\_Flag circuitry does not run off the VBATT\_MON Pin, and can not be disabled by grounding VBATT MON.

Each of the three warning circuits utilizes a push-pull output stage. The high signal is provided by  $V_{PP}$ .  $V_{PP}$  is internally tied to  $V_{OUT2}$ .

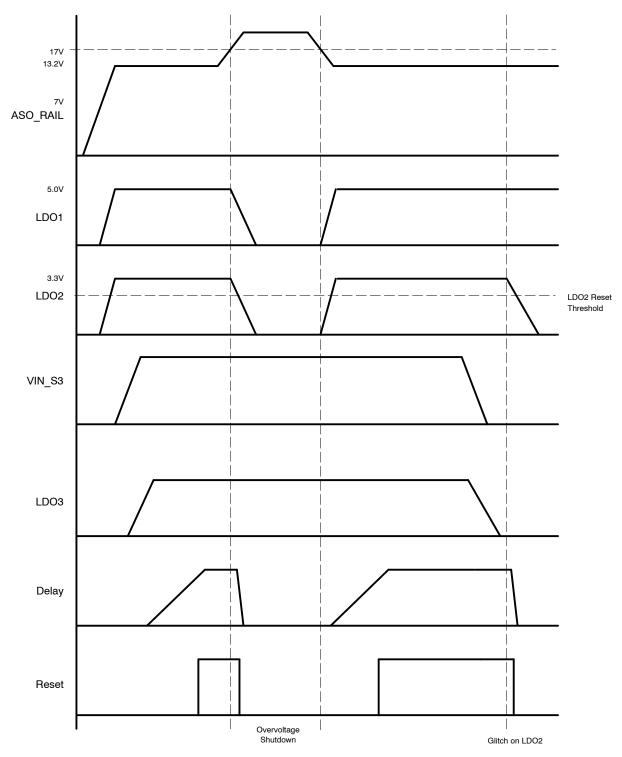

### **Overvoltage Shutdown**

The NCV8614B is equipped with overvoltage shutdown (OVS) functionality. The OVS is designed to turn on when the VBATT\_MON signal crosses 17 V. If the VBATT\_MON pin is tied to ground, the OVS functionality will be disabled.

When OVS is triggered, LDO1 and LDO2 will both be shut down. LDO3 is run off a separate input voltage line, VIN\_S3, and will not shutdown in this condition. Once the OVS condition has passed, LDO1 and LDO2 will both turn back on.

The VIN–H line is equipped with a bleed transistor to prevent a continued OVS condition on the chip once the high battery condition has subsided. This transistor is needed to discharge the high voltage from the VIN–H hold–up capacitor. This transistor will only turn on when an OVS is detected on–chip, and will turn off as soon as the OVS condition is no longer detected by the chip.

Figure 7. Auto Switchover Circuit Timing Diagram VBATTMON Connected to ASO\_RAIL

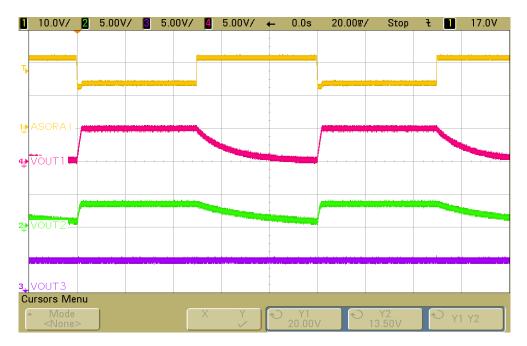

Figure 10. NCV8614B Regulator Output Timing Diagram- VIN\_S3 Tied to ASO\_RAIL

Figure 21.  $R_{\theta JA}$  vs. Duty Cycle

Figure 22. C<sub>OUT1</sub> ESR Stability Region – 1 µF

# Figure 23. C<sub>OUT1</sub> ESR Stability Region – 47 μF

\*The min specified ESR is based on Murata's capacitor GRM31CR60J476ME19 used in measurement. The true min ESR limit might be lower than shown.

Figure 25. C<sub>OUT2</sub> ESR Stability Region – 47 µF

Figure 24. C<sub>OUT2</sub> ESR Stability Region – 1 µF \*The min specified ESR is based on Murata's capacitor GRM31CR60J476ME19 used in measurement. The true min ESR limit might be lower than shown.

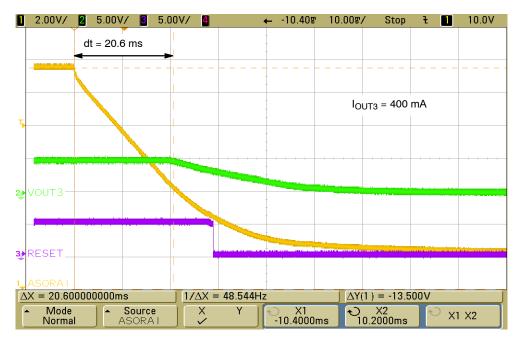

Figure 28. Output Response of LDO3 to Loss of Vin-B

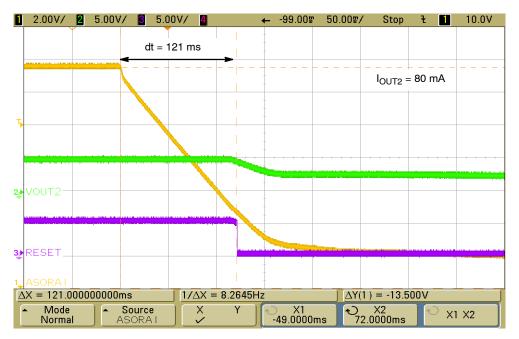

Figure 29. Output Response of LDO2 to Loss of Vin-B

Figure 30. HV-DET Response to High Voltage - VBAT-MON tied to ASO-RAIL

Figure 31. HV-DET Response to High Voltage – VBAT-MON Left Open

Figure 32. BO-DET Response to LOW Voltage - VBAT-MON tied to ASO-RAIL

Figure 33. BO-DET Response to LOW Voltage – VBAT-MON Left Open

Figure 34. Output Response to OVS - VBAT-MON tied to ASO-RAIL

Figure 35. Output Response to OVS – VBAT–MON Left Open

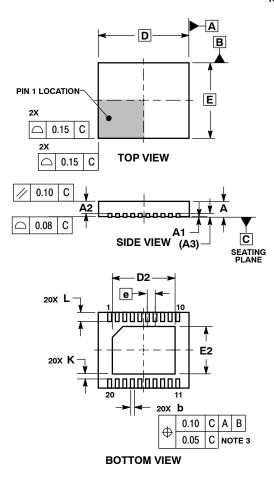

#### PACKAGE DIMENSIONS

DFN20 CASE 505AB-01 ISSUE B

NOTES: 1. DIMENSIONS AND TOLERANCING PER ASME Y14.5M, 1994.

- 2. DIMENSIONS IN MILLIMETERS.

3. DIMENSION b APPLIES TO PLATED

- 3. DIMENSION b APPLIES TO PLATED TERMINALS AND IS MEASURED BETWEEN 0.25 AND 0.30 MM FROM TERMINAL

- 4. COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

|     | MILLIMETERS |      |  |

|-----|-------------|------|--|

| DIM | MIN         | MAX  |  |

| Α   | 0.80        | 1.00 |  |

| A1  | 0.00        | 0.05 |  |

| A2  | 0.65        | 0.75 |  |

| A3  | 0.20 REF    |      |  |

| b   | 0.20        | 0.30 |  |

| D   | 6.00 BSC    |      |  |

| D2  | 3.98        | 4.28 |  |

| E   | 5.00 BSC    |      |  |

| E2  | 2.98        | 3.28 |  |

| е   | 0.50 BSC    |      |  |

| К   | 0.20        |      |  |

| L   | 0.50        | 0.60 |  |

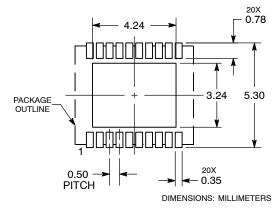

#### SOLDERING FOOTPRINT\*

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and use registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typical" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is a Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicatio coryight laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5773-3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative