## 30V/4A Half Bridge Driver

## ■ GENERAL DESCRIPTION

The **NJW4800** is a general purpose, half bridge power driver capable of supplying 4A current. The internal gate driver drives high-side/low-side power MOSFET; therefore, it has fast switching.

Additionally, it has protection features such as over current protection and thermal shutdown.

And in the case of failure, it can output a fault flag.

It is suitable for power switching applications of DSP/micro controller.

## ■ PACKAGE OUTLINE

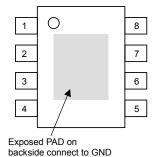

NJW4800GM1

## **■** FEATURES

- Output Switch Current ±4A

- Operating Voltage 7.5V to 30V

- Up to 1.2MHz Switching Frequency

- Thermal Shut Down

- Over Current Protection

- Under Voltage Lockouts

- Fault Indicator Output

- Stand-by Current I<sub>QOFF</sub> =3μA typ.

- High Heat Radiation Package

- Package Outline HSOP8

## ■ PIN CONFIGURATION

## PIN FUNCTION

- 1. PWM

- 2. VDD

- 3. OUT

- 4. GND

- 5. BS

- 6. STBY

- 7. REG

- 8. FLT

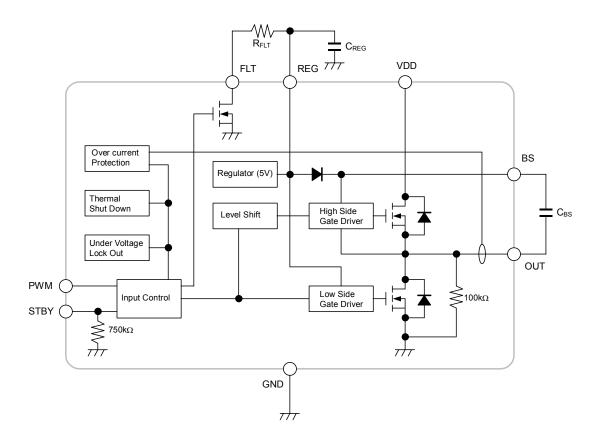

## ■ BLOCK DIAGRAM

## ■ ABSOLUTE MAXIMUM RATINGS

(Ta=25°C)

| PARAMETER                      | SYMBOL               | MAXIMUM RATINGS       | UNIT | REMARKS              |

|--------------------------------|----------------------|-----------------------|------|----------------------|

| Supply Voltage                 | V <sup>+</sup>       | 35                    | V    | VDD-GND pin          |

| Input Voltage                  | $V_{STBY} \ V_{PWM}$ | -0.3 ~ 6              | >    | STBY,<br>PWM-GND pin |

| FLT pin Voltage                | $V_{FLT}$            | -0.3 ~ 6              | V    | FLT-GND pin          |

| BS pin Voltage                 | $V_{BS}$             | 40                    | V    | BS-GND pin           |

| BS-OUT pin Voltage             | $V_{BS-OUT}$         | -0.3 ~ 6              | V    | BS-OUT pin           |

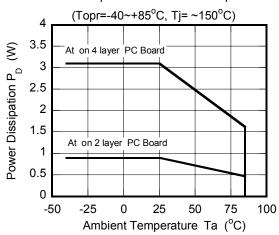

| Power Dissipation              | $P_D$                | 900 (*1)<br>3100 (*2) | W    | -                    |

| Operating Junction Temperature | Tj                   | -40 ~ +150            | °C   | _                    |

| Operating Temperature Range    | T <sub>opr</sub>     | -40 ~ +85             | °C   | _                    |

| Storage Temperature Range      | T <sub>stg</sub>     | -50 ~ +150            | °C   | _                    |

## ■ RECOMMENDED OPERATING CONDITIONS

(Ta=25°C)

| PARAMETER             | SYMBOL                                                                         | MIN. | TYP. | MAX.       | UNIT | REMARKS              |

|-----------------------|--------------------------------------------------------------------------------|------|------|------------|------|----------------------|

| Operating Voltage     | $V_{opr}$                                                                      | 7.5  | _    | 30         | V    | VDD-GND pin          |

| Output Switch Current | I <sub>OM</sub>                                                                | 0    | _    | 4          | Α    | OUT pin              |

| Input Voltage         | $egin{array}{c} egin{array}{c} egin{array}{c} V_{STBY}, \ V_{PWM} \end{array}$ | 0    | _    | 5.5        | V    | STBY,<br>PWM-GND pin |

| FLT pin Voltage       | $V_{FLT}$                                                                      | 0    | _    | $V_{REG1}$ | V    | FLT-GND pin          |

## ■ THERMAL CHARACTERISTICS

(Ta=25°C)

|                                     |        |                     | , ,  |

|-------------------------------------|--------|---------------------|------|

| PARAMETER                           | SYMBOL | THERMAL RESISTANCE  | UNIT |

| Junction-to-<br>Ambient Temperature | θја    | 139 (*1)<br>40 (*2) | °C/W |

| Junction-to-Case                    | ψjt    | 19 (*1)<br>3.7 (*2) | °C/W |

<sup>(\*1):</sup> Mounted on glass epoxy board based on EIA/JEDEC. ( $76.2 \times 114.3 \times 1.6$ mm: 2-Layers)

$(76.2 \times 114.3 \times 1.6 \text{mm}: 4\text{-Layers Internal foil area}: 74.2 \times 74.2 \text{mm})$

<sup>(\*2):</sup> Mounted on glass epoxy board based on EIA/JEDEC.

| PARAMETER                                      | SYMBOL                   | TEST CONDITION                                       | MIN. | TYP. | MAX. | UNIT |

|------------------------------------------------|--------------------------|------------------------------------------------------|------|------|------|------|

|                                                |                          |                                                      |      | •    |      | •    |

| General Characteristics                        |                          |                                                      |      | 1    |      |      |

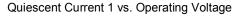

| Quiescent Current 1 (Operating)                | $I_{Q1}$                 | V <sub>PWM</sub> =0V                                 | _    | 1    | 2    | mA   |

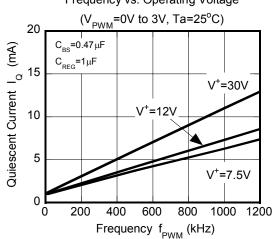

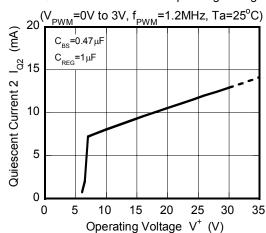

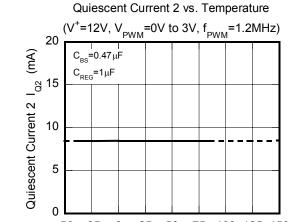

| Quiescent Current 2 (Switching)                | $I_{Q2}$                 | V <sub>PWM</sub> =0V to 3V, f <sub>PWM</sub> =1.2MHz | _    | 9    | 14   | mA   |

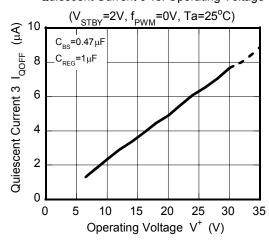

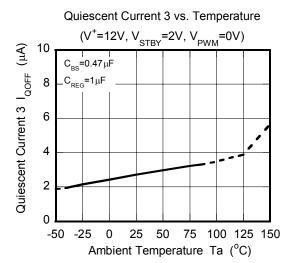

| Quiescent Current 3 (Standby)                  | $I_{QOFF}$               | V <sub>STBY</sub> =5.5V, V <sub>PWM</sub> =0V        | _    | 3    | 10   | μΑ   |

| O ( Dled                                       |                          |                                                      |      |      |      |      |

| Output Block                                   |                          | 10.14                                                |      | 0.05 | 0.45 |      |

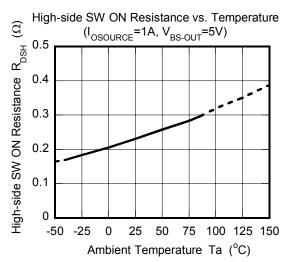

| High-side SW ON Resistance                     | R <sub>DSH</sub>         | I <sub>OSOURCE</sub> =1A, V <sub>BS-OUT</sub> =5V    |      | 0.25 | 0.45 | Ω    |

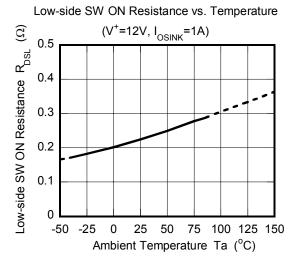

| Low-side SW ON Resistance                      | R <sub>DSL</sub>         | I <sub>OSINK</sub> =1A                               |      | 0.25 | 0.45 | Ω    |

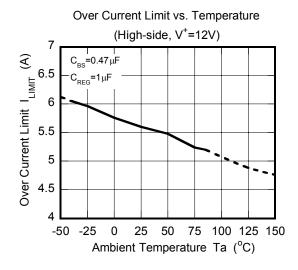

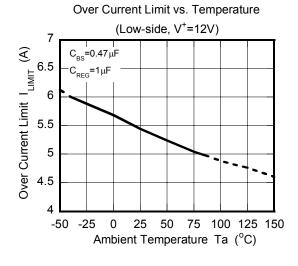

| Over Current Limit                             | I <sub>LIMIT</sub>       | High-side and Low-side                               | 4    | 5.5  | 7    | Α    |

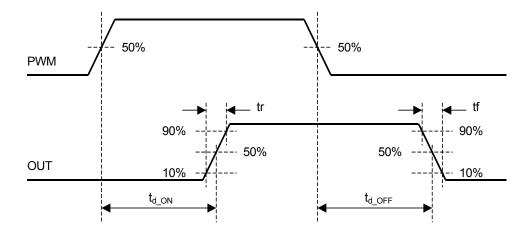

| Output Rise Time                               | tr                       | V <sub>PWM</sub> =0V to 3V                           | _    | 3    | _    | ns   |

| Output Fall Time                               | tf                       | V <sub>PWM</sub> =3V to 0V                           | _    | 3    | _    | ns   |

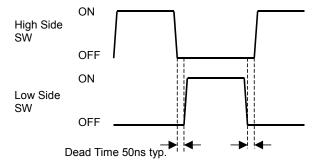

| Dead Time                                      | Dt                       | V <sub>PWM</sub> =0V to 3V                           | _    | 20   | _    | ns   |

| PWM Rise Delay Time                            | $t_{d\_ON}$              | V <sub>PWM</sub> =0V to 3V                           | _    | 60   | -    | ns   |

| PWM Fall Delay Time                            | $t_{d\_OFF}$             | V <sub>PWM</sub> =3V to 0V                           | _    | 60   | _    | ns   |

| OUT pin – VDD pin<br>Potential Difference      | $V_{PDOV}$               | V <sup>+</sup> =5.7V, I <sub>ORH</sub> =1A           | _    | 0.85 | 1.1  | V    |

| GND pin – OUT pin<br>Potential Difference      | $V_{PDGO}$               | V <sup>+</sup> =5.7V, I <sub>ORL</sub> =1A           | _    | 0.85 | 1.1  | V    |

| Output Pull-down Resistance                    | $R_{PD}$                 | $V^{+}$ =5.7V, $V_{STBY}$ =5.5V                      | 50   | 100  | 200  | kΩ   |

| Output Leak Current<br>(High Side SW OFF)      | I <sub>OLEAKOUT</sub>    | $V^{+}$ =30V, $V_{STBY}$ =5.5V, $V_{OUT}$ =0V        | _    | _    | 1    | μА   |

| OUT pin Output Current<br>(FLT Signal Output ) | I <sub>O-FLT</sub>       | V <sup>+</sup> =5.7V, V <sub>OUT</sub> =0V           | -    | 30   | 60   | μА   |

| Input Circuit Block                            |                          |                                                      |      |      |      |      |

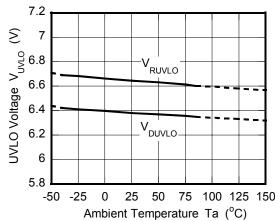

| STBY pin High Voltage<br>(Standby Mode)        | $V_{\text{IHSTBY}}$      |                                                      | 2.4  | _    | 5.5  | V    |

| STBY pin Low Voltage<br>(Operating Mode)       | $V_{\text{ILSTBY}}$      |                                                      | 0    | _    | 0.8  | V    |

| STBY pin Input Current                         | I <sub>ISTBY</sub>       | V <sub>STBY</sub> =5.5V                              | _    | 0.01 | 1    | μΑ   |

| STBY Pull-down Resistance                      | I <sub>ISTBY</sub>       |                                                      | 500  | 750  | 1000 | kΩ   |

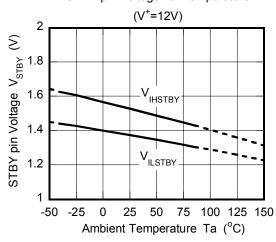

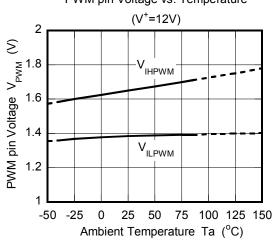

| PWM pin High Voltage                           | $V_{\text{IHPWM}}$       |                                                      | 2.2  |      | 5.5  | V    |

| PWM pin Low Voltage                            | $V_{\text{ILPWM}}$       |                                                      | 0    | _    | 0.9  | V    |

| PWM pin Input Current                          | I <sub>IPWM</sub>        | V <sub>PWM</sub> =5.5V                               | _    | 0.01 | 1    | μΑ   |

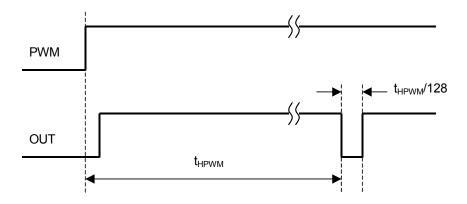

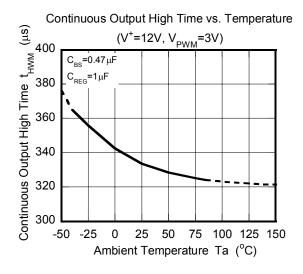

| Continuous Output High Time                    | t <sub>HPWM</sub>        | V <sub>PWM</sub> =5.5V                               | 140  | 300  | -    | μS   |

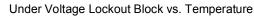

| Under Voltage Lockout (UVLO) BI                | ock                      |                                                      |      |      |      |      |

| UVLO Release Voltage                           | $V_{UVLO2}$              | V+ = L → H                                           | 5.9  | 6.6  | 7.3  | V    |

| UVLO Operation Voltage                         | V <sub>UVLO1</sub>       | V+ = H → L                                           | 5.65 | 6.35 | 7.05 | V    |

| UVLO Hysteresis Voltage                        | $\Delta V_{\text{UVLO}}$ | V <sub>UVLO2</sub> -V <sub>UVLO1</sub>               |      | 0.25 |      | V    |

$\blacksquare \ \, \text{ELECTRICAL CHARACTERISTICS} \quad \text{(Unless otherwise noted, V}^{+} = 12 \text{V, V}_{\text{STBY}} = 0 \text{V, C}_{\text{BS}} = 0.1 \mu\text{F, C}_{\text{REG}} = 1 \mu\text{F, Ta} = 25 ^{\circ}\text{C)}$

| PARAMETER                     | SYMBOL                | TEST CONDITION                                  | MIN. | TYP. | MAX. | UNIT |  |

|-------------------------------|-----------------------|-------------------------------------------------|------|------|------|------|--|

| Internal Power Supply Circuit |                       |                                                 |      |      |      |      |  |

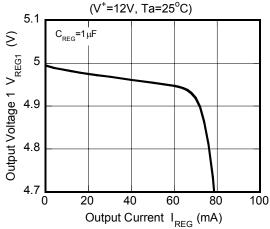

| Output Voltage 1              | $V_{REG1}$            | I <sub>REG</sub> =0mA                           | 4.75 | 5    | 5.25 | V    |  |

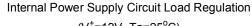

| Line Regulation               | $\Delta V_{REG-VDD}$  | $V^{+}=8 \sim 30V$ , $I_{REG}=0mA$              | _    | 2    | 20   | mV   |  |

| Load Regulation               | $\Delta V_{REG-IO}$   | $I_{REG}$ =0 ~ 20mA                             | _    | 20   | 50   | mV   |  |

| REG pin Output Current        | I <sub>OREG</sub>     | V <sub>REG1</sub> ×0.95,<br>Input signal=500kHz | 30   | _    | ı    | mA   |  |

| Fault Function (FLT pin)      |                       |                                                 |      |      |      |      |  |

| Low Level Output Voltage      | $V_{LFLT}$            | I <sub>FLT</sub> =500μA                         | _    | 0.25 | 0.5  | V    |  |

| OFF Leak Current              | I <sub>OLEAKFLT</sub> | V <sub>FLT</sub> =5.5V                          | _    | _    | 1    | μА   |  |

## ■ PIN OPERATION TABLE

|     | INF  | PUT                   |     | OUTPUT          |                |          |

|-----|------|-----------------------|-----|-----------------|----------------|----------|

| PWM | STBY | VDD                   | FLT | High-side<br>SW | Low-side<br>SW | Mode     |

| L   | L    | $V^{+} \ge V_{RUVLO}$ | ON  | OFF             | ON             | Normal   |

| Н   | L    | $V^{+} \ge V_{RUVLO}$ | ON  | ON (*3)         | OFF            | Normal   |

| L   | Н    | _                     | OFF | OFF             | OFF            | Stand-by |

| Н   | Н    | _                     | OFF | OFF             | OFF            | Stand-by |

| L   | L    | $V^{+} < V_{DUVLO}$   | OFF | OFF             | OFF            | UVLO     |

| Н   | L    | $V^+ < V_{DUVLO}$     | OFF | OFF             | OFF            | UVLO     |

<sup>(\*3)</sup> If PWM=H continues by t<sub>HPWM</sub> or more and is input, it becomes low-side SW=ON during t<sub>HPWM</sub>/128.

| INP       | UT                   | OUTPUT |                 |                | OUTPUT |  |  |

|-----------|----------------------|--------|-----------------|----------------|--------|--|--|

| Tj        | l <sub>out</sub>     | FLT    | High-side<br>SW | Low-side<br>SW | Mode   |  |  |

| Tj >150°C | _                    | OFF    | OFF             | OFF            | TSD    |  |  |

| _         | $I_{OUT} \ge I_{OM}$ | OFF    | OFF             | OFF            | OCP    |  |  |

## ■ TIMING CHART

Fig1. Output Rise/Fall Time, PWM Rise/Fall Delay Time

Fig2. Maximum Continuous Output Time (High-level)

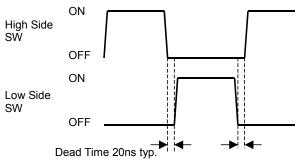

Fig3. Switching and Dead Time

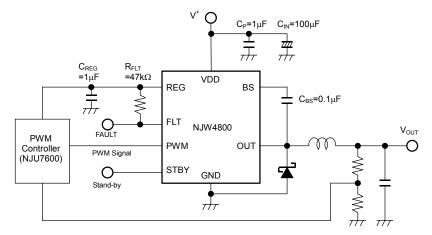

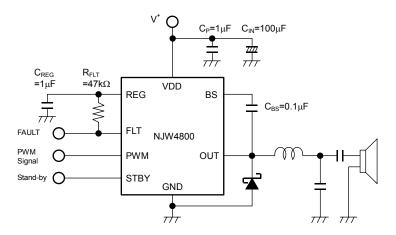

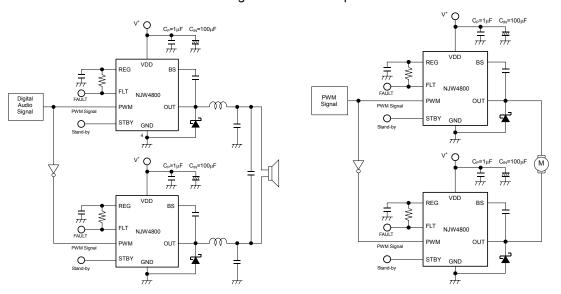

## ■ TYPICAL APPLICATIONS

Synchronous PWM step down switching regulator

Class-D single ended audio amplifier

Class-D full bridge audio amplifier

Full bridge motor driver

## ■ CHARACTERISTICS

## ■ CHARACTERISTICS

STBY pin Voltage vs. Temperature

## PWM pin Voltage vs. Temperature

Frequency vs. Operating Voltage

## ■ CHARACTERISTICS

$C_{REG}^{}=1 \mu F$

25 50 75 100 125 150

75 100 125 150

Ambient Temperature Ta (°C)

C<sub>BS</sub>=0.47μF

-50 -25

-25

-50

0

25 50

Ambient Temperature Ta (°C)

0

Quiescent Current 1 vs. Temperature

$(V^{+}=12V, V_{PWM}=0V)$

Quiescent Current 2 vs. Operating Voltage

Quiescent Current 3 vs. Operating Voltage

## ■ PIN DESCRIPTION

| - I II I DECONII I |             |                                                                                                                                                                                                                                                                  |

|--------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN<br>NUMBER      | PIN NAME    | FUNCTION                                                                                                                                                                                                                                                         |

| 1                  | PWM         | PWM Signal Input Terminal As for Control Logic, Refer to PIN OPERATION TABLE (page.5)                                                                                                                                                                            |

| 2                  | VDD         | Power Supply Terminal You should connect capacitor (AL and MLCC) for reducing Input Impedance.                                                                                                                                                                   |

| 3                  | OUT         | Output Terminal The High-side/Low-side Switch are Limited to 5.5A(typ.) by Over Current Protection Circuit.                                                                                                                                                      |

| 4                  | GND         | Ground Terminal                                                                                                                                                                                                                                                  |

| 5                  | BS          | Boot Strap Output Terminal Boot Strap Output drives the High-side Switch. You should connect capacitor larger than 0.1µF between BS Terminal (5-pin) and Out Terminal (3-pin).                                                                                   |

| 6                  | STBY        | Standby Terminal NJW4800 becomes standby status by High Level NJW4800 operates by Low Level                                                                                                                                                                      |

| 7                  | REG         | Built-in Regulator (5V) Output Terminal<br>You should connect capacitor larger than 1µF for stable output.                                                                                                                                                       |

| 8                  | FLT         | Fault Signal Output Terminal It is Open Drain Output Type. You should connect through Pull-up Resister to REG Terminal (7-pin) or External Power Supply. It outputs Low Level under normal operating condition and outputs High Level under Abnormal Conditions. |

| -                  | Exposed PAD | Connected to 4pin (Ground Terminal)                                                                                                                                                                                                                              |

### **■ FUNCTIONAL EXPLANATION**

## High-side, Low-side Switch

The SW output drives the load. It is controlled by the logic input signal from PWM terminal at PWM. When the signal at PWM is high (above 2.2V), the high-side switch is turned on. When the signal at PWM is low (less than 0.9V), the low-side switch is turned on.

The NJW4800 uses built-in Nch MOSFETs ( $R_{ON}$ =0.25 $\Omega$  typ.) for both the high-side and low-side switches. The high-side SW gate is driven with V<sup>+</sup>+5V that generated by bootstrap. The high-side SW turn on time is limited to 300µsec(typ.). (ex. Fig2)

There is a dead time region (20nsec (typ.): design value) to prevent short circuit (high-side and low-side) where both the high-side and low-side switches are off. (ex. Fig3)

The NJW4800 is suitable for high-frequency switching regulator. The NJW4800 operates at frequencies up to 1.2MHz.

The OUT terminal is pulled down inside with  $100k\Omega$ , compensates the leak current of the High-side SW.

Fig3. SW Function and Dead Time Relation

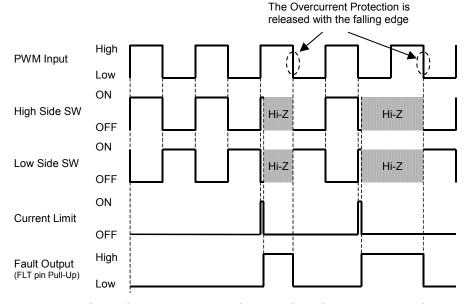

## Over Current Protection Function

The internal over-current protection circuit monitors the flow currents of both the high-side and low-side switches. The over-current protection circuit operates at 5.5A (typ.) and stops the SW operation. The FLT signal is output from FLT terminal at the same time. The over-current protection operation is released at the PWM input signal falling edge. (ex. Fig4)

If OUT terminal is shorted directly to GND, a large surge current is flowing for fast current change and may exceed current limit. Because that time big electric power consumption occurs instantaneously in NJW4800, you should design sufficient heat dissipation.

When a load condition is inductive property, a reverse direction current flows to the high-side and low-side SW body diode by inductive kickback.

The built-in over-current protection circuit has not aimed at protection against the inductive kickback.

Therefore, an external diode should be considered usage against reverse-current regeneration according to the kind of the application.

Fig4. Timing Chart of High-side/Low-side Switch at Over Current Protection Operating

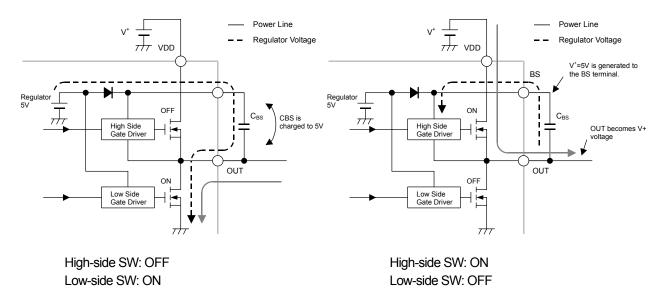

## Boot Strap

In order to drive the gate of the high side SW, the voltage that is higher than power supply voltage is necessary. The bootstrap condenser generates the power supply voltage of  $V^++5V$  to BS terminal and it supplies the power to the gate of the high side SW. As Shown as Fig5 in detail.

Fig5. High-side SW driven by Boot Strap

You should connect bootstrap condenser larger than C<sub>BS</sub>=0.1μF between BS Terminal and OUT Terminal.

The internal counter decides the bootstrap condenser Charge and Discharge time.

A capacitor discharge time (t<sub>HPWM</sub>) for High-side SW Maximum ON Time is 300ms (typ).

A capacitor charge time (t<sub>HPWM</sub> / 128) for Low-side SW Minimum ON Time is 2.34µs (typ).

#### Built-in Regulator

The REG Terminal outputs Reference Voltage (5V).

It can be used as generating of the voltage for the bootstrap or a power supply voltage for other device(s). You should connect capacitor ( $C_{REG}$ ) larger than  $1\mu F$  for stable regulator output.

This regulator current capability ( $I_{OREG}$ ) is 30mA (min) at ( $V_{REG1} \times 0.95$ ). This regulator over current protection is a drooping characteristic type. It has drooping characteristic at over current protection function.

## Thermal Shut Down Function

When NJW4800 chip temperature exceeds the 170°C, internal thermal shutdown circuit operates and SW function is stopped. The Fault signal is output simultaneously from the FLT terminal. In order to return SW operation, you should make chip surface temperature (Junction Temperature: Tj) below the 150°C\*.

This function is a circuit to prevent IC at the high temperature from malfunctioning and is not something that urges positive use. You should make sure to operate inside the junction temperature range rated. (\* Design value)

## NJW4800

## Under Voltage Lockout(UVLO)

The UVLO circuit operating is released above  $V^{\dagger}$ =6.6V(typ.) and IC operation starts. When power supply voltage is low, because the UVLO circuit operates, IC does not operate. There is 0.25V width hysteresis voltage at rise and decay of power supply voltage. Hysteresis prevents the malfunction at the time of UVLO operating and releasing.

## FAULT Signal Output

This Terminal is Open Drain Output Type. You should connect through Pull-up Resister to REG Terminal (7-pin) or External Power Supply. It outputs Low Level under normal operating condition and outputs High Level under Abnormal Conditions.

The following information is output as FAULT signal.

- Stop Operation at Under Voltage Lockout (UVLO)

- · Over Current Protection Function

- Thermal Shut Down

At the time of standby state, it outputs High Level.

When outputting the FAULT signal, it has stopped SW operation, but the internal regulator continues operation. Because of this 30mA it is flowing via the OUT terminal from the regulator circuit.

## Standby Function

NJW4800 stops the operating and becomes standby status when 2.4V or more is supplied to STBY terminal. You should connect the terminal with GND level to prevent the malfunction by a noise when you do not use this function.

#### ■ APPLICATION TIPS

In the application that does a high-speed switching of NJW4800, because the current flow corresponds to the input frequency, the substrate (PCB) layout becomes an important.

NJW4800 is driving the High-side/Low-side SW gate with high speed to reduce switching losses. The transient voltage is generated by parasitic inductance and a high-speed current change of high side and low side SW.

You should attempt the transition voltage decrease by making a current loop area minimize as much as possible. Therefore, you should make a current flowing line thick and short as much as possible.

You should insert a bypass capacitor between VDD terminal and GND terminal to prevent malfunction by generating over voltage and/or exceed maximum input voltage rating. The recommended bypass capacitor is  $1\mu F$  or more high frequency capacitor.

A  $100\mu$ F aluminum electrolysis capacitor is recommended for smoothing condenser. However, you should use larger capacitor by sufficient evaluation (assessment) due to load condition and/or application use environment. (There is a possibility that the supply voltage rises by inductive kickback when the supply current of the inductive load is large.) The bypass capacitors should be connected as much as possible near VDD terminal.

#### Ex. Bill of Materials

| Components      | Parts Name         | Functions                         | Manufacturers    |

|-----------------|--------------------|-----------------------------------|------------------|

| C <sub>IN</sub> | -                  | Aluminum-Cap.                     | Nippon Chemi-con |

| $C_P$           | GRM21BB11H104KA01B | Ceramic-Cap. 0.1μF, 50V (B-val)   | Murata           |

| $C_REG$         | GRM31MB31H105KA87B | Ceramic-Cap. 1µF, 50V (B-val)     | Murata           |

| $C_{BS}$        | GRM21BR71H474KA88B | Ceramic-Cap. 0.1µF, 50V (X7R-val) | Murata           |

| $R_{FLT}$       | RK73B1JT473        | 47kΩ                              | KOA              |

# **MEMO**

[CAUTION]

The specifications on this databook are only given for information , without any guarantee as regards either mistakes or omissions. The application circuits in this databook are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.