## MIC47050

# 500mA ULDO™ with Low Input and Low Output Voltage

## **General Description**

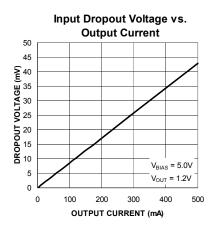

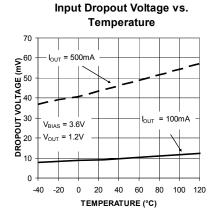

The MIC47050 is a high-speed, ultra-low dropout, dual-supply NMOS ULDO™ designed to take advantage of point-of-load applications that use multiple supply rails to generate a low-voltage, high-current power supply. The MIC47050 can source 500mA of output current while only requiring a 1µF ceramic output capacitor for stability. A 1.5% output voltage accuracy, low dropout voltage (44mV @ 500mA), and low ground current makes this device ideally suited for mobile and point-of-load applications.

The MIC47050 has an NMOS output stage offering very low output impedance. The NMOS output stage makes for a unique ability to respond very quickly to sudden load changes such as that required by a microprocessor, DSP or FPGA. The MIC47050 consumes little quiescent current and therefore can be used for driving the core voltages of mobile processors, post regulating a core DC/DC converter in any processor.

The MIC47050 is available in fixed and adjustable output voltages in the tiny 2mm x 2mm MLF $^{\otimes}$  package with an operating junction temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C.

Data sheets and support documentation can be found on Micrel's web site at: <a href="https://www.micrel.com">www.micrel.com</a>.

## **Features**

Voltage Range

Input Voltage: 1.0V to 3.6VBias Voltage: 2.3V to 5.5V

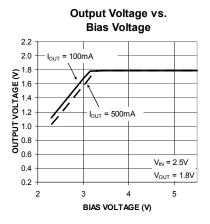

0.4V to 2.0V output voltage range

• Low dropout voltage of 44mV at 500mA

• ±1.5% initial output voltage accuracy

• High bandwidth – very fast transient response

• Stable with a 1µF ceramic output capacitor

· Logic level enable input

• UVLO on both supply voltages

• Thermally-enhanced 2mm x 2mm MLF® package

• Junction temperature range of -40°C to +125°C

## **Applications**

- · Point-of-load applications

- PDAs, Notebooks, and Desktops

- · Datacom and Telecom systems

- DSP, PLD and FPGA power supply

- Low-voltage post regulation

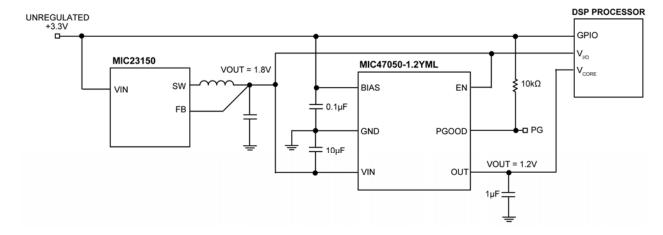

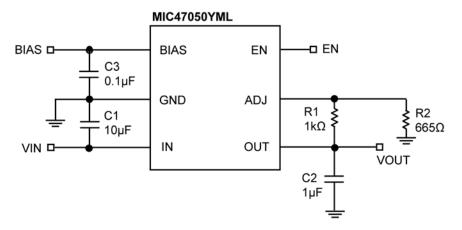

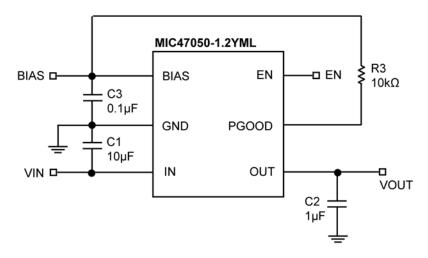

# Typical Application

ULDO is a trademark of Micrel Inc.

MLF and MicroLeadFrame are registered trademarks of Amkor Technology, Inc.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

March 2010 M9999-032310-A

## **Ordering Information**

| Part Number     | Voltage <sup>(1)</sup> | Marking Code <sup>(2)</sup> | Temperature<br>Range | Package                          | Lead Finish <sup>(3)</sup> |

|-----------------|------------------------|-----------------------------|----------------------|----------------------------------|----------------------------|

| MIC47050-1.2YML | 1.2V                   | ZG4                         | -40°C to +125°C      | 6-Pin 2mm x 2mm MLF <sup>®</sup> | Pb-Free                    |

| MIC47050YML     | ADJ                    | ZGA                         | -40°C to +125°C      | 6-Pin 2mm x 2mm MLF <sup>®</sup> | Pb-Free                    |

#### Notes:

- 1. Other Voltage available. Contact Micrel Marketing for details.

- 2. Overbar ( ) may not be to scale.

- 3. MLF® is a GREEN RoHS compliant package. Lead finish is NiPdAu. Mold compound is Halogen Free.

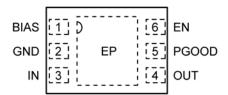

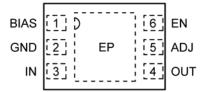

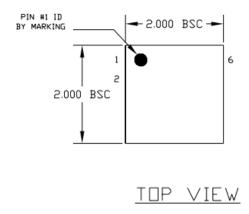

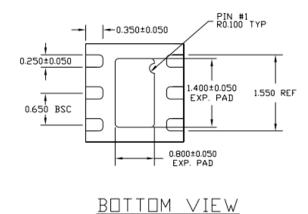

# **Pin Configuration**

6-pin 2mm x 2mm MLF® - Fixed (ML)

6-pin 2mm x 2mm MLF® - Adjustable (ML)

# **Pin Description**

| Fixed | ADJ | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                       |

|-------|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | 1   | BIAS     | Bias Supply. The bias supply is the power supply for the internal circuitry of the regulator.                                                                                                                                                                                                                      |

| 2     | 2   | GND      | Ground. Ground pins and exposed pad must be connected externally.                                                                                                                                                                                                                                                  |

| 3     | 3   | IN       | Input Supply. Drain of NMOS pass transistor which is the power input voltage for regulator. The NMOS pass transistor steps down this input voltage to create the output voltage.                                                                                                                                   |

| 4     | 4   | OUT      | Output. Output Voltage of Regulator.                                                                                                                                                                                                                                                                               |

| 5     | _   | PGOOD    | Power Good Output. Open-drain output. Output is driven low when the output voltage is less than the power good threshold of its programmed nominal output voltage. When the output goes above the power good threshold, the open-drain output goes high-impedance, allowing it to be pulled up to a fixed voltage. |

| _     | 5   | ADJ      | Adjust Input. Connect external resistor divider to program the output voltage.                                                                                                                                                                                                                                     |

| 6     | 6   | EN       | Enable: TTL/CMOS compatible input. Logic high = enable, logic low = shutdown. Do not leave floating.                                                                                                                                                                                                               |

| EP    | EP  | GND      | Exposed thermal pad. Connect to the ground plane to maximize thermal performance.                                                                                                                                                                                                                                  |

# Absolute Maximum Ratings<sup>(1)</sup>

| 0.3V to +4V                |

|----------------------------|

| 0.3V to +6V                |

|                            |

| 260°C                      |

| 65°C to +150°C             |

| –65°C to +150°C<br>2kV HBM |

|                            |

# Operating Ratings<sup>(2)</sup>

| IN Supply Voltage (V <sub>IN</sub> )+1.0V                | to $+3.6V$ ( $V_{IN} < V_{BIAS}$ ) |

|----------------------------------------------------------|------------------------------------|

| Bias Voltage (V <sub>BIAS</sub> )                        | +2.3V to +5.5V                     |

| Enable Voltage (V <sub>EN</sub> )                        | 0V to V <sub>BIAS</sub>            |

| Power Good Voltage (V <sub>PGOOD</sub> )                 | 0V to V <sub>BIAS</sub>            |

| Output Voltage Range                                     | 0.4V to 2.0V                       |

| Junction Temperature (T <sub>J</sub> )                   |                                    |

| Ambient Temperature (T <sub>A</sub> )                    | 40°C to +85°C                      |

| Junction Thermal Resistance                              |                                    |

| 2mm x 2mm MLF <sup>®</sup> -6L (θ <sub>JA</sub> )        | 90°C/W                             |

| 2mm x 2mm MLF $^{\text{®}}$ -6L ( $\theta_{\text{JC}}$ ) | 45°C/W                             |

|                                                          |                                    |

# **Electrical Characteristics**(4)

$V_{IN} = V_{OUT} + 0.5V; \ V_{BIAS} = V_{OUT} + 2.1V; \ C_{OUT} = 1 \mu F; \ I_{OUT} = 100 \mu A; \ T_J = 25^{\circ}C, \ \textbf{bold} \ values \ indicate -40^{\circ}C \leq T_J \leq +125^{\circ}C, \ unless \ noted.$

| Parameter                                                         | Condition                                                           | Min. | Тур.  | Max. | Units |

|-------------------------------------------------------------------|---------------------------------------------------------------------|------|-------|------|-------|

| Input Supply                                                      |                                                                     |      |       |      |       |

| Input Voltage Range (V <sub>IN</sub> )                            |                                                                     | 1.0  |       | 3.6  | V     |

| V <sub>IN</sub> UVLO Threshold <sup>(5)</sup>                     | V <sub>IN</sub> Rising                                              | 0.7  | 0.85  | 1.0  | V     |

| V <sub>IN</sub> UVLO Hysteresis                                   |                                                                     |      | 40    |      | mV    |

| Ground Current in Shutdown (I <sub>GND</sub> )                    | V <sub>EN</sub> ≤ 0.2V (Regulator Shutdown)                         |      | 0.1   | 1.0  | μΑ    |

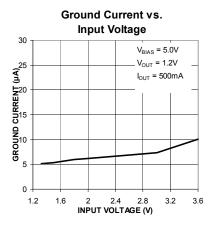

| Ground Current (I <sub>GND</sub> )                                | I <sub>OUT</sub> = 500mA; V <sub>IN</sub> = V <sub>OUT</sub> + 0.5V |      | 6     |      | μА    |

| Bias Supply                                                       |                                                                     | •    | •     | •    | •     |

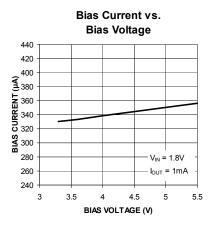

| BIAS Input Voltage (V <sub>BIAS</sub> )                           |                                                                     | 2.3  |       | 5.5  | V     |

| V <sub>BIAS</sub> UVLO Threshold <sup>(5)</sup>                   | V <sub>BIAS</sub> Rising                                            | 1.7  | 2.1   | 2.3  | V     |

| V <sub>BIAS</sub> UVLO Hysteresis                                 |                                                                     |      | 75    |      | mV    |

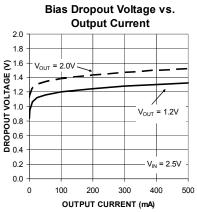

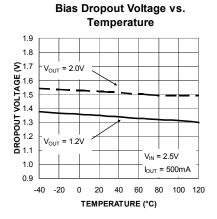

| Dranaut voltage (V V )                                            | I <sub>OUT</sub> = 100mA                                            |      | 1.15  |      | V     |

| Dropout voltage (V <sub>BIAS</sub> - V <sub>OUT</sub> )           | I <sub>OUT</sub> = 500mA                                            |      | 1.25  | 2.1  | V     |

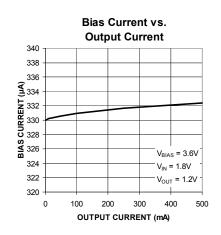

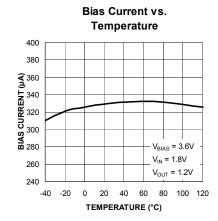

| V <sub>BIAS</sub> Supply Current (I <sub>BIAS</sub> )             | I <sub>OUT</sub> = 1mA; V <sub>BIAS</sub> = V <sub>OUT</sub> + 2.1V |      | 330   | 500  | μΑ    |

| V <sub>BIAS</sub> Supply Current in Shutdown (I <sub>BIAS</sub> ) | V <sub>EN</sub> ≤ 0.2V (Regulator Shutdown)                         |      | 0.1   | 1.0  | μА    |

| Output Voltage                                                    | ·                                                                   |      |       | •    |       |

| Dropout voltage                                                   | I <sub>OUT</sub> = 100mA                                            |      | 9     | 50   | mV    |

| (V <sub>IN</sub> - V <sub>OUT</sub> )                             | I <sub>OUT</sub> = 500mA                                            |      | 44    | 120  | mV    |

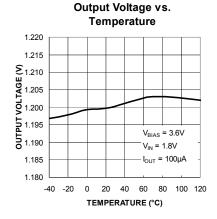

| Output Valtage Assurance                                          | Ι <sub>ΟUT</sub> = 100μΑ                                            | -1.5 |       | +1.5 | %     |

| Output Voltage Accuracy                                           | I <sub>OUT</sub> = 100μA                                            | -2.0 |       | +2.0 | %     |

| V <sub>BIAS</sub> Line Regulation                                 | V <sub>BIAS</sub> = V <sub>OUT</sub> + 2.1V to 5.5V                 | -0.1 | 0.015 | 0.1  | %/V   |

# **Electrical Characteristics**(4)

$V_{\text{IN}} = V_{\text{OUT}} + 0.5 \text{V}; \ V_{\text{BIAS}} = V_{\text{OUT}} + 2.1 \text{V}; \ C_{\text{OUT}} = 1 \mu \text{F}; \ I_{\text{OUT}} = 100 \mu \text{A}; \ T_{\text{J}} = 25 ^{\circ} \text{C}, \ \textbf{bold} \ \text{values indicate} \ -40 ^{\circ} \text{C} \\ \leq T_{\text{J}} \leq +125 ^{\circ} \text{C}, \ \text{unless noted}. \ \text{C} = 1 \text{C} + 125 ^{\circ} \text{C}, \ \text{C} = 1 \text{C} + 125 ^{\circ} \text{C}, \ \text{C} = 1 \text{C} + 125 ^{\circ} \text{C}, \ \text{C} = 1 \text{C} + 125 ^{\circ} \text{C}, \ \text{C} = 1 \text{C} + 125 ^{\circ} \text{C}, \ \text{C} = 1 \text{C} + 125 ^{\circ} \text{C}, \ \text{C} = 1 \text{C} + 125 ^{\circ} \text{C}, \ \text{C} = 1 \text{C} + 125 ^{\circ} \text{C}, \ \text{C} = 1 \text{C} + 125 ^{\circ} \text{C}, \ \text{C} = 1 \text{C} + 125 ^{\circ} \text{C}, \ \text{C} = 1 \text{C} + 125 ^{\circ} \text{C}, \ \text{C} = 1 \text{C} + 125 ^{\circ} \text{C}, \ \text{C} = 1 \text{C} + 125 ^{\circ} \text{C}, \ \text{C} = 125 ^{\circ} \text{C$

| Parameter                                                      | Condition                                                        | Min.  | Тур.  | Max.  | Units         |

|----------------------------------------------------------------|------------------------------------------------------------------|-------|-------|-------|---------------|

| V <sub>IN</sub> Line Regulation                                | $V_{IN} = V_{OUT} + 0.5V \text{ to } 3.6V$                       | -0.05 | 0.005 | 0.05  | %/V           |

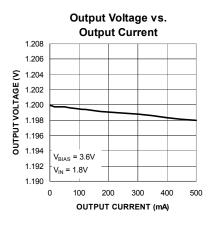

| Load Regulation                                                | I <sub>OUT</sub> = 10mA to 500mA                                 |       | 0.2   | 0.5   | %             |

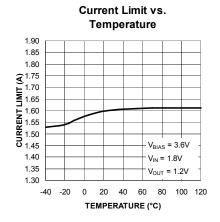

| Current Limit                                                  |                                                                  |       |       |       |               |

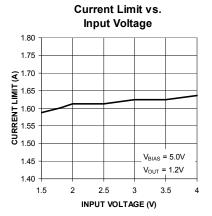

| Short Circuit Current Limit                                    | V <sub>IN</sub> = 2.7V; V <sub>OUT</sub> = 0V                    | 0.6   | 1.6   | 2.5   | Α             |

| Enable Input                                                   |                                                                  |       |       |       |               |

| EN Logic Level High                                            |                                                                  | 1.0   | 0.77  |       | V             |

| EN Logic Level Low                                             |                                                                  |       | 0.67  | 0.2   | V             |

| EN Hysteresis                                                  |                                                                  |       | 100   |       | mV            |

| Enable Bigs Current                                            | V <sub>EN</sub> ≤ 0.2V ( Regulator Shutdown)                     |       | 1     |       | μА            |

| Enable Bias Current                                            | V <sub>EN</sub> ≥ 1.0V ( Regulator Enabled)                      |       | 6     |       | μΑ            |

| Turn-on Time                                                   | $C_{OUT}$ = 1 $\mu$ F; 90% of typical $V_{OUT}$                  |       | 15    | 500   | μS            |

| Thermal Protection                                             |                                                                  | •     |       |       |               |

| Over-Temperature Shutdown                                      | T <sub>J</sub> Rising                                            |       | 160   |       | °C            |

| Over-Temperature Shutdown Hysteresis                           |                                                                  |       | 20    |       | °C            |

| Power Good                                                     |                                                                  |       |       |       |               |

| Davis October 1 Thursday 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | V <sub>OUT</sub> Rising                                          |       | 91    | 95    | %             |

| Power Good Threshold Voltage                                   | V <sub>OUT</sub> Falling                                         | 85    | 89    |       | %             |

| Power Good Hysteresis                                          |                                                                  |       | 2     |       | %             |

| Power Good Output Low Voltage                                  | I <sub>PG</sub> = 250μA                                          |       | 0.02  | 0.1   | V             |

| Power Good Leakage Current                                     | V <sub>PG</sub> = 5.0V                                           | -1    | 0.01  | +1    | μΑ            |

| Reference Voltage (Adjustable Option On                        | ly)                                                              |       |       |       |               |

| Fig. Book B. Constant V. House                                 | I <sub>OUT</sub> = 100μA                                         | 0.394 |       | 0.406 | V             |

| Feedback Reference Voltage                                     | $I_{OUT} = 100\mu A$                                             | 0.392 | 0.4   | 0.408 | V             |

| FB Bias Current                                                | V <sub>FB</sub> = 0.8V                                           |       | 20    |       | nA            |

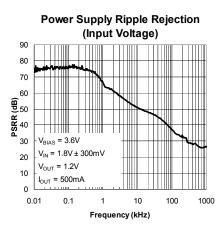

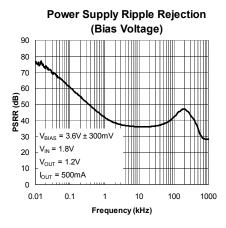

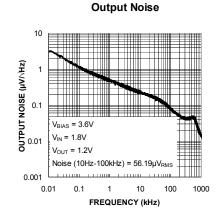

| Output Voltage Noise and Ripple Rejection                      | n                                                                |       |       |       |               |

| Output Voltage Noise                                           | $f = 10Hz \text{ to } 100kHz; I_{OUT} = 100mA; C_{OUT} = 1\mu F$ |       | 63    |       | $\mu V_{RMS}$ |

| B: 4 B : #                                                     | $f = 10kHz; C_{OUT} = 1.0\mu F, I_{OUT} = 100mA$                 |       | 50    |       | dB            |

| Ripple Rejection                                               | $f = 100kHz$ ; $C_{OUT} = 1.0\mu F$ , $I_{OUT} = 100mA$          |       | 37    |       | dB            |

| Notes:                                                         | <u> </u>                                                         |       |       |       | 1             |

#### Notes:

- 1. Exceeding the absolute maximum rating may damage the device.

- 2. The device is not guaranteed to function outside its operating rating.

- 3. Devices are ESD sensitive. Handling precautions recommended. Human body model,  $1.5k\Omega$  in series with 100pF.

- 4. Specification for packaged product only.

- 5. Both VIN and VBIAS UVLO thresholds must be met for the output voltage to turn-on. If either of the two input voltages is below the UVLO thresholds, the output is disabled.

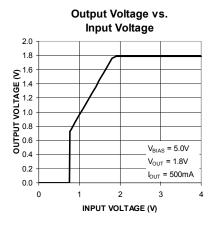

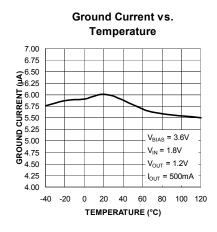

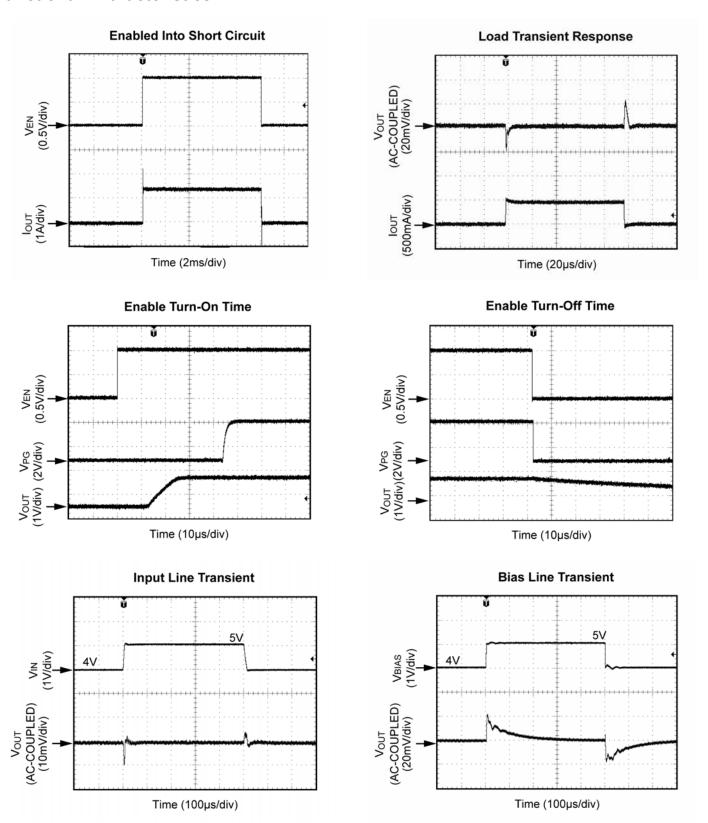

## **Typical Characteristics**

## **Typical Characteristics (Continued)**

## **Functional Characteristics**

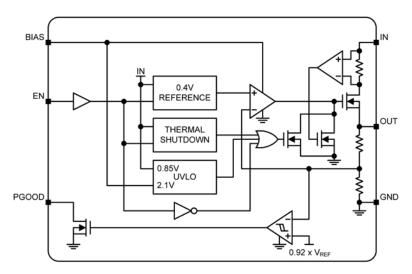

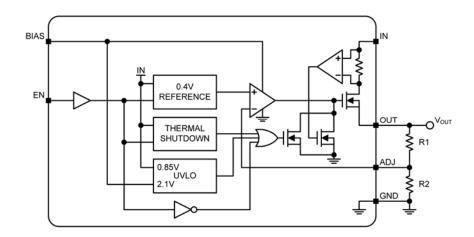

# **Functional Diagram**

MIC47050 Fixed Output Block Diagram

MIC47050 Adjustable Output Block Diagram

## **Functional Description**

The MIC47050 is a high-speed, ultra-low dropout, dual supply NMOS ULDO™ designed to take advantage of point-of-load applications that use multiple supply rails to generate a low voltage, high current power supply. The MIC47050 can source 0.5A of output current while only requiring a 1µF ceramic output capacitor for stability. The MIC47050 regulator is fully protected from damage due to fault conditions, offering linear current limiting and thermal shutdown.

### **Bias Supply Voltage**

$V_{BIAS}$ , requiring relatively light current, provides power to the control portion of the MIC47050. Bypassing on the bias pin is recommended to improve performance of the regulator during line and load transients. Small  $0.1\mu F$  ceramic capacitors from  $V_{BIAS}$ -to-ground help reduce high frequency noise from being injected into the control circuitry from the bias rail and are good design practice.

#### **Input Supply Voltage**

$V_{\text{IN}}$  provides the supply to power the LDO. The minimum input voltage is 1.0V. This allows conversion from low voltage supplies to reduce the power dissipation in the pass element.

### **Input Capacitor**

The MIC47050 is a high-performance, high bandwidth device. Therefore, it requires a well-bypassed input supply for optimal performance. A 1µF capacitor is the minimum required for stability. A 10µF ceramic capacitor is recommended for most applications, especially if the LDO's headroom (V\_IN –V\_OUT) is small and/or large load transients are present. Fast load transient and low headroom requires a larger input filter capacitor to ensure that the regulator does not drop out of regulation. A 10µF will better attenuate any voltage glitches from exceeding the maximum voltage rating of the part.

Additional high-frequency capacitors, such as small-valued NPO dielectric-type capacitors, help filter out high-frequency noise and are good practice in any RF-based circuit.

X7R and X5R dielectric ceramic capacitors are recommended because of their temperature performance. X7R-type capacitors change capacitance by 15% over their operating temperature range and are the most stable type of ceramic capacitors. Z5U and Y5V dielectric capacitors are not recommended since they change value by as much as 50% and 60% respectively over their operating temperature ranges. To use a ceramic-chip capacitor with Y5V dielectric, the value must be much higher than an X7R ceramic or a tantalum capacitor to ensure the same capacitance value over the operating temperature range. Tantalum capacitors have a very stable dielectric (10% over their operating temperature range) and can also be used with this device. See "*Typical Characteristic*" for examples of load transient response.

### **Output Capacitor**

The MIC47050 requires an output capacitor of  $1\mu F$  or greater to maintain stability. The design is optimized for use with low-ESR ceramic chip capacitors. High ESR capacitors may cause high frequency oscillation. The output capacitor can be increased, but performance has been optimized for a  $1\mu F$  ceramic output capacitor and does not improve significantly with larger capacitance.

The output capacitor type and placement criteria are the same as the input capacitor. See the input capacitor subsection for a detailed description.

#### **Minimum Load Current**

The MIC47050, unlike most other regulators, does not require a minimum load to maintain output voltage regulation.

### **Adjustable Regulator Design**

The MIC47050 adjustable version allows programming the output voltage from 0.4V to 2.0V. Two external resistors are required. The R1 resistor value between  $V_{\text{OUT}}$  and the ADJ pin should not exceed  $10k\Omega$ , as larger values can cause instability. R2 connects between the ADJ pin and ground. The resistor values are calculated as follows:

$$R1 = R2 \times \left( \frac{V_{OUT}}{V_{REF}} - 1 \right)$$

Where  $V_{\text{OUT}}$  is the desired output voltage and  $V_{\text{REF}}$  is the internal reference voltage.

#### Enable/Shutdown

The MIC47050 comes with a single active-high enable pin that allows the regulator to be disabled. Forcing the enable pin low disables the regulator and sends it into a "zero" off-mode-current state. In this state, current consumed by the regulator goes nearly to zero. Forcing the enable pin high enables the output voltage. The active-high enable pin uses CMOS technology and the enable pin cannot be left floating; a floating enable pin may cause an indeterminate state on the output.

#### **Power Good**

The PGOOD pin is an open drain output that goes low when the output voltage (fixed version) drops below the PGOOD threshold voltage.

The pull-up resistor value should be large enough to guarantee a proper "low" voltage when the PGOOD pin pulls low. The PGOOD low voltage is typically 0.1V at 250uA current. A 10k resistor or greater is recommended when pulling up to 3.3V bias.

If the Power Good function is not required, the PGOOD pin may be left unconnected.

#### **Thermal Shutdown**

The MIC47050 has an internal over-temperature protection feature. This feature is for protection only. The device should never be intentionally operated near this temperature as this may reduce long term reliability. The device will turn off when the over-temperature threshold is exceeded. A 20°C hysteresis is built in to allow the device to cool before turning back on.

#### **Thermal Considerations**

The MIC47050 is designed to provide 0.5A of continuous current in a very small package. Maximum ambient operating temperature can be calculated based on the output current and the voltage drop across the part. Given that the input voltage is 1.8V, the output voltage is 1.2V and the output current is 0.5A. The actual power dissipation of the regulator circuit can be determined using the equation:

$$P_{D} = (V_{IN} - V_{OUT}) \times I_{OUT} + V_{IN} \times I_{GND} + V_{BIAS} \times I_{BIAS}$$

Because this device is CMOS, the ground current is insignificant for power dissipation and can be ignored for this calculation.

$$P_D = (1.8V - 1.2V) \times 0.5A = 0.3W$$

To determine the maximum ambient operating temperature of the package, use the junction-to-ambient thermal resistance of the device and the following basic equation:

$$P_{D(MAX)} = \left[ \frac{T_{J(MAX)} - T_{A}}{\Theta_{JA}} \right]$$

$T_{J(MAX)}$  = 125°C, the maximum junction temperature of the die.

$\theta_{JA}$  thermal resistance = 90°C/W.

Table 1 shows junction-to-ambient thermal resistance for the MIC47050 in the MLF<sup>®</sup> package.

**Table 1. Thermal Resistance**

| Package              | θ <sub>JA</sub> Recommended<br>Min. Footprint | θ <sub>JC</sub> |

|----------------------|-----------------------------------------------|-----------------|

| 6-pin 2mm x 2mm MLF® | 90°C/W                                        | 45°C/W          |

Substituting  $P_D$  for  $P_{D(max)}$  and solving for the ambient operating temperature will give the maximum operating conditions for the regulator circuit. The junction-to-ambient thermal resistance for the minimum footprint is 90°C/W. The maximum power dissipation must not be exceeded for proper operation. For example, when operating the MIC47050-1.2YML at an input voltage of 1.8V and a 0.5A load with a minimum footprint layout, the maximum ambient operating temperature  $T_A$  can be determined as follows:

$$T_A = T_{J(MAX)} - \Theta_{JA} \times P_{D(MAX)}$$

$T_A = 125^{\circ}C - 90^{\circ}C/W \times 0.3W$

$T_A = 98^{\circ}C$

Therefore, a 1.2V application with 0.5A of output current can accept an ambient operating temperature of 98°C in a 2mm x 2mm MLF<sup>®</sup> package.

#### **Thermal Measurements**

Measuring the IC's case temperature is recommended to insure it is within its operating limits. Although this might seem like a very elementary task, it is easy to get erroneous results. The most common mistake is to use the standard thermal couple that comes with a thermal meter. This thermal couple wire gauge is large, typically 22 gauge, and behaves like a heatsink, resulting in a lower case measurement.

Two methods of temperature measurement are using a smaller thermal couple wire or an infrared thermometer. If a thermal couple wire is used, it must be constructed of 36 gauge wire or higher (smaller wire size) to minimize the wire heat-sinking effect. In addition, the thermal couple tip must be covered in either thermal grease or thermal glue to make sure that the thermal couple junction is making good contact with the case of the IC. Omega brand thermal couple (5SC-TT-K-36-36) is adequate for most applications.

Wherever possible, an infrared thermometer is recommended. The measurement spot size of most infrared thermometers is too large for an accurate reading on a small form factor ICs. However, a IR thermometer from Optris has a 1mm spot size, which makes it a good choice for the 2mm x 2mm MLF® package. An optional stand makes it easy to hold the beam on the IC for long periods of time.

For a full discussion of heat sinking and thermal effects of voltage regulators, refer to the "Regulator Thermals" section of Micrel's *Designing with Low-Dropout Voltage Regulators* handbook. This information can be found on Micrel's website at:

http://www.micrel.com/ PDF/other/LDOBk ds.pdf

# **MIC47050 Typical Application Schematic**

MIC47050 Adjustable Output

MIC47050 Fixed Output

## MIC47050 Bill of Materials

| Item | Part Number        | Manufacturer                | Description                                          | Qty. |

|------|--------------------|-----------------------------|------------------------------------------------------|------|

| C1   | GRM21BR60J106ME19  | Murata <sup>(1)</sup>       | Ceramic Capacitor, 10µF, 6.3V, X5R, 0603 size        | 1    |

|      | C1608X5R0J106MT    | TDK <sup>(2)</sup>          | Ceramic Capacitor, 10µF, 6.3V, X5R, 0603 size        | '    |

| C2   | GRM155R61A105KE15D | Murata <sup>(1)</sup>       | Capacitor, 1µF, 10V, X5R, 0402 size                  | 1    |

| C2   | C1005X5R0J105KT    | TDK <sup>(2)</sup>          | Capacitor, 1µF, 10V, X5R, 0402 size                  | '    |

| C3   | 06035D104MAT2A     | AVX <sup>(3)</sup>          | Ceramic Capacitor, 0.1µF, 50V, X5R, 0603 size        | 1    |

| R1   | CRCW06031001FRT1   | Vishay Dale <sup>(4)</sup>  | Resistor, 1k (0603 size), 1%                         | 1    |

| R2   | CRCW06036650FRT1   | Vishay Dale <sup>(4)</sup>  | Resistor, 665 (0603 size), 1%                        | 1    |

| R3   | CRCW06031002FRT1   | Vishay Dale <sup>(4)</sup>  | Resistor, 10k (0603 size), 1%                        | 1    |

| U1   | MIC47050YML        | Micrel, Inc. <sup>(5)</sup> | Low Input and Output 500mA ULDO™ - Adjustable Output | 1    |

| 01   | MIC47050-1.2YML    | wiiciei, ilic.              | Low Input and Output 500mA ULDO™ - Fixed 1.2V Output | ı    |

#### Notes:

1. Murata: www.murata.com.

2. TDK: www.tdk.com.

3. AVX: www.avx.com.

4. Vishay: www.vishay.com.

5. Micrel, Inc.: www.micrel.com.

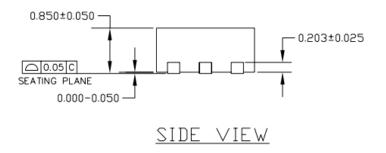

## **Package Information**

NOTE:

- ALL DIMENSIONS ARE IN MILLIMETERS.

- MAX. PACKAGE WARPAGE IS 0.05 mm.

MAXIMUM ALLOWABE BURRS IS 0.076 mm IN ALL DIRECTIONS.

PIN #1 ID ON TOP WILL BE LASER MARKED.

6-pin 2mm x 2mm MLF® (ML)

## MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB http://www.micrel.com

The information furnished by Micrel in this data sheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use. Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2010 Micrel, Incorporated.

March 2010 M9999-032310-A 14