THE INFINITE POWER OF INNOVATION

# **RangeMAX**<sup>TM</sup>

LX1686

## DIGITAL DIMMING CCFL CONTROLLER IC

PRELIMINARY DATA SHEET

#### **DESCRIPTION**

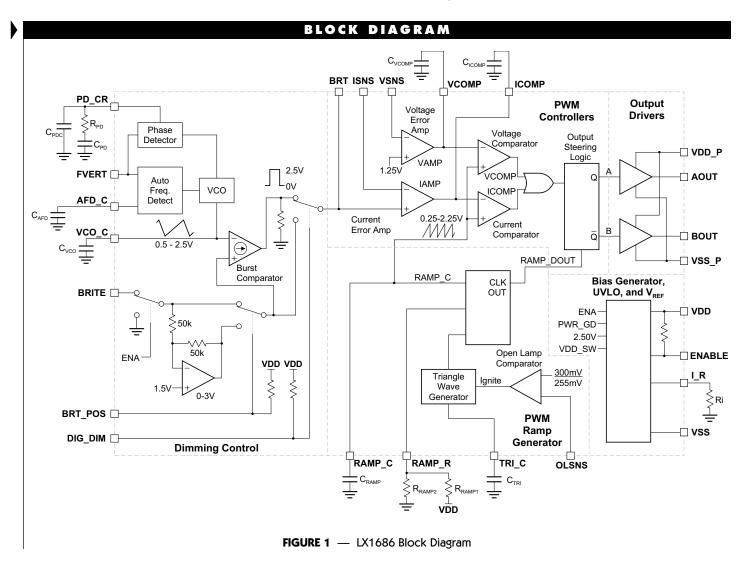

The LX1686 Backlight Controller IC provides all the control functions needed to implement Linfinity's direct drive inverters used to operate cold cathode fluorescent lamps (CCFL's). This IC can be used to control single or multiple-lamp configurations. CCFL's are used for back or edge lighting of liquid crystal flat panel displays (LCD's) and typically find application in notebook computers, web browsers, automotive and industrial instrumentation, and entertainment systems.

The LX1686 includes a PWM controlled lamp current burst circuit that can provide a >100:1 dimming range from a simple zero to 2.5V potentiometer input. The PWM dimming burst rate is easily synchronized to the LCD panel's frame rate to prevent interference from optical beat frequencies.

Safety and reliability features include a new dual feedback contol loop that permits regulation of maximum lamp strike voltage as well as lamp current. Regulating maximum lamp voltage permits the designer to provide for ample worst case lamp strike voltage while at the same time conservatively limit maximum open circuit voltage.

An innovative new strike voltage generation technique enables the module designer to optimize high voltage transformer design for maximum operating efficiency with no power dissipating overhead to guarantee strike capability.

Direct drive topology is a non-resonant, oscillator-controlled PWM regulation method. The LX1686 allows a wide choice of fixed operating frequencies to match lamp current frequency to the lamp's most efficient operating point, and to minimize high frequency interference

#### KEY FEATURES

- RangeMAX<sup>TM</sup> Wide Range Dimming (>100:1)

- Synchronizable To Display Video Frequency

- High Voltage Feedback Loop Directly Controls Maximum Open Lamp And Minimum Strike Voltages

- Transformer Protected From Over-Heating During Lamp Striking

- Micro-Amp Sleep Mode

- User-Programmable Fixed Frequency Operation

- Under-Voltage Lockout Feature With Power-Up Reset

- Built-In Soft-Start Feature

- Operates With 3.3V or 5V Power Supplies

- 100mA Output Drive Capability

#### **APPLICATIONS**

- Notebooks

- Instrumentation Displays

- Desktop Computer Monitors

- Low Ambient Light Displays (used in Aircraft, Automobiles, and Hand-held Equipment)

#### BENEFITS

- Externely High Efficiency From 3.3V or 5V Power Supplies

- Lower Cost Than Conventional Buck / Royer Inverter Topologies

- Improved Lamp Strike Capability

- Improved Over-Voltage Control

# **NOTE:** For current data & package dimensions, visit our web site: <a href="http://www.linfinity.com">http://www.linfinity.com</a>.

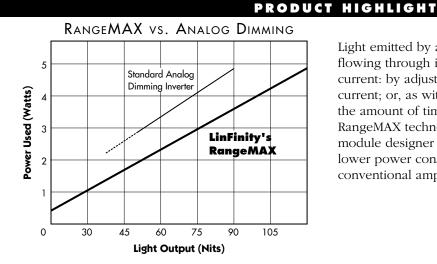

Light emitted by a CCFL is proportional to the current flowing through it. There are two ways to control the current: by adjusting the amplitude of a continuous AC current; or, as with RangeMAX technology, by varying the amount of time a burst of full current is present. RangeMAX technology frees the backlight inverter module designer to operate in a lower brightness and lower power consumption mode than is possible with conventional amplitude control methods.

PACKAGE ORDER INFO

T<sub>A</sub> (°C)

PW

Plastic TSSOP 24-pin

0 to 85

LX1686CPW

Note: All surface-mount packages are available in Tape & Reel. Append the letter "T" to part number. (i.e. LX1686CPWT)

LINFINITY MICROELECTRONICS INC.

## DIGITAL DIMMING CCFL CONTROLLER IC

## PRELIMINARY DATA SHEET

| ABSOLUTE MAXIMUM RATINGS                                                                                              | (Note 1)        |

|-----------------------------------------------------------------------------------------------------------------------|-----------------|

| Supply Voltage (VDD, VDD, D)                                                                                          | 6 EV            |

| Supply Voltage (VDD, VDD_P)                                                                                           | 0.5 v           |

| Digital Inputs                                                                                                        |                 |

| Analog Inputs                                                                                                         | 0.3 to VDD+0.5V |

| Digital Outputs                                                                                                       | 0.3 to VDD+0.5V |

| Analog Outputs                                                                                                        | 0.3 to VDD+0.5V |

| Operating Junction Temperature                                                                                        |                 |

| Plastic (DB, PW Packages)                                                                                             | 150°C           |

| Storage Temperature Range                                                                                             | 65°C to 150°C   |

| Lead Temperature (Soldering, 10 seconds)                                                                              | 300°C           |

| Note 1. Exceeding these ratings could cause damage to the dev respect to Ground. Currents are positive into, negative | U               |

#### **PACKAGE PIN OUTS** AOUT \_\_\_ 24 BOUT VSS\_P \_\_\_ 23 **VDD\_P** vss 🖂 AFD\_C \_\_\_\_ RAMP\_C \_\_\_\_\_5 20 OLSNS 19 ISNS RAMP\_R $\Box$ FVERT \_\_\_\_ 18 COMP 17 **VSNS** PD\_CR 🖂 vco\_c □□ 16 VCOMP 15 BRT 14 I\_R BRT\_POS === BRITE 🗆 DIG\_DIM 12 13 ENABLE PW PACKAGE (Top View)

#### THERMAL DATA

#### **PW PACKAGE:**

THERMAL RESISTANCE-JUNCTION TO AMBIENT,  $\theta_{LA}$

100°C/W

Junction Temperature Calculation:  $T_J = T_A + (P_D \times \theta_{JA})$ .

The  $\theta_{JA}$  numbers are guidelines for the thermal performance of the device/pc-board system. All of the above assume no ambient airflow.

#### **ELECTRICAL CHARACTERISTICS**

(Unless otherwise specified, these specifications apply over the recommended operating conditions of  $T_A$  = 0 to 85°C, VDD=VDD\_P= 3.0 to 5.5V) (Ri =  $40k\Omega$ ,  $C_{VCO}$  =  $0.01\mu$ F,  $C_{AED}$  =  $0.22\mu$ F,  $C_{TRI}$  =  $0.83\mu$ F,  $C_{RAMP}$  = 208pF,  $R_{RAMP}$  =  $15k\Omega$ ,  $C_{PD}$  =  $0.22\mu$ F,  $C_{PDC}$  =  $0.047\mu$ F,  $R_{PD}$  =  $110k\Omega$ .)

| Parameter                                               |                                            | Test Conditions                                    | LX1686 |       |      | Units |

|---------------------------------------------------------|--------------------------------------------|----------------------------------------------------|--------|-------|------|-------|

|                                                         |                                            | rest conditions                                    | Min.   | Тур.  | Max. | Units |

| Power Supply Voltage                                    |                                            | VDD = VDD_P                                        | 3      |       | 5.5  | ٧     |

| Operating Current                                       | I <sub>DD</sub>                            | VDD = VDD_P = 5V                                   |        | 5     | 7    | mA    |

| Power Supply Voltage                                    | VDD_P                                      | VDD = VDD_P                                        | 3      |       | 5.5  | ٧     |

| Output Buffer Operating Current                         | I <sub>DD_P</sub>                          | Volsns = $VDD = VDD_P = 5V$ , $C_A = C_B = 1000pF$ |        | 2     | 10   | mA    |

| UVLO Threshold                                          | $V_{\text{TH\_UVLO}}$                      |                                                    | 2.7    |       | 2.9  | ٧     |

| UVLO Hysteresis                                         | V <sub>H_UVLO</sub>                        |                                                    |        | 160   |      | m۷    |

| Direct Drive Ramp Block                                 |                                            |                                                    |        |       |      |       |

| Triangular Wave Generator Analog Output Peak Voltage    |                                            |                                                    |        | 2.25  |      | ٧     |

| Triangular Wave Generator Analog Output Valley Voltage  | $V_{v\_TRI}$                               |                                                    |        | 0.75  |      | ٧     |

| Triangular Wave Generator Oscillation Frequency         |                                            |                                                    |        | 10    |      | Hz    |

| Triangular Wave Generator Oscillation Charge Current    |                                            | Tri_c = 0V                                         | -2.3   | -2.55 | -2.9 | μΑ    |

| Triangular Wave Generator Oscillation Discharge Current |                                            | Tri_c = 3V                                         | 2.3    | 2.65  | 2.9  | μA    |

| Ramp Generator Analog Output Peak Voltage               |                                            |                                                    |        | 2.25  |      | ٧     |

| Ramp Generator Analog Output Valley Voltage             |                                            |                                                    |        | 0.75  |      | ٧     |

| Ramp Frequency Change Threshold                         | V <sub>V_RAMP</sub> V <sub>TH_RAMP_R</sub> | VDD = 3V                                           | 1.4    | 1.5   | 1.65 | ٧     |

|                                                         |                                            | VDD = 5.5V                                         | 1.55   | 1.65  | 1.8  | ٧     |

| Ramp Generator Oscillation Frequency - Nominal          | F <sub>RAMP</sub>                          | $V_{TRI\_C} = 1.4V$                                | 84     | 100   | 116  | KHz   |

| Ramp Generator Oscillation Frequency - Maximum          |                                            | $V_{TRI\_C} = 2.25V$                               | 170    | 200   | 256  | KHz   |

| OLSNS Threshold Voltage                                 |                                            | VDD = 3V                                           | 250    | 300   | 360  | m۷    |

| OLSNS Hysteresis                                        | V <sub>H_OLSNS</sub>                       | VDD = 3V                                           |        | 45    |      | m۷    |

| OLSNS-to-ICOMP Propagation Delay                        | T <sub>D_OLSNS</sub>                       | GBD                                                |        | 1     |      | μS    |

# **RangeMAX**<sup>TM</sup>

# DIGITAL DIMMING CCFL CONTROLLER IC

## PRELIMINARY DATA SHEET

|                                                                 | NICAL CHA                | RACTERISTICS (continued)                      |       |        |      |        |

|-----------------------------------------------------------------|--------------------------|-----------------------------------------------|-------|--------|------|--------|

| Parameter                                                       | Symbol                   | Test Conditions                               |       | LX1686 |      | Units  |

|                                                                 | 3,111001                 | rest conditions                               | Min.  | Тур.   | Max. |        |

| Digital Dimmer Block                                            |                          | I                                             | 1     |        |      | T      |

| FVERT Input Frequency Capture Range                             | F <sub>R_FVERT</sub>     |                                               | 40    | 10000  | 200  | Hz     |

| FVERT Logic Threshold                                           | V <sub>TH_FVERT</sub>    | Design Reference Only                         |       | VDD/2  |      | ٧      |

| FVERT Input Resistance                                          | R <sub>FVERT</sub>       | Design Reference Only                         |       | 50     |      | kΩ     |

| VCO Analog Output Peak Voltage                                  | V <sub>P_VCO</sub>       |                                               |       | 2.5    |      | ٧      |

| VCO Analog Output Valley Voltage                                | V <sub>v_vco</sub>       |                                               |       | 0.65   |      | ٧      |

| VCO Forced Source Current                                       | F <sub>R_VCO_I_SRC</sub> |                                               | -6.4  | -5.8   | -5.2 | μA     |

| Forced VCO Oscillation Frequency                                | F <sub>X_VCO</sub>       | AFC_C = 0V, $C_{VCO} = 0.01 \mu F$            |       | 250    |      | Hz     |

| Auto-Frequency Detection Response                               | T <sub>D_AFD</sub>       | FVERT Frequency is 200Hz, VDD = 3V            |       | 1000   |      | ms     |

| BRITE Voltage Range                                             | V <sub>R_BRITE</sub>     |                                               | 0     |        | VDD  | ٧      |

| Full-Brightness Brite Input Voltage                             | V <sub>BRITE_FULL</sub>  | $V_{BRT\_POS} = VDD$ or float; $BRITE = 2.5V$ | 2.35  | 2.5    | 2.65 | ٧      |

|                                                                 |                          | $V_{BRT\_POS} = OV$ , $BRITE = 0.5V$          | 2.35  | 2.5    | 2.65 | ٧      |

| Full-Darkness Brite Input Voltage                               | V <sub>BRITE_DARK</sub>  | $V_{BRT\_POS} = VDD$ or float BRITE = 0.5V    | 0.35  | 0.5    | 0.65 | ٧      |

|                                                                 |                          | $V_{BRT\_POS} = OV$ , $BRITE = 2.5V$          | 0.35  | 0.5    | 0.65 | ٧      |

| BRITE-to-ICOMP Propagation Delay                                | T <sub>D_BRITE</sub>     |                                               |       | 300    |      | ns     |

| BRITE_POS Logic Threshold                                       |                          |                                               |       | VDD/2  |      | ٧      |

| DIG_DIM Logic Threshold                                         |                          |                                               |       | VDD/2  |      | ٧      |

| Direct Drive PWM Block                                          |                          |                                               |       |        |      |        |

| ISNS Threshold Voltage Range                                    | $V_{R\_ISNS}$            | DIG_DIM = VDD                                 | 0     |        | 2.5  | ٧      |

| VAMP Transconductance                                           | G <sub>M_VAMP</sub>      | VCOMP = 1.25V                                 |       | 400    |      | μmh    |

| VAMP Output Source Current                                      | I <sub>S_VAMP</sub>      | VCOMP = 1.5V                                  | 10    | 50     | 110  | μΑ     |

| VAMP Output Sink Current                                        | I <sub>SK_VAMP</sub>     | VCOMP = 1.5V                                  | 20    | 70     | 120  | μA     |

| VAMP Output Voltage Range                                       | $V_{R_{-}VAMP}$          |                                               | 0     |        | VDD  | ٧      |

| VSNS Threshold Voltage                                          | V <sub>TH_VSNS</sub>     | VCOMP = VSNS                                  | 1.12  | 1.25   | 1.38 | ٧      |

| VCOMP Discharge Current                                         | I <sub>D_VCOMP</sub>     | VCOMP = 0.5V, VDD = 3V                        | 0.8   | 1.5    | 10   | mA     |

| IAMP Transconductance                                           | G <sub>M_IAMP</sub>      | BRITE = 0.5 - 2.6V                            | 70    | 200    | 700  | μmh    |

| IAMP Output Source Current                                      | I <sub>S_IAMP</sub>      | ICOMP = 1.5V, VDD = 3V                        | -15   | -40    | -80  | μA     |

| IAMP Output Sink Current                                        | I <sub>SK_IAMP</sub>     | ICOMP = 1.5V, VDD = 3V                        | 20    | 60     | 100  | μA     |

| IAMP Output Voltage Range                                       | V <sub>R_IAMP</sub>      |                                               | 0     |        | VDD  | ٧      |

| IAMP Input Offset Voltage                                       | T <sub>SS</sub>          | $C_{VCOMP} = 1\mu F$                          |       | 40     |      | ms     |

| VCMP Input Offset Voltage                                       | V <sub>OS_VCMP</sub>     | VCOMP = 1.25V, VDD = 3V                       | -10   | 3      | 10   | m۷     |

| VCOMP-to-Output Propagation Delay                               | T <sub>D_VCOMP</sub>     | VDD = 3V                                      |       | 250    | 500  | ns     |

| ICMP Input Offset Voltage                                       | V <sub>OS_ICMP</sub>     | ICOMP = 0.5 to 2.25V, VDD = 3V                | -10   | 3      | 10   | m۷     |

| ICOMP-to-Output Propagation Delay                               | T <sub>D_ICOMP</sub>     | BRITE = 1.25V, RAMP_C = 2V, VDD = 3V          |       | 1100   |      | ns     |

| Output Buffer Block                                             | - D_ICOMF                | 1                                             |       |        | l    |        |

| Output Sink Current                                             | 1                        | AOUT, BOUT = VDD = 3V                         | 25    | 45     | 80   | m/     |

| Output Sink Current                                             | I <sub>SK_OUTBUF</sub>   | AOUT, BOUT = 1V, VDD = 3V                     | 20    | 35     | 55   | m/     |

| Output Source Current                                           | 1                        | AOUT, BOUT = 0V, VDD = 3V                     | -35   | -50    | -80  | m/     |

| Output source current                                           | I <sub>S_OUTBUF</sub>    | AOUT, BOUT = 2V, VDD = 3V                     | -20   | -40    | -55  | m/     |

| Bias Control Block                                              | I                        | 1 AOO1, BOO1 - 21, 100 = 31                   | 1 -20 | -40    | -33  | 1 111/ |

| Voltage at Pin I_R                                              | V <sub>IR</sub>          |                                               | 0.98  |        | 1.02 | Ιv     |

| Pin I_R Maximum Source Current                                  | I <sub>MAX_IR</sub>      | Design Reference Only                         | 0.70  | 50     | 1.02 | μA     |

| VBG Output Resistance                                           |                          | Design Reference Only                         | +     | 10     |      | kΩ     |

| ENABLE Logic Threshold - 3V                                     | R <sub>O_VBG</sub>       | VDD = 3V                                      | 1.5   | 1.9    | 2.4  | V      |

| ENABLE Logic Threshold - 5.5V                                   | V <sub>EN3V</sub>        | VDD = 3V<br>VDD = 5.5V                        | 2.7   | 3.2    | 3.6  | V      |

| ENABLE Logic Inresnoid - 5.5V  ENABLE Threshold Hysteresis - 3V | V <sub>EN5.5</sub>       | אכ.כ = טעץ = 3.3ץ                             | 2.1   |        | 3.0  | l v    |

| ENABLE THRESHOLD MYSLERESIS - 3V                                | V <sub>H_EN3</sub>       | I .                                           | 1     | 0.45   | I    | ı v    |

# DIGITAL DIMMING CCFL CONTROLLER IC

## PRELIMINARY DATA SHEET

| FUNCTIONAL PIN DESCRIPTION |                   |                                                                                                                                                                                                                          |  |  |

|----------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin<br>Number              | Pin<br>Designator | Description                                                                                                                                                                                                              |  |  |

| 1                          | AOUT              | Output driver A.                                                                                                                                                                                                         |  |  |

| 2                          | VSS_P             | Power ground for output drivers only.                                                                                                                                                                                    |  |  |

| 3                          | VSS               | Signal ground.                                                                                                                                                                                                           |  |  |

| 4                          | AFD_C             | Connects to an external cap, C <sub>AFD</sub> . Forcing to ground or VDD will make the VCO oscillate at approxi 50% of the maximum VCO frequency. Forcing to VDD/2 will make the VCO oscillate at 2x the FVER frequency. |  |  |

| 5                          | RAMP_C            | Connects to external capacitor C <sub>RAMP</sub> for setting Direct Drive PWM operating frequency.                                                                                                                       |  |  |

| 6                          | RAMP_R            | Connects to external resistor R <sub>RAMP</sub> for setting Direct Drive PWM operating frequency.                                                                                                                        |  |  |

| 7                          | FVERT             | Vertical frequency reference digital input. Has internal pull down.                                                                                                                                                      |  |  |

| 8                          | PD_CR             | Phase Detector Filter. Part of phase lock loop. Connects to external capacitor and resistor network.                                                                                                                     |  |  |

| 9                          | VCO_C             | Connects to external capacitor $C_{VCO}$ .                                                                                                                                                                               |  |  |

| 10                         | BRT_POS           | Brightness control polarity. Has internal pullup. Leave open or pull up to VDD for dimming brightness proportional to BRITE voltage, connec to ground for brightness inversely proportional to BRITE voltage.            |  |  |

| 11                         | BRITE             | Analog voltage input for brightness control.                                                                                                                                                                             |  |  |

| 12                         | DIG_DIM           | Digital Dimming Enable internal pullup. Leave open or pull up to VDD for operating in digital dimming mode. Connect to ground for analog dimming mode.                                                                   |  |  |

| 13                         | ENABLE            | Chip Enable internal pullup. High enables the chip. Low disables.                                                                                                                                                        |  |  |

| 14                         | I_R               | Current Reference Resistor. External resistor to ground (Ri) determines internal capacitor $C_{\text{ICOMP}}$ .                                                                                                          |  |  |

| 15                         | BRT               | Current Error Amplifier non-inverting input.                                                                                                                                                                             |  |  |

| 16                         | VCOMP             | Voltage Error Amplifier output. Connects to external frequency compensation capacitor C <sub>VCOMP</sub> . Controls soft-start timing.                                                                                   |  |  |

| 17                         | VSNS              | Voltage Error Amplifier inverting input.                                                                                                                                                                                 |  |  |

| 18                         | ICOMP             | Current Error Amplifier output. Connects to external frequency compensation capacitor CICOMP.                                                                                                                            |  |  |

| 19                         | ISNS              | Current Error Amplifier inverting input.                                                                                                                                                                                 |  |  |

| 20                         | OLSNS             | Open Lamp Sense Input.                                                                                                                                                                                                   |  |  |

| 21                         | TRI_C             | Connects to external capacitor $C_{TRI}$ for setting strike frequency ramp slope.                                                                                                                                        |  |  |

| 22                         | VDD               | VDD                                                                                                                                                                                                                      |  |  |

| 23                         | VDD_P             | Dedicated VDD for output buffers only.                                                                                                                                                                                   |  |  |

| 24                         | BOUT              | Output driver B.                                                                                                                                                                                                         |  |  |

RangeMAX<sup>™</sup> LX1686

# DIGITAL DIMMING CCFL CONTROLLER IC

### PRELIMINARY DATA SHEET

RangeMAX and is a trademark of Linfinity Microelectronics Inc.

PRELIMINARY DATA - Information contained in this document is pre-production data, and is proprietary to LinFinity. It may not modified in any way without the express written consent of LinFinity. Product referred to herein is offered in sample form only, and Linfinity reserves the right to change or discontinue this proposed product at any time.