# Advance Information Three Channel Linear LED Driver

The NUD4330 device is an integrated LED driver designed to replace discrete solutions for driving multiple LED arrays in DC high voltage applications (up to 200 V).

It contains three independent channels capable to drive three independent LED arrays of up to 100 mA. The LED current setting for each of the channels is made through an external low power resistor.

It also has three enable pins that control each of the channels independently for PWM or on/off purposes.

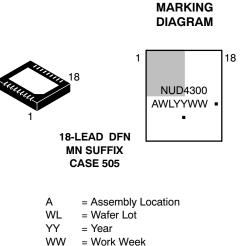

The device is packaged in a space saving 18 pins 6x5 mm DFN package.

## Features

- Independent PWM (On/Off) Control for Each of the Channels

- Internal Thermal Protection

- Independent LED current setting up to 100 mA for each channel

- Settable Low Quiescent Current Circuit for Battery Based Applications

- This is a Pb-Free Device

### **Typical Applications**

- LED General Lighting

- LED Backlighting

# **ON Semiconductor®**

http://onsemi.com

- E = Automotive Grade

- = Pb-Free Package

(Note: Microdot may be in either location)

#### **ORDERING INFORMATION**

| Device       | Package            | Shipping <sup>†</sup> |

|--------------|--------------------|-----------------------|

| NUD4330MNTXG | DFN18<br>(Pb-Free) | 2500 / Tape &<br>Reel |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

This document contains information on a new product. Specifications and information herein are subject to change without notice.

© Semiconductor Components Industries, LLC, 2007 August, 2007 - Rev. P0

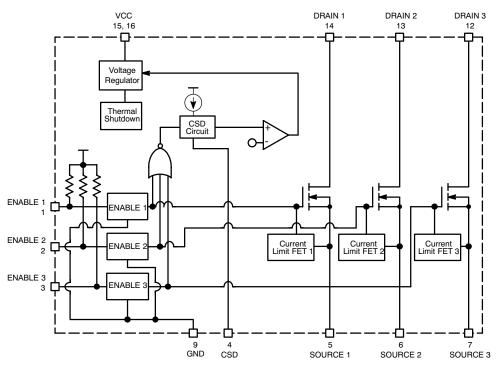

Figure 1. Block Diagram

| Pin               | Function | Description                                                                                                                                                                                               |

|-------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                 | Enable 1 | This pin is used for enable or PWM dimming control of channel 1. A positive voltage signal at this pin enables channel 1. A PWM signal with greater amplitude than 2.2 V is required for dimming control. |

| 2                 | Enable 2 | This pin is used for enable or PWM dimming control of channel 2. A positive voltage signal at this pin enables channel 2. A PWM signal with greater amplitude than 2.2 V is required for dimming control. |

| 3                 | Enable 3 | This pin is used for enable or PWM dimming control of channel 3. A positive voltage signal at this pin enables channel 3. A PWM signal with greater amplitude than 2.2 V is required for dimming control. |

| 4                 | CSD      | This pin is the circuit shutdown delay and can be used to set the non-operational IBias to a low value. See applications info for more details about this circuit.                                        |

| 5                 | Source 1 | Source terminal of the FET 1. A resistor from this pin to ground is used to set the ILimit for channel 1.                                                                                                 |

| 6                 | Source 2 | Source terminal of the FET 2. A resistor from this pin to ground is used to set the ILimit for channel 2.                                                                                                 |

| 7                 | Source 3 | Source terminal of the FET 3. A resistor from this pin to ground is used to set the ILimit for channel 3.                                                                                                 |

| 8,10,11<br>17, 18 | N/C      | No Connection                                                                                                                                                                                             |

| 9                 | GND      | The ground reference to the device.                                                                                                                                                                       |

| 12                | Drain 3  | Drain terminal of the FET 3, which is also the switching node of the load 3.                                                                                                                              |

| 13                | Drain 2  | Drain terminal of the FET 2, which is also the switching node of the load 2.                                                                                                                              |

| 14                | Drain 1  | Drain terminal of the FET 1, which is also the switching node of the load 1.                                                                                                                              |

| 15,16             | VCC      | Input voltage to the LED driver. This voltage can be between 20 V and 80 V dc.                                                                                                                            |

| 19                |          | This pin is the center flag of the package. Although it does not have direct contact with the ground potential, it is still recommended to ground it.                                                     |

Table 2. MAXIMUM RATINGS (Maximum ratings are those, that, if exceeded, may cause damage to the device. Electrical

Characteristics are not guaranteed over this range)

| Rating                                                                                            | Symbol              | Value       | Unit |

|---------------------------------------------------------------------------------------------------|---------------------|-------------|------|

| Control Circuitry Input Voltage, Operating (V <sub>CC</sub> to Ground)                            | V <sub>CC</sub>     | 20 to 80    | V    |

| Drain Voltage, Operating (Drain to Ground)<br>Steady-State<br>Transient (1 ms)                    | V <sub>DD</sub>     | 200<br>220  | V    |

| Maximum Enable Voltage, Operating                                                                 | V <sub>EN</sub>     | 12          | V    |

| Maximum Voltage at CSD pin                                                                        | V <sub>CSD</sub>    | 10          | V    |

| Drain Current, Peak                                                                               | I <sub>Dpk</sub>    | 200         | mA   |

| Drain Current, Continuous                                                                         | I <sub>D(avg)</sub> | 100         | mA   |

| Human Body Model (HBM)<br>Machine Model (MM)<br>According to EIA/JESD22/A114, A115 Specifications | ESD                 | 2000<br>200 | V    |

## Table 3. THERMAL CHARACTERISTICS

| Rating                                                                                                                                                   | Symbol           | Value        | Unit         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------|--------------|

| Operating Temperature Range                                                                                                                              | TJ               | -40 to 125   | °C           |

| Non-Operating Temperature Range                                                                                                                          | TJ               | -55 to 150   | °C           |

| Lead Temperature, Soldering (1/8 in from case for 10 sec)                                                                                                | ΤL               | 260          | °C           |

| Thermal Resistance, Junction-to-Air<br>Mounted onto the Minimum Recommended Pad<br>Mounted onto FR-4 Board, 1.0 in <sup>2</sup> Pad, 1 oz Coverage       | Q <sub>JA</sub>  | 240<br>65    | °C/W<br>°C/W |

| Thermal Resistance, Junction-to-Lead                                                                                                                     | Q <sub>JL</sub>  | 12           | °C/W         |

| Power Dissipation (T <sub>A</sub> = 25°C)<br>Mounted onto the Minimum Recommended Pad<br>Mounted onto FR-4 Board, 1.0 in <sup>2</sup> Pad, 1 oz Coverage | P <sub>max</sub> | 0.52<br>1.92 | W            |

| Table 4. ELECTRICAL CHARACTERISTICS (Unless otherwise noted: $T_A = 25^{\circ}C$ , Rsense = 16.5 $\Omega$ 1 |

|-------------------------------------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------------------------------|

| Characteristics                                                                                                                                                                                                                           |                                      | Min  | Тур        | Max  | Uni |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------|------------|------|-----|

| POWER FET (Each Channel)                                                                                                                                                                                                                  | -                                    |      | -          | -    | -   |

| ON Resistance (V <sub>CC</sub> = 24V, I <sub>D</sub> = 20 mA, R <sub>sense</sub> = 16.5 $\Omega$ , Enable = 3.3 V)                                                                                                                        | R <sub>DS(ON)</sub>                  | -    | 20         | -    | Ω   |

| Zero Enable Voltage Drain Current<br>(V <sub>DD</sub> = 200 V, Enable Low)                                                                                                                                                                | I <sub>DSS</sub>                     | -    | -          | 10   | μA  |

| Drain-to-Source Sustaining Voltage $(I_D = 1 \text{ mA})$                                                                                                                                                                                 | V <sub>(BR)</sub>                    | 200  | -          | -    | V   |

| Output Capacitance<br>(V <sub>DD</sub> = 40 V, Enable Low, f = 1 kHz)                                                                                                                                                                     |                                      | -    | 330        | -    | pF  |

| Voltage drop (Notes 1 and 2)<br>(I <sub>D</sub> = 30 mA, R <sub>sense</sub> = 16.5 $\Omega$ , Enable = 3.3 V)                                                                                                                             | V <sub>drop</sub>                    | -    | -          | 1.5  | V   |

| CURRENT REGULATION CIRCUIT (Each Channel)                                                                                                                                                                                                 | •                                    |      |            |      |     |

| Line LED Current Regulation, ( $T_J$ = -20°C to 85°C)<br>( $V_{in}$ = 0.8 $V_{DD}$ to $V_{DD}max$ ; $V_{CC}$ = 24 V; $R_{sense}$ = 16.5 $\Omega$ ,<br>$V_{LEDs}$ = 0.8 $V_{DD}$ - 2 V ; Enable = 3.3 V)                                   | l <sub>out1</sub>                    | 28.5 | 30         | 31.5 | mA  |

| Load LED Current Regulation, ( $T_J$ = -20 to 85°C)<br>( $V_{in}$ = rated $V_{DD}$ , $V_{CC}$ = 24 V, $V_{LEDs}$ = 0.8 $V_{in}$ to ( $V_{in}$ - 2 V),<br>$R_{sense}$ =16.5 $\Omega$ ; Enable = 3.3 V)                                     | I <sub>out2</sub>                    | 28.5 | 30         | 31.5 | mA  |

| THERMAL LIMIT                                                                                                                                                                                                                             |                                      |      |            |      |     |

| Shutdown Junction Temperature (Notes 3 and 4)                                                                                                                                                                                             | T <sub>SD</sub>                      | 140  | 150        | 160  | °C  |

| Hysteresis (Note 4)                                                                                                                                                                                                                       |                                      | -    | 10         | -    | °C  |

| ENABLE CIRCUIT (Each Channel)                                                                                                                                                                                                             |                                      |      |            |      |     |

| Logic Level High (Unit Operational)                                                                                                                                                                                                       | V <sub>ENhigh</sub>                  | 2.2  | -          | -    | V   |

| Logic Level Low (Unit Shutdown)                                                                                                                                                                                                           | V <sub>ENlow</sub>                   | -    | -          | 1.6  | V   |

| PWM Frequency                                                                                                                                                                                                                             | f <sub>PWM</sub>                     | 100  | -          | 1000 | Hz  |

| Internal Pullup Resistor<br>(Connected to an Internal 9 V Source)                                                                                                                                                                         | R <sub>pullup</sub>                  | -    | 600        | -    | kΩ  |

| CSD CIRCUIT                                                                                                                                                                                                                               |                                      |      |            |      |     |

| Charging Current (Into External Capacitor)<br>(V <sub>CC</sub> = 24 V, CSD Pin Grounded)                                                                                                                                                  | I <sub>Charge</sub>                  | 9.0  | 10         | 11   | μA  |

| Maximum Capacitor Voltage                                                                                                                                                                                                                 | V <sub>Cmax</sub>                    | -    | -          | 10   | V   |

| TOTAL DEVICE                                                                                                                                                                                                                              |                                      |      |            |      |     |

| Bias Current, Operational<br>(All Enables = 3.3 V, V <sub>CC</sub> = 40 V)                                                                                                                                                                | I <sub>BIAS1</sub>                   | -    | 1          | 2.5  | mA  |

| Bias Current, Non-Operational<br>(All Enables Low, CSD Pin Open, V <sub>CC</sub> = 40 V)                                                                                                                                                  | I <sub>BIAS2</sub>                   | -    | 100        | 200  | μA  |

| Bias Current, Non-Operational<br>(All Enables Low, CSD Pin Grounded, V <sub>CC</sub> = 40 V)                                                                                                                                              | I <sub>BIAS3</sub>                   | -    | 600        | 800  | μA  |

| Minimum Operating Voltage                                                                                                                                                                                                                 |                                      | 20   | -          | -    | V   |

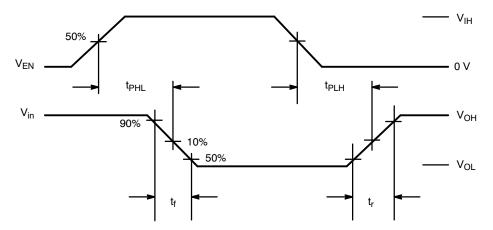

| SWITCHING CHARACTERISTICS                                                                                                                                                                                                                 |                                      |      |            |      |     |

| Propagation Delay Times<br>(V <sub>EN</sub> = 3.3V, V <sub>CC</sub> = 24V, V <sub>in</sub> = 60 V, R <sub>L</sub> = 1.5 kΩ, R <sub>sense</sub> = 10 Ω, CSD Pin Shorted)<br>High to Low Propagation Delay<br>Low to High Propagation Delay | t <sub>PHL</sub><br>t <sub>PLH</sub> | -    | 2960<br>96 | -    | ns  |

| Transition Times<br>( $V_{EN} = 3.3 \text{ V}, V_{CC} = 24 \text{ V}, \text{Vin} = 60 \text{ V}, \text{R}_{L} = 1.5 \text{ k}\Omega, \text{R}_{\text{sense}} = 10 \Omega, \text{ CSD Pin Shorted}$ )<br>Rise Time;<br>Fall Time;          | tr<br>tf                             | -    | 90<br>620  | -    | ns  |

V<sub>drop</sub> = V<sub>DS</sub> + V<sub>Rsense</sub> (This is the minimum voltage needed across the device and R<sub>sense</sub> for operation)

The max voltage drop is limited by the device's power dissipation for given conditions of ambient temperature and board copper area.

The typical thermal limit is set to 150°C so that the device shuts down when its lead temperature reaches 138°C for 1.0 W of power dissipation and 12°C/W of junction-to-lead thermal resistance.

Guaranteed by design

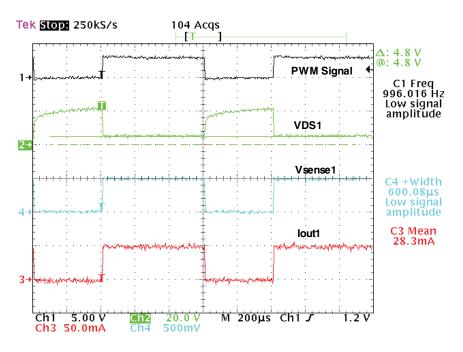

Figure 2. Switching Waveforms

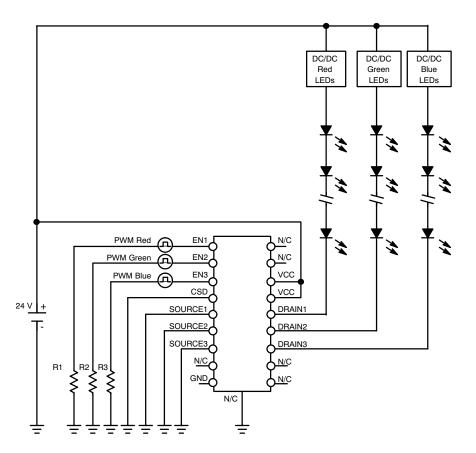

Figure 3. Typical Application Circuit

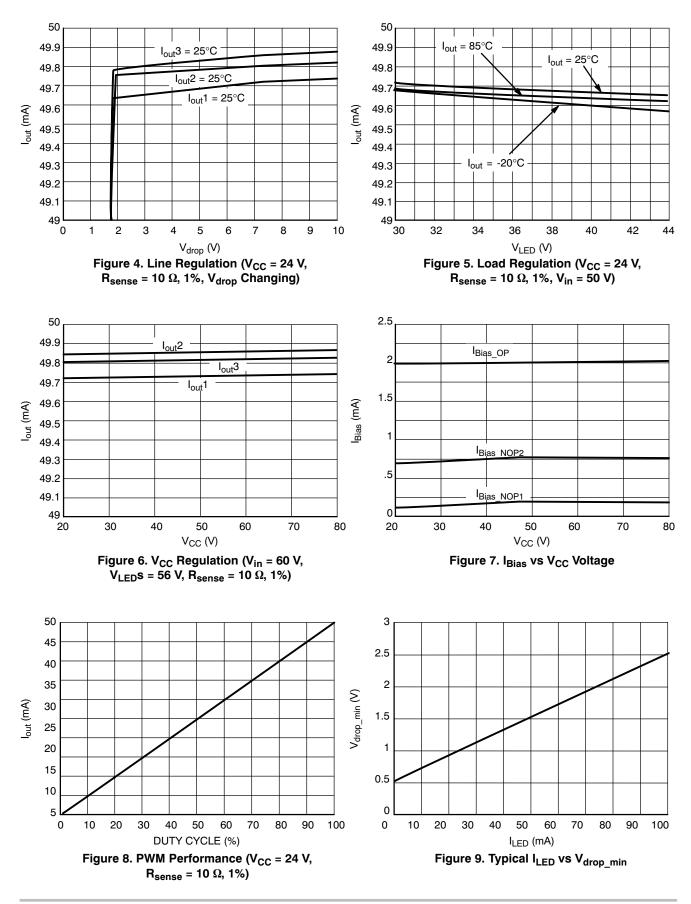

# **TYPICAL PERFORMANCE CURVES** ( $T_A = 25^{\circ}C$ unless otherwise noted)

http://onsemi.com 6

Figure 10. PWM Waveforms (V<sub>CC</sub> = 24 V,  $R_{sense}$  = 10  $\Omega$ , 1%)

## **APPLICATIONS INFORMATION**

## **Theory of Operation**

This device contains three linear LED current sources. Each channel is comprised of a FET controlled by a current limit circuit that senses the voltage drop across the Rsense resistor and compares it with an internal bandgap voltage reference (0.5 V) to provide the current regulation.

#### **Current Limit Circuit**

The current limit circuit contains a bandgap voltage reference of 0.5 V. Then the value of the sense resistor ( $R_{sense}$ ) is calculated by simply using the ohms law formula:

$$R_{sense} = \frac{0.5 \text{ V}}{I_{LED}}$$

(eq. 1)

Each of the three channels can be set independently for  $I_{\text{LED}}$  using the same formula.

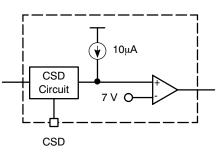

### **CSD Circuit**

The circuit shutdown delay (CSD) allows for low quiescent current when the device is in its non-operational state (all enables low). This is extremely important in particular for Li-Ion battery based applications (LapTops and portables). Figure 11 shows the equivalent circuit for CSD

Figure 11. CSD Circuit

Depending on how the CSD pin is connected, the CSD circuit can be configured for three different options:

- CSD pin open = immediate shutdown

- CSD pin grounded = No shutdown

- External capacitor = Delay before shutdown

The delay capacitor is connected between CSD pin and ground and is calculated using the following formula:

$$C_{delay} = \frac{\left(t_{delay} \times 10^{E-6} \text{ A}\right)}{7.0 \text{ V}} \tag{eq. 2}$$

Where:

T<sub>delay</sub> = Wanted delay time (seconds) C<sub>delay</sub> = Delay capacitor (Farads)

#### Thermal Shutdown

The temperature limit circuit senses the temperature of the junction and removes the gate drive of all FETs if the maximum level (150°C) is exceeded. There is a nominal hysteresis of 10°C for this circuit. After a thermal shutdown, the device will automatically restart when the temperature drops to a safe level as determined by the hysteresis.

#### **Minimum Vdrop**

There is a minimum voltage drop required to have across the drain-to-source terminals of each of the FETs and  $R_{sense}$ for operation. Since  $V_{drop} = V_{DS} + V_{Rsense}$ , the minimum  $V_{drop}$  required will change for different I<sub>LED</sub> currents according the following formula:

$$Vdrop_{min} = (I_{LED} \times R_{DS(on)}) + 0.5 V$$

(eq. 3)

This will be the minimum voltage required across the drain-to-source terminals of each of the FETs and its respective Rsense for regulation.

#### Maximum Vdrop

The maximum voltage drop in each of the channels will be limited by the device's max power dissipation. That is, the voltage drop across each of the internal FETs should be taken into account for the calculation of the device's total power dissipation. The following formula is used to calculate the device's total power dissipation:

$$P_{\text{Dtotal}} = P_{\text{Dcontrol}} + P_{\text{Dch1}} + P_{\text{Dch2}} + P_{\text{Dch3}} \qquad (\text{eq. 4})$$

$$\begin{split} \mathbf{P}_{\mathsf{Dtotal}} &= \left( \mathbf{V}_{\mathsf{CC}} * 2.5 \; \mathsf{mA} \right) + \left( \mathbf{V}_{\mathsf{DS1}} * \mathbf{I}_{\mathsf{LED1}} \right) \\ &+ \left( \mathbf{V}_{\mathsf{DS2}} * \mathbf{I}_{\mathsf{LED2}} \right) + \left( \mathbf{V}_{\mathsf{DS3}} * \mathbf{I}_{\mathsf{LED3}} \right) \end{split} \tag{eq. 5}$$

Where  $V_{DS(n)} = V_{DD(n)} - V_{LEDs(n)} - 0.5V$

The resulting total power dissipation should not exceed the PD value shown on the maximum ratings table.

#### **Power Dissipation**

Since the NUD4330 device is a linear device, power dissipation considerations should be taken into account. That is, the device's power dissipation listed on the maximum ratings table is for  $T_A = 25^{\circ}C$ . So the device's power dissipation capability will be derated for higher temperatures than 25°C. The following formula may be used for those purposes:

$$T_{J} = T_{A} + R_{\theta JA} \times P_{D}$$

(eq. 6)

### **Enable Circuit**

The enable circuit can be used to enable/disable the channels or for PWM dimming purposes. The PWM frequency is recommended to be between 100 Hz and 1 kHz. Each of the enable circuits have an internal 0.6 M $\Omega$  pullup resistor connected to an internal 9 V voltage source. So if left open, the channel will automatically be enabled.

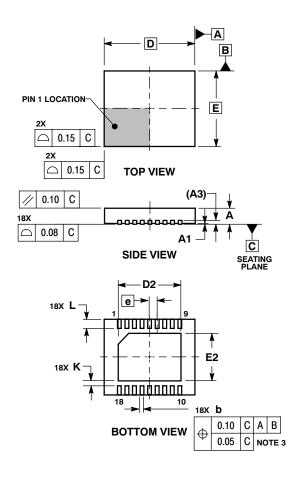

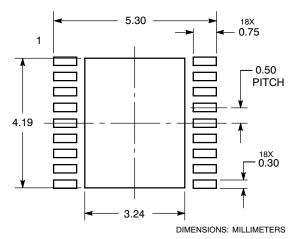

#### PACKAGE DIMENSIONS

DFN18 6x5, 0.5P CASE 505-01 ISSUE D

NOTES DIMENSIONS AND TOLERANCING PER 1.

- 2.

- 3

|     | MILLIMETERS |      |  |

|-----|-------------|------|--|

| DIM | MIN         | MAX  |  |

| Α   | 0.80        | 1.00 |  |

| A1  | 0.00        | 0.05 |  |

| A3  | 0.20 REF    |      |  |

| b   | 0.18        | 0.30 |  |

| D   | 6.00 BSC    |      |  |

| D2  | 3.98        | 4.28 |  |

| E   | 5.00 BSC    |      |  |

| E2  | 2.98        | 3.28 |  |

| е   | 0.50 BSC    |      |  |

| к   | 0.20        |      |  |

| L   | 0.45        | 0.65 |  |

#### SOLDERING FOOTPRINT\*

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and 💷 are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its peter frights or the rights of others. SCILLC products are not designed, intended, or authorized for use a components in systems intended for surgical implant into the body, or other applications Intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5773-3850

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative