TOSHIBA Bi-CMOS Integrated Circuit Silicon Monolithic

# **TB62802FG**

#### **CCD Clock Drivers**

The TB62802FG is a clock distribution driver for CCD linear image sensors.

The IC can functionally drive the CCD input capacitance. It also supports inverted outputs, eliminating the need for crosspoint control.

The IC contains a 1-to-4 clock distribution driver and 4-bit buffer.

The suffix (G) appended to the part number represents a Lead (Pb) ·Free product.

#### **Features**

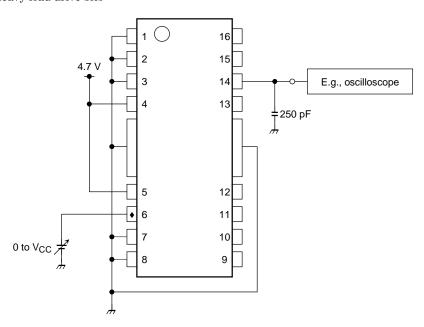

- High drivability: Guaranteed driving 250 pF load capacitance

@fclock = 25 MHz

- (4-bit distribution driver)

- Operating temperature range: Ta = 0°C to 60°C

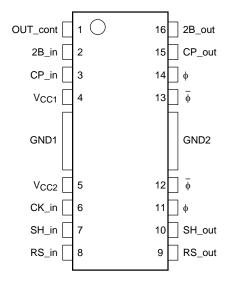

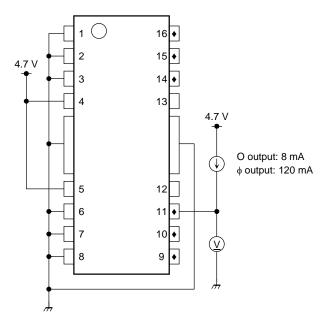

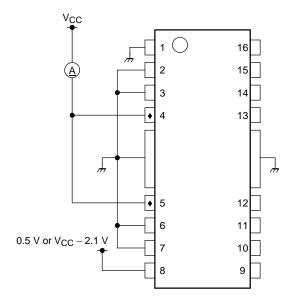

# Pin Connection (top view)

Weight: 0.5 g (typ.)

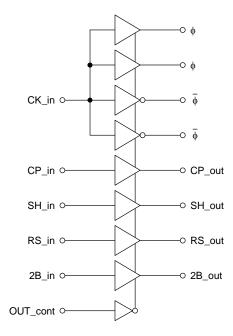

# **Logic Diagram**

# **Pin Description**

| Pin No. | Pin Name         | Functions                              | Remarks                                |

|---------|------------------|----------------------------------------|----------------------------------------|

| 1       | OUT_cont         | Output control pin                     | _                                      |

| 2       | 2B_in            | Light load drive input                 | Driver input for CCD last-stage clock  |

| 3       | CP_in            | Light load drive input                 | CCD clamp gate driver input            |

| 4       | V <sub>CC1</sub> | Light load power supply                | _                                      |

| _       | GND1             | Light load ground                      | _                                      |

| 5       | V <sub>CC2</sub> | Heavy load power supply                | _                                      |

| 6       | CK_in            | Heavy load drive input                 | Driver input for CCD transfer clock    |

| 7       | SH_in            | Light load drive input                 | CCD shift gate driver input            |

| 8       | RS_in            | Light load drive input                 | CCD reset gate driver input            |

| 9       | RS_out           | Light load drive output (not inverted) | CCD reset gate driver output           |

| 10      | SH_out           | Light load drive output (not inverted) | CCD shift gate driver output           |

| 11      | ф                | Heavy load drive output (not inverted) | Driver output for CCD transfer clock   |

| 12      | φ                | Heavy load drive output (inverted)     | Driver output for CCD transfer clock   |

| _       | GND2             | Heavy load ground                      | _                                      |

| 13      | φ                | Heavy load drive output (inverted)     | Driver output for CCD transfer clock   |

| 14      | ф                | Heavy load drive output (not inverted) | Driver output for CCD transfer clock   |

| 15      | CP_out           | Light load drive output (not inverted) | CCD clamp gate driver output           |

| 16      | 2B_out           | Light load drive output (not inverted) | Driver output for CCD last-stage clock |

Note: The internal circuits for heavy load drive pins  $\phi$  and  $\bar{\phi}$  have the same configuration as those of light load drive pins RS\_out, SH\_out, CP\_out and 2B\_out. Thus, these internal circuits have the same characteristics.

# **Truth Table**

|          | Inp   | Output         |    |                   |       |  |

|----------|-------|----------------|----|-------------------|-------|--|

| Pin Name | Logic | Pin Name Logic |    | Pin Name          | Logic |  |

|          |       | CK_in          | L  | ф                 | L     |  |

|          |       |                | _  | $\overline{\phi}$ | Н     |  |

|          |       | OK_III         | Н  | ф                 | Н     |  |

|          | L     |                | 11 | φ                 | L     |  |

|          |       | CP_in          | L  | CP_out            | L     |  |

|          |       |                | Н  | OI _Out           | Н     |  |

| OUT_cont |       | SH_in          | L  | SH_out            | L     |  |

|          |       |                | н  | OH_Out            | Н     |  |

|          |       | RS_in          | L  | RS_out            | L     |  |

|          |       | K3_III         | Н  | K3_out            | Н     |  |

|          |       | OD to          | L  | 2B_out            | L     |  |

|          |       | 2B_in          | Н  | 26_0ut            | Н     |  |

|          | Н     | _              | _  | All Output        | L     |  |

# Absolute Maximum Ratings (Ta = 25°C)

| Charac                                                  | cteristic                    | Symbol Rating                                 |                         | Unit |

|---------------------------------------------------------|------------------------------|-----------------------------------------------|-------------------------|------|

| Power supply voltage                                    | je                           | V <sub>CC</sub>                               | -0.5 to 7.0             | V    |

| Input voltage                                           |                              | V <sub>IN</sub> -1.2 to V <sub>CC</sub> + 0.5 |                         | V    |

| Output voltage                                          |                              | Vo                                            | -0.5 to V <sub>CC</sub> | V    |

| Input clamp diode c                                     | urrent (V <sub>IN</sub> < 0) | I <sub>IK</sub>                               | -50.0                   | mA   |

| Output clamp diode                                      | current (V <sub>O</sub> < 0) | I <sub>OK</sub> –50.0                         |                         | mA   |

| Output current                                          | High level                   | I <sub>OH</sub> (O)                           | -16.0                   | mA   |

| excluding other than $\phi$ , $\overline{\phi}$ outputs | Low level                    | I <sub>OL</sub> (O)                           | +16.0                   | mA   |

| φ output current                                        | High level                   | I <sub>OH</sub> (φ)                           | -150                    | mA   |

| φ σαιραί carrent                                        | Low level                    | I <sub>OL</sub> ( $\phi$ )                    | 150                     | mA   |

| Storage temperature                                     | е                            | T <sub>stg</sub>                              | -40 to 150              | °C   |

| Junction temperatur                                     | e                            | T <sub>j</sub> 150                            |                         | °C   |

| Thermal resistance                                      | Chip to ambient air          | $\theta_{ja}$                                 | 83                      | °C/W |

Note: Output current is specified as follows:  $V_{\mbox{OH}} = 4.0 \mbox{ V}, \mbox{ } V_{\mbox{OL}} = 0.5 \mbox{ V}.$

# Recommended Operating Conditions (Ta = 25°C)

| Characte                          | Symbol            | Min                 | Тур. | Max             | Unit  |    |

|-----------------------------------|-------------------|---------------------|------|-----------------|-------|----|

| Power supply voltage              | Vcc               | 4.7                 | 5.0  | 5.5             | V     |    |

| Input voltage                     | V <sub>IN</sub>   | 0                   | _    | V <sub>CC</sub> | V     |    |

| Output voltage                    | Vo                | 0                   | _    | V <sub>CC</sub> | V     |    |

| Output current_                   | High level        | V <sub>OH</sub> (O) | _    | _               | -8.0  | mA |

| excluding φ, φ outputs            | Low level         | V <sub>OL</sub> (O) |      |                 | 8.0   | mA |

| φ output current                  | High level        | V <sub>OH</sub> (φ) | _    | _               | -10.0 | mA |

| ψ σαιραί carrent                  | Low level         | V <sub>OL</sub> (φ) | _    | _               | 10.0  | mA |

| Thermal resistance (chip to case) | $\theta_{\sf jc}$ | _                   | 12   |                 | °C/W  |    |

| Operating temperature             | T <sub>opr</sub>  | 0                   | 25   | 60              | °C    |    |

| Input rise/fall time              | tri/tfi           | _                   | 2.5  | 5.0             | ns    |    |

Note: There is no hysteresis in the input block of this IC. Therefore attention should be given to the following:

A CMOS integrated circuit charges and discharges the capacitance load (internal equivalent capacitance) of

the internal circuit while operating. The charged or discharged current flows in the package of the IC and

inductance of transmission line, which causes inductive spike voltage to be generated.

When the spike voltage is generated in the reference GND, it affects the amplitude of an input signal. The amplitude seems to be fluctuating compared to when no spike voltage is generated in the reference GND. In this case, some induced spike waveforms exceed the input threshold level. For low-frequency inputs, the rate at which a spike exceeds the level increases, resulting in unstable output.

Therefore, do not apply input signals lower than 1  $\mu$ s. When designing a board, be sure to take transmission line inductance into consideration.

### **Electrical Characteristics**

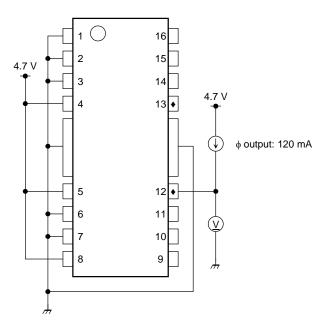

# DC Characteristics (unless otherwise specified, $V_{CC} = 4.7$ to 5.5 V, Ta = 0 to $60^{\circ}$ C)

| Characteristic                 |                         | Symbol                                         | Test<br>Circuit                                                                                                        | Test Condition                                                                                    | V <sub>CC</sub> | Min | Тур. | Max             | Unit |  |  |  |

|--------------------------------|-------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------|-----|------|-----------------|------|--|--|--|

| Input voltage                  | High                    | $V_{IH}$                                       | 1                                                                                                                      |                                                                                                   | 4.7             | 2.0 | _    | V <sub>CC</sub> | V    |  |  |  |

| input voltage                  | Low                     | VIL                                            | ] '                                                                                                                    |                                                                                                   | 4.7             | 0   | _    | 0.8             |      |  |  |  |

| Input clamp volta              | age                     | $V_{IK}$                                       | 2                                                                                                                      | I <sub>IK</sub> = -20 mA                                                                          | 4.7             | _   | _    | 1.0             | V    |  |  |  |

|                                |                         | V <sub>OH</sub> (O)                            | 3                                                                                                                      | $I_{OH} = -50 \mu A$                                                                              | 4.7             | 4.5 | _    | V <sub>CC</sub> |      |  |  |  |

| Qutput voltage e               | xcluding φ,             | VOH (O)                                        | 3                                                                                                                      | I <sub>OH</sub> = -8 mA                                                                           | 4.7             | 3.9 | _    | V <sub>CC</sub> | V    |  |  |  |

| φ outputs                      |                         | V <sub>OL</sub> (O)                            | 5                                                                                                                      | $I_{OL} = 50 \mu A$                                                                               | 4.7             | 0   | _    | 0.2             | V    |  |  |  |

|                                |                         | VOL (O)                                        | 3                                                                                                                      | I <sub>OL</sub> = 8 mA                                                                            | 4.7             | 0   | _    | 0.7             |      |  |  |  |

|                                |                         |                                                |                                                                                                                        | I <sub>OH</sub> = -10 mA                                                                          | 4.7             | 4.5 | _    | V <sub>CC</sub> |      |  |  |  |

|                                |                         | $V_{OH} \left( \phi / \overline{\phi} \right)$ | 3, 4                                                                                                                   | I <sub>OH</sub> = -30 mA                                                                          | 4.7             | 3.9 |      | Vcc             |      |  |  |  |

|                                |                         |                                                |                                                                                                                        | I <sub>OH</sub> = -120 mA                                                                         | 4.7             | 3.0 | _    | V <sub>CC</sub> | V    |  |  |  |

| φ output voltage               |                         |                                                |                                                                                                                        | I <sub>OL</sub> = 50 μA                                                                           | 4.7             | 0   | _    | 0.3             |      |  |  |  |

|                                |                         |                                                | 5, 6                                                                                                                   | I <sub>OL</sub> = 30 mA                                                                           | 4.7             | 0   | _    | 0.5             | 1    |  |  |  |

|                                |                         |                                                |                                                                                                                        | I <sub>OL</sub> = 120 mA                                                                          | 4.7             | 0   | _    | 2.0             |      |  |  |  |

| Input voltage                  |                         | I <sub>IN</sub>                                | 7                                                                                                                      | V <sub>IN</sub> = V <sub>CC</sub> or GND                                                          | 5.5             | _   | _    | 1.0             | μА   |  |  |  |

| Total                          |                         | I <sub>CC</sub>                                | 8                                                                                                                      | For light load output, all bits are High. For heavy load output, 2 bits are High. 2 bits are Low. | 5.5             | _   | _    | 15.0            |      |  |  |  |

| Static current consumption     | Forced low for all bits | ICCL                                           | _                                                                                                                      | Out_cont = "H"                                                                                    | 5.5             | _   | _    | 30.0            | mA   |  |  |  |

|                                | Each bit                | Δl <sub>CC</sub>                               | One input : V <sub>IN</sub> = 0.5 V or V <sub>CC</sub> – 2.1 V Other inputs : V <sub>IN</sub> = V <sub>CC</sub> or GND |                                                                                                   | _               | _   | _    | 1.5             |      |  |  |  |

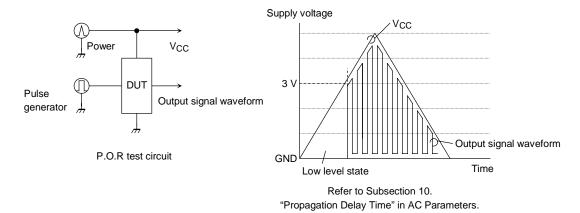

| Output off mode supply voltage |                         | V <sub>POR</sub>                               | (Note)                                                                                                                 | Light load power supply (V <sub>CC1</sub> ) reference                                             | _               | _   | 3.0  | _               | V    |  |  |  |

Note: Refer to the description of the P.O.R below.

# Mode in Which Output Is Held at Low at Power-On (P.O.R: Power On Reset circuit)

To eliminate the unstable period for the internal logic, this IC incorporates a function for monitoring the light load power supply (VCC1) at power-on to maintain the outputs at Low.

- At power-on, all output are held at Low until light load power supply (VCC1) reaches the voltage level of 3 V.

- When the light load power supply (VCC1) voltage is higher than 3 V (typ.), the internal logic operates according to input signals.

- For normal operation, be sure to use a power supply of 4.7 V or higher as guaranteed.

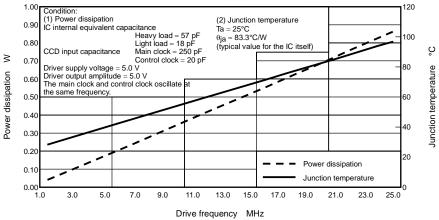

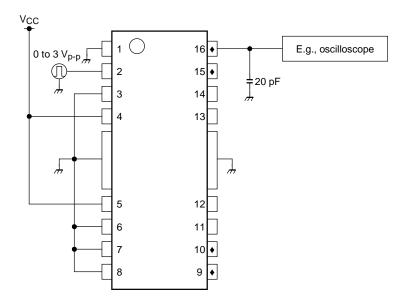

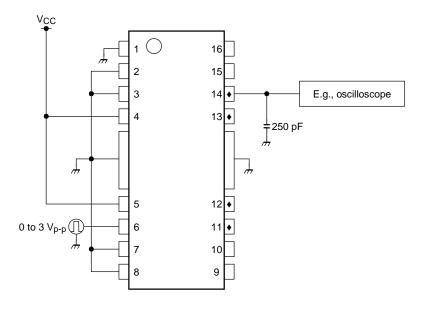

## AC Characteristics (input transition rise or fall time: $t_r/t_f = 3.0 \text{ ns}$ )

| Characteristic                      | Symbol         | Test Condition                    | Ta = 25°C, V <sub>CC</sub> = 5.0 V |      |      | Ta = 0 to $60^{\circ}$ C<br>V <sub>CC</sub> = 4.7 to<br>5.5 V |      | Unit | Reference<br>Measurement |  |

|-------------------------------------|----------------|-----------------------------------|------------------------------------|------|------|---------------------------------------------------------------|------|------|--------------------------|--|

|                                     |                |                                   | Min                                | Тур. | Max  | Min                                                           | Max  |      | Diagram                  |  |

|                                     | tpLH (φ)       | C <sub>I</sub> = 250 pF           | 5.3                                | 10.8 | 15.5 | 5.0                                                           | 16.0 |      | Measurement<br>diagram 1 |  |

| Propagation delay time              | tpHL (φ)       | OL = 230 pi                       | 5.3                                | 9.8  | 15.5 | 5.0                                                           | 16.0 | ns   |                          |  |

| r ropagation delay time             | tpLH (O)       | C <sub>I</sub> = 20 pF            | 2.5                                | 5.4  | 9.5  | 2.0                                                           | 10.0 |      | Measurement<br>diagram 2 |  |

|                                     | tpHL (O)       | OL = 20 pi                        | 2.5                                | 6.0  | 10.5 | 2.0                                                           | 12.0 |      |                          |  |

|                                     | tpCLH (φ)      | C <sub>L</sub> = 250 pF           | 9.5                                | 14.0 | 24.0 | 9.0                                                           | 25.0 | ns . | Measurement              |  |

| Output OFF time                     | tpCHL (φ)      |                                   | 9.5                                | 15.4 | 24.0 | 9.0                                                           | 25.0 |      | diagram 1                |  |

| Output OFF time                     | tpCLH (O)      | C: 20 pF                          | 7.2                                | 10.7 | 19.0 | 6.0                                                           | 23.0 |      | Measurement<br>diagram 2 |  |

|                                     | tpCHL (O)      | $C_L = 20 pF$                     | 7.3                                | 18.5 | 30.0 | 6.0                                                           | 35.0 |      |                          |  |

| Light load drive output skew        | to (skw)       | C <sub>L</sub> = 20 pF            | 0                                  | _    | 2.0  | 0                                                             | 2.0  | ns   | Measurement diagram 3    |  |

| Heavy load drive output crosspoints | VT (crs)       | C <sub>L</sub> = 100 to<br>250 pF | 1.5                                | _    | _    | 1.5                                                           | _    | V    | Measurement diagram 4    |  |

| Equivalent internal                 | CPD ( $\phi$ ) |                                   |                                    | 57   |      |                                                               |      |      |                          |  |

| capacitance (Note 1)                | CPD (O)        |                                   | _                                  | 18   | _    | _                                                             | _    | pF   |                          |  |

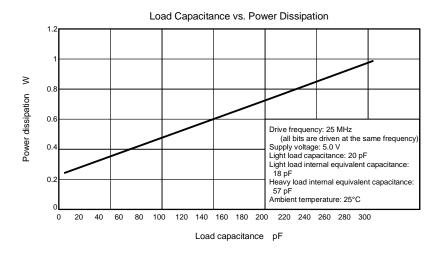

Note 1: CPD denotes "power dissipation capacitance". Dynamic power dissipation can be calculated using the CPD value.

$$Pd = \Sigma \left[ CPD \times V_{CC}^2 \times Fin \right] + \Sigma \left( CL \times V_{CC}^2 \times Fout \right)$$

CL: Load capacitance per output CPD: Power dissipation capacitance

Fin: Input clock frequency

Fout: Output clock frequency

For example:

For heavy load drive output, driving a load capacity of 250 pF at 25 MHz; For light load drive output, driving a load capacity of 20 pF at 25 MHz.

Note 2: In practice, the frequencies of some shift gate control signals are lower than the transfer clock. Therefore the power dissipation during practical use is smaller than the calculated value below.

$$Pd = [57 \text{ pF} \times 5.0 \text{ V} \times 5.0 \text{ V} \times 25 \text{ MHz}] \times 4 \text{ bit} + (250 \text{ pF} \times 5.0 \text{ V} \times 5.0 \text{ V} \times 25 \text{ MHz}) \times 4 \text{ bit} + [18 \text{ pF} \times 5.0 \text{ V} \times 5.0 \text{ V} \times 25 \text{ MHz}] \times 4 \text{ bit} + (20 \text{ pF} \times 5.0 \text{ V} \times 5.0 \text{ V} \times 25 \text{ MHz}) \times 4 \text{ bit} \\ \approx 862 \text{ mW}$$

The typical power dissipation is approximately 862 mW.

## **Notes on System Design**

As shown above, the TB62802FG consumes high current while operating. There is temporary flow of a current greater than the calculated value. To suppress bouncing from the power supply and GND, decoupling for the power supply is a vital necessity.

Below is an example of how the capacitance of a decoupling capacitor is calculated. Be sure to refer to this when designing a system.

The decoupling capacitor should be placed underneath the IC to reduce the high-frequency components.

Supply current variable: 350 mA (estimated variable in 1 bit)

Supply voltage variable: 0.3 V

Noise pulse width: 10 ns (time in which fluctuation occurs)

$\mathrm{C} = \Delta \mathrm{I_{CC}}/(\Delta \mathrm{V}/\Delta \mathrm{T})$

$= 350 \text{ mA} \times 4 \text{ bit/}(0.3 \text{ V/}10 \text{ ns})$

$\simeq 47 \text{ nF}$

$\simeq 0.047 \,\mu\text{F}$  (when using a normal capacitor)

To control the fluctuation in the low-frequency components, it is recommended that the power supply on the board be decoupled using a 10  $\mu$ F to 50  $\mu$ F capacitor.

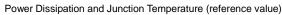

### **Reference Characteristics**

### **Thermal Design**

The junction temperature is expressed as follows:

$T_j = Ta + (\theta jc + \theta ca) \times Pd$

$= Ta + \theta ja \times Pd$

T<sub>i</sub>: Junction temperature

Ta: Ambient temperature

θjc: Thermal resistance from chip to case (a specific value not affected by environment)

Oja: Thermal resistance from chip to ambient temperature (affected by environment)

Pd: Power dissipation when driving external load

Here, the thermal performance of the heat dispersion on the PCB and of the ambient temperature setting should be so designed that the calculated value is within the specified range.

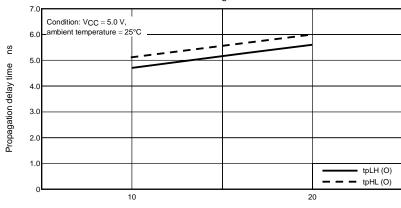

## Propagation Delay Time Capacitance Dependency of the TB62802FG Heavy Load Drive Pin

#### Propagation Delay Time Capacitance Dependency of the TB62802FG Light Load Drive Pin

Load capacitance pF

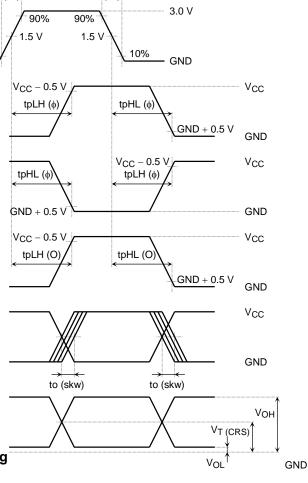

# **Waveform Measuring Point**

## **Propagation Delay Time Setting**

Input signal

- •2B\_in

- •CK\_in

- •SH\_in

- $\cdot$ RS\_in

- •CP in

- •out\_cont

### **Measurement Diagram 1**

$\bullet \phi$  Output signal

$\cdot \bar{\phi}$  Output signal

### **Measurement Diagram 2**

- $\cdot 2B_{out}$

- $\cdot$  CK\_out

- $\boldsymbol{\cdot} \mathrm{SH\_out}$

- $\boldsymbol{\cdot} \operatorname{RS\_out}$

- CP\_out

# **Measurement Diagram 3**

- $\cdot 2B_{out}$

- CK\_out

- $\cdot$ SH\_out

- $\cdot RS_{out}$

- CP\_out

tfi

tri

10%

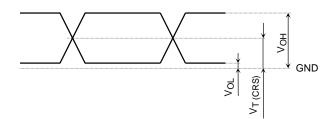

# **Output Waveform Crosspoint/Level Setting**

### **Measurement Diagram 4**

- \$\phi\$ Output signal

- \$\overline{\psi}\$ Output signal

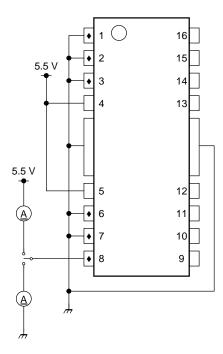

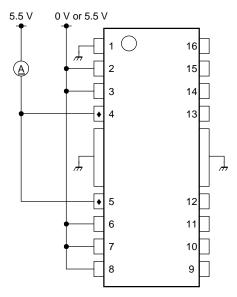

# **Test Circuit**

### **DC Parameters**

Pins marked with an asterisk (\*) are test pins. Be sure to ground those input pins that are not used as test pins so that the logic is determined. Unless otherwise specified, bits of the same type are measured in the same way.

### 1. V<sub>IH</sub>/V<sub>IL</sub>

### (1) Light load drive bits

Note 1: When measuring input pins, connect to GND those input pins that are not being measured.

### (2) Heavy load drive bits

Note 2: Connect to GND those input pins that are not being measured.

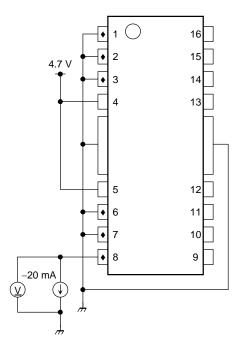

# 2. V<sub>IK</sub>

Note 1: When measuring input pins, connect to GND those input pins that are not being measured.

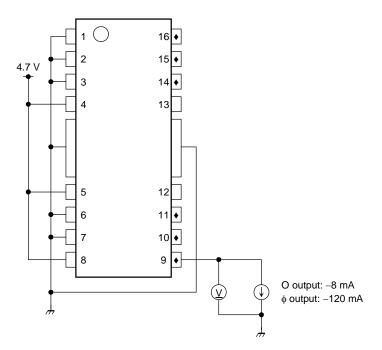

# 3. V<sub>OH</sub> (Ο/φ)

Note 2: Connect to GND those input pins that are not being measured.

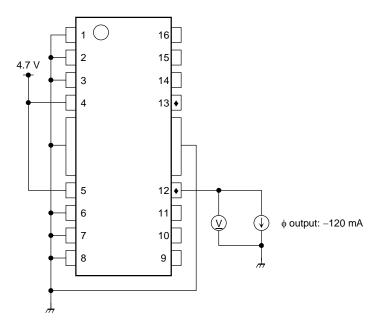

# 4. V<sub>OH</sub> (<sup>-</sup><sub>φ</sub>)

Note 1: Connect to GND those input pins that are not being measured.

# 5. V<sub>OL</sub> (Ο/φ)

Note 2 Connect to GND those input pins that are not being measured.

# 6. $V_{OL}(\bar{\phi})$

Note 1: Connect to GND those input pins that are not being measured.

# 7. I<sub>IN</sub>

Note 2: Connect to GND those input pins that are not being measured.

# 8. I<sub>CC</sub>

Note 1: The input logic of the heavy load drive clock input pin (pin 6) is the same for HIGH or LOW.

# 9. ∆I<sub>CC</sub>

Note 2: When measuring input pins, connect to GND (or to the power supply) those input pins that are not being measured.

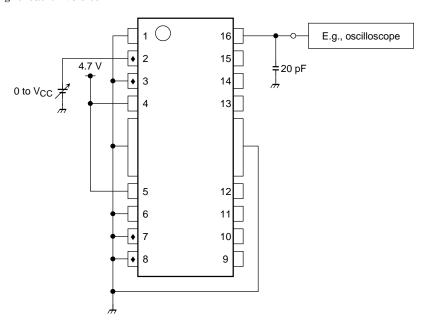

### **AC Parameters**

Pins marked with an asterisk (\*) are test pins. Ground those input pins that are not being used as test pins so that the logic is determined. Unless otherwise specified, bits of the same type are measured in the same way.

# 10. Propagation Delay Time

### (1) Light load drive bits

### (2) Heavy load drive bits

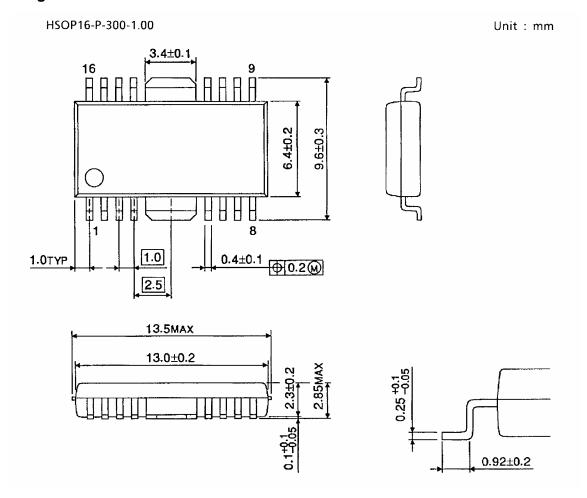

# **Package Dimensions**

Weight: 0.5 g (typ.)

#### **Notes on Contents**

### 1. Block Diagrams

Some of the functional blocks, circuits, or constants in the block diagram may be omitted or simplified for explanatory purposes.

#### 2. Equivalent Circuits

The equivalent circuit diagrams may be simplified or some parts of them may be omitted for explanatory purposes.

# 3. Timing Charts

Timing charts may be simplified for explanatory purposes.

## 4. Application Circuits

The application circuits shown in this document are provided for reference purposes only.

Thorough evaluation is required, especially at the mass production design stage.

To shiba does not grant any license to any industrial property rights by providing these examples of application circuits.

#### 5. Test Circuits

Components in the test circuits are used only to obtain and confirm the device characteristics. These components and circuits are not guaranteed to prevent malfunction or failure from occurring in the application equipment.

### **IC Usage Considerations**

### Notes on Handling of ICs

- (1) The absolute maximum ratings of a semiconductor device are a set of ratings that must not be exceeded, even for a moment. Do not exceed any of these ratings.

Exceeding the rating(s) may cause the device breakdown, damage or deterioration, and may result injury by explosion or combustion.

- (2) Use an appropriate power supply fuse to ensure that a large current does not continuously flow in case of over current and/or IC failure. The IC will fully break down when used under conditions that exceed its absolute maximum ratings, when the wiring is routed improperly or when an abnormal pulse noise occurs from the wiring or load, causing a large current to continuously flow and the breakdown can lead smoke or ignition. To minimize the effects of the flow of a large current in case of breakdown, appropriate settings, such as fuse capacity, fusing time and insertion circuit location, are required.

- (3) If your design includes an inductive load such as a motor coil, incorporate a protection circuit into the design to prevent device malfunction or breakdown caused by the current resulting from the inrush current at power ON or the negative current resulting from the back electromotive force at power OFF. IC breakdown may cause injury, smoke or ignition.

Use a stable power supply with ICs with built-in protection functions. If the power supply is unstable, the protection function may not operate, causing IC breakdown. IC breakdown may cause injury, smoke or ignition.

- (4) Do not insert devices in the wrong orientation or incorrectly.

- Make sure that the positive and negative terminals of power supplies are connected properly. Otherwise, the current or power consumption may exceed the absolute maximum rating, and exceeding the rating(s) may cause the device breakdown, damage or deterioration, and may result injury by explosion or combustion.

- In addition, do not use any device that is applied the current with inserting in the wrong orientation or incorrectly even just one time.

(5) Carefully select external components (such as inputs and negative feedback capacitors) and load components (such as speakers), for example, power amp and regulator.

If there is a large amount of leakage current such as input or negative feedback condenser, the IC output DC voltage will increase. If this output voltage is connected to a speaker with low input withstand voltage, overcurrent or IC failure can cause smoke or ignition. (The over current can cause smoke or ignition from the IC itself.) In particular, please pay attention when using a Bridge Tied Load (BTL) connection type IC that inputs output DC voltage to a speaker directly.

# Points to Remember on Handling of ICs

#### (1) Heat Radiation Design

In using an IC with large current flow such as power amp, regulator or driver, please design the device so that heat is appropriately radiated, not to exceed the specified junction temperature (Tj) at any time and condition. These ICs generate heat even during normal use. An inadequate IC heat radiation design can lead to decrease in IC life, deterioration of IC characteristics or IC breakdown. In addition, please design the device taking into considerate the effect of IC heat radiation with peripheral components.

#### (2) Back-EMF

When a motor rotates in the reverse direction, stops or slows down abruptly, a current flow back to the motor's power supply due to the effect of back-EMF. If the current sink capability of the power supply is small, the device's motor power supply and output pins might be exposed to conditions beyond absolute maximum ratings. To avoid this problem, take the effect of back-EMF into consideration in system design.

About solderability, following conditions were confirmed

- Solderability

- (1) Use of Sn-37Pb solder Bath

- · solder bath temperature = 230°C

- · dipping time = 5 seconds

- · the number of times = once

- · use of R-type flux

- (2) Use of Sn-3.0Ag-0.5Cu solder Bath

- solder bath temperature = 245°C

- · dipping time = 5 seconds

- · the number of times = once

- · use of R-type flux

#### RESTRICTIONS ON PRODUCT USE

060116EBA

- The information contained herein is subject to change without notice. 021023\_D

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as actificity in the most recent TOSHIBA products are please leads in mind the productions and

- set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc. 021023\_A

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk. 021023\_B

- The products described in this document shall not be used or embedded to any downstream products of which

manufacture, use and/or sale are prohibited under any applicable laws and regulations. 060106\_Q

- The information contained herein is presented only as a guide for the applications of our products. No

responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which

may result from its use. No license is granted by implication or otherwise under any patent or patent rights of

TOSHIBA or others. 021023\_c

- The products described in this document are subject to the foreign exchange and foreign trade laws. 021023\_E