TOSHIBA BI-CMOS INTEGRATED CIRCIUTS SILICON MONOLITHIC

TB62725P/F/FN

TB62725 series is the constant current driver designed for LED and the LED display. Output current value is set with one resistor with the outside.

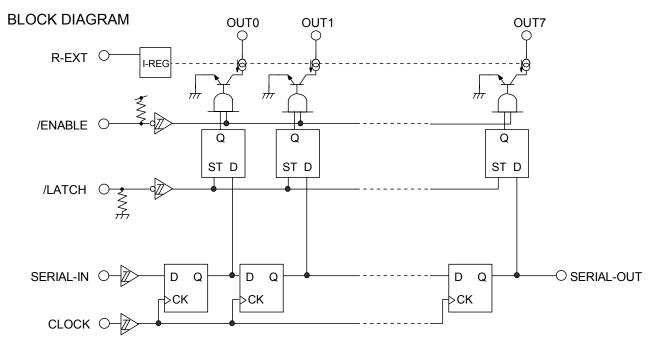

Then, all the output becomes the about same current. This driver builds in the constant current output of eight bits, the shift register of eight bits, the latch of eight bits and gate circuit.

This driver is designed by using the BI-CMOS process.

#### FEATURE

- \*Output Current Capability and the number of the output : 90mA X 8 outputs \*Constant Current Range : 5 to 90mA

- \*Application Output Voltage :

- 0.7V (output current 40 to 80 mA)

- 0.4V (output current 5 to 40 mA)

- \*For Annode Common LED

- \*Input Signal Voltage Level :

- 3.3V CMOS Level (Shmitt Triggered Input)

- \*Power Supply Voltage Range VDD=3.0 to 3.6V

- \*Muximum output terminal voltage 17V

- \*Serial and Pararell Data Transfer Rate : 20MHz (max, Cascade Connection)

- \*Operation Temperature Range :

- Topr= -40 to 85 degrees

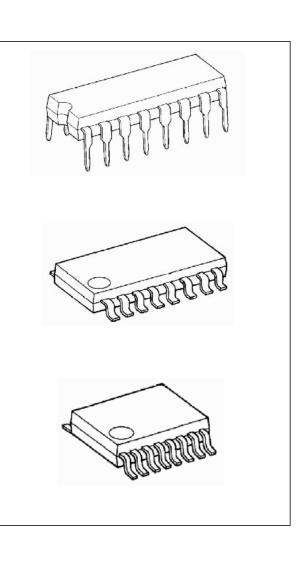

\*Package :

- Type P : DIP16-P-300-2.56A

- Type F : SSOP16-P-225-1.00

- Type FN : SSOP16-P-225-0.65

- \*Package and Pin Layout : Same as the TB62705 series.

\*Constant Current Error bitween bits ( All Output On )

| Output<br>Voltage | Current<br>Error<br>between bits | Current<br>Error<br>between ICs | Output<br>Current |

|-------------------|----------------------------------|---------------------------------|-------------------|

| >= 0.4V           | +/- 6%                           | +/- 15%                         | 2 to 40 mA        |

| >= 0.7V           |                                  |                                 | 2 to 90 mA        |

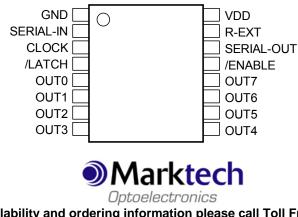

Pin layout (TOP VIEW)

For part availability and ordering information please call Toll Free: 800.984.5337 Website: www.marktechopto.com | Email: info@marktechopto.com

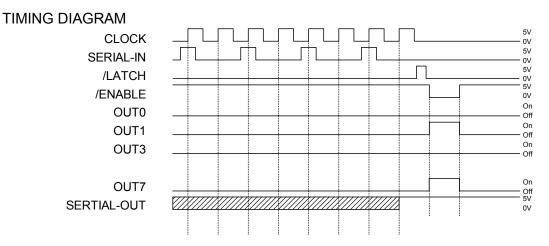

## TRUTH TABLE

| CLOCK | /LATCH | /ENABLE | SERIAL-IN | OUT0 OUT5 OUT7 | SERIAL-OUT |

|-------|--------|---------|-----------|----------------|------------|

| UP    | Н      | L       | Dn        | Dn Dn-5 Dn-7   | Dn-7       |

| UP    | L      | L       | Dn+1      | No Change      | Dn-6       |

| UP    | Н      | L       | Dn+2      | Dn+2 Dn-3 Dn-5 | Dn-5       |

| DOWN  | Х      | L       | Dn+3      | Dn+2 Dn-3 Dn-5 | Dn-5       |

| DOWN  | Х      | Н       | Dn+3      | Off            | Dn-5       |

Note) "OUT0 to 7 = On" in case of Dn= "H" Level and "OUT0 to 7 = Off" in case of Dn= "L" Level. A resistor is connected with R-EXT and GND accompanied with outside, and it is necessary that a correct power supply voltage is supplied.

Note) Latches are level sensitive, not rising edge sensitive and not syncronus CLOCK. Input of LATCH-terminal to "H" level, data passes latches and input to "L" level, data hold latches. Input of ENABLE-terminal to "H" level, all output (OUT0 to 7) off.

### TERMINAL DISCRIPTION

| PIN No. | PIN NAME   | FUNCTION                                                                                                                                 |

|---------|------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | GND        | GND terminal for control logic.                                                                                                          |

| 2       | SERIAL-IN  | Input terminal of a serial-data for shift-register                                                                                       |

| 3       | CLOCK      | Input terminal of a clock for data shift to up-edge.                                                                                     |

| 4       | /LATCH     | Input terminal of a data strobe. Latches passes data with "H" level input of LATCH-terminal, and hold data with "L" level input.         |

| 5~12    | OUT0 to 7  | Output terminals.                                                                                                                        |

| 13      | /ENABLE    | Input terminal of output enable. All outputs (OUT0 to 7) do off with "H" level input of ENABLE-terminal, and do on with "L" level input. |

| 14      | SERIAL-OUT | Output terminal of a serial-data for next SERIAL-IN terminal.                                                                            |

| 15      | R-EXT      | Input terminal of connects with a resister for to set up all output current.                                                             |

| 16      | VDD        | 5V Supply voltage terminal                                                                                                               |

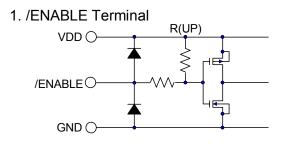

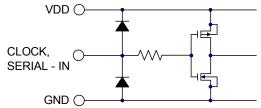

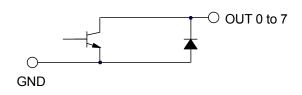

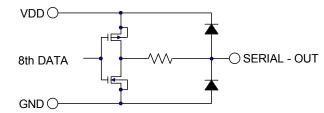

# EQUIVALENT CIRCUIT OF INPUTS AND OUTPUTS

3. CLOCK, SERIAL-IN Terminal

5. OUT0 to 7 Terminal

- 2. /LATCH Terminal VDDO /LATCH O GNDO R(DOWN)

- 4. SERIAL-OUT Terminal

| CHARACTERISTICS       | SYMBOL    | RATING                                         | UNIT   |

|-----------------------|-----------|------------------------------------------------|--------|

| Supply Voltage        | VDD       | 0 to 7                                         | V      |

| Input Voltage         | VIN       | -0.2 to VDD+0.2                                |        |

| Output Current        | IOUT      | +90                                            | mA/ch  |

| Output Voltage        | VOUT      | -0.5 to 17                                     | V      |

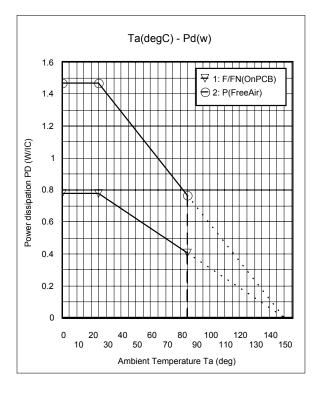

| Power Dissipation     | Pd1       | Type P : 1.47(Free Air)                        | W      |

|                       | Pd2       | Type F and FN : 0.37 (Free Air), 0.78 (On PCB) |        |

| Thrmal Resistance     | Rth(j-a)1 | Type P : 85(Free Air)                          | degC/W |

|                       | Rth(j-a)2 | Type F and FN : 330 (Free Air),160 (On PCB)    |        |

| Oparating Temperature | Topr      | -40 to 85                                      | degC   |

| Storage Temperature   | Tstg      | -55 to 150                                     |        |

# MAXIMUM RATINGS ( Ta = 25degC )

Note) Type P : Ambient temperature delated above 25degC in the proportion of 11.76 mW/degC. Type F and FN : Ambient temperature delated above 25degC in the proportion of 7.69 mW/degC. Condition) On PCB at 50 X 50 X 1.6mm Cu <= 40% ( Glass Epoxy PCB )

| CHARACTERISTICS                   | SYMBOL     | CONDITION          | MIN.   | TYP. | MAX.         | UNIT  |

|-----------------------------------|------------|--------------------|--------|------|--------------|-------|

| Supply Voltage                    | VDD        |                    | 3      | 3.3  | 3.6          | V     |

| Output Voltage                    | VOUT       |                    |        | 0.7  | 4            | V     |

| Output Current                    | IOUT       | Each DC 1 Circuit  | 2      |      | 70           | mA/ch |

|                                   | IOH        | SERIAL-OUT         |        |      | -1           | mA    |

|                                   | IOL        |                    |        |      | 1            |       |

| Input Voltage                     | VIH        |                    | 0.7VDD |      | VDD<br>+0.15 | V     |

|                                   | VIL        |                    | -0.15  |      | 0.3VDD       |       |

| Clock Frequency                   | fCLK       | Cascade Connected  |        |      | 20           | MHz   |

| /LATCH Pulse Width                | tw /LATCH  |                    | 50     |      |              |       |

| CLOCK Pulse Width                 | tw CLOCK   |                    |        |      | 25           |       |

| /ENABLE Pulse Width               | tw /ENABLE | Upper IOUT = 20 mA | 2000   |      |              |       |

|                                   |            | Lower IOUT = 20 mA | 4500   |      |              |       |

| Setup Time<br>for CLOCK Terminal  | tsetup1    |                    | 10     |      |              | ns    |

| Hold Time<br>for CLOCK Terminal   | thold      |                    | 5      |      |              |       |

| Setup Time<br>for /LATCH Terminal | tsetup2    |                    | 50     |      |              |       |

# RECOMMENDED OPERATING CONDITION (Ta=-40 to 85degC unless otherwise noted)

| CHARACTERISTICS                                | SYMBOL    | CONDITION                                    | MIN        | TYP    | MAX        | UNIT  |

|------------------------------------------------|-----------|----------------------------------------------|------------|--------|------------|-------|

| Supply Voltage                                 | VDD       | Normal Operation                             | 3.0        | 3.3    | 3.6        | V     |

| Output Current                                 | IOUT1     | VOUT=0.4V,REXT=490ohms                       | 31.9       | 37.5   | 43.1       | mA    |

|                                                | IOUT2     | VOUT=0.7V,REXT=250ohms                       | 62.6       | 73.6   | 84.6       |       |

| Output Current                                 | dIOUT1    | VOUT>=0.4V,REXT=490ohms<br>All outout on.    |            | +/-1.5 | +/-6       | %     |

| Error bitween bits                             | dIOUT2    | VOUT>=0.7V,REXT=250ohms<br>All outout on.    |            | +/-1.5 | +/-6       |       |

| Output Leakage<br>Current                      | IOZ       | VOUT=15.0V                                   |            | 1.0    | 5.0        | uA    |

| Input Voltage                                  | VIH       |                                              | 0.7<br>VDD |        | VDD        |       |

|                                                | VIL       |                                              | GND        |        | 0.3<br>VDD |       |

| SOUT Terminal                                  | VOL       | IOH=+1mA                                     |            |        | 0.4        | V     |

| Output Voltage                                 | VOH       | IOL=-1mA                                     | 2.8        |        |            |       |

| Output Currnet<br>Supply Voltage<br>Reguration | %/VDD     | VDD = 3V to 3.6V                             |            | +/-1.5 | +/-5.0     | %     |

| Pull up Resistor                               | R(up)     | /ENABLE Terminal                             | 100        | 200    | 400        | kohms |

| Pull down Resistor                             | R(down)   | /LATCH Terminal                              | 125        | 250    | 500        |       |

|                                                | IDD(OFF)1 | REXT=OPEN,VOUT=15.0V                         |            | 1      | 2          |       |

|                                                | IDD(OFF)2 | REXT=490Ohms,<br>VOUT=15V,OUT0 to 7 are Off. | 1          | 3      | 5          |       |

| Supply Current                                 | IDD(OFF)3 | REXT=250Ohms,<br>VOUT=15V,OUT0 to 7 are Off. | 3          | 6      | 8          | mA    |

|                                                | DD (ON)1  | REXT=490Ohms,<br>VOUT=0.7V,OUT0 to 7 are On. |            | 7      |            | ]     |

|                                                |           | Same as the avobe , Ta=-40degC               |            |        | 14         | 1     |

|                                                | DD (ON)2  | REXT=250Ohms,<br>VOUT=0.7V,OUT0 to 7 are On. |            | 13     |            |       |

|                                                |           | Same as the avobe , Ta=-40degC               |            |        | 25         |       |

# ELECTRICAL CHARACTERISTICS (VDD=3.3V, Ta=25degC unless otherwise noted)

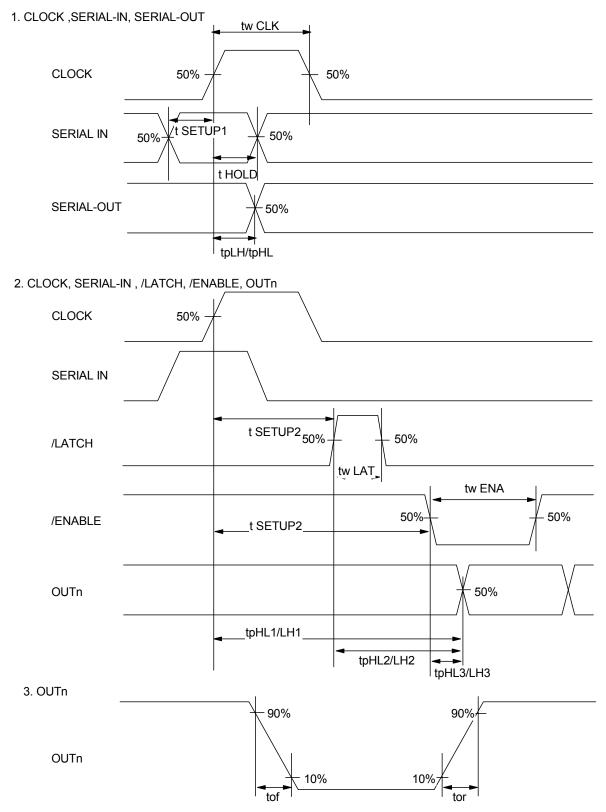

#### SWITCHING CHARACTERISTICS (Ta=25degC unless otherwise noted)

| CHARACTERISTICS            | SYBOL | TEST CONDITION                        | MIN | TYP | MAX | UNIT |

|----------------------------|-------|---------------------------------------|-----|-----|-----|------|

|                            | tpLH1 | CLK - OUTn,<br>/LATCH="H",/ENABLE="L" |     | 140 |     |      |

|                            | tpLH2 | /LATCH - OUTn, /ENABLE="L"            |     | 140 |     |      |

|                            | tpLH3 | /ENABLE - OUTn, /LATCH="H"            |     | 140 |     |      |

| Propagation                | tpLH  | CLK - SERIAL OUT                      |     | 5   |     |      |

| Delay Time                 | tpHL1 | CLK - OUTn,<br>/LATCH="H",/ENABLE="L" |     | 170 |     |      |

|                            | tpHL2 | /LATCH - OUTn, /ENABLE="L"            |     | 170 |     | ns   |

|                            | tpHL3 | /ENABLE - OUTn, /LATCH="H"            |     | 170 |     |      |

|                            | tpHL  | CLK - SERIAL OUT                      |     | 6   |     |      |

| Output Rise Time           | t or  | Voltage Waveform 10% to 90%           |     | 70  |     |      |

| Output Fall Time           | t of  | Voltage Waveform 90% to 10%           |     | 90  |     |      |

| Muximum CLOCK<br>Rise Time | tr    | Cascade connection isn't guarantee.   |     |     | 5   | us   |

| Muximum CLOCK<br>Fall Time | tf    | (Note1)                               |     |     | 5   |      |

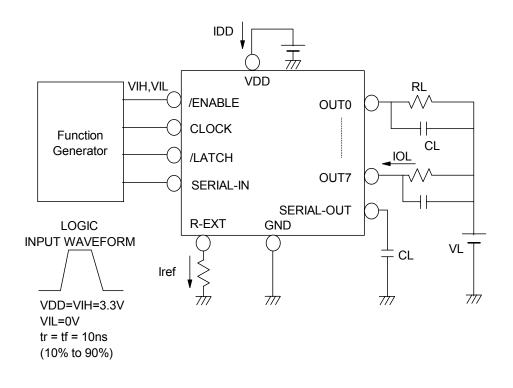

Condition : (Refer to test circuit.)

Ta= 25 degC, VDD=VIH=3.3V, VOUT=0.7V, VIL=0V, REXT=490ohms, VL=3.0V, RL=60ohms, CL=10.5pF

Note 1 : When tf / tf of clock wave form is enlarged at the time as the cascade connection, the timing condition which is necessary for the data transfer may not be able to be secured. Give careful consideration to the timing condition.

# **TEST CIRCUIT**

## TIMING WAVEFORM

Provisional Data Sheet (Subject to change without notice.)

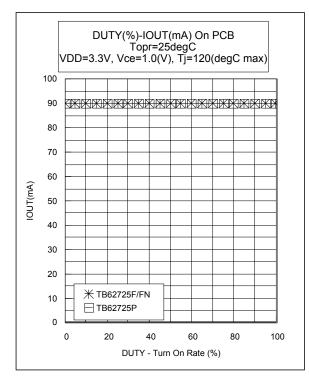

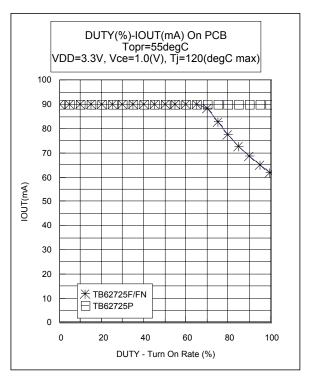

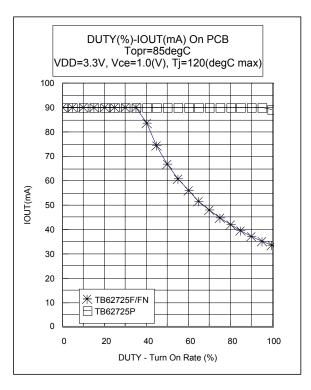

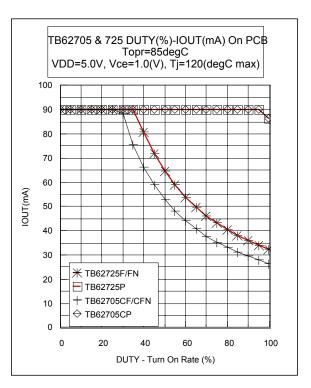

# OUTPUT CURRNET vs Duty (LED Turn On Rate)

# TOSHIBA

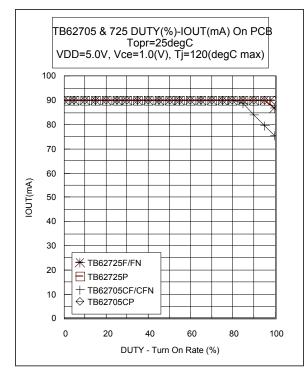

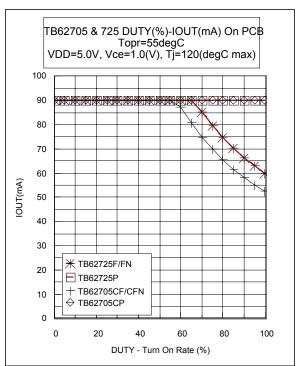

# OUTPUT CURRNET vs Duty (LED Turn On Rate) \*\* Comparison in VDD=5V of TB62705 and TB6272

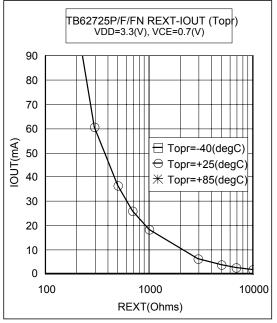

# **OUTPUT CURRNET vs REXT RESISTOR**

IOUT[mA]=(1.14/REXT[ohms])\*16 -- Theory formula

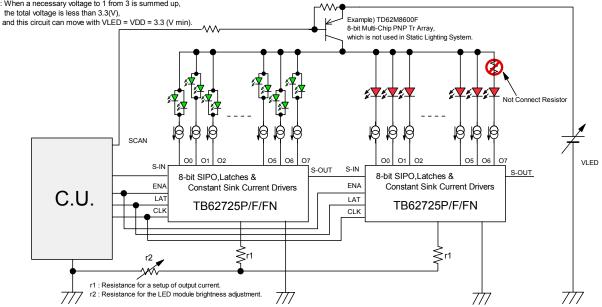

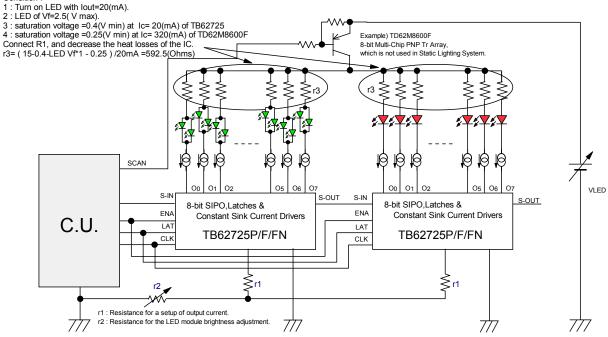

# APPLICATION NOTES(1 of 2)

#### TB62725P/F/FN application circuit (a general example)

TB62725 Series recommend VLED=VDD= 3.3(V min) and data transfer of fclk=20(MHz) is possible at cascade connection.

- 1: Vf of LED is Vf=2.5 (V max).

- 2 : Output saturation Vce1 = 0.4(V min) at lout <= 40(mA) of TB62725.

- : Output saturation Vce2 = -0.25(V max) at Ic = -1(A) of TD62M8600F : TB62725 can move with VDDopr = 3 to 3.6(V). 3

- 5 : When a necessary voltage to 1 from 3 is summed up

This device owns only one ground pin that means signal ground pin and power ground pin are common. If ground pattern layout contains large inductance and impedance, and the voltage between ground and LATCH, CLOCK terminals exceeds 0.5\*Vdd by switching noise in operation, this device may miss-operate. So we would lile you to pay attention to pattern layout to minimize inductance.

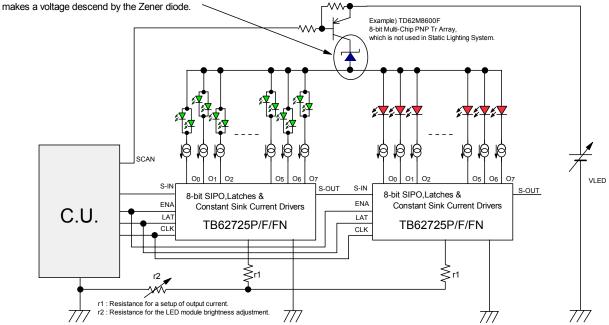

# APPLICATION NOTES(2 of 2)

TB62725P/F/FN application circuit (the case of VLED>17(V))

#### Example :

An unnecessary voltage in the case of VLED>17(V)

TB62725P/F/FN application circuit (with VLED<=17(V), the case of the over-saturation) Example

An over-saturation voltage makes a voltage descend by the resistance with the outside.

- Condition :

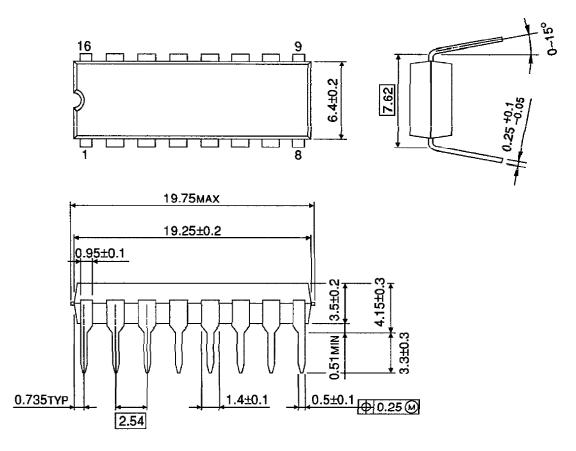

#### OUTLINE DRAWING DIP16-P-300-2.54A

Unit : mm

Weight : 1.11g (Typ.)

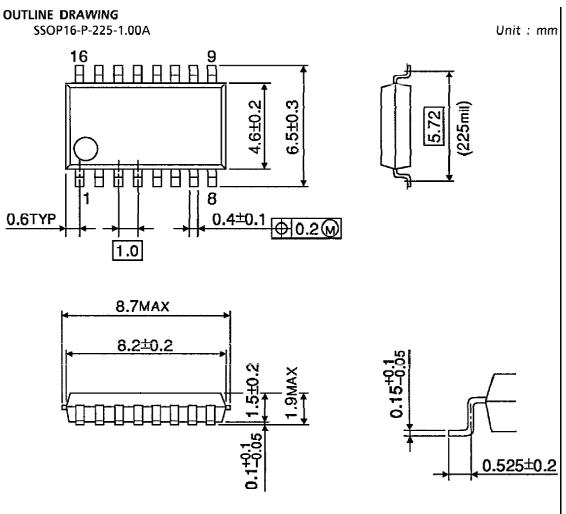

Weight : 0.14g (Typ.)

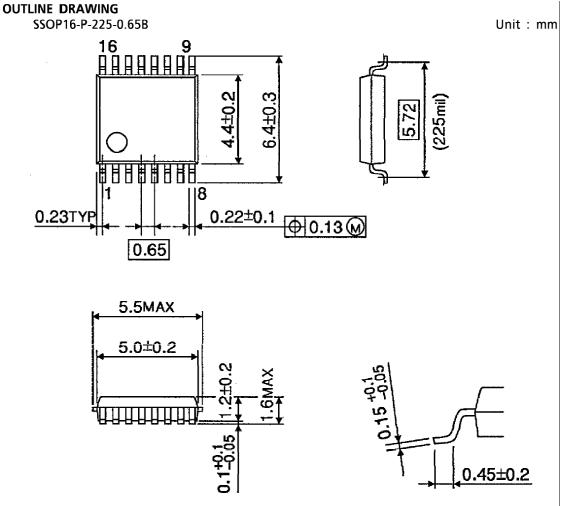

Weight: 0.07g (Typ.)

The information contained herein is subject to change without notice.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patens or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others.

TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within spacified operating ranges as set forth in the most recent products spacifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

The products described in the document may include products subject to foreign exchange and foreign trade control laws.

(C) 2000 TOSHIBA CORPORATION ALL RIGHT Reserved